#### Condor Engineering CEI520A-1616 **ARINC Interface for PCI**

In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/82073-5

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

· Full-service, independent repair center

ARTISAN' TECHNOLOGY GROUP

Your definitive source for quality pre-owned equipment.

**Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

Critical and expedited services In stock / Ready-to-ship

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# User's Manual CEI-100/CEI-200/CEI-x20

#### Copyrights

Software Copyright © 1998-2016 Abaco Systems, Inc.

User's Manual Copyright © 1998-2016 Abaco Systems, Inc.

This software product is copyrighted and all rights are reserved. The distribution and sale of this product are intended for the use of the original purchaser only per the terms of the License Agreement.

Confidential Information - This document contains Confidential/Proprietary Information of Abaco Systems, Inc. and/or its suppliers or vendors. Distribution or reproduction prohibited without permission.

THIS DOCUMENT AND ITS CONTENTS ARE PROVIDED "AS IS", WITH NO REPRESENTATIONS OR WARRANTIES OF ANY KIND, WHETHER EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO WARRANTIES OF DESIGN, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. ALL OTHER LIABILITY ARISING FROM RELIANCE ON ANY INFORMATION CONTAINED HEREIN IS EXPRESSLY DISCLAIMED.

Microsoft is a registered trademark of Microsoft Corporation.

Windows is a registered trademark of Microsoft Corporation.

Abaco Systems, Inc. acknowledges the trademarks of other organizations for their respective products or services mentioned in this document.

#### CEI-100/CEI-200/CEI-x20 User's Manual (1500-011)

Document Revision: 6.15

Document Date: 8 November 2016

**Software Revisions:**

CEI-SW for CEI-100, CEI-200 4.52

CEI-x20-SW for CEI-220, CEI-420/420A, CEI-520/520A, CEI-620, CEI-820, CEI-820TX 4.50

Abaco Systems, Inc. 26 Castilian Drive, Suite B Goleta, CA 93117

Main +1 805-965-8000 or 877-429-1553 (US-only)

Support +1 805-883-6097

support@abaco.com (email)

https://www.abaco.com/products/avionics

#### Additional Resources

For more information, please visit the Abaco Systems website at:

www.abaco.com

# Contents and Tables

# Contents

| Chapter 1 | Introduction                                          | 1  |

|-----------|-------------------------------------------------------|----|

|           | Features                                              | 1  |

|           | Hardware Specifications                               | 2  |

| Chapter 2 | Installation                                          | 1  |

| Onapter 2 | Overview                                              |    |

|           |                                                       |    |

|           | Installing the Board                                  |    |

|           | Setting the ISA Bus Base Address.                     |    |

|           | ARINC 429 Slew Rate Configuration for CEI-100/CEI-200 |    |

|           | Configuring the CEI-820TX                             |    |

|           | CEI-820TX Input/Output Connector Pin Out              |    |

|           | Configuring the CEI-820                               |    |

|           | CEI-820 Outline Drawing                               |    |

|           | CEI-820 Input/Output Connector Pin Out                |    |

|           | CEI-820 Transition Cable Pin Out                      |    |

|           | Configuring the CEI-620                               |    |

|           | CEI-620 Outline Drawing                               |    |

|           | CEI-620 Input/Output Connector Pin Out                |    |

|           | CEI-620 Transition Cable Pin Out                      | 15 |

|           | Configuring the CEI-520 and CEI-520A                  | 17 |

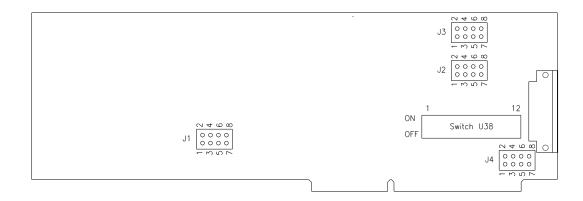

|           | CEI-520/520A Outline Drawing                          | 17 |

|           | CEI-520/520A Input/Output Connector Pin Out           | 17 |

|           | CEI-520/520A Transition Cable Pin Out                 | 21 |

|           | Configuring the CEI-220                               | 22 |

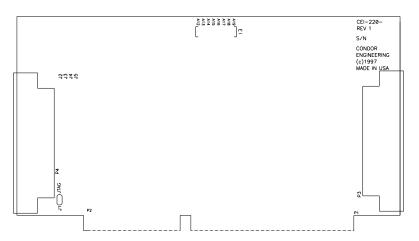

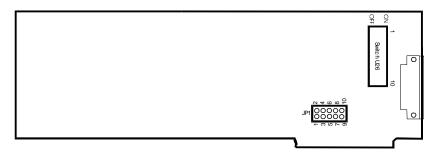

|           | CEI-220 Outline Drawing                               | 22 |

|           | CEI-220 Base Memory Address                           | 22 |

|           | CEI-220 Interrupts and Slew Rate                      |    |

|           | CEI-220 ARINC Connector Pin Out                       |    |

|           | Configuring the CEI-420 and CEI-420A                  |    |

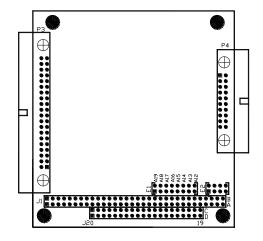

|           | CEI-420/420A Outline Drawing                          |    |

|           | CEI-420/420A Base Memory Address                   | 26 |

|-----------|----------------------------------------------------|----|

|           | CEI-420/420A Interrupts and Slew Rate              | 26 |

|           | CEI-420/420A Power                                 | 26 |

|           | CEI-420/420A ARINC Connector Pin Out               | 27 |

|           | Configuring the CEI-200                            | 29 |

|           | CEI-200 Outline Drawing                            | 29 |

|           | CEI-200 Base Memory Address                        | 29 |

|           | CEI-200 Base I/O Address                           | 30 |

|           | CEI-200 Interrupts and Slew Rate                   | 30 |

|           | CEI-200 ARINC Connector Pin Out                    | 31 |

|           | Configuring the CEI-100                            | 32 |

|           | CEI-100 Outline Drawing                            | 32 |

|           | CEI-100 Base Memory Address                        | 32 |

|           | CEI-100 Base I/O Address                           | 33 |

|           | CEI-100 Interrupts and Slew rate                   | 33 |

|           | CEI-100 ARINC Connector Pin Out                    | 34 |

|           | CEI-100/CEI-200 Software Installation              | 35 |

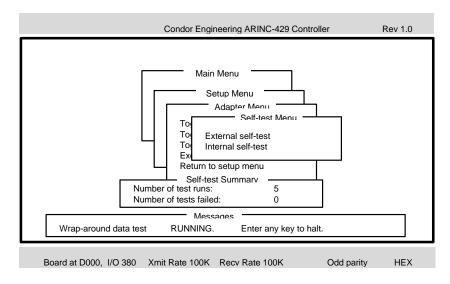

|           | CEI-100/CEI-200 Self-test                          | 35 |

|           | CEI-x20 Software Installation                      | 36 |

|           | CEI-220/420/420A/520/520A/620/820/820TX Self-test  | 37 |

|           | CEI-220 Discrete Inputs                            | 37 |

|           | CEI-420/420A/520/520A/620/820 Discrete Inputs      | 39 |

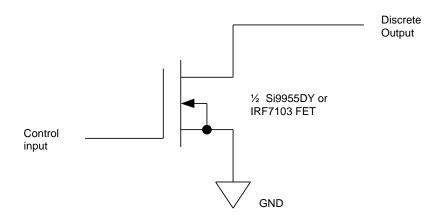

|           | CEI-220/420/420A/520/520A/620/820 Discrete Outputs | 40 |

| Chapter 3 | CEI-100/200 ARINC Test Program                     | 42 |

|           | General Information                                |    |

|           | Accessing the Program                              |    |

|           | Example 1                                          |    |

|           | Example 2                                          |    |

|           | Hot Keys                                           |    |

|           | Main Menu                                          |    |

|           | Setup Menu                                         |    |

|           | Board Setup                                        |    |

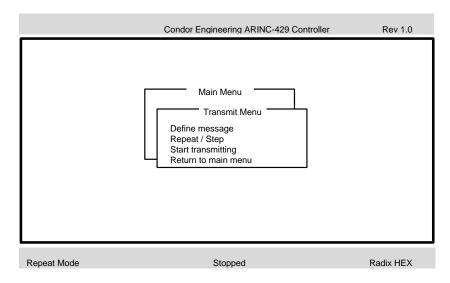

|           | Transmit Menu                                      |    |

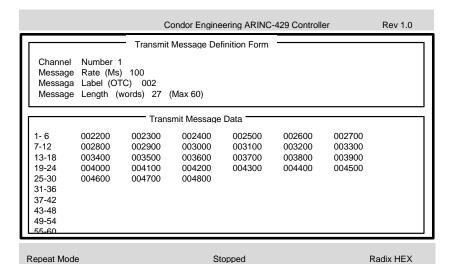

|           | Defining a Message                                 |    |

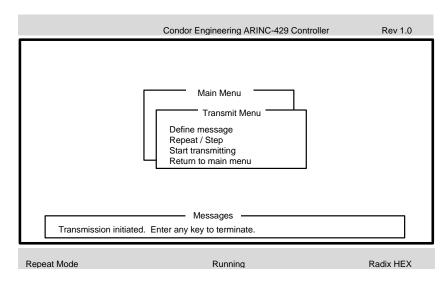

|           | Transmitting a Message                             |    |

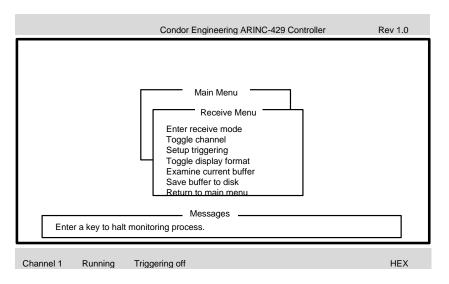

|           | Receive Menu                                       |    |

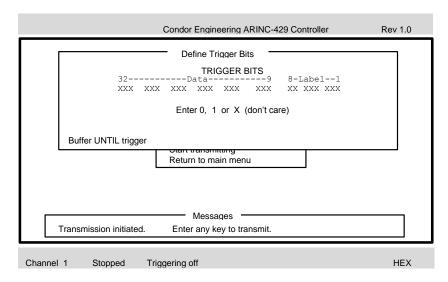

|           | Triggering                                         |    |

|           | Receiving Messages                                 |    |

| Chapter 4 | BusTools/ARINC Data Bus Analyzer                   | 54 |

| onapter 4 | General Information                                | 54 |

|           |                                                    |    |

|           | BusTools/ARINC Demo Software            | 54 |

|-----------|-----------------------------------------|----|

| Chapter 5 | Program Interface Library               | 55 |

|           | Overview                                |    |

|           | DOS Programming                         |    |

|           | Windows, VxWorks, and Linux Programming |    |

|           | CEI-100/200 Programming                 |    |

|           | CEI-x20 Programming                     |    |

|           | Programming the ARINC Interface         |    |

|           | ARINC 429 Data Format                   |    |

|           | Label Formatting                        | 60 |

|           | Transmission Order                      |    |

|           | ARINC Parity                            |    |

|           | CEI-x20 Interrupt Support               |    |

|           | Receiver 'Await Data' Mode              |    |

|           | Utility Routines – Summary              |    |

|           | Utility Routines – By Function          | 65 |

|           | Board and API Initialization            |    |

|           | Board and API Information               | 65 |

|           | Error Reporting                         |    |

|           | Tick-Timer and Time Tag Functions       |    |

|           | Channel Parameter Definition/Setup      |    |

|           | Channel Parameter Read-Back             | 67 |

|           | Mode Control                            |    |

|           | Channel Data Read Functions             |    |

|           | Channel Data Write Functions            |    |

|           | Label Filtering Functions               |    |

|           | Data Structure Initialization Functions |    |

|           | Hardware Interrupt Control              |    |

|           | Miscellaneous Functions                 |    |

|           | Board and Application Shutdown          |    |

|           | AR _CANCEL_DATA_WAIT                    |    |

|           | AR _CLOSE                               |    |

|           | AR_CLR_RX_COUNT                         | 72 |

|           | AR_DEFINE_MSG                           |    |

|           | AR_EXECUTE_BIT                          |    |

|           | Supported Built-In Tests                | 75 |

|           | AR_GET_BOARDNAME                        |    |

|           | AR_GET_BOARDTYPE                        |    |

|           | AR_GET_CONFIG                           |    |

|           | CEI-x20 Parameters                      |    |

|           | CEI-100/200 Items                       |    |

|           | CFI-v20 Items                           | 83 |

| AR_GET_ERROR                              | 85  |

|-------------------------------------------|-----|

| AR_GET_LABEL_FILTER                       | 86  |

| AR_GET_LATEST                             | 87  |

| AR_GET_RAW_MODE                           | 89  |

| AR_GET_RX_COUNT                           | 90  |

| AR_GET_TIMERCNT                           | 91  |

| AR_GET_TIMERCNTL                          | 92  |

| AR_GETBLOCK                               | 93  |

| AR_GETFILTER                              | 95  |

| AR_GETNEXT                                | 97  |

| AR_GETNEXTT                               | 98  |

| AR_GETWORD                                | 99  |

| ARINC 429 Receiver Buffer Data Format     | 99  |

| ARINC 573/717 Receiver Buffer Data Format | 99  |

| CSDB Receiver Buffer Data Format          | 100 |

| AR_GETWORDT                               | 102 |

| AR_GO                                     | 104 |

| AR_INIT_DUAL_PORT                         | 105 |

| AR_INIT_SLAVE                             | 106 |

| AR_INT_CONTROL                            | 107 |

| AR_INT_SET                                | 109 |

| AR_INT_SLAVE                              | 110 |

| AR_LABEL_FILTER                           | 111 |

| AR_LOADSLV                                | 112 |

| AR_MODIFY_MSG                             | 114 |

| AR_MSG_CONTROL                            | 116 |

| AR_NUM_RCHANS                             | 118 |

| AR_NUM_XCHANS                             | 119 |

| AR_PUTBLOCK                               | 120 |

| AR_PUTFILTER                              | 121 |

| AR_PUTWORD                                | 122 |

| ARINC 429 Transmit Data Format            | 122 |

| ARINC 573/717 Transmit Data Format        | 122 |

| CSDB Transmit Data Format                 | 123 |

| AR_PUTWORD2X16                            | 125 |

| AR_RECREATE_PARITY                        | 126 |

| AR_REFORMAT                               | 127 |

| AR_RESET                                  | 128 |

| AR_RESET_INT                              | 129 |

| AR_RESET_TIMERCNT                         | 130 |

| AR_SET_CONFIG                             | 131 |

| CEI-100/200 Items                         | 131 |

| CFL-v20 Items                             | 132 |

| Appendix B | CEI-x20 Structure Definitions              | 169 |

|------------|--------------------------------------------|-----|

| Appendix A | Modifying CEI-200 Base Bit Rate            |     |

|            | Transmitting Data                          | 165 |

|            | Filtering Out Labels                       |     |

|            | Receiving Data                             | 163 |

|            | Enabling Interrupts                        |     |

|            | Enabling Time Tags                         |     |

|            | Selecting the Receive Modes                |     |

|            | Controlling the Timers                     |     |

|            | Programming the ARINC Channel Setup        |     |

|            | Initializing the Board                     |     |

|            | Controlling the Board                      |     |

|            | Loading the Board                          |     |

| Chapter 7  | Description of CEI-100/200 ARINC Interface |     |

|            | Building the Sample Program                | 157 |

|            | Building the CEI-x20 API                   |     |

|            | ISA Memory Mapping                         |     |

|            | x86 PCI BIOS Configuration                 |     |

|            | Building a VxWorks Image                   |     |

| Chapter 6  | VxWorks Support                            |     |

| Chantar 6  | VvWorke Support                            | 150 |

|            | AR_XMIT_SYNC                               | 152 |

|            | AR_VERSION                                 |     |

|            | AR_TIMETAG_CONTROL                         |     |

|            | AR_SLEEP                                   |     |

|            | AR_SETINTERRUPTS                           |     |

|            | AR_SET_HMERRATEAR_SETCHPARMS               |     |

|            | AR_SET_STORAGE_MODEAR_SET_TIMERRATE        |     |

|            | AR_SET_RAW_MODE<br>AR_SET_STORAGE_MODE     |     |

|            | AR_SET_PRELOAD_CONFIG                      |     |

|            | AR_SET_CONTROL                             |     |

|            | CEI-x20 Parametric Values                  |     |

|            | CEL-x20 Values                             |     |

|            | CEI-100/200/x20 Values                     |     |

|            |                                            |     |

|            | AR_CHANNEL_PARMS               | 169 |

|------------|--------------------------------|-----|

| Appendix C | Parametric Voltage Programming | 174 |

| • •        | Introduction                   |     |

|            | CEI-220 DAC Definitions        | 174 |

|            | CEI-420/420A DAC Definitions   | 175 |

|            | CEI-520/520A DAC Definitions   | 175 |

|            | CEI-620 DAC Definitions        | 176 |

|            | CEI-820 DAC Definitions        | 176 |

| Appendix D | Example CEI-x20 Programs       | 177 |

|            | Introduction                   |     |

|            | .NET Example Programs          | 177 |

|            | Visual Basic 6 Example Program | 177 |

|            | LabWindows CVI Support         | 178 |

|            | C/C++ Example Programs         | 178 |

# Figures

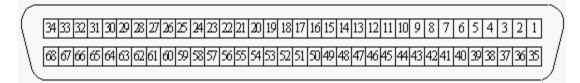

| Figure 1. 68-pin Receptacle Connector (SCSI-3 compatible, view facing receptacles)    | 6    |

|---------------------------------------------------------------------------------------|------|

| Figure 2. CEI-820 Outline Drawing                                                     | 8    |

| Figure 3. 50-pin P1 connector (AMP Champ 0.8 mm receptacle connectors - AMP part      |      |

| number 787096-1)                                                                      | 8    |

| Figure 4. CEI-620 Outline Drawing                                                     | 12   |

| Figure 5. 50-pin Connector (AMP Champ 0.8 mm Receptacle Connectors - AMP Part         |      |

| Number 787096-1)                                                                      |      |

| Figure 6. CEI-520/520A Outline Drawing                                                | 17   |

| Figure 7. 68-pin Receptacle Connector (SCSI-3 compatible with rails and latch blocks, |      |

| view facing receptacles)                                                              |      |

| Figure 8. 50-pin IDC-style Discrete I/O connector (3M Part Number 2550-6002-UB)       |      |

| Figure 9. 68-pin connector for the CEI-520/520A Transition Cable                      |      |

| Figure 10. CEI-220 Outline Drawing                                                    |      |

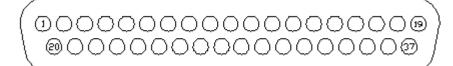

| Figure 11. CEI-220 P3 Connector Pinout                                                |      |

| Figure 12. CEI-220 P4 Connector Pinout                                                |      |

| Figure 13. CEI-420/420A Outline Drawing                                               |      |

| Figure 14. CEI-420/420A P4 Front View                                                 | 28   |

| Figure 15. CEI-200 Outline Drawing                                                    |      |

| Figure 16. CEI-200 I/O Connector - Front View                                         | 31   |

| Figure 17. CEI-100 Outline Drawing                                                    |      |

| Figure 18. CEI-100 I/O Connector - Front View                                         | 34   |

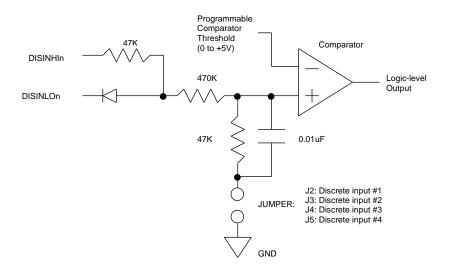

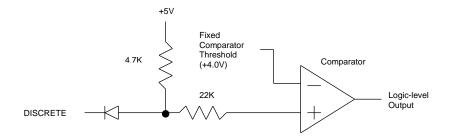

| Figure 19. CEI-220 Discrete Inputs Circuit                                            | 37   |

| Figure 20. CEI-420/420A/520/520A/620/820 Discrete Input Circuit                       | 39   |

| Figure 21. CEI-220/420/420A/520/520A/620/820 Discrete Outputs                         | 40   |

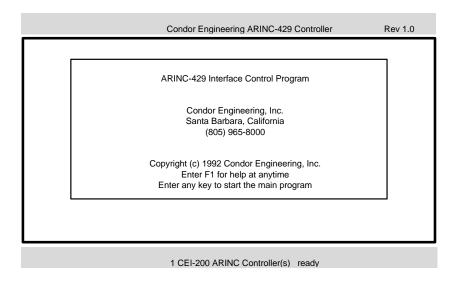

| Figure 22. Welcome Screen                                                             | 43   |

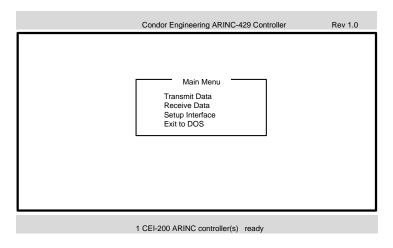

| Figure 23. Main Menu                                                                  | 45   |

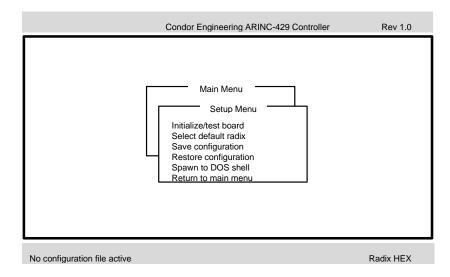

| Figure 24. Setup Menu                                                                 | 46   |

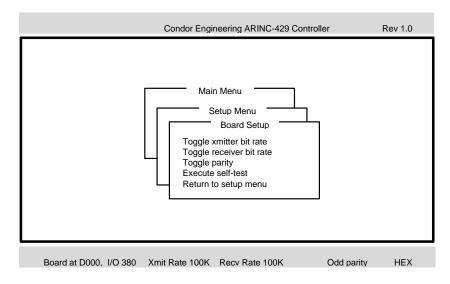

| Figure 25. Board Setup Menu                                                           | 47   |

| Figure 26. Self-test                                                                  | 48   |

| Figure 27. Transmit Menu                                                              | 48   |

| Figure 28. Transmit Message Definition Form                                           | 49   |

| Figure 29. Screen during Transmission                                                 | 50   |

| Figure 30. Receive Menu                                                               | 51   |

| Figure 31. Trigger Bit Definition                                                     | 52   |

| Figure 32. Sample Application Trace                                                   | .158 |

# Tables

| Table 1. Hardware Specifications                                          | 2  |

|---------------------------------------------------------------------------|----|

| Table 2. CEI-820TX Connector Definitions (P1 and P14)                     | 7  |

| Table 3. CEI-820-xx and CEI-820-xxJ Connector Definitions (P1 and P14)    | 8  |

| Table 4. CEI-820-44L Connector Definitions (P1 and P14)                   | 10 |

| Table 5. Mating Connector for P1                                          | 11 |

| Table 6. CEI-820 Transition Cable Pin Out                                 | 11 |

| Table 7. CEI-620 Rear Panel Input/Output Connector Definition             | 12 |

| Table 8. Front View – ARINC 429 Input/Output Connector (P1 and P2)        | 14 |

| Table 9. Mating Connectors for P1 and P2                                  | 15 |

| Table 10. CEI-620 Transition Cable Pin Out                                | 15 |

| Table 11. Front View – Standard CEI-520/520A ARINC 429 I/O Connector (P2) | 18 |

| Table 12. Front View – CEI-520-1208-C/CEI-520A-1208-C I/O Connector (P2)  | 18 |

| Table 13. Front View – CEI-520-xxxx-J/CEI-520A-xxxx-J I/O Connector (P2)  | 19 |

| Table 14. CEI-520/520A P2 Mating Connector                                | 20 |

| Table 15. Top View – Discrete Input/Output Connector (P3)                 | 20 |

| Table 16. CEI-520/520A P3 Mating Connector                                | 21 |

| Table 17. Mapping of Switch Positions to Address Bits                     | 22 |

| Table 18. CEI-220 P3 Connector Change for ARINC 6-wire Configurations     | 24 |

| Table 19. Mapping of Switch Positions to Address Bits                     | 26 |

| Table 20. CEI-420/420A P3 Front View                                      | 27 |

| Table 21. CEI-420/420A P3 Pin Connections                                 | 28 |

| Table 22. CEI-420/420A P4 Pin Connections                                 | 28 |

| Table 23. CEI-200 Mapping of Switch Positions to Address Bits             | 29 |

| Table 24. Default Address of 380 (hex) Example                            | 30 |

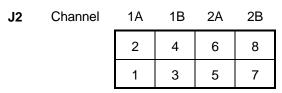

| Table 25. Jumper blocks J2 and J3                                         | 30 |

| Table 26. Jumper block J4                                                 | 31 |

| Table 27. CEI-200 I/O Connector Pin Assignments                           | 31 |

| Table 28. Default Address of CC00 Example                                 | 32 |

| Table 29. Default Address of 380 (hex) Example                            | 33 |

| Table 30. Jumper block JP1                                                | 33 |

| Table 31. CEI-100 I/O Connector Pin Assignments                           | 34 |

| Table 32. Typical Discrete Input Application                              | 38 |

| Table 33. CEI-220 Discrete Input Operating Modes Specification            | 38 |

| Table 34. Programming Examples                                            |    |

| Table 35. Read Discrete Input (AR_GET_CONFIG) Format                      | 39 |

| Table 36. Discrete Input Operating Modes Specifications                   | 40 |

| Table 37. Discrete Output Specifications                                  | 41 |

| Table 38. CEI-200 Buffer Size Table                                       | 55 |

| Table 39. CEI-x20 Family Features                                         | 56 |

| Table 40. ARINC 429 Receive buffer                             | 99  |

|----------------------------------------------------------------|-----|

| Table 41. ARINC 573/717 Receive Buffer                         | 99  |

| Table 42. CSDB Receive Buffer                                  | 100 |

| Table 43. ARINC 573/717 Transmit Buffer                        | 122 |

| Table 44. CSDB Transmit Buffer                                 | 123 |

| Table 45. Typical CSDB Message Lengths                         | 123 |

| Table 46. Supported Concurrency Modes                          | 138 |

| Table 47. Control Word Format                                  | 161 |

| Table 48. Calculating a Clock-Scaling Factor                   | 167 |

| Table 49. CEI-220 DAC Register Scale Factors                   | 175 |

| Table 50. CEI-520/520A DAC Register Scale Factors              | 175 |

| Table 51. DAC Register Functions and Scaling Factors (CEI-620) | 176 |

| Table 52. DAC Register Functions and Scaling Factors (CEI-820) | 176 |

1

# Introduction

#### **Features**

The CEI-100, CEI-200, CEI-220, CEI-420, CEI-420A, CEI-520, CEI-520A, CEI-620, CEI-820, and CEI-820TX are intelligent interfaces between multiple ARINC-429/575 data buses and a compatible host computer. The CEI-100, CEI-200, and the CEI-220 are ISA-bus interface boards. The CEI-420 interfaces with the host using the PC/104 bus. The CEI-420A uses the PC/104 bus and includes a PC/104*Plus* pass-through connector. The CEI-520 (5V-only) and CEI-520A (3.3V and 5V) interface with the host using the 33 MHz PCI Revision 2.1 bus specification. The CEI-620 interfaces with the host using the CompactPCI bus specification. The CEI-820/820TX interfaces with the host using the PCI Mezzanine Card (PMC) bus specification.

The CEI-100, CEI-200, and CEI-x20 devices support ARINC-429/575 data buses. The CEI-220, CEI-420, CEI-420A, CEI-520, CEI-520A, CEI-620, and CEI-820 can also support other protocols including CSDB, ARINC 561, ARINC 568, and ARINC 573/717. Each of these boards has its own processor for interface control, data formatting, filtering, and time tagging. They have substantial dual-port RAM for buffering of data. The boards are powerful enough to support all of their channels running at maximum theoretical throughput simultaneously. The hardware buffering mechanisms guarantee valid data transfer between the ARINC buses and user programs. Powerful, easy-to-use application software and user interface libraries support the boards.

The distribution CD-ROM, available for most configurations of the hardware, contains a rich, programming toolkit. CEI-SW is the software distribution for the CEI-100 and CEI-200, and CEI-x20-SW is the software distribution for the CEI-220, CEI-420, CEI-420A, CEI-520, CEI-520A, CEI-620, CEI-820, and CEI-820TX.

The CEI-x20-SW distribution contains device drivers for Linux, VxWorks, and Windows NT/XP/Vista/Server 2008/7/8.0/8.1/Server 2012/10 (note

Introduction Hardware Specifications

that the only Windows platforms supported by the CEI-220 and CEI-420/420A are Windows NT and 32-bit XP). The distribution includes source code for many sample programs, supporting ANSI C, C#.NET, Linux, VxWorks, and Visual Basic (VB6 and VB.NET). A LabWindows CVI function panel and sample program are also provided.

BusTools/ARINC, our Windows-based ARINC data bus analysis and simulation software, is available to control any of these products (except the CEI-100, CEI-200, CEI-820, and CEI-820TX). Visit our web site for additional information or to download demo software.

## Hardware Specifications

This section shows hardware specifications for the CEI-100, CEI-200, CEI-220, CEI-420, CEI-420A, CEI-520, CEI-520A, CEI-620, CEI-820, and CEI-820TX.

Table 1. Hardware Specifications

| Feature                                      | CEI-100             | CEI-200                                | CEI-220                                                    | CEI-420                                                    | CEI-420A                                                                  | CEI-520/520A                                                             | CEI-620             | CEI-820                                | CEI-820TX                              |

|----------------------------------------------|---------------------|----------------------------------------|------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------|----------------------------------------|----------------------------------------|

| Host Bus<br>Interface                        | 8 bit ISA           | 16 bit ISA                             | 16 bit ISA                                                 | 16 bit PC/104                                              | 16 bit PC/104<br>with optional<br>PC/104plus<br>pass through<br>connector | (CEI-520)<br>5V PCI (32-bit)<br>(CEI-520A)<br>3.3V or 5V PCI<br>(32-bit) | 5V cPCI<br>(32-bit) | 3.3V or 5V<br>PMC (32-bit)             | 3.3V or 5V<br>PMC (32-bit)             |

| Dual Port RAM                                | 4K or<br>8K bytes   | 16K or 32K                             | 64K bytes                                                  | 64K bytes                                                  | 64K bytes                                                                 | 512K bytes                                                               | 512K bytes          | 1M bytes                               | 2M bytes                               |

| Transmit<br>Channels                         | 1                   | Up to 4                                | Up to 12                                                   | Up to 8                                                    | Up to 8                                                                   | Up to 16                                                                 | Up to 16            | Up to 8                                | Up to 32                               |

| Receive<br>Channels                          | 2                   | Up to 8                                | Up to 12                                                   | Up to 8                                                    | Up to 8                                                                   | Up to 16                                                                 | Up to 16            | Up to 8                                | 1                                      |

| ARINC<br>Transmit Bit<br>Rates               | 12.5 or 100<br>Kbs  | 12.5 or 100 Kbs<br>or<br>programmable  | 12.5 or 100<br>Kbs                                         | 12.5 or 100<br>Kbs                                         | 12.5 or 100<br>Kbs                                                        | 12.5 or 100 Kbs                                                          | 12.5 or 100<br>Kbs  | 12.5 or 100 Kbs<br>or<br>programmable  | 12.5 or 100 Kbs<br>or<br>programmable  |

| ARINC Receive<br>Low Speed                   | 10.4 to 15.6<br>Kbs | 10.4 to 15.6<br>Kbs or<br>programmable | 10.4 to 15.6<br>Kbs                                        | 10.4 to 15.6<br>Kbs                                        | 10.4 to 15.6<br>Kbs                                                       | 10.4 to 15.6 Kbs                                                         | 10.4 to 15.6<br>Kbs | 10.4 to 15.6<br>Kbs or<br>programmable | 10.4 to 15.6<br>Kbs or<br>programmable |

| ARINC Receive<br>High Speed                  | 83 to 125 Kbs       | 83 to 125 Kbs<br>or<br>programmable    | 83 to 125 Kbs                                              | 83 to 125 Kbs                                              | 83 to 125 Kbs                                                             | 83 to 125 Kbs                                                            | 83 to 125<br>Kbs    | 83 to 125 Kbs<br>or<br>programmable    | 83 to 125 Kbs<br>or<br>programmable    |

| ARINC<br>Transmit Slew<br>Rate<br>Adjustment | Manual              | Manual                                 | Automatic                                                  | Automatic                                                  | Automatic                                                                 | Automatic                                                                | Automatic           | Automatic                              | Automatic                              |

| Memory<br>Footprint<br>Required              | 4K or 8K bytes      | 32K bytes                              | 4K bytes<br>(paged access<br>by host to full<br>64K bytes) | 4K bytes<br>(paged access<br>by host to full<br>64K bytes) | 4K bytes<br>(paged access<br>by host to full<br>64K bytes)                | 16M byte                                                                 | 16M byte            | 16M byte                               | 16M byte                               |

| I/O port<br>address<br>required              | Yes                 | Yes                                    | No                                                         | No                                                         | No                                                                        | No                                                                       | No                  | No                                     | No                                     |

Introduction Hardware Specifications

| Feature                               | CEI-100                        | CEI-200                        | CEI-220                                                 | CEI-420                                     | CEI-420A                                                                                                        | CEI-520/520A                                                       | CEI-620                                                                                     | CEI-820                                                                                                       | CEI-820TX                             |

|---------------------------------------|--------------------------------|--------------------------------|---------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------|

| On-board<br>Processor                 | 8-bit 80C88<br>@ 5 MHz         | 16-bit 80C186<br>@ 16 MHz      | 32-bit 80960<br>@ 12 MHz                                | 32-bit 80960<br>@ 12 MHz                    | 32-bit 80960<br>@ 16 MHz                                                                                        | 32-bit 80960 @<br>100 MHz                                          | 32-bit 80960<br>@ 100 MHz                                                                   | 32-bit 80960<br>@ 100 MHz                                                                                     | 32-bit 80960<br>@ 100 MHz             |

| Discrete Inputs                       | None                           | None                           | 4 universal<br>with software<br>adjustable<br>threshold | 8,<br>ground/open,<br>low/high,<br>TTL/CMOS | Up to 16,<br>ground/open,<br>low/high,<br>TTL/CMOS<br>(8 share the<br>same lines as<br>the discrete<br>outputs) | Up to 16,<br>ground/open,<br>low/high,<br>TTL/CMOS                 | Up to 16,<br>ground/open<br>, low/high,<br>TTL/CMOS                                         | Up to 16,<br>ground/open,<br>low/high,<br>TTL/CMOS<br>(share the<br>same lines as<br>the discrete<br>outputs) | None                                  |

| Discrete<br>Outputs                   | None                           | None                           | 4<br>Open/Ground,<br>.5 amp max.                        | 8<br>Open/Ground,<br>.5 amp max.            | Up to 8<br>Open/Ground,<br>.5 amp max.<br>(share the<br>same lines as<br>discrete<br>inputs 9-16)               | Up to 16<br>Open/Ground, .5<br>amp max.                            | Up to 16<br>Open/Groun<br>d, .5 amp<br>max.                                                 | Up to 16<br>Open/Ground,<br>.5 amp max.<br>(share the<br>same lines as<br>the discrete<br>inputs)             | None                                  |

| Variable ARINC receive threshold      | No                             | No                             | Yes - software<br>adjustable<br>from 0 to 25<br>Vpp     | No                                          | No                                                                                                              | Yes                                                                | Yes                                                                                         | Yes                                                                                                           | No                                    |

| Variable ARINC<br>transmit<br>voltage | No                             | No                             | Yes - software<br>adjustable<br>from 0 to 10<br>Vpp     | No                                          | No                                                                                                              | Yes - software<br>adjustable from<br>0 to 10 Vpp - all<br>channels | Yes -<br>software<br>adjustable<br>from 0 to 10<br>Vpp -<br>channels 1<br>through 4<br>only | No                                                                                                            | No                                    |

| Power                                 | 2 watts                        | 6 watts                        | 5 watts                                                 | 3 watts                                     | 3 watts                                                                                                         | 7 watts                                                            | 7 watts                                                                                     | 5 watts                                                                                                       | 7 watts                               |

| ARINC<br>Connector(s)                 | 15 pin female<br>"D" connector | 25 pin female<br>"D" connector | 37 pin "D" (1<br>male and 1<br>female)                  | 40 pin and 20<br>pin IDC                    | 40 pin and 20<br>pin IDC                                                                                        | 68 pin SCSI-3<br>and 40 pin IDC                                    | Two 50 pin<br>Champ<br>0.8mm<br>connectors                                                  | 50 pin Champ<br>0.8mm and<br>P14<br>mezzanine                                                                 | 68 pin SCSI-3<br>and P14<br>mezzanine |

# Installation

#### Overview

Software for these products is distributed on CD-ROM. Updates are available on our web site (www.abaco.com/products/avionics).

#### Note:

When installing a CEI-x20 device under Windows, you must install the software before installing the hardware. When installing a CEI-x20 device under Linux, you must install the hardware first.

It is recommended that you examine your system for resource conflicts before installation. When upgrading from an older version, uninstall the previous version of software before installing the new version. Software installation instructions are provided in the Quick Start Guide.

# Installing the Board

Before handling a circuit board, allocate a static free workstation and be sure you are properly grounded. Then remove the board from its static protective bag and inspect it.

#### Caution:

Be aware of the potential for damage to this (and any other) circuit card by static electricity. The board is shipped in a protective, anti-static bag and must be handled according to static prevention procedures. Failure to protect the board from static electricity may result in damage to the board. Such damage may be evident immediately or not for years.

Each board is tested and shipped with the default settings described in this manual. Resource conflicts or application requirements may cause you to make adjustments to the default board settings. For this reason, the following sections provide detailed information about features that may be configured on these boards through DIP-switches and jumper settings.

## Setting the ISA Bus Base Address

The base memory address of the board defines the base segment address of the dual-port memory. The host computer sees the board at this address. The default segment address for the CEI-100 is 0xCC00 (hex), which translates to a physical address of 0xCC000. The default segment address for the CEI-200, CEI-220, CEI-420, and CEI-420A is 0xD000 (hex), which translates to a physical address of 0xD0000.

Make a note of the board address you program so you can make it known to the software. Use the physical address when installing the ISA hardware under VxWorks, Linux, or Windows NT or 32-bit XP. The address for both boards is switch-selectable within the upper memory block (UMB) area of the IBM PC. This is the address space between 640K and 1024K. Since other devices also use this space, select an area not already being used. Many common software programs such as Norton Utilities and Quarterdeck Manifest can help you identify software on your system. The default addresses were chosen to minimize conflict within a typical system; however, you may need to make a change.

Avoid selecting any addresses that directly conflict with other installed devices. The ARINC memory address space must not directly overlap with any other devices. In addition, you must avoid any indirect conflicts. This occurs when a 16-bit memory interface (such as the CEI-200/220/420/420A) is placed in the same 128 Kbytes region (i.e., segment address ranges: A000-C000 or C000-E000 or E000-10000) as an 8-bit memory interface. This is due to an inherent architectural limitation of the IBM PC.

Finally, when selecting a base memory address, be aware of a potential conflict with expanded memory managers (e.g., EMM386, QEMM386) also using the UMB. You can avoid this problem by configuring the memory manager to exclude the ARINC memory from its list of available mapping regions. For example, when starting EMM386, use the command line switch: X=D000-D7FF for a CEI-200 at the default segment address of D000. See your memory manager documentation for a complete discussion of these switches.

The base I/O address is also switch-selectable. I/O commands are used to control the CEI-100 and CEI-200 boards, while the CEI-220, CEI-420, and CEI-420A boards don't use a base I/O address.

Both the base memory and base I/O address are selected through a single DIP-switch located on each board next to the end panel. Only certain address bits are selectable. All other bits are fixed as shown. When a switch is OFF, the corresponding address bit is a one and when it is ON the corresponding address bit is a zero.

### ARINC 429 Slew Rate Configuration for CEI-100/CEI-200

Some jumpers may be installed on the CEI-100 and CEI-200 boards to allow proper selection of ARINC transmission slew rate. On CEI-x20 devices, *slew rate* selection is automatic. The slew rate refers to the rise and fall times for the ARINC signals.

To configure the slew rate for low-speed transmission (12.5K bps) for a channel, install a pair of jumpers to connect the proper capacitance. The bit rate (100K or 12.5K) is software-programmable. As a rule, it is possible to run at either bit rate without the jumpers in place. However, to meet the ARINC 429 specification exactly for low speed slew rate, you must install the appropriate jumpers.

Transmitting at low speed without the jumpers installed causes the ARINC waveform to be squarer than the specification defines. However, most ARINC 429 receivers can tolerate this. Transmitting at high speed with the jumpers in place makes the waveform so far out of specification that it is not useable.

## Configuring the CEI-820TX

This section provides configuration information for the CEI-820TX.

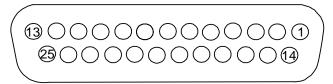

#### CEI-820TX Input/Output Connector Pin Out

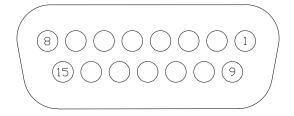

To couple the CEI-820TX to ARINC devices, a front bezel connector (P1) and a mezzanine PMC connector (P14) are provided. The front bezel connector is a 68-pin SCSI connector (AMP/Tyco part number 787394-7).

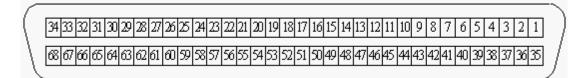

Figure 1. 68-pin Receptacle Connector (SCSI-3 compatible, view facing receptacles)

Table 2. CEI-820TX Connector Definitions (P1 and P14)

| Signal | P1 Pin | P14 Pin | Signal | P1 Pin | P14 Pin |

|--------|--------|---------|--------|--------|---------|

| RX1A   | 1      |         | RX1B   | 35     |         |

| TX1A   | 2      | 1       | TX1B   | 36     | 2       |

| TX2A   | 3      | 3       | TX2B   | 37     | 4       |

| TX3A   | 4      | 5       | TX3B   | 38     | 6       |

| TX4A   | 5      | 7       | TX4B   | 39     | 8       |

| TX5A   | 6      | 9       | TX5B   | 40     | 10      |

| TX6A   | 7      | 11      | TX6B   | 41     | 12      |

| TX7A   | 8      | 13      | TX7B   | 42     | 14      |

| TX8A   | 9      | 15      | TX8B   | 43     | 16      |

| TX9A   | 10     | 17      | TX9B   | 44     | 18      |

| TX10A  | 11     | 19      | TX10B  | 45     | 20      |

| TX11A  | 12     | 21      | TX11B  | 46     | 22      |

| TX12A  | 13     | 23      | TX12B  | 47     | 24      |

| TX13A  | 14     | 25      | TX13B  | 48     | 26      |

| TX14A  | 15     | 27      | TX14B  | 49     | 28      |

| TX15A  | 16     | 29      | TX15B  | 50     | 30      |

| TX16A  | 17     | 31      | TX16B  | 51     | 32      |

| Ground | 18     |         | Ground | 52     |         |

| TX17A  | 19     | 33      | TX17B  | 53     | 34      |

| TX18A  | 20     | 35      | TX18B  | 54     | 36      |

| TX19A  | 21     | 37      | TX19B  | 55     | 38      |

| TX20A  | 22     | 39      | TX20B  | 56     | 40      |

| TX21A  | 23     | 41      | TX21B  | 57     | 42      |

| TX22A  | 24     | 43      | TX22B  | 58     | 44      |

| TX23A  | 25     | 45      | TX23B  | 59     | 46      |

| TX24A  | 26     | 47      | TX24B  | 60     | 48      |

| TX25A  | 27     | 49      | TX25B  | 61     | 50      |

| TX26A  | 28     | 51      | TX26B  | 62     | 52      |

| TX27A  | 29     | 53      | TX27B  | 63     | 54      |

| TX28A  | 30     | 55      | TX28B  | 64     | 56      |

| TX29A  | 31     | 57      | TX29B  | 65     | 58      |

| TX30A  | 32     | 59      | TX30B  | 66     | 60      |

| TX31A  | 33     | 61      | TX31B  | 67     | 62      |

| TX32A  | 34     | 63      | TX32B  | 68     | 64      |

Notes:

Signal pairs "TXnA"/"TXnB" and "RXnA"/"RXnB" are the positive and negative lines of an ARINC differential pair.

The ARINC receive channel is available only on the front bezel connector (P1). Configurations with less than 32 transmit channels use the first (lowest number) defined channels.

One source for a breakout adapter for a 68-pin SCSI connector is Dynamic Engineering (www.dyneng.com). A three-foot SCSI cable, part number HDECable68-1, is available as well as a pass-through breakout adapter with screw terminals, part number HDEterm68. Some standard 68-pin SCSI cables built for computer peripheral use do not include wires for all 68 pins.

# Configuring the CEI-820

This section provides configuration information for the CEI-820.

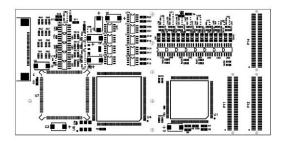

### CEI-820 Outline Drawing

Figure 2. CEI-820 Outline Drawing

#### CEI-820 Input/Output Connector Pin Out

To couple the CEI-820 to ARINC devices and discrete inputs and outputs, a front panel connector (P1) and a mezzanine PMC connector (P14) are provided.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

Figure 3. 50-pin P1 connector (AMP Champ 0.8 mm receptacle connectors - AMP part number 787096-1)

Table 3. CEI-820-xx and CEI-820-xxJ Connector Definitions (P1 and P14)

| Signal | P1 Pin | P14 Pin | Signal | P1 Pin | P14 Pin |

|--------|--------|---------|--------|--------|---------|

| TX8A   | 1      | 9       | TX8B   | 26     | 10      |

| TX7A   | 2      | 11      | TX7B   | 27     | 12      |

| TX6A   | 3      | 13      | TX6B   | 28     | 14      |

| TX5A   | 4      | 15      | TX5B   | 29     | 16      |

| TX4A   | 5      | 17      | TX4B   | 30     | 18      |

| TX3A   | 6      | 19      | TX3B   | 31     | 20      |

| TX2A   | 7      | 21      | TX2B   | 32     | 22      |

| TX1A   | 8      | 23      | TX1B   | 33     | 24      |

| RX8A   | 9      | 25      | RX8B   | 34     | 26      |

| Signal                   | P1 Pin   | P14 Pin | Signal                   | P1 Pin   | P14 Pin |

|--------------------------|----------|---------|--------------------------|----------|---------|

| RX7A                     | 10       | 27      | RX7B                     | 35       | 28      |

| RX6A                     | 11       | 29      | RX6B                     | 36       | 30      |

| RX5A                     | 12       | 31      | RX5B                     | 37       | 32      |

| RX4A                     | 13       | 33      | RX4B                     | 38       | 34      |

| RX3A                     | 14       | 35      | RX3B                     | 39       | 36      |

| RX2A                     | 15       | 37      | RX2B                     | 40       | 38      |

| RX1A                     | 16       | 39      | RX1B                     | 41       | 40      |

| GND                      | 17,19,23 | 41,47   | GND                      | 42,44,48 | 42,48   |

| Discrete Input/Output 1  | 20       | 49      | Discrete Input/Output 2  | 45       | 50      |

| Discrete Input/Output 3  | 21       | 51      | Discrete Input/Output 4  | 46       | 52      |

| Discrete Input/Output 5  | 24       | 53      | Discrete Input/Output 6  | 49       | 54      |

| Discrete Input/Output 7  | 25       | 55      | Discrete Input/Output 8  | 50       | 56      |

| Discrete Input/Output 9  |          | 57      | Discrete Input/Output 10 |          | 58      |

| Discrete Input/Output 11 |          | 59      | Discrete Input/Output 12 |          | 60      |

| Discrete Input/Output 13 |          | 61      | Discrete Input/Output 14 |          | 62      |

| Discrete Input/Output 15 |          | 63      | Discrete Input/Output 16 |          | 64      |

#### Notes:

P1 is a 50-pin, Champ 0.8 mm receptacle connector. The AMP part number is 787096-1.

Signal pairs "TXnA"/"TXnB" and "RXnA"/"RXnB" are the positive and negative lines of an ARINC differential pair.

The discrete inputs and outputs share the same lines. There are a total of 16 bi-directional discretes on the CEI-820, each of which can be treated as an input or an output. For example, you may choose to use discretes 1-4 as inputs and 5-16 as outputs.

Discrete inputs/outputs 9-16 are available only on the mezzanine connector (P14).

Optional, non-ARINC 429 protocols are assigned to the following channels for configurations that support them:

| Protocol                                         | Receive channels | Transmit channels                                                                     |

|--------------------------------------------------|------------------|---------------------------------------------------------------------------------------|

| ARINC 573/717<br>Bipolar return-to-zero encoding | #1               | #1                                                                                    |

| ARINC 573/717<br>Harvard bi-phase encoding       | #1               | #1 Since they use the same pins, BPRZ & HBP encoding cannot be used at the same time. |

| ARINC 561                                        | See Table 4.     | None                                                                                  |

Table 4. CEI-820-44L Connector Definitions (P1 and P14)

| Signal                    | P1 Pin   | P14 Pin | Signal                    | P1 Pin   | P14 Pin |

|---------------------------|----------|---------|---------------------------|----------|---------|

| reserved – do not connect | 1        | 9       | reserved – do not connect | 26       | 10      |

| reserved – do not connect | 2        | 11      | reserved – do not connect | 27       | 12      |

| reserved – do not connect | 3        | 13      | reserved – do not connect | 28       | 14      |

| reserved – do not connect | 4        | 15      | reserved – do not connect | 29       | 16      |

| ARINC 429 TX4A            | 5        | 17      | ARINC 429 TX4B            | 30       | 18      |

| ARINC 429 TX3A            | 6        | 19      | ARINC 429 TX3B            | 31       | 20      |

| ARINC 429 TX2A            | 7        | 21      | ARINC 429 TX2B            | 32       | 22      |

| ARINC 429 TX1A            | 8        | 23      | ARINC 429 TX1B            | 33       | 24      |

| reserved – do not connect | 9        | 25      | reserved – do not connect | 34       | 26      |

| ARINC 561 RX SYNC+        | 10       | 27      | ARINC 561 RX SYNC-        | 35       | 28      |

| ARINC 561 RX DATA+        | 11       | 29      | ARINC 561 RX DATA-        | 36       | 30      |

| ARINC 561 RX CLK+         | 12       | 31      | ARINC 561 RX CLK-         | 37       | 32      |

| ARINC 429 RX4A            | 13       | 33      | ARINC 429 RX4B            | 38       | 34      |

| ARINC 429 RX3A            | 14       | 35      | ARINC 429 RX3B            | 39       | 36      |

| ARINC 429 RX2A            | 15       | 37      | ARINC 429 RX2B            | 40       | 38      |

| ARINC 429 RX1A            | 16       | 39      | ARINC 429 RX1B            | 41       | 40      |

| GND                       | 17,19,23 | 41,47   | GND                       | 42,44,48 | 42,48   |

| Discrete Input/Output 1   | 20       | 49      | Discrete Input/Output 2   | 45       | 50      |

| Discrete Input/Output 3   | 21       | 51      | Discrete Input/Output 4   | 46       | 52      |

| Discrete Input/Output 5   | 24       | 53      | Discrete Input/Output 6   | 49       | 54      |

| Discrete Input/Output 7   | 25       | 55      | Discrete Input/Output 8   | 50       | 56      |

| Discrete Input/Output 9   |          | 57      | Discrete Input/Output 10  |          | 58      |

| Discrete Input/Output 11  |          | 59      | Discrete Input/Output 12  |          | 60      |

| Discrete Input/Output 13  |          | 61      | Discrete Input/Output 14  |          | 62      |

| Discrete Input/Output 15  |          | 63      | Discrete Input/Output 16  |          | 64      |

For external wrap, connect each transmit signal to the corresponding receive signal (e.g., TX1+ to RX1+, TX1- to RX1-, etc.). Also, wrap discretes 1-4 to discretes 5-8 (e.g., discrete 1 to discrete 5, discrete 2 to discrete 6, etc.) and discretes 9-12 to discretes 13-16.

The mating connector for P1 is shown below:

Table 5. Mating Connector for P1

| Manufacturer:        | AMP      |

|----------------------|----------|

| Connector:           | 787131-1 |

| Metal backshell kit: | 787233-1 |

| Wire:                | 30 AWG   |

## CEI-820 Transition Cable Pin Out

Table 6 defines the CONCEI-620 cable provided with each CEI-820. The cable is approximately three feet in length. There is a Champ 0.8mm 50-pin connector (AMP p/n 787131-1) at one end. The other end is a standard subminiature-D, 50-pin plug connector (AMP p/n 205212-3 or equivalent).

Table 6. CEI-820 Transition Cable Pin Out

| P1 | D50 | Signal                  | P1 | D50 | Signal                  |

|----|-----|-------------------------|----|-----|-------------------------|

| 25 | 17  | Discrete Input/Output 7 | 50 | 50  | Discrete Input/Output 8 |

| 24 | 49  | Discrete Input/Output 5 | 49 | 33  | Discrete Input/Output 6 |

| 23 | 32  | GND                     | 48 | 16  | GND                     |

| 21 | 47  | Discrete Input/Output 3 | 46 | 31  | Discrete Input/Output 4 |

| 20 | 30  | Discrete Input/Output 1 | 45 | 14  | Discrete Input/Output 2 |

| 19 | 13  | GND                     | 44 | 46  | GND                     |

| 17 | 28  | GND                     | 42 | 12  | GND                     |

| 16 | 11  | RX1A                    | 41 | 44  | RX1B                    |

| 15 | 43  | RX2A                    | 40 | 27  | RX2B                    |

| 14 | 26  | RX3A                    | 39 | 10  | RX3B                    |

| 13 | 9   | RX4A                    | 38 | 42  | RX4B                    |

| 12 | 41  | RX5A                    | 37 | 25  | RX5B                    |

| 11 | 24  | RX6A                    | 36 | 8   | RX6B                    |

| 10 | 7   | RX7A                    | 35 | 40  | RX7B                    |

| 9  | 39  | RX8A                    | 34 | 23  | RX8B                    |

| 8  | 22  | TX1A                    | 33 | 6   | TX1B                    |

| 7  | 5   | TX2A                    | 32 | 38  | TX2B                    |

| 6  | 37  | TX3A                    | 31 | 21  | TX3B                    |

| 5  | 20  | TX4A                    | 30 | 4   | TX4B                    |

| 4  | 3   | TX5A                    | 29 | 36  | TX5B                    |

| 3  | 35  | TX6A                    | 28 | 19  | TX6B                    |

| 2  | 18  | TX7A                    | 27 | 2   | ТХ7В                    |

| 1  | 1   | TX8A                    | 26 | 34  | TX8B                    |

# Configuring the CEI-620

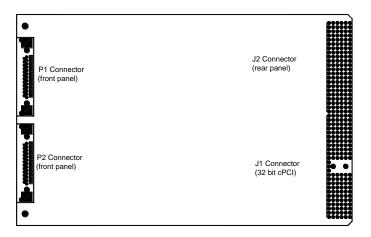

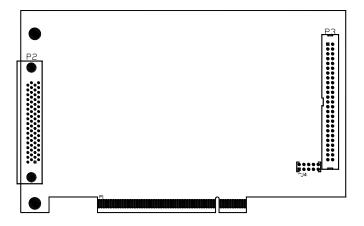

This section provides configuration information for the CEI-620.

## CEI-620 Outline Drawing

Figure 4. CEI-620 Outline Drawing

## CEI-620 Input/Output Connector Pin Out

Use the cPCI J2 back plane connector to couple the CEI-620 to ARINC devices and discrete inputs and outputs for rear panel configurations. For front panel configurations, two connectors, P1 and P2, are provided. Each connector is identical.

| Table 7 CFI-620 R | Rear Panel Input/Output | Connector Definition |

|-------------------|-------------------------|----------------------|

|    | Row a              | Row b              | Row c             | Row d             | Row e             |

|----|--------------------|--------------------|-------------------|-------------------|-------------------|

| 22 | Discrete Output 16 | Discrete Output 12 | Discrete Output 9 | Discrete Output 6 | Discrete Output 3 |

| 21 | Discrete Output 15 | Discrete Output 11 | Discrete Output 8 | Discrete Output 5 | Discrete Output 2 |

| 20 | Discrete Output 14 | Discrete Output 10 | Discrete Output 7 | Discrete Output 4 | Discrete Output 1 |

| 19 | Discrete Output 13 | Discrete Input 12  | Discrete Input 9  | Discrete Input 6  | Discrete Input 3  |

| 18 | Discrete Input 16  | Discrete Input 11  | Discrete Input 8  | Discrete Input 5  | Discrete Input 2  |

| 17 | Discrete Input 15  | Discrete Input 10  | Discrete Input 7  | Discrete Input 4  | Discrete Input 1  |

| 16 | Discrete Input 14  | RX16B              | RX16A             | RX8B              | RX8A              |

| 15 | Discrete Input 13  | RX15B              | RX15A             | RX7B              | RX7A              |

| 14 |                    | RX14B              | RX14A             | RX6B              | RX6A              |

|    | Row a | Row b | Row c | Row d | Row e |

|----|-------|-------|-------|-------|-------|

| 13 |       | RX13B | RX13A | RX5B  | RX5A  |

| 12 |       | RX12B | RX12A | RX4B  | RX4A  |

| 11 |       | RX11B | RX11A | RX3B  | RX3A  |

| 10 |       | RX10B | RX10A | RX2B  | RX2A  |

| 9  |       | RX9B  | RX9A  | RX1B  | RX1A  |

| 8  |       | TX16B | TX16A | TX8B  | TX8A  |

| 7  |       | TX15B | TX15A | ТХ7В  | TX7A  |

| 6  |       | TX14B | TX14A | TX6B  | TX6A  |

| 5  |       | TX13B | TX13A | TX5B  | TX5A  |

| 4  |       | TX12B | TX12A | TX4B  | TX4A  |

| 3  |       | TX11B | TX11A | TX3B  | TX3A  |

| 2  |       | TX10B | TX10A | TX2B  | TX2A  |

| 1  |       | TX9B  | TX9A  | TX1B  | TX1A  |

#### Notes:

Per the compact PCI specification, row "A" is closest to the edge of the circuit board and Row "E" is furthest from the edge of the circuit board.

Signal pairs "TXnA"/"TXnB" and "RXnA"/"RXnB" are the positive and negative lines of an ARINC differential pair.

Optional, non-ARINC 429 protocols are assigned to the following channels for configurations that support them:

| Protocol                                         | Receive channel(s) | Transmit channel(s)                  |

|--------------------------------------------------|--------------------|--------------------------------------|

| ARINC 573/717<br>Bipolar return-to-zero encoding | #1                 | #1<br>TX+: pin E1<br>TX-: pin D1     |

| ARINC 573/717<br>Harvard bi-phase encoding       | #1                 | #1, #2<br>TX+: pin E1<br>TX-: pin E2 |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

Figure 5. 50-pin Connector (AMP Champ 0.8 mm Receptacle Connectors - AMP Part Number 787096-1)

Table 8. Front View – ARINC 429 Input/Output Connector (P1 and P2)

| P1 Connector |                   |     | P2 Connector      |     |                    |     |                    |

|--------------|-------------------|-----|-------------------|-----|--------------------|-----|--------------------|

| Pin          | Signal            | Pin | Signal            | Pin | Signal             | Pin | Signal             |

| 25           | Discrete Output 7 | 50  | Discrete Output 8 | 25  | Discrete Output 15 | 50  | Discrete Output 16 |

| 24           | Discrete Output 5 | 49  | Discrete Output 6 | 24  | Discrete Output 13 | 49  | Discrete Output 14 |

| 23           | Discrete Output 3 | 48  | Discrete Output 4 | 23  | Discrete Output 11 | 48  | Discrete Output 12 |

| 22           | Discrete Output 1 | 47  | Discrete Output 2 | 22  | Discrete Output 9  | 47  | Discrete Output 10 |

| 21           | Discrete Input 7  | 46  | Discrete Input 8  | 21  | Discrete Input 15  | 46  | Discrete Input 16  |

| 20           | Discrete Input 5  | 45  | Discrete Input 6  | 20  | Discrete Input 13  | 45  | Discrete Input 14  |

| 19           | Discrete Input 3  | 44  | Discrete Input 4  | 19  | Discrete Input 11  | 44  | Discrete Input 12  |

| 18           | Discrete Input 1  | 43  | Discrete Input 2  | 18  | Discrete Input 9   | 43  | Discrete Input 10  |

| 17           | GND               | 42  | GND               | 17  | GND                | 42  | GND                |

| 16           | RX8A              | 41  | RX8B              | 16  | RX16A              | 41  | RX16B              |

| 15           | RX7A              | 40  | RX7B              | 15  | RX15A              | 40  | RX15B              |

| 14           | RX6A              | 39  | RX6B              | 14  | RX14A              | 39  | RX14B              |

| 13           | RX5A              | 38  | RX5B              | 13  | RX13A              | 38  | RX13B              |

| 12           | RX4A              | 37  | RX4B              | 12  | RX12A              | 37  | RX12B              |

| 11           | RX3A              | 36  | RX3B              | 11  | RX11A              | 36  | RX11B              |

| 10           | RX2A              | 35  | RX2B              | 10  | RX10A              | 35  | RX10B              |

| 9            | RX1A              | 34  | RX1B              | 9   | RX9A               | 34  | RX9B               |

| 8            | TX8A              | 33  | TX8B              | 8   | TX16A              | 33  | TX16B              |

| 7            | TX7A              | 32  | TX7B              | 7   | TX15A              | 32  | TX15B              |

| 6            | TX6A              | 31  | TX6B              | 6   | TX14A              | 31  | TX14B              |

| 5            | TX5A              | 30  | TX5B              | 5   | TX13A              | 30  | TX13B              |

| 4            | TX4A              | 29  | TX4B              | 4   | TX12A              | 29  | TX12B              |

| 3            | TX3A              | 28  | ТХЗВ              | 3   | TX11A              | 28  | TX11B              |

| 2            | TX2A              | 27  | TX2B              | 2   | TX10A              | 27  | TX10B              |

| 1            | TX1A              | 26  | TX1B              | 1   | TX9A               | 26  | TX9B               |

Notes:

P1 and P2 are 50-pin, Champ 0.8 mm receptacle connectors. They are AMP part number 787096-1.

Signal pairs "TXnA"/"TXnB" and "RXnA"/"RXnB" are the positive and negative lines of an ARINC differential pair.

Optional, non-ARINC 429 protocols are assigned to the following channels for configurations that support them:

| Protocol                                         | Receive channel(s) | Transmit channel(s)                      |

|--------------------------------------------------|--------------------|------------------------------------------|

| ARINC 573/717<br>Bipolar return-to-zero encoding | #1                 | #1<br>TX+: pin P1-1<br>TX-: pin P1-26    |

| ARINC 573/717<br>Harvard bi-phase encoding       | #1                 | #1, #2<br>TX+: pin P1-1<br>TX-: pin P1-2 |

For external wrap, connect each transmit signal to the corresponding receive signal (e.g., TX1+ to RX1+, TX1- to RX1-, etc.) In addition, connect each discrete output to the corresponding discrete input.

The mating connectors for P1 and P2 are as shown in Table 9:

Table 9. Mating Connectors for P1 and P2

| Manufacturer:        | AMP      |

|----------------------|----------|

| Connector:           | 787131-1 |

| Metal backshell kit: | 787233-1 |

| Wire:                | 30 AWG   |

#### CEI-620 Transition Cable Pin Out

Table 10 defines the CONCEI-620 cable provided with each CEI-620. The cable is approximately three feet in length. There is a Champ 0.8mm 50 pin connector (AMP 787131-1) on one end. The other end is a standard subminiature-D, 50-pin plug connector (AMP p/n 205212-3 or equivalent).

Table 10. CEI-620 Transition Cable Pin Out

|    | P1 Conne | ector             |    | P2 Conne | ector              |  |

|----|----------|-------------------|----|----------|--------------------|--|

| P1 | D50      | Signal            | P2 | D50      | Signal             |  |

| 25 | 17       | Discrete Output 7 | 25 | 17       | Discrete Output 15 |  |

| 24 | 49       | Discrete Output 5 | 24 | 49       | Discrete Output 13 |  |

| 23 | 32       | Discrete Output 3 | 23 | 32       | Discrete Output 11 |  |

| 22 | 15       | Discrete Output 1 | 22 | 15       | Discrete Output 9  |  |

| 21 | 47       | Discrete Input 7  | 21 | 47       | Discrete Input 15  |  |

| 20 | 30       | Discrete Input 5  | 20 | 30       | Discrete Input 13  |  |

| 19 | 13       | Discrete Input 3  | 19 | 13       | Discrete Input 11  |  |

| 18 | 45       | Discrete Input 1  | 18 | 45       | Discrete Input 9   |  |

| 17 | 28       | GND               | 17 | 28       | GND                |  |

|    | P1 Conne | ector             |       |    | P2 Conne | ector              |

|----|----------|-------------------|-------|----|----------|--------------------|

| P1 | D50      | Signal            |       | P2 | D50      | Signal             |

| 16 | 11       | RX8A              |       | 16 | 11       | RX16A              |

| 15 | 43       | RX7A              | 15 43 |    | 43       | RX15A              |

| 14 | 26       | RX6A              |       | 14 | 26       | RX14A              |

| 13 | 9        | RX5A              |       | 13 | 9        | RX13A              |

| 12 | 41       | RX4A              |       | 12 | 41       | RX12A              |

| 11 | 24       | RX3A              |       | 11 | 24       | RX11A              |

| 10 | 7        | RX2A              |       | 10 | 7        | RX10A              |

| 9  | 39       | RX1A              |       | 9  | 39       | RX9A               |

| 8  | 22       | TX8A              |       | 8  | 22       | TX16A              |

| 7  | 5        | TX7A              |       | 7  | 5        | TX15A              |

| 6  | 37       | TX6A              |       | 6  | 37       | TX14A              |

| 5  | 20       | TX5A              |       | 5  | 20       | TX13A              |

| 4  | 3        | TX4A              |       | 4  | 3        | TX12A              |

| 3  | 35       | TX3A              |       | 3  | 35       | TX11A              |

| 2  | 18       | TX2A              |       | 2  | 18       | TX10A              |

| 1  | 1        | TX1A              |       | 1  | 1        | TX9A               |

| 50 | 50       | Discrete Output 8 |       | 50 | 50       | Discrete Output 16 |

| 49 | 33       | Discrete Output 6 |       | 49 | 33       | Discrete Output 14 |

| 48 | 16       | Discrete Output 4 |       | 48 | 16       | Discrete Output 12 |

| 47 | 48       | Discrete Output 2 |       | 47 | 48       | Discrete Output 10 |

| 46 | 31       | Discrete Input 8  |       | 46 | 31       | Discrete Input 16  |

| 45 | 14       | Discrete Input 6  |       | 45 | 14       | Discrete Input 14  |

| 44 | 46       | Discrete Input 4  |       | 44 | 46       | Discrete Input 12  |

| 43 | 29       | Discrete Input 2  |       | 43 | 29       | Discrete Input 10  |

| 42 | 12       | GND               |       | 42 | 12       | GND                |

| 41 | 44       | RX8B              |       | 41 | 44       | RX16B              |

| 40 | 27       | RX7B              |       | 40 | 27       | RX15B              |

| 39 | 10       | RX6B              |       | 39 | 10       | RX14B              |

| 38 | 42       | RX5B              |       | 38 | 42       | RX13B              |

| 37 | 25       | RX4B              |       | 37 | 25       | RX12B              |

| 36 | 8        | RX3B              |       | 36 | 8        | RX11B              |

| 35 | 40       | RX2B              |       | 35 | 40       | RX10B              |

| 34 | 23       | RX1B              |       | 34 | 23       | RX9B               |

| 33 | 6        | TX8B              |       | 33 | 6        | TX16B              |

| 32 | 38       | TX7B              |       | 32 | 38       | TX15B              |

| 31 | 21       | TX6B              |       | 31 | 21       | TX14B              |

|    | P1 Conne | ector  | P2 Connector |     |        |  |  |  |

|----|----------|--------|--------------|-----|--------|--|--|--|

| P1 | D50      | Signal | P2           | D50 | Signal |  |  |  |

| 30 | 4        | TX5B   | 30           | 4   | TX13B  |  |  |  |

| 29 | 36       | TX4B   | 29           | 36  | TX12B  |  |  |  |

| 28 | 19       | TX3B   | 28           | 19  | TX11B  |  |  |  |

| 27 | 2        | TX2B   | 27           | 2   | TX10B  |  |  |  |

| 26 | 34       | TX1B   | 26           | 34  | TX9B   |  |  |  |

# Configuring the CEI-520 and CEI-520A

This section provides configuration information for the CEI-520 and the CEI-520A.

#### CEI-520/520A Outline Drawing

Figure 6. CEI-520/520A Outline Drawing

## CEI-520/520A Input/Output Connector Pin Out

To couple the CEI-520/520A to ARINC devices using the rear panel, the following rear panel connector is provided (AMP/Tyco 787171-1).

Figure 7. 68-pin Receptacle Connector (SCSI-3 compatible with rails and latch blocks, view facing receptacles)

Signal Pin Pin Signal Pin Signal Pin Signal 1 35 52 TX1+ TX1-18 RX1+ RX1-2 TX2+ TX2-19 RX2+ 53 RX2-36 3 TX3+ 37 ТХ3-20 RX3+ 54 RX3-4 21 55 TX4+ 38 TX4-RX4+ RX4-5 TX5+ 39 TX5-22 RX5+ 56 RX5-6 TX6+ 40 TX6-23 RX6+ 57 RX6-7 41 TX7-24 RX7+ 58 RX7-TX7+ 8 +8XT 42 TX8-25 RX8+ 59 RX8-9 TX9+ 43 TX9-26 **GND** 60 **GND** 10 44 27 RX9+ 61 RX9-TX10+ TX10-11 TX11+ 45 TX11-28 RX10+ 62 RX10-12 TX12+ 46 TX12-29 RX11+ 63 RX11-13 TX13+ 47 TX13-30 RX12+ 64 RX12-14 TX14+ TX14-31 RX13+ 65 RX13-48 15 TX15+ 49 TX15-32 RX14+ 66 RX14-16 TX16+ 50 TX16-33 RX15+ 67 RX15-17 GND 51 GND 34 RX16+ 68 RX16-

Table 11. Front View – Standard CEI-520/520A ARINC 429 I/O Connector (P2)

Note:

For external wrap, connect each transmit signal to the corresponding receive signal (e.g. TX1+ to RX1+, TX1- to RX1-, etc.).

Also available are the CEI-520-1208-C/CEI-520A-1208-C (which provide CSDB support) and the CEI-520-xxxx-J/CEI-520A-xxxx-J (which provide ARINC 573/717 support). The P2 connector pinouts for these configurations are shown in the following tables.

Table 12. Front View – CEI-520-1208-C/CEI-520A-1208-C I/O Connector (P2)

| Pin | Signal    | Pin | Signal   | Pin | Signal | Pin | Signal |

|-----|-----------|-----|----------|-----|--------|-----|--------|

| 1   | TX1+      | 35  | TX1-     | 18  | RX1+   | 52  | RX1-   |

| 2   | TX2+      | 36  | TX2-     | 19  | RX2+   | 53  | RX2-   |

| 3   | TX3+      | 37  | TX3-     | 20  | RX3+   | 54  | RX3-   |

| 4   | TX4+      | 38  | TX4-     | 21  | RX4+   | 55  | RX4-   |

| 5   | TX5+      | 39  | TX5-     | 22  | RX5+   | 56  | RX5-   |

| 6   | TX6+      | 40  | TX6-     | 23  | RX6+   | 57  | RX6-   |

| 7   | TX7+      | 41  | TX7-     | 24  | RX7+   | 58  | RX7-   |

| 8   | TX8+      | 42  | TX8-     | 25  | RX8+   | 59  | RX8-   |

| 9   | CSDB TX1+ | 43  | reserved | 26  | GND    | 60  | GND    |

| 10  | CSDB TX1- | 44  | reserved | 27  | RX9+   | 61  | RX9-   |

| Pin | Signal    | Pin | Signal   | Pin | Signal    | Pin | Signal    |

|-----|-----------|-----|----------|-----|-----------|-----|-----------|

| 11  | CSDB TX2+ | 45  | reserved | 28  | RX10+     | 62  | RX10-     |

| 12  | CSDB TX2- | 46  | reserved | 29  | RX11+     | 63  | RX11-     |

| 13  | CSDB TX3+ | 47  | reserved | 30  | RX12+     | 64  | RX12-     |

| 14  | CSDB TX3- | 48  | reserved | 31  | CSDB RX1+ | 65  | CSDB RX1- |

| 15  | CSDB TX4+ | 49  | reserved | 32  | CSDB RX2+ | 66  | CSDB RX2- |

| 16  | CSDB TX4- | 50  | reserved | 33  | CSDB RX3+ | 67  | CSDB RX3- |

| 17  | GND       | 51  | GND      | 34  | CSDB RX4+ | 68  | CSDB RX4- |

Table 13. Front View – CEI-520-xxxx-J/CEI-520A-xxxx-J I/O Connector (P2)

| Pin | Signal                                                | Pin | Signal                    | Pin                   | Signal   | Pin | Signal                                      |

|-----|-------------------------------------------------------|-----|---------------------------|-----------------------|----------|-----|---------------------------------------------|

| 1   | ARINC 573/717<br>BPRZ TX+<br>ARINC 573/717<br>HBP TX+ | 35  | ARINC 573/717<br>BPRZ TX- | 1 18   RX+ (hoth RPR7 |          | 52  | ARINC 573/717<br>RX- (both BPRZ<br>and HBP) |

| 2   | ARINC 573/717<br>HBP TX-                              | 36  | reserved                  | 19                    | reserved | 53  | reserved                                    |

| 3   | TX3+                                                  | 37  | TX3-                      | 20                    | RX3+     | 54  | RX3-                                        |

| 4   | TX4+                                                  | 38  | TX4-                      | 21                    | RX4+     | 55  | RX4-                                        |

| 5   | TX5+                                                  | 39  | TX5-                      | 22                    | RX5+     | 56  | RX5-                                        |

| 6   | TX6+                                                  | 40  | TX6-                      | 23                    | 3 RX6+   |     | RX6-                                        |

| 7   | TX7+                                                  | 41  | TX7-                      | 24                    | RX7+     | 58  | RX7-                                        |

| 8   | TX8+                                                  | 42  | TX8-                      | 25                    | RX8+     | 59  | RX8-                                        |

| 9   | TX9+                                                  | 43  | TX9-                      | 26                    | GND      | 60  | GND                                         |

| 10  | TX10+                                                 | 44  | TX10-                     | 27                    | RX9+     | 61  | RX9-                                        |

| 11  | TX11+                                                 | 45  | TX11-                     | 28                    | RX10+    | 62  | RX10-                                       |