#### ICS ICS-610A-32A 32-Channel, 108 kHz/ch. Data Acquisition Board

In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/51104-2

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

Your definitive source for quality pre-owned equipment.

**Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

# **ICS-610**

# **OPERATING MANUAL**

Interactive Circuits and Systems Ltd.

February 2006

The information in this manual has been carefully checked and is believed to be reliable; however, no responsibility is assumed for possible inaccuracies or omissions. Interactive Circuits and Systems Ltd. reserves the right to make changes to products herein described to improve reliability, function, or design. No patent rights are granted to any of the circuits described herein.

Extra copies of this manual are available from the factory.

ICS Ltd. 5430 Canotek Road Ottawa, Ontario K1J 9G2 Canada

http://www.ics-ltd.com

Tel: (613) 749-9241 USA: (800) 267-9794 Fax: (613) 749-9461

THIS DOCUMENT CONTAINS COMPANY CONFIDENTIAL INFORMATION AND MUST NOT BE DISCLOSED TO ANY UNAUTHORIZED PERSON.

# **TABLE OF CONTENTS**

| 1 |                | ODUCTIONoduct Versions                        |    |

|---|----------------|-----------------------------------------------|----|

| 2 |                | RAL DESCRIPTION                               |    |

| 2 |                | ecifications                                  |    |

|   | •              | poling                                        |    |

|   |                | wer                                           |    |

| 3 |                | ILED DESCRIPTION                              |    |

| J |                | gma-Delta Analog Conversion                   |    |

|   |                | nti-Alias Filtering                           |    |

|   |                | nalog Inputs                                  |    |

|   |                | atched Channels                               |    |

|   | 3.5 Sa         | mpling Clock                                  | 9  |

|   | 3.6 Ou         | ıtput Decimation                              | 9  |

|   | 3.7 CI         | ock vs. Channel Output Rate Relationship      | 10 |

|   | 3.8 Ex         | ternal Trigger                                | 11 |

|   | 3.9 Mo         | odes of Operation                             | 11 |

|   | 3.10 Da        | ıta Packing                                   | 12 |

|   | 3.11 Op        | otional FPDP Interface                        | 12 |

|   | 3.12 FF        | PDP Timing Limits                             | 13 |

|   | 3.13 PC        | CI Bus Interface                              | 13 |

|   | 3.14 Int       | errupts                                       | 13 |

|   |                | ock Transfers                                 |    |

|   | 3.16 Cc        | onverter Programmable Features                |    |

|   | 3.16.          |                                               |    |

|   | 3.16.2         | 2 Converter High Pass Filtergnal Conditioning |    |

|   |                | ultiple Board Configurations                  |    |

| _ |                | •                                             |    |

| 4 |                | WARE CONFIGURATION                            |    |

|   |                | ternal Clock and Trigger Terminations         |    |

|   |                | ont Panel Data Port (FPDP) Connections        |    |

| _ |                | ,                                             |    |

| 5 |                | BRAMMING MODEL                                |    |

|   |                | 60EPC Registers                               |    |

|   |                | erforming DMA Transfers                       |    |

|   | 5.3.1          | PCI Bus DMA Master                            |    |

|   | 5.3.2          | PCI Bus DMA Chaining                          |    |

|   | 5.3.3          | PCI Bus DMA Slave                             | 37 |

|   |                | OC Data/Diagnostics Area                      |    |

|   |                | atus Register (SR)                            |    |

|   | 5.5.1          | SR<0> - ADC IRQSR<1> - ADC Interrupt Pending  |    |

|   | 5.5.2<br>5.5.3 | SR<1> - ADC Interrupt Pending                 |    |

|   | 5.5.5          | C. C. Diagnood in Chipty                      | 55 |

|                                                                                                       | 5.4                                                                                          | SR<3> - ADC Offset Calibration                                                                                                               |                      |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                                                                                                       | 5.5                                                                                          | SR<5> - Daughter Card Present                                                                                                                |                      |

|                                                                                                       | 5.6                                                                                          | SR<6> - Buffer Overflow                                                                                                                      |                      |

| 5.6                                                                                                   | Interr                                                                                       | upt Mask Register (IMR)                                                                                                                      |                      |

|                                                                                                       | 6.1                                                                                          | IMR<0> - ADC IRQ Mask                                                                                                                        |                      |

|                                                                                                       | 6.2                                                                                          | IMR<6> - Buffer Overflow IRQ Mask                                                                                                            |                      |

| 5.7                                                                                                   | Contr                                                                                        | ol Register (CR)                                                                                                                             |                      |

|                                                                                                       | 7.1                                                                                          | CR<00> - Trigger Select                                                                                                                      |                      |

| _                                                                                                     | 7.2                                                                                          | CR<01> - ADC Sampling Clock Select                                                                                                           |                      |

|                                                                                                       | 7.3                                                                                          | CR<02> - Diagnostic Mode Enable/Disable                                                                                                      |                      |

|                                                                                                       | 7.4                                                                                          | CR<03> - FPDP Enable                                                                                                                         |                      |

|                                                                                                       | 7.5                                                                                          | CR<04> - Select Packed Data                                                                                                                  |                      |

|                                                                                                       | 7.6                                                                                          | CR<05> - Select ADC Master<br>CR<06> - ADC Terminations Enable                                                                               |                      |

|                                                                                                       | 7.7<br>7.8                                                                                   | CR<06> - ADC Terminations Enable                                                                                                             |                      |

|                                                                                                       | 7.8<br>7.9                                                                                   | CR<08> - FPDP Terminations Enable                                                                                                            |                      |

|                                                                                                       | 7.3<br>7.10                                                                                  | CR<10> - Oversampling Ratio                                                                                                                  |                      |

| _                                                                                                     | 7.11                                                                                         | CR<11> - ADC HP Filter Enable                                                                                                                |                      |

|                                                                                                       | 7.12                                                                                         | CR<12> - Zero Calibration                                                                                                                    |                      |

|                                                                                                       | 7.13                                                                                         | CR<13> - Acquisition Mode                                                                                                                    |                      |

| 5.                                                                                                    | 7.14                                                                                         | CR<14> - ADC Internal Trigger                                                                                                                |                      |

| 5.                                                                                                    | 7.15                                                                                         | CR<15> - ADC Enable                                                                                                                          |                      |

| 5.8                                                                                                   | Gain/                                                                                        | Bandwidth Control                                                                                                                            | 45                   |

| 5.                                                                                                    | 8.1                                                                                          | GBCR <03:00> - Input Voltage Range                                                                                                           | 45                   |

| 5.                                                                                                    | 8.2                                                                                          | GBCR <05:04> - Bandwidth Selection                                                                                                           |                      |

| 5.9                                                                                                   | Chan                                                                                         | nel Count Register                                                                                                                           |                      |

| 5.10                                                                                                  | Buffe                                                                                        | r Length Register                                                                                                                            | 46                   |

| 5.11                                                                                                  |                                                                                              | isition Length Register                                                                                                                      |                      |

| J. 1 1                                                                                                | •                                                                                            |                                                                                                                                              | 4/                   |

| F 40                                                                                                  | D !                                                                                          | antina Danintan                                                                                                                              | 40                   |

| 5.12                                                                                                  |                                                                                              | nation Register                                                                                                                              |                      |

| 5.13                                                                                                  | Frame                                                                                        | e Length Register                                                                                                                            | 48                   |

| 5.13                                                                                                  | Frame                                                                                        | •                                                                                                                                            | 48                   |

| 5.13<br>5.14                                                                                          | Frame                                                                                        | e Length Register                                                                                                                            | 48                   |

| 5.13<br>5.14<br>5.15                                                                                  | Frame<br>ADC (<br>FPDP                                                                       | e Length RegisterClock Frequency Register                                                                                                    | 48<br>49<br>49       |

| 5.13<br>5.14<br>5.15<br>5.16                                                                          | Frame<br>ADC<br>FPDP<br>Arm F                                                                | e Length Register  Clock Frequency Register  Clock Frequency Register                                                                        | 48<br>49<br>49       |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17                                                                  | Frame<br>ADC (<br>FPDP<br>Arm F<br>ADC (                                                     | e Length RegisterClock Frequency Register                                                                                                    | 48<br>49<br>49<br>50 |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18                                                          | Frame<br>ADC (<br>FPDP<br>Arm F<br>ADC (<br>Board                                            | e Length Register  Clock Frequency Register  Clock Frequency Register  Register  Reset Register                                              | 48<br>49<br>50<br>50 |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18                                                          | Frame<br>ADC (<br>FPDP<br>Arm F<br>ADC (<br>Board<br>Maste                                   | e Length Register  Clock Frequency Register  Clock Frequency Register  Register  Reset Register  d Reset Register  er Control Register (MCR) | 4849505050           |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19                                                  | Frame<br>ADC (<br>FPDP<br>Arm F<br>ADC (<br>Board<br>Maste                                   | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19                                                  | Frame<br>ADC (<br>FPDP<br>Arm F<br>ADC (<br>Board<br>Maste<br>19.1<br>19.2                   | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19                                                  | Frame<br>ADC (<br>FPDP<br>Arm F<br>ADC (<br>Board<br>Maste<br>19.1<br>19.2                   | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.<br>5.20                                    | Frame<br>ADC (<br>FPDP<br>Arm F<br>ADC (<br>Board<br>Maste<br>19.1<br>19.2<br>Using          | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.<br>5.<br>5.20<br>5.21                      | Frame<br>ADC (<br>FPDP<br>Arm F<br>ADC (<br>Board<br>Maste<br>19.1<br>19.2<br>Using<br>Typic | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.<br>5.20<br>5.21                            | Frame ADC   FPDP Arm F ADC   Board Maste 19.1 19.2 Using Typic                               | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.<br>5.20<br>5.21<br>US<br>6.1               | Frame<br>ADC (<br>FPDP<br>Arm F<br>ADC (<br>Board<br>19.1<br>19.2<br>Using<br>Typic          | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.<br>5.20<br>5.21<br>US<br>6.1               | Frame ADC   FPDP Arm F ADC   Board Maste 19.1 19.2 Using Typic ING T ADC   1.1               | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.<br>5.20<br>5.21<br>US<br>6.1<br>6.         | Frame ADC   FPDP Arm F ADC   Board 19.1 19.2 Using Typic ING T ADC   1.1 1.2                 | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.20<br>5.21<br>US<br>6.1<br>6.6              | Frame ADC   FPDP Arm F ADC   Board 19.1 19.2 Using Typic ING T ADC   1.1 1.2 Single          | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.<br>5.20<br>5.21<br>US<br>6.1<br>6.         | Frame ADC   FPDP Arm F ADC   Board 19.1 19.2 Using Typic ING T ADC   1.1 1.2 Single          | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.<br>5.20<br>5.21<br>US<br>6.1<br>6.2<br>6.2 | Frame ADC   FPDP Arm F ADC   Board 19.1 19.2 Using Typic ING T ADC   1.1 1.2 Single Two-I    | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.20<br>5.21<br>US<br>6.1<br>6.2<br>6.3<br>TE | Frame ADC   FPDP Arm F ADC   Board 19.1 19.2 Using Typic ING T ADC   1.1 1.2 Single Two-I    | e Length Register                                                                                                                            |                      |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.20<br>5.21<br>US<br>6.1<br>6.2<br>6.3<br>TE | Frame ADC   FPDP Arm F ADC   Board 19.1 19.2 Using Typic ING T ADC   1.1 1.2 Single Two-I    | e Length Register                                                                                                                            |                      |

6

7 8

| A.1        | Introduction                               | 63 |

|------------|--------------------------------------------|----|

| <b>A.2</b> | Programming Summary                        | 63 |

| A.3        | Control Register                           | 63 |

| A.4        | Programming Register                       | 64 |

| A.5        | VCO Programming Constraints                | 65 |

| A.6        | Program Register Example                   | 66 |

| <b>A.7</b> | Oscillator Programming Example             | 67 |

| APPEN      | NDIX B ANALOG INPUT 1-32 CONNECTOR DETAILS | 68 |

| APPEN      | NDIX C P4 LOCAL BUS CONNECTOR DETAILS      | 70 |

| APPEN      | NDIX D P5 FPDP DETAILS                     | 72 |

|            | FPDP Connector Pin Assignments             |    |

| D.2        | FPDP Signals                               | 74 |

### 1 INTRODUCTION

The ICS-610 is a PCI analog input board providing up to 32 differential input channels. It is currently being offered as the ICS-610A, a 2<sup>nd</sup> generation product. Note: The ICS-610 product is still available for legacy customers. All references in this manual to ICS-610 refer to both products unless otherwise specified.

The ICS-610 board offers the following features:

- Up to 32 differential input channels;

- 2-pole anti-aliasing filter consistent with the requirements of Sigma-Delta ADCs;

- Programmable gain;

- Built-in over voltage protection;

- Simultaneous sampling at rates of up to 108 kHz/ch;

- Software-selectable high-pass filter for low frequency rejection;

- External or internal clock and trigger;

- Internal clock programmable in steps of less than 20 Hz at output frequency;

- Greater than 90 dB Signal-to-noise ratio;

- 1 M Sample on-board swing buffer memory;

- Continuous, one-shot and transient (pre-trigger) data capture;

- · Programmable-length PCI Bus interrupt;

- 33 MHz master/slave PCI interface

- Universal PCI Signaling Environment

- Optional FPDP and synchronization interface;

- Up to 32 ICS-610 boards can be operated synchronously to ensure simultaneous sampling;

- Comprehensive software device driver supporting Windows NT, Windows 2000, Windows XP and Windows Server 2003

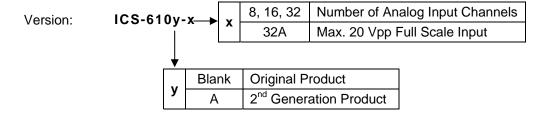

### 1.1 Product Versions

The ICS-610 is available in a number of versions providing a different number of differential analog input channels to the board. The product version is given on a label on the product, and is represented as follows:

#### 2 GENERAL DESCRIPTION

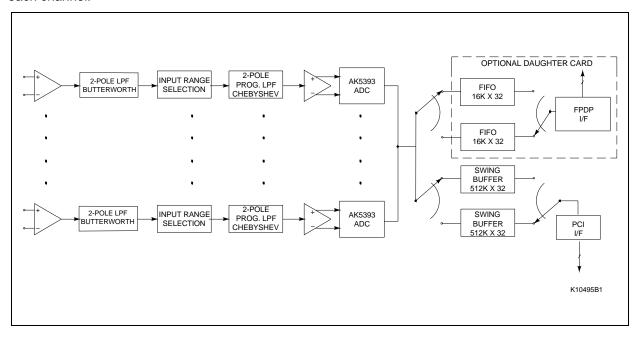

Figure 1 shows a simplified block diagram of the ICS-610. The board includes up to 32 separate 24-bit Sigma-Delta ADCs to simultaneously digitize all channels at rates up to 108 kHz per channel. All inputs are differential in order to suppress common-mode noise. The ICS-610 includes signal conditioning for each channel.

Figure 1 - ICS-610 Block Diagram (only two channels shown)

The differential signals at the front panel analog input connectors are buffered and converted to single ended signals. The signal for each channel then passes through a fixed two-pole, 75 kHz anti-alias filter with a Butterworth characteristic. The filter output is applied to an input range selection stage; the input voltage is selectable from one of four ranges that provide full scale outputs for inputs of 1 Vpp, 2 Vpp, 5 Vpp and 10 Vpp on each wire of the differential input. The ICS-610-32A product version has selectable inputs of 2 Vpp, 4 Vpp, 10 Vpp and 20 Vpp on each wire of the differential input. The signal then goes through a bandwidth selection stage. This programmable low pass filter provides the proper filtering for bandwidths of 0-2 kHz, 2-6 kHz, 6-20 kHz and 20-45 kHz.

After the filter stage, the signal is buffered and is then applied to the ADC. The serial output from the ADC is converted to a 24-bit parallel word before either being stored in a swing buffer memory for subsequent read-out over the PCI Bus, or being stored in a dual-banked FIFO on the optional FPDP daughter card interface.

Data is acquired in frames, where a frame contains one sample from each selected channel at a single sampling instant. Any numbers of channels (multiples of 2 only) up to the maximum for the board may be selected for operation, but the channels are always allocated in ascending order starting at channel one.

At the output, 24-bit signed (2's complement) samples are presented in the most significant 24 bits of each 32-bit data word; the least significant 8 bits are forced to zero. If preferred, the 24-bit data may be truncated to 16-bits. In this case, data from consecutive odd and even channels is combined to form a 32-bit word in order to make the most efficient use of bus bandwidth. This is known as the packed data

mode of operation. The PCI Bus interface supports block transfers. A PCI Bus interrupt at swing buffer swap can be generated to facilitate real-time operation.

The sampling clock for the ICS-610 board can be either an external clock or the board's programmable frequency internal clock. The clock frequency must be 128 times the output data rate for each channel when using the ADCs at double speed, and 256 times the output data rate when using ADC at normal speed. The output data rate is equivalent to the sampling rate of conventional ADCs. The input signal is sampled at one half the clock rate, which is 64 or 128 times the input signal bandwidth; this is known as the oversampling rate. This high sampling rate virtually eliminates the need for anti-aliasing. Each Sigma-Delta ADC uses internal digital filtering and decimation to produce an output at the desired sampling rate. The output data rate can be further reduced using a programmable on-board decimation register; however, care must be taken to ensure that the input signal is properly anti-aliased before decimating the ADC output.

The internal sampling clock of the ICS-610 can produce a user-specified sampling rate to within 20 Hz at the output rate. The clock is programmed by writing the appropriate clock frequency program word to the board's ADC clock frequency register. Software is included with the software device driver for the board to simplify computation of this programming word.

Data acquisition can be triggered using either an external signal or by software control. When using the external trigger, the signal is applied to the EXT\_TRIG input and must conform to TTL signal levels. Acquisition starts when the signal changes from the low state to the high state.

The ADCs can be operated either in continuous or capture modes. In the continuous mode, data is continuously supplied to the selected interface upon application of a trigger signal until the acquisition is disabled. In capture mode, a fixed number of samples are acquired upon each application of the trigger. There are two ways in which this may be done. When using pre-trigger storage, the ICS-610 stores samples continuously before the trigger and acquires a programmable number of samples following the trigger (to a maximum of 32768 samples/channel in packed mode and 16384 samples/channel in unpacked mode if all 32 channels are active). When pre-trigger storage is not used, conversion starts at each application of the trigger and a programmable number of samples are acquired.

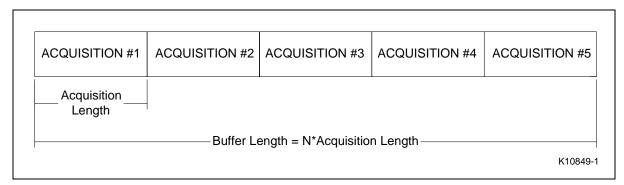

In capture mode without pre-trigger storage, the acquisition length and buffer length may be programmed separately. Thus it is possible to perform multiple capture sequences at each occurrence of the trigger, until the buffer is filled to the programmed length.

The ICS-610 board can generate PCI Bus interrupts at any user-programmed interval (number of samples acquired).

When using the optional FPDP daughter card, up to 32 ICS-610 boards may be configured as a cluster to provide simultaneous sampling with excellent synchronization. When operating in this configuration, one board must be configured as Sampling Master, while the remaining boards are configured as Slaves. This board generates the sampling clock and trigger (external or internal) and feeds them to all other boards in the cluster. The signals required to provide this functionality are routed on the P4 Local Bus connector located on the FPDP daughter card.

The ANSI/VITA 17 Front panel Data Port (FPDP) on the daughter card provides a 32-bit parallel, synchronous interface which is connected using ribbon cable. This may be used in point-to-point and multi-drop configurations to carry sampled data to other devices such as digital signal processors and storage devices. Please see the ICS website (see cover page) for names of FPDP partner companies.

When using multiple board configurations, the Front Panel Data Port (FPDP) can operate in a multiplexed fashion so that a composite data frame is generated on FPDP containing data from all channels in the cluster. The control signals required to generate composite FPDP frames with the correct timing are also included on the P4 Local Bus interface.

### 2.1 Specifications

| ICS-610 Board                                 |                                                            |

|-----------------------------------------------|------------------------------------------------------------|

|                                               | 9. 46 or 22                                                |

| Number of Differential Analog Inputs          | 8, 16 or 32<br>>1 MOhm                                     |

| Input Impedance Full Scale Input: ICS-610     | _                                                          |

| ICS-610-32A                                   | 1, 2, 5, 10 Vpp differential 2, 4, 10, 20 Vpp differential |

|                                               | ±37 V each wire                                            |

| Maximum Safe Input Voltage                    | 2-pole Butterworth characteristic                          |

| Fixed Anti-alias Lowpass Filter               | Cutoff frequency 75 kHz                                    |

| Programmable Anti-alias Lowpass Filter        | Signal Bandwidth Cutoff                                    |

| 1 Togrammable Anti-alias Lowpass Filter       | 0 – 2 kHz 6.5 kHz                                          |

|                                               | 2 – 6 kHz 20 kHz                                           |

|                                               | 6 – 20 kHz 65 kHz                                          |

|                                               | 20 – 45 kHz 150 kHz                                        |

| Maximum Input Signal Bandwidth                | 49 kHz                                                     |

|                                               | 128 x Output rate for BW < 24 kHz                          |

| Input Sampling Rate                           | 64 x Output rate for BW > 24 kHz                           |

| Output Rate (Effective Sampling Rate)         | Max. 108 kHz/ch                                            |

|                                               | Min. 1 kHz/ch (External Clock)                             |

|                                               | Min. 2 kHz/ch (Internal Clock)                             |

| Internal Sample Clock                         | Programmable in steps of 20 Hz (at output freq.)           |

| Signal-to-Noise Ratio                         | > 90 dB                                                    |

| Total Harmonic Distortion                     | < -90 dBFS                                                 |

| Crosstalk                                     | < -90 dBFS                                                 |

| On-board Storage                              | 2 MSamples (16-bit truncated data)                         |

| On-board Storage                              | 1 MSample (24-bit data)                                    |

| Output Word Length                            | 32 bits packed for 2 channels                              |

|                                               | 24 bits for 1 channel                                      |

| PCI Bus Interface: ICS-610                    | 32-bit 33 MHz Master/Slave                                 |

| ICS-610A                                      | Universal 32-bit 33 MHz Master/Slave                       |

| Power: ICS-610                                | 3.8 Amps @ +5 V                                            |

|                                               | 0.79 Amps @ +12 V                                          |

| 100 0404                                      | 0.66 Amps @ -12 V                                          |

| ICS-610A                                      | 0.15 Amps @ +3.3 V<br>3.7 Amps @ +5 V                      |

|                                               | 0.79 Amps @ +12 V                                          |

|                                               | 0.66 Amps @ -12 V                                          |

| Operating Temperature                         | 0 to +50 °C                                                |

| Storage Temperature                           | -40 to +85 °C                                              |

| Humidity                                      | ≤ 95% Rel. Humidity, non-condensing                        |

| Board Size                                    | Full-length PCI                                            |

| DC-610 Daughter Board (Optional)              | i congari or                                               |

| FPDP Interface                                | ANSI/VITA 17 (32-bit @ 160 MBytes/second)                  |

|                                               | 32 bits packed for 2 channels                              |

| Output Word Length                            | 24 bits for 1 Channel                                      |

| acifications aubicat to abance without nation |                                                            |

Specifications subject to change without notice

<sup>\*</sup> This voltage is on each wire of the differential pair, with respect to ground. When providing a single-ended input, the input must be twice this value in order to achieve a full scale output. The ICS-610 standard product cannot achieve full scale output when using a single-ended input on the 10 Vpp range. The ICS-610-32A product version cannot achieve full scale output when using a single-ended input on the 20 Vpp range. For details see Section 3.3.

### 2.2 Cooling

It is essential that the user provides adequate cooling air to the ICS-610 when it is installed in the target system. It is not possible to design high performance, high density A/D and D/A converter products with very low power consumption requirements. Higher power requirements translate to a greater requirement for heat dissipation. Many PCI backplane/enclosure systems are not designed to provide a flow of cooling air to the boards. In some cases, a flow of air is provided through the case, but this may not directly cool the boards. In other situations, no cooling arrangements exist, apart from a fan in the power supply unit and a separate one for the CPU. The ideal cooling arrangement consists of a laminar flow of cooling air over each surface of the board, with the warm air being removed to the external environment. However, this may not be possible to achieve at all times. We recommend that the user consider the following approaches:

- 1. Use a PCI backplane/enclosure system that has been designed to provide a laminar flow of cooling air to the boards.

- 2. Use a 'fan card' in a slot adjacent to the component side of the ICS-610.

- 3. Examples of such products may be found at:

- http://www.antec-inc.com/

- http://www.thecardcooler.com

- 4. Mount a fan in close proximity to the ICS-610.

#### 2.3 Power

It is not possible to design high performance, high density A/D and D/A converter products with very low power consumption requirements. Many backplane/enclosure products do not measure or limit the power consumption of each PCI slot. However, some products are now taking this approach. We therefore recommend that the user should consider the PCI backplane/enclosure/system to be used with the ICS-610 and avoid products that specifically limit power consumption to 25 Watts.

#### 3 DETAILED DESCRIPTION

### 3.1 Sigma-Delta Analog Conversion

The operation of a Sigma-Delta ADC differs significantly from traditional ADCs. A 1-bit analog-to-digital conversion is performed at a very high rate. The total quantization noise energy remains constant, but by spreading it over a wider spectrum, the amount in the frequency band of interest is reduced. The noise in the passband is further reduced by filtering (noise shaping). The oversampled signal is then lowpass filtered to remove the out-of-band quantization noise. This is achieved using a decimation comb filter and a FIR low-pass filter/decimator. The resulting output spectrum is equivalent to a traditional ADC.

For more information on Sigma-Delta analog-to-digital conversion techniques, see Reference [6].

## 3.2 Anti-Alias Filtering

The ICS-610 board uses an AKM AK5393 Sigma-Delta converter. This device is designed to sample the input signal at a rate which is greater than 128 times the signal bandwidth, when an output rate of up to 54 kHz is required. A 64x oversampling mode is also provided for output rates up to 108 kHz.

Since the Nyquist frequency is at least six (6) octaves away from the highest signal frequency, no more than a 3-pole filter is required for anti-aliasing. The input differential amplifiers buffering the analog inputs on the ICS-610 board, however, have a finite bandwidth. Further, in many applications, the input signal strength reduces naturally beyond the passband of interest. There are 2-pole, fixed Butterworth anti-alias filters provided on the ICS-610 filter (see Section 3.17) along with a programmable 2-pole Chebyshev filter.

The Sigma-Delta ADC limits the signal bandwidth to approximately 45.35% of the output data rate by digital filtering. The minimum output rate is 1 kHz (2 kHz when using the on-board programmable sampling clock). However, lower output rates can be achieved by using the on-board decimation feature. In this case, care must be taken to ensure that the input signal is bandlimited to less than half the final output rate in order to avoid aliasing.

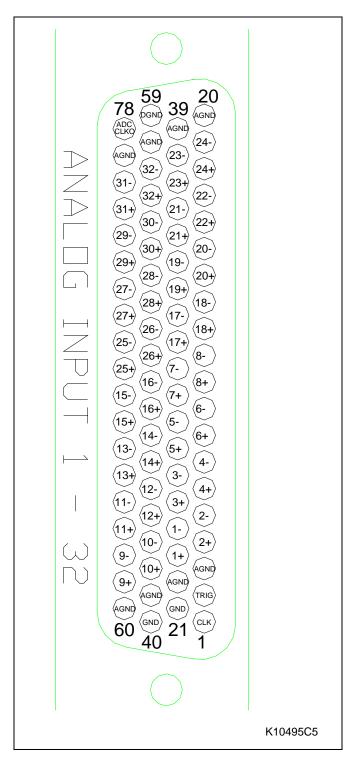

### 3.3 Analog Inputs

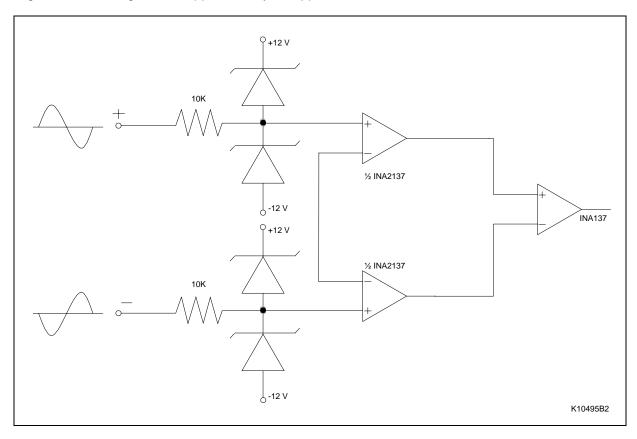

The ICS-610 standard board accepts true differential analog input signals with peak amplitudes of 1 Vpp, 2 Vpp, 5 Vpp and 10 Vpp (2 Vpp, 4 Vpp, 10 Vpp and 20 Vpp for the ICS-610-32A version) on each differential leg (for a nominal gain control setting of 0 dB), as shown in Figure 2. The input impedance is 1 MOhm. The converted samples are presented as two's complement (signed) 24-bit values.

For best performance, differential input signals are recommended on both the ICS-610 standard board and ICS-610-32A product versions. If, however, a single-ended input must be used, the negative (-) input terminals can be tied together to a common analog ground, preferably the ground of the source. The input signal is applied to the positive (+) terminal. Users should note that, for ICS-610, it will not be possible to drive the input to full scale on the 10 Vpp range when using a single-ended input. This would nominally require a 20 Vpp input; the output will appear to clip at approximately 14 Vpp.

For the ICS-610-32A version, when using a single-ended input, it would normally require a 40 Vpp signal in order to achieve a full scale output; the output will appear to clip at approximately 20 Vpp.

The ICS-610-32A version linear range of operation does not extend to full scale input on the 20 Vpp range; the linear range limit is approximately 14 Vpp on each wire.

Figure 2 - ICS-610 Analog Input Configuration

#### 3.4 Matched Channels

The ICS-610 offers excellent gain and phase matching across channels. Since the Sigma-Delta converters employ minimal analog technologies, such performance is expected. In the design of the ICS-610 board, extreme care has been taken in the generation of sampling clocks in order to assure precise simultaneous sampling on every card, and across cards in a multiple board system.

### 3.5 Sampling Clock

The ICS-610 board can be configured (by programming the control register) to use either the internal programmable-frequency sampling clock or an external clock. If used, the external sampling clock signal must be a TTL level signal and must be applied to the EXT\_CLK pin on the front panel analog input connector. The frequency of the clock signal must be 128 times the desired output rate when operating in 64x oversampling mode, or 256 times the desired output rate when operating in 128x oversampling mode.

The buffered clock signal (whether internally or externally sourced) is available at the Local Bus connector pins on the optional daughter card in order to supply clock signals to other ICS-610 boards for synchronous operation. The board generating the clock signal must be programmed as the ADC Sampling Master so that the appropriate slave clock signals are routed to the P4 connector. All boards, including the master, see identical propagation delays for the clock signal, regardless of whether it is generated by an ICS-610 board or applied from an external source.

The maximum clock frequency is 13.824 MHz and the minimum clock frequency is 256 kHz (external) and 512 kHz (internal).

#### 3.6 Output Decimation

The output rate can be further reduced using the on-board decimation feature. At the output, samples are automatically discarded, which has the effect of lowering the effective sampling rate. The maximum decimation factor that may be programmed is 256.

The user is cautioned that decimating the output requires anti-alias filtering (similar to using a conventional ADC) in order to bandlimit the input signal to a Nyquist frequency that is equal to half the final output rate. Thus, output decimation is only recommended for reducing the output rate below 1 kHz.

### 3.7 Clock vs. Channel Output Rate Relationship

The channel output rate is directly related to the frequency of the internal programmable or external clock signal frequency as follows:

```

Channel Output Rate = Fs / (2 x OSR x DF)

```

where Fs is the clock frequency, OSR is the oversampling ratio selected in the Control register (64x or 128x), and DF is the decimation factor (see Section 3.6).

Thus, for a maximum 13.824 MHz clock, using 64x oversampling and assuming no output decimation, the channel output rate is:

```

Channel Output Rate = 13,824,000 / (2 \times 64 \times 1)

= 108 \text{ kHz}.

```

For a maximum 13.824 MHz clock, using 128x oversampling and assuming no output decimation, the channel output rate is:

```

Channel Output Rate = 13,824,000 / (2 \times 128 \times 1)

= 54 \text{ kHz}.

```

For a minimum 256 kHz clock, when using the internal ADC clock and 128x oversampling (and assuming no output decimation), the channel output rate is:

```

Channel Output rate = 256,000 / (2 \times 128 \times 1)

= 1.0 kHz.

```

# 3.8 External Trigger

Triggering of acquisition can be either internally controlled from the PCI Bus by writing to the Control register, or externally controlled via the front panel analog input connector EXT\_TRIG signal. In either case, the effect is to start enabling and inhibiting writes to the board's swing buffer memory. The operation is data frame-oriented; acquisition can only be started at the beginning of a frame or stopped at the end of a frame. A frame includes all channel data corresponding to a given sample period. Note that the ADCs are never stopped, they are always operating.

### 3.9 Modes of Operation

Three modes of operation are provided in the ICS-610 design:

- Capture mode without pre storage,

- Capture mode with pre storage,

- Continuous mode, which has no pre storage option.

In the Capture mode without pre storage, data is acquired for a programmable number of samples following the application of each trigger.

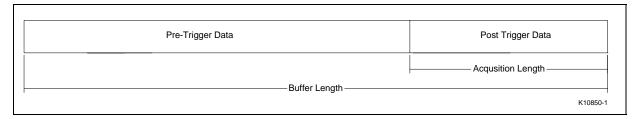

Important note: When using Capture mode without pre-trigger storage, the memory buffer length programmed must always be an integral number of acquisition lengths. See Figure 3.

Figure 3 – Buffer Length in Terms of Acquisition Length

In the Capture mode with pre storage, the ICS-610 memory is used as a circular buffer of programmable length. The ICS-610 is armed by the user, and the control logic continuously fills the circular buffer with fresh data samples in anticipation of the trigger signal. When the trigger signal is received, the final acquisition length number of samples is stored in memory, and acquisition is automatically terminated.

To select pre-trigger storage of data in Capture mode, the Arm register must be written to as the last action of configuring the board. This will cause the board to start acquiring data. If the Arm register is not written to, pre-trigger storage will not occur.

Note: When using pre-trigger storage, acquisition length and memory buffer size may be independently set. Data stored in the memory buffer will be divided into two sections: data acquired before the application of the trigger, and data acquired after the application of the trigger. See Figure 4.

Figure 4 - Trigger Data Storage

In the Continuous mode of operation, acquisition begins upon application of the trigger and continues until the board is disabled.

#### 3.10 Data Packing

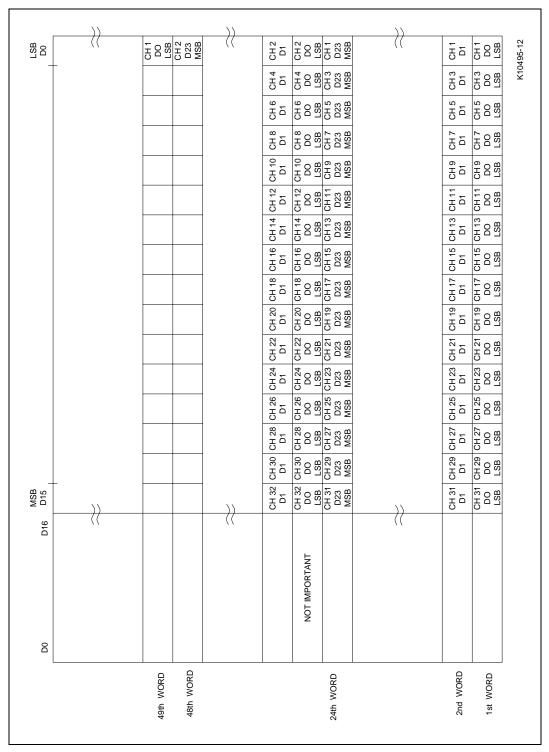

Data packing is available on both PCI and FPDP interfaces. 24-bit resolution is provided on the ICS-610, and when unpacked data is selected (CR<04>), it drives data on only the most significant 24 bits of each 32-bit PCI or FPDP word; the least significant 8 bits are read as zeroes. When packed data is selected, the 24-bit samples are truncated to 16 bits and two samples are contained in each 32-bit FPDP or PCI word, with the lower channel number in the upper 16 bits of each word.

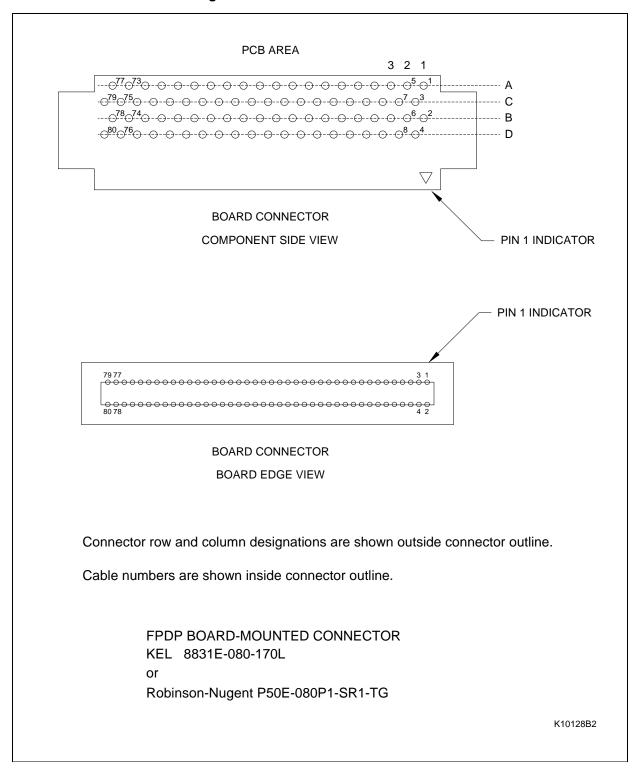

#### 3.11 Optional FPDP Interface

The ANSI/VITA 17 Front Panel Data Port (FPDP) is a synchronous parallel data transfer bus which uses ribbon cable. It is ideally suited to the requirements of high speed real-time data transfer. Since only one bus master is allowed, and there is no addressing on the bus, the maximum possible bandwidth is available for data transfer. FPDP provides a simple and inexpensive mechanism for off-loading data from PCI Bus.

The FPDP protocol for data transfer is supported by all ICS current products. An 80- pin ribbon cable connector is provided for the FPDP (see APPENDIX D).

When unpacked data is selected (see Section 3.10), the undriven least significant 8 bits of the 32-bit bus contain zeroes.

The FPDP burst rate (Data Strobe frequency) is software programmable up to 20 MHz. In addition to the Data Strobe signal, positive-logic ECL differential clocks (+PECL Strobe & -PECL Strobe) are also supplied in order to support longer cable lengths, high speed operation, and greater immunity from clock-related problems.

The Front Panel Data Port interface operates using two FIFO memories in a swing buffer configuration. During one frame, data is converted and written to one FIFO memory, while the FPDP interface reads data from the other and transmits it over the FPDP cable. At the end of the frame, the two banks switch. Before any new ADC data is written to the swapped FIFO memory, it is automatically reset to ensure channel synchronization. If the synchronization is somehow lost, this scheme ensures that the synchronization is recovered in the next frame.

By programming the frame length register, the user can set the bank switch to occur after storing a specified number of frames.

### 3.12 FPDP Timing Limits

When using the FPDP in a multiple board configuration, it must be noted that the maximum FPDP data rate is 20 MHz. The value programmed for the FPDP Data Strobe frequency using the FPDP Clock Frequency register should not exceed this value (see Section 5.15 and APPENDIX A). The user must ensure that whatever FPDP Data Strobe frequency is programmed is sufficient to provide the data throughput required by the selected sampling frequency. The minimum required data strobe rate is the sample output frequency multiplied by the number of channels programmed for the system (i.e. for all ICS-610 boards connected on the same FPDP). This channel count is programmed in the Master Control register.

At the 108 kHz maximum channel output rate, approximately 190 channels can be used (108 kHz x 190 = 19.7 MHz). Note that the on-board decimator reduces the output rate. If the decimator is used, this should be taken into account when calculating the FPDP throughput and required Strobe frequency.

In cases where the user's requirement would exceed the maximum transfer rate of FPDP, it is possible to set up multiple board configurations with multiple FPDP outputs. This is possible because the Sampling Master and FPDP Master functions of the ICS-610 are separate. By configuring a system with a single Sampling Master and multiple FPDP masters, the cluster of ICS-610 boards will all sample synchronously, but will output data on two or more FPDP cables. Details of board configuration are given in Section 4.

#### 3.13 PCI Bus Interface

The ICS-610 implements a 33 MHz, 32-bit, PCI Bus Master/Slave interface compliant with the PCI 2.1 specification, using the V3 Semiconductor V360EPC integrated circuit. At power-on, the operating system will automatically set the PCI base addresses for the board.

**Important note:** The data on the PCI Bus is in little-endian format, i.e. ascending byte address read from LSB to MSB of the data.

### 3.14 Interrupts

When enabled, the ICS-610 will generate a PCI interrupt when a swing buffer swap occurs. To enable the interrupt, the ADC Interrupt Enable bit in the Interrupt Mask register must be set.

When an interrupt occurs, the user may transfer data using either conventional or block transfer cycles. The swing buffer input side should be completely emptied in order to prevent a further interrupt before the next swing buffer swap.

#### 3.15 Block Transfers

The ICS-610 can act as either a master or a slave device for block (DMA) transfers on the PCI Bus. When using the V360EPC DMA Controller, chained DMA transfers are not supported. An interrupt can be generated at DMA transfer completion.

When addressing the ADC Data/ Diagnostics area of the PCI Bus memory map, successive reads need not be to sequential addresses. Any access within the valid address range from the base address (see above) will read the next data value from the swing buffer. It is valid to use the same address on every access, if desired.

## 3.16 Converter Programmable Features

#### 3.16.1 Converter Calibration

The AKM5393 converter requires calibration before use. Calibration occurs automatically following power-up and whenever the ADC sampling clock frequency is changed.

### 3.16.2 Converter High Pass Filter

The AKM AK5393 converter includes a first order high pass digital filter at the output, which may be used to remove DC offset. The filter 3 dB cut-off frequency is 1.0 Hz when the output rate is 48 kHz, and it scales linearly with frequency. The filter is enabled by setting bit 11 of the control register.

#### 3.17 Signal Conditioning

The signal conditioning feature provides up to 32 channels of programmable input voltage range selection and programmable input signal bandwidth selection. The block diagram in

Figure 1 shows the arrangement of the signal conditioning elements.

The design includes pre-gain anti-alias filters consisting of 2-pole low pass filters with a Butterworth characteristic. The cut-off frequency of these filters is fixed at 75 kHz.

There are four input voltage ranges that can be selected under software control: 1 Vpp, 2 Vpp, 5 Vpp, and 10 Vpp on each differential input wire for the ICS-610 standard product and 2 Vpp, 4 Vpp, 10 Vpp & 20 Vpp for the ICS-610-32A product version on each differential input wire.

The 2-pole post-gain low pass filter has a Chebyshev characteristic and is programmable to select the desired input signal bandwidth. There are four input bandwidth selection ranges as follows. The signal band is considered to extend from DC to one of the following ranges:

| Input Signal Bandwidth | Post-Gain Filter Selection |

|------------------------|----------------------------|

| 0 – 2 kHz              | 6.5 kHz                    |

| 2 – 6 kHz              | 20 kHz                     |

| 6 – 20 kHz             | 65 kHz                     |

| 20 – 45 kHz            | 150 kHz                    |

#### 3.18 Multiple Board Configurations

The ICS-610 is designed to allow simultaneous sampling across all channels on a board, and also across all channels on multiple boards. The optional FPDP daughter board must be present for the latter feature to be used, even if FPDP output is not used. To facilitate multiple board clusters, timing and external clock/trigger signals are bussed on the P4 Local Bus cable. In addition, if the Front Panel Data Port (FPDP) is used for data output, multiple ICS-610 boards may be bussed on the same FPDP cable.

Several multiple board cluster configurations are possible:

- All ICS-610 boards on one Local Bus cable, data read over PCI Bus from each board

- All ICS-610 boards on one Local Bus cable and on one FPDP cable

- All ICS-610 boards on one Local Bus cable, and on two or more FPDP cables

The latter case addresses the situation where a single FPDP cable would not have sufficient throughput, or where the FPDP/R- (receiver) board has insufficient throughput and multiple receiving boards must be used.

For the purposes of correctly driving and terminating bussed front panel signals, there are four possible software-controlled configurations for an ICS-610 board. These are:

- Master the board drives timing signals and terminates received signals

- Mid-Slave the board does not terminate or drive signals except data lines

- End-Slave the board terminates timing signals and drives data lines

- Stand-alone Master the board drives and terminates all signals

These classifications are applicable to both Local Bus and FPDP operation. It is possible for a board to be a Local Bus Mid-Slave but an FPDP Master, FPDP End-Slave or FPDP Stand-alone Master. The Master board must be located at one end of the cable. The End-Slave is located at the opposite end of the cable to the Master. The Mid-Slaves are located in between the Master and End-Slave boards. In a two board system, only Master and End-Slave configurations apply. The Stand-Alone Master refers to a one board system. The required Control register settings are determined by which of these four cases applies to the board in question. Also, switch settings are affected by whether a configuration uses internal or external clock (EXT\_CLK) and trigger (EXT\_TRIG) signals.

In PCI Bus systems, it is sometimes difficult to be sure which board is the master and which is the slave. In general, board PCI Bus address spaces are allocated by the BIOS in sequence from one end of the bus to the other, but it may not be immediately apparent which the starting end is. To resolve this uncertainty, a test should be done in which all boards are inserted in the system, and only one board is operated (as a stand-alone master). This board should be at one end of the group. An analog signal should be applied to channel 1 of each board in turn. It will then be apparent which board is the selected board, indicating which end of the bus is the starting end for PCI configuration.

When operating multiple boards, and reading data over PCI Bus (not FPDP), the last board to be read following each swing buffer swap interrupt must be the master board, in order to ensure that buffer swap signals required by the slave board/s are correctly generated.

If the ICS-610 board/s is/are connected to one or more Digital Signal Processor (DSP) or Array Processor boards using the FPDP, the DSP board/s should be installed in the chassis as the End-Slave of the FPDP cable (i.e. the ordering should be Master, Mid-slaves, End-Slave, DSP). If FPDP is not being used, the position of the DSP board/s in the chassis with respect to the ICS-610 boards is not important. The Master board (ICS610/0), should be inserted in the lower numbered PCI slot and should be initiated first by the driver. Slave board/s should be inserted in higher numbered PCI slot/s than the Master and should be initialized after the Master board. For example, the Master board is installed in slot 10 and the Slave boards should be inserted in slots 12 and higher.

# 4 HARDWARE CONFIGURATION

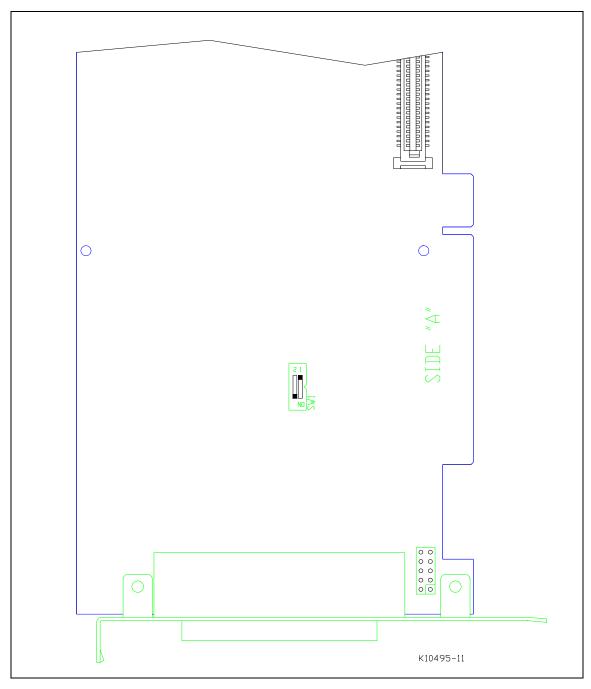

This section provides information necessary for hardware preparation of both single board and multiple board ICS-610 systems. Figure 5 shows the position of the switch block on the ICS-610 motherboard. There are no switches on the daughter board.

Figure 5 - ICS-610 Switch Locations

#### 4.1 Functions of Board Switches

The ICS-610 has a switch block that must be configured by the user according to the required operating configuration. Figure 5 shows the location of this switch block on the ICS-610 motherboard.

### 4.2 External Clock and Trigger Terminations

Switch block SW1 is used to connect parallel (pull-up/pull-down) resistive terminations to the External Clock and Trigger signals, as shown in the following table. These are required if the user chooses not to use serial terminating resistors at the signal transmitter/s. The resistive terminations are 220 Ohm pull-up to +5 VDC and 330 Ohm pull-down to ground on each signal.

Functions of the P4 Local Bus can be programmed by software using the Control Register (see Section 5.7). When connecting external clock and/or trigger signals to a multiple board FPDP configuration, the signals must be connected and terminated on the sampling master board. The external clock signal must be applied as a TTL level signal to pin 1 of the Analog Input connector. The external trigger signal must be applied as a TTL level signal to pin 2 of the Analog Input connector. The rising edge of the external trigger will cause sampling to start, if external triggering has been selected.

| SWITCH | FUNCTION (When switch in "ON" or Closed Position) |

|--------|---------------------------------------------------|

| SW1-1  | Terminate External Trigger Input                  |

| SW1-2  | Terminate External Clock Input                    |

### 4.3 Front Panel Data Port (FPDP) Connections

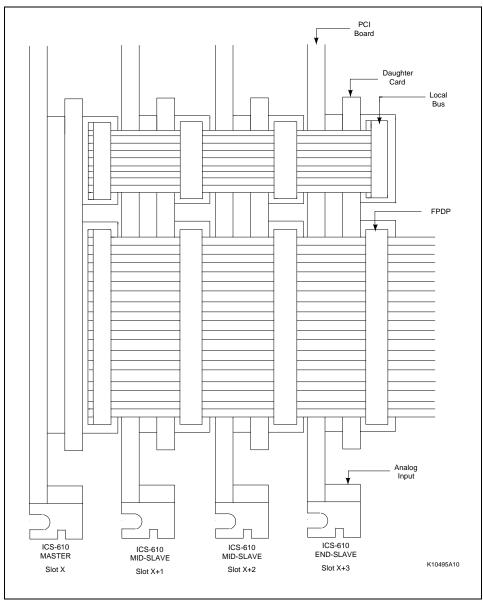

The FPDP provides a bus style interface between multiple ICS-610 boards and one or more Digital Signal Processor (Array Processor) boards. Up to 32 ICS-610 boards may be linked on a single FPDP connection. Figure 6 shows, as an example, how four ICS-610 boards can be bussed together. The 80-pin ribbon cable busses the four FPDP outputs, while the 26-pin Local Bus ribbon cable busses the synchronization signals. The Control Register FPDP Master bit (CR<07>), FPDP term bit (CR<08>) and ADC Master bit (CR<05>) must be set on the master board. The ADC Term bit (CR<06>) must be set on the End-Slave board. None of these bits must be set on Mid-Slave boards (if present).

Figure 6 - ICS-610 FPDP and Local Bus Connections

### 5 PROGRAMMING MODEL

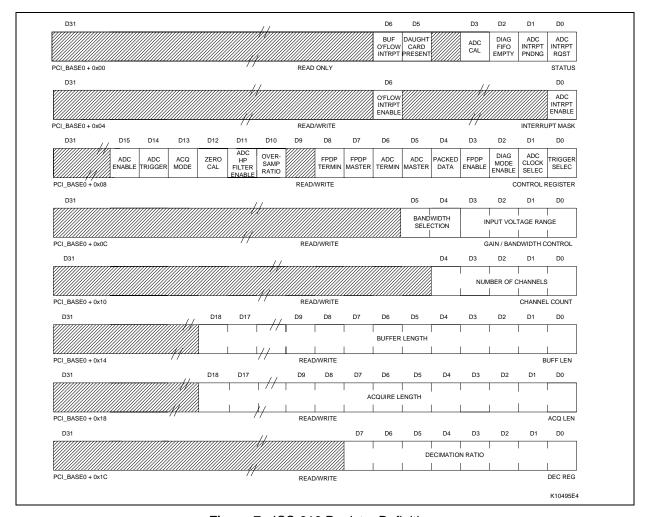

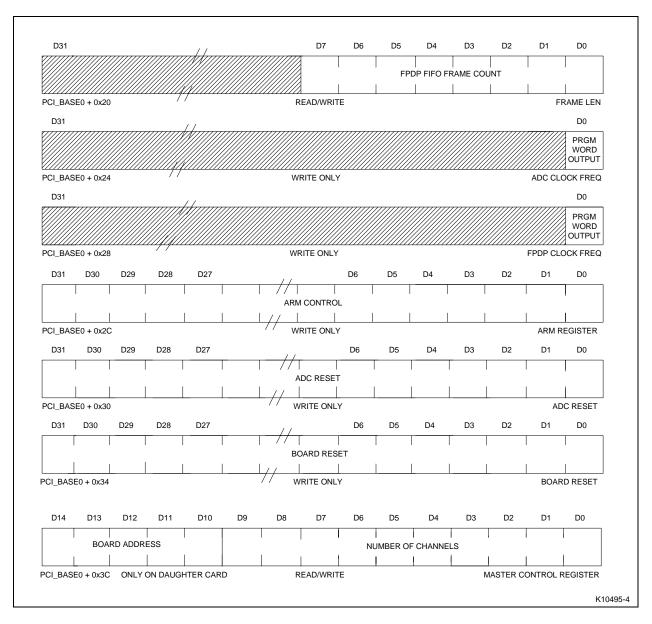

The ICS-610 PCI Bus Memory and I/O Map are shown in Table 5.1 below. The individual bit fields of the registers are shown in Figure 7 and Figure 8. Detailed register descriptions are given in the following sections. All programming and control of the ICS-610 is accomplished through the PCI Bus interface using 32-bit transfers. All control register bits that are not defined have no effect on the operation of the ICS-610. All undefined bits may be read as zero or one.

### 5.1 General Notes

Individual bits in the 32-bit registers are referred to in braces. e.g. CR<00> corresponds to ICS-610 Control register bit 0, and MCR<09:00> refers to Master Control register bits 9 through 0, inclusive.

Table 5.1 - ICS-610 Memory Map

| Register                  | PCI Bus Address        | Туре                 |

|---------------------------|------------------------|----------------------|

| V360EPC Configuration     | PCI_IO_BASE            | Read/Write           |

| ICS-610 Register Set      | PCI_BASE0 + 0x00000000 |                      |

| ADC Data/Diagnostics area | PCI_BASE1 + 0x80000000 | Read Only/Write Only |

| DMA Chain Memory          | PCI_BASE1 + 0xE0000000 | Read/Write           |

Figure 7 - ICS-610 Register Definitions

Figure 8 - ICS-610 Register Descriptions (Cont'd)

### 5.2 V360EPC Registers

The ICS-610 uses the V3 Semiconductor V360EPC PCI bus interface chip to handle all PCI bus communications. Full details of the V360EPC may be found in the V360EPC PCI Controller Data Book (see Reference [3]). Descriptions of the V360EPC registers, that may be needed when programming the ICS-610, are given in Table 5.2.

As with any PCI Bus device, the V360EPC has a unique 256-Byte region called the Configuration Header Space, or just Configuration Space (see Reference [3]). It is mandatory that portions of this configuration header are addressable in order for a PCI agent to be in full compliance with the PCI specification.

Following power-up, the V360EPC downloads the contents of the Configuration Space from an EEPROM device on the ICS-610. These values can be read at any time after power-up. The operating system may modify parts of them.

Five registers are used to define the PCI Bus base addresses and address ranges (sizes) of the three apertures used for access to the V360EPC and the ICS-610 register and data areas. The operating system must perform configuration of PCI Bus devices following power up in order to establish and configure these registers. The user cannot access the ICS-610 until this process has been completed.

PCI IO BASE: Base address of Configuration Space. Points to the V360EPC register set. This

register is referred to as PCI BAR0 in the PCI specification.

PCI\_BASE0: Base address of aperture 0. Points to the ICS-610 register set. This register is

referred to as PCI BAR1 in the PCI specification.

PCI\_BASE1: Base address of aperture 1. Points to the ADC Data/Diagnostic area. This register is

referred to as PCI BAR2 in the PCI specification.

PCI\_MAP0: Defines the range (size) of aperture 0 and mapping address. PCI\_MAP1: Defines the range (size) of aperture 1 and mapping address.

The vendor and device identification information is contained in address offsets 0x2C and 0x2E, respectively, from the base of the configuration register area. These 16-bit read-only registers contain the following information:

Sub-Vendor Identification 0x1464 Sub-Device Identification 0x0610

Other relevant register descriptions are given in Table 5.2. For a full description of the V360EPC register set, consult Reference [3].

Each bit in the V360EPC registers is readable and writable according to one of the following designations. Those marked with an asterisk (\*) apply to the PCI Configuration Registers only and comply with the PCI specification to provide the required PCI configuration header.

R: Read only – bits are internally driven and cannot be modified.

**FR\*:** Firmware Initialized, Configuration Read Only – these bits are initialized after a system reset by downloading via the serial EEPROM device or by the local bus master. Once 'FR' bits are loaded they may be locked from further modification by setting the LOCK bit in the SYSTEM register.

W: Write only. Typically used to issue commands.

**FRW\*:** Firmware Initialized, Configuration Read/Write – Initialized at boot-time but can be either read or written from the PCI and Local buses.

RW: Read and Write.

All reserved register bits read back as zeros.

Table 5.2 - V360EPC Operation Register Descriptions

| Register                | Mnemonic  | Туре | Reset Value | Offset | Description                       |                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|-----------|------|-------------|--------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI_VENDOR              | VENDOR    | FR   | 11B0H       | 0x00   | Vendor ID (V3 Semiconductor Inc.) |                                                                                                                                                                                                                                                                                                                                                                                     |

| PCI_DEVICE              | DEVICE    | FR   | see text    | 0x02   | Device ID Reads bad               | ck as a value representing V360EPC.                                                                                                                                                                                                                                                                                                                                                 |

| PCI_CMD                 |           |      |             | 0x04   | This is a register requ           | uired by the PCI specification                                                                                                                                                                                                                                                                                                                                                      |

| PCI Command<br>Register | -         | R    | 0H          |        | PCI_CMD <15:10>                   | Reserved.                                                                                                                                                                                                                                                                                                                                                                           |

|                         | FBB_EN    | FRW  | 0H          |        | PCI_CMD <09>                      | Fast Back-to-Back Enable.  1 = EPC will perform fast back-to-back transfers when bus master.  0 = EPC will not perform back-to-back transfers.                                                                                                                                                                                                                                      |

|                         | SERR_EN   | FRW  | 0H          |        | PCI_CMD <08>                      | System Error Enable. Enable system error. If PAR_En (bit 6) is also enabled, then /SERR is driven in response to an address parity error.                                                                                                                                                                                                                                           |

|                         | -         | R    | 0H          |        | PCI_CMD <07>                      | Reserved.                                                                                                                                                                                                                                                                                                                                                                           |

|                         | PAR_EN    | FRW  | 0H          |        | PCI_CMD <06>                      | Parity Error Enabled. When set, EPC will report PCI parity errors.                                                                                                                                                                                                                                                                                                                  |

|                         | -         | R    | 0H          |        | PCI_CMD <05>                      | Reserved.                                                                                                                                                                                                                                                                                                                                                                           |

|                         | -         | R    | 0H          |        | PCI_CMD <04>                      | Reserved.                                                                                                                                                                                                                                                                                                                                                                           |

|                         | -         | R    | 0H          |        | PCI_CMD <03>                      | Reserved.                                                                                                                                                                                                                                                                                                                                                                           |

|                         | MASTER_EN | FRW  | ОН          |        | PCI_CMD <02>                      | PCI Master Enable. When set, V360EPC will act as PCI Bus master (i.e. assert /REQ). (Note: Clearing this bit effectively prohibits any local bus reads/writes to PCI space. If PCI Bus mastering is disabled, all local bus writes to PCI space, and all DMA transfers destined for PCI space, will be queued in the Local-to-PCI FIFO until this bit is set, or the FIFO is full). |

|                         | MEM_EN    | FRW  | 0H          |        | PCI_CMD <01>                      | Memory Access Enable. When set, V360EPC will respond to memory accesses on the PCI Bus.                                                                                                                                                                                                                                                                                             |

| Register | Mnemonic  | Туре | Reset Value | Offset |                  | Description                                                                                                                                                                                                                                                                                    |

|----------|-----------|------|-------------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | IO_EN     | FRW  | 0H          |        | PCI_CMD <00>     | I/O Access Enable. When set, V360EPC will respond to I/O accesses on the PCI Bus.                                                                                                                                                                                                              |

| PCI_STAT | PAR_ERR   | FRW  | ОН          | 0x06   | PCI_STAT <15>    | Parity Error Enable. Set (1) in response to a parity being detected on the PCI Bus. Cleared by writing '1' to this bit.                                                                                                                                                                        |

|          | SYS_ERR   | FRW  | OН          |        | PCI_STAT <14>    | System Error. Set (1) in response to system error being detected by this device and reported on the /SERR pin on the PCI Bus. Cleared by writing '1' to this bit.                                                                                                                              |

|          | M_ABORT   | FRW  | OН          |        | PCI_STAT <13>    | Master Abort. Set (1) in response to a master abort being detected during transaction in which the EPC was acting as a bus master. Cleared by writing '1' to this bit.                                                                                                                         |