In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/60477-1

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

Your **definitive** source for quality pre-owned equipment.

**Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

## VMIVME-1160A

# 32-bit OPTICALLY COUPLED DIGITAL INPUT BOARD WITH CHANGE-OF-STATE DETECTION

## **INSTRUCTION MANUAL**

DOCUMENT NO. 500-101160-000 C

Revised June 18, 1999

VMIC, Inc. 12090 SOUTH MEMORIAL PARKWAY HUNTSVILLE, AL 35803-3308 (256) 880-0444 Fax: (256) 882-0859 1-800-322-3616

#### COPYRIGHT AND TRADEMARKS

© Copyright July 1991. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, Instant OPC wizard logo, IOWorks Access, IOWorks Foundation, IOWorks man figure, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(ler), VMEaccess, VMEmanager, VMEmonitor, VMEnet, VMEnet II, and VMEprobe are trademarks and The I/O Experts, The I/O Systems Experts, The Soft Logic Experts, and The Total Solutions Provider are service marks of VMIC.

(Instant OPC wizard logo)

(IOWorks man figure)

The I/O man figure, IOWorks, UIOC, Visual IOWorks, the VMIC logo, and WinUIOC are registered trademarks of VMIC.

ActiveX, Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

Celeron and MMX are trademarks and Intel and Pentium are registered trademarks of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers' Group.

Other registered trademarks are the property of their respective owners.

#### **VMIC** All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless granted express written permission from VMIC.

| WAIL. |  |

|-------|--|

|       |  |

## **RECORD OF REVISIONS**

| REVISION LETTER                                                         |

|-------------------------------------------------------------------------|

| B 02/16/94 Cover, pages ii and 5-5 94-0210                              |

| 1 1                                                                     |

| C 06/18/99 Cover, pages ii, v, vi, vii, 5-2, 5-3, and Section 6 99-0551 |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

| MIC, Inc.  BEVITE PAGE NO                                               |

VMIC, Inc.

REV LTR

PAGE NO.

12090 South Memorial Parkway •

DOC. NO. 500-101160-000

C

ii

Huntsville, AL 35803-3308 • (256) 880-0444

DOC. NO. 500-101160-000

C

ii

### VMIC SAFETY SUMMARY

THE FOLLOWING GENERAL SAFETY PRECAUTIONS MUST BE OBSERVED DURING ALL PHASES OF THE OPERATION, SERVICE, AND REPAIR OF THIS PRODUCT. FAILURE TO COMPLY WITH THESE PRECAUTIONS OR WITH SPECIFIC WARNINGS ELSEWHERE IN THIS MANUAL VIOLATES SAFETY STANDARDS OF DESIGN, MANUFACTURE, AND INTENDED USE OF THIS PRODUCT. VME MICROSYSTEMS INTERNATIONAL CORPORATION ASSUMES NO LIABILITY FOR THE CUSTOMER'S FAILURE TO COMPLY WITH THESE REQUIREMENTS.

#### GROUND THE SYSTEM

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

#### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

#### KEEP AWAY FROM LIVE CIRCUITS

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### DO NOT SERVICE OR ADJUST ALONE

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### DO NOT SUBSTITUTE PARTS OR MODIFY SYSTEM

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VME Microsystems International Corporation for service and repair to ensure that safety features are maintained.

#### DANGEROUS PROCEDURE WARNINGS

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

**WARNING**

DANGEROUS VOLTAGES, CAPABLE OF CAUSING DEATH, ARE PRESENT IN THIS SYSTEM. USE EXTREME CAUTION WHEN HANDLING, TESTING, AND ADJUSTING.

#### SAFETY SYMBOLS

#### GENERAL DEFINITIONS OF SAFETY SYMBOLS USED IN THIS MANUAL

Instruction manual symbol: the product is marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect against damage to the system.

Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1000 volts are so marked).

Protective conductor terminal. For protection against electrical shock in case of a fault. Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment.

Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as well as providing protection against electrical shock in case of a fault. Before operating the equipment, terminal marked with this symbol must be connected to ground in the manner described in the installation (operation) manual.

Frame or chassis terminal. A connection to the frame (chassis) of the equipment which normally includes all exposed metal structures.

Alternating current (power line).

Direct current (power line).

Alternating or direct current (power line).

WARNING

The WARNING sign denotes a hazard. It calls attention to a procedure, a practice, a condition, or the like, which, if not correctly performed or adhered to, could result in injury or death to personnel.

The CAUTION sign denotes a hazard. It calls attention to an operating a procedure, a practice, a condition, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system.

NOTE:

The NOTE sign denotes important information. It calls attention to a procedure, a practice, a condition or the like, which is essential to highlight.

## VMIVME-1160A

## 32-bit OPTICALLY COUPLED DIGITAL INPUT BOARD WITH CHANGE-OF-STATE DETECTION

## TABLE OF CONTENTS

| SECTIO            | ON 1                      | INTRODUC'                              | TION                      |             |                   | !               | <u>Page</u>        |

|-------------------|---------------------------|----------------------------------------|---------------------------|-------------|-------------------|-----------------|--------------------|

| SECTION           |                           |                                        |                           |             |                   |                 |                    |

| 1.1<br>1.2<br>1.3 | FUNCT                     | IONAL DESC                             | RIPTION<br>RIAL LIST      |             | ***************** | ******          | 1-3                |

| SECTIO            | ON 2.                     | PHYSICAL                               | DESCRIPTION               | DN AND      | SPECIFIC          | ATIONS          |                    |

| SECTIO            | ON 3.                     | THEORY OF                              | OPERATIO                  | N           |                   |                 |                    |

| 3.1<br>3.2<br>3.3 | BLOCK<br>INTERF<br>PRIORI | DIAGRAMS<br>RUPT FUNCTI<br>TY INTERRUI | ONSPT SUBSYSTE            | EM          |                   |                 | 3-1<br>3-1<br>3-11 |

| SECTIO            | ON 4.                     | PROGRAMI                               | <b>MING</b>               |             |                   |                 |                    |

| 4.1<br>4.2        | OPERAT                    | TIONAL OVER<br>L PROGRAMN              | VIEW                      | <br>E       | ••••••            |                 | 4-1<br>4-6         |

| SECTIO            | ON 5.                     | CONFIGUR                               | ATION AND                 | INSTALL     | ATION             |                 |                    |

| 5.1               | UNPAC                     | KING PROCE                             | DURES                     |             |                   |                 | 5-1                |

| 5.2               |                           |                                        | ATION                     |             |                   |                 |                    |

| 5.3               | CONFI                     | <b>GURATION S</b> 1                    | WITCHES                   |             |                   |                 | 5-1                |

| 5.4               | CURRE                     | NT SENSE, \                            | OLTAGE SOL                | JRCE SEL    | ECTION            |                 | 5-3                |

| 5.5               |                           |                                        | VOLTAGE                   |             |                   |                 |                    |

| 5.6               | ADDRE                     | SS MODIFIE                             | RS<br>ON SWITCHE          |             | •••••             | ,               | 5-3                |

| 5.7               |                           |                                        | ON SWITCHE<br>ONFIGURATIO |             |                   |                 |                    |

| 5.8<br>5.9        |                           | EUTUR PIN U                            | NT PANEL CC               | NINECTO     | R CONFIGUR        | RATION          | 5-4<br>5-5         |

| J. <del>J</del>   |                           | THE WIND LUC                           | IN LEVINER OF             | NAINFO I OL | I CONFIGU         | . 1/7 I I () (N | 0                  |

## TABLE OF CONTENTS (CONTINUED)

| SECTIO                                                                                                                                        | ON 6. MAINTENANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 6.1<br>6.2                                                                                                                                    | MAINTENANCE MAINTENANCE PRINTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-1<br>3-1                                                                               |

|                                                                                                                                               | LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                          |

| <u>Figure</u>                                                                                                                                 | <u>Pa</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <u>ige</u>                                                                               |

| 1.1-1<br>3.1-2<br>3.1-3<br>3.1-4<br>3.1-5<br>3.1-6<br>3.1-7<br>3.1-8<br>3.1-9<br>3.1-10<br>4.1-1<br>5.6-1<br>5.7-1<br>5.8-1<br>5.9-2<br>5.9-3 | Typical COSMODULE™ Functional Block Diagram.  VMIVME-1160A Functional Block Diagram.  Address Section Block Diagram.  Control Section Block Diagram.  Data Section Block Diagram.  VMEbus Signal Lines Used by the VMIVME-1160A.  BIM Foundation Section Block Diagram.  Typical IER Logic Section.  Typical Change-of-State Detection Logic Section.  Input Data Registers Block Diagram.  Signal Conditioning Block Diagram.  Signal Conditioning Block Diagram.  VMIVME-1160A Programming Flow Diagram.  Locations of Jumpers and Address Switches.  I/O Access Mode Selection.  Data Register Address Select Switches.  Typical Input Channel.  Cable Connector Configuration.  P3 Connector Pin Layout. | 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-15<br>5-2<br>5-4<br>5-6<br>5-7 |

|                                                                                                                                               | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                          |

| <u>Table</u>                                                                                                                                  | <u>Pa</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <u>age</u>                                                                               |

| 1.1-1<br>4.1-1<br>4.1-2<br>4.1-3<br>4.1-4<br>5.9-1<br>5.9-2                                                                                   | COSMODULE™ Product Line Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-1<br>4-2<br>4-3<br>4-4<br>5-9                                                          |

## **TABLE OF CONTENTS (Concluded)**

## **APPENDICES**

- Assembly Drawing, Parts List, and Schematic MC68153 BIM Data Sheet Α

- В

## SECTION 1 INTRODUCTION

#### 1.1 INTRODUCTION

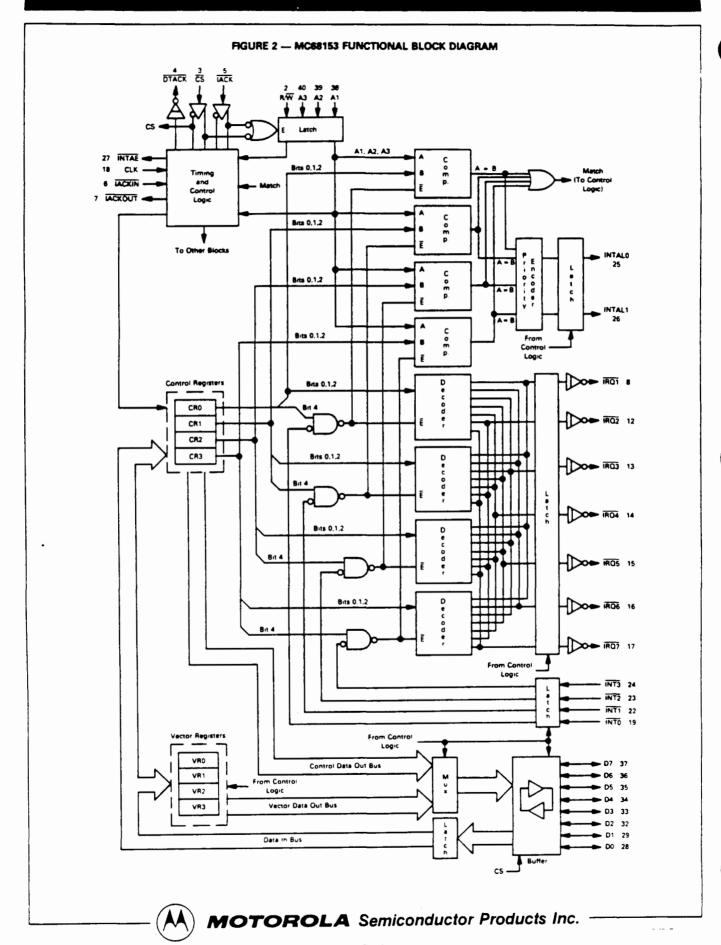

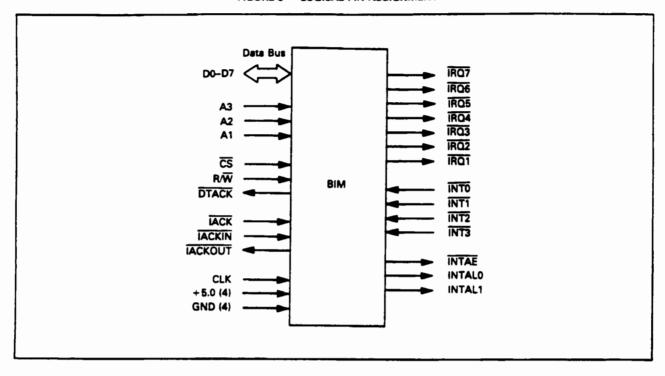

The VMIVME-1160A is designed with standard Change-of-State (COS) control and interrupt logic that detects any COS and provides an interrupt vector to the byte level. It incorporates an MC68153 Bus Interrupter Module (BIM) and interrupts are supported on any of seven levels.

Each byte (8 bits) of input may have a unique interrupt vector that is generated upon a COS in any bit of that byte. This product also has an Interrupt Enable Register which is used to allow interrupts to be enabled on a byte-by-byte basis. The input data may be accessed as a D8 or D16 transfer.

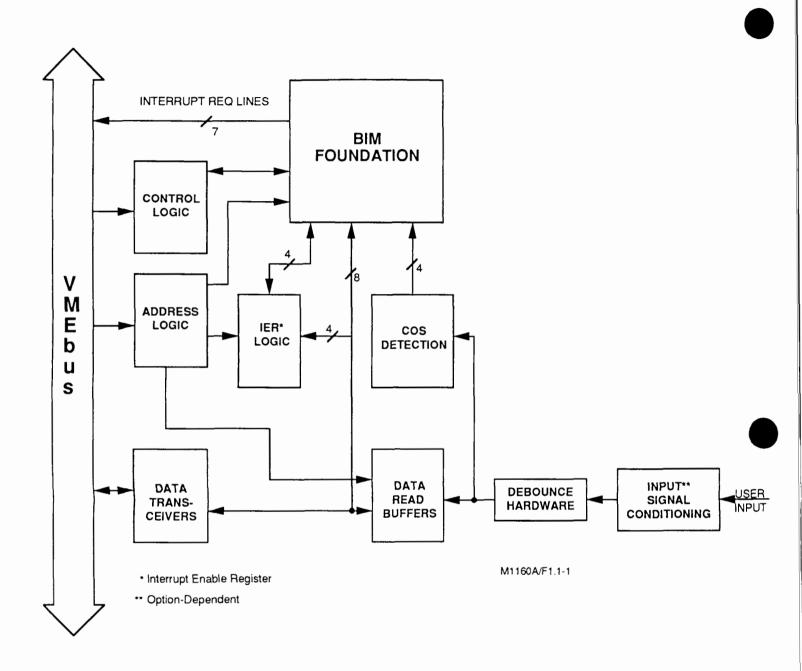

A functional block diagram of this product is shown in Figure 1.1-1. Interrupts are generated on any COS (positive or negative transition). Polarity is determined by reading the input port after the COS interrupt.

#### NOTE

STATE CHANGES THAT OCCUR DURING THE INTERRUPT PROCESSING WINDOW (INTERNAL REQUEST TO INTERRUPT ACKNOWLEDGE CYCLE COMPLETE) WILL NOT BE DETECTED. THE TIME BETWEEN USER INPUT STATE CHANGES MUST NOT BE LESS THAN THE COMPUTER INTERRUPT PROCESSING TIME; OTHERWISE, THE STATE CHANGES WILL BE LOST.

A Change-of-State Application Guide that describes the complete COSMODULE<sup>TM</sup> product line, VMIC's Document No. 825-000000-002, is available from VMIC. A summary of the COSMODULE<sup>TM</sup> product line is provided in Table 1.1-1 for reference.

Figure 1.1-1. Typical COSMODULE™ Functional Block Diagram

Table 1.1-1. COSMODULE™ Product Line Summary

| ITEM<br>NO. | DESCRIPTION                                                                                                  | MODEL<br>NO. | TRANSFER<br>Type |

|-------------|--------------------------------------------------------------------------------------------------------------|--------------|------------------|

| 1.          | 16-Channel AC or DC High Voltage<br>(5 V to 240 V) Optically Coupled<br>Input with Change-of-State Interrupt | VMIVME-1001  | D8,D16           |

| 2.          | 32-bit TTL Digital Input with Change-of-State Interrupt                                                      | VMIVME-1101  | D8,D16           |

| 3.          | 32-bit High Voltage (5 to 50 V) Digital Input with Change-of-State Interrupt                                 | VMIVME-1180  | D8,D16           |

| 4.          | 32-bit High Voltage (1 to 66 V) COS board with Data Capture Registers and Built-in-Test                      | VMIVME-1181  | D8,D16,D32       |

| 5.          | 32-bit Optically Coupled Digital Input with Change-of-State Interrupt                                        | VMIVME-1160A | D8,D16           |

M1160A/T1.1-1

#### 1.2 FUNCTIONAL DESCRIPTION

The VMIVME-1160A provides 32 high voltage, optically coupled inputs with change-of-state detection and vectoring to the byte level. The interrupt functions are supported by an MC68153 Bus Interrupter Module. The major features of the VMIVME-1160A are:

- a. Quad 8-bit ports

- b. Change-of-State port identified with interrupt vector

- c. Voltage sourcing or contact sensing signal conditioning

- d. Double-height Eurocard form factor with front panel

- e. 8- or 16-bit data transfers

- f. 64-pin DIN type input connector

- g. Jumper-selectable nonprivileged short I/O, supervisory short I/O, or both

- h. 32 optically coupled inputs

#### 1.3 REFERENCE MATERIAL LIST

The reader should refer to "The VMEbus Specification" for a detailed explanation of the VMEbus. "The VMEbus Specification" is available from the following source:

VITA

VMEbus International Trade Association

10229 N. Scottsdale Road

Scottsdale, AZ 85253

(602) 951-8866

The following Application and Configuration Guides are available from VMIC to assist the user in the selection, specification, and implementation of systems based on VMIC's products:

| TITLE                                                     | <b>DOCUMENT</b> |

|-----------------------------------------------------------|-----------------|

| NO.                                                       |                 |

| Digital Input Board Application Guide                     | 825-000000-000  |

| Change-of-State Application Guide                         | 825-000000-002  |

| Digital I/O (with Built-in-Test) Product Line Description | 825-000000-003  |

| Connector and I/O Cable Application Guide                 | 825-000000-006  |

## SECTION 2 PHYSICAL DESCRIPTION AND SPECIFICATIONS

REFER TO 800-101160-000 SPECIFICATION

#### SECTION 3

## THEORY OF OPERATION

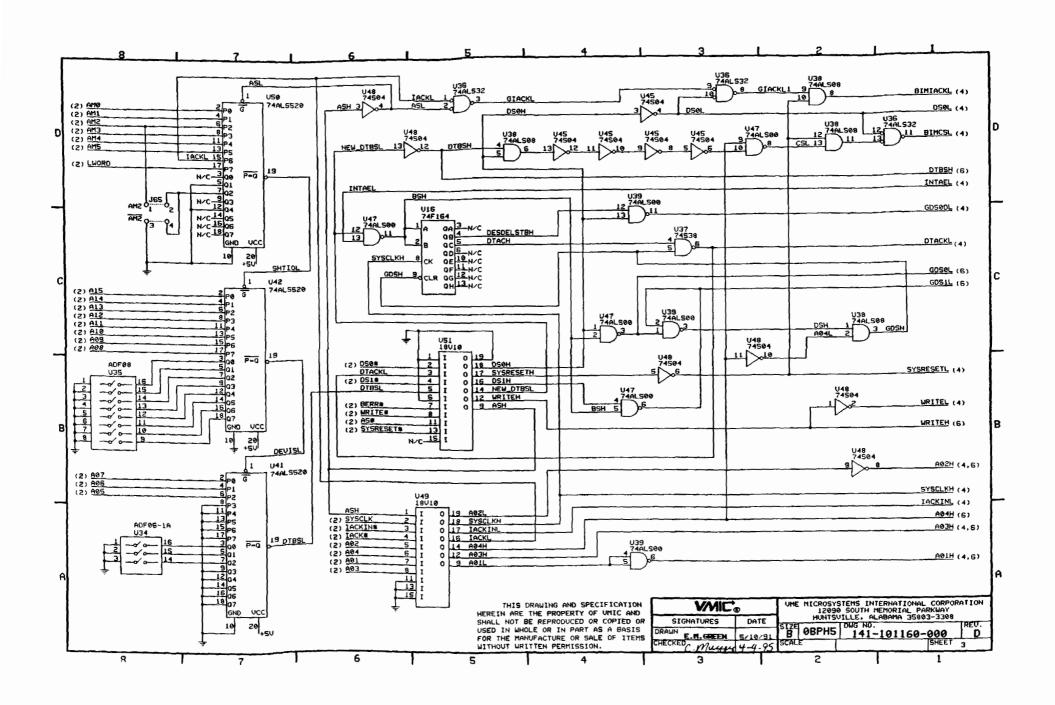

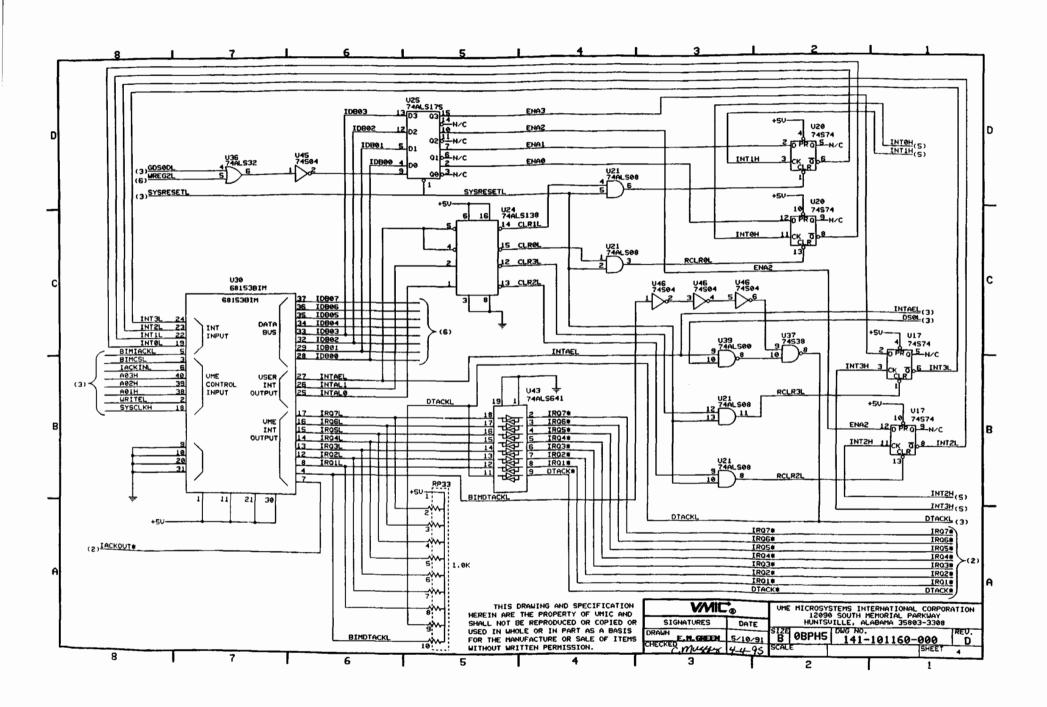

#### 3.1 BLOCK DIAGRAMS

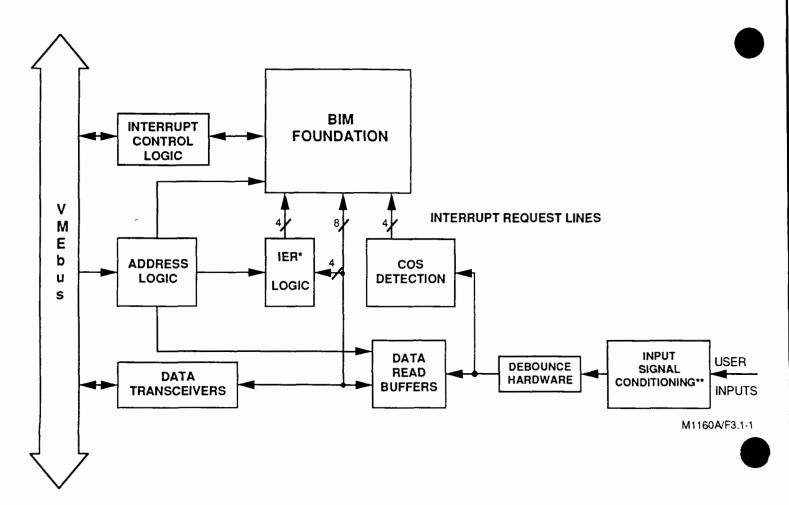

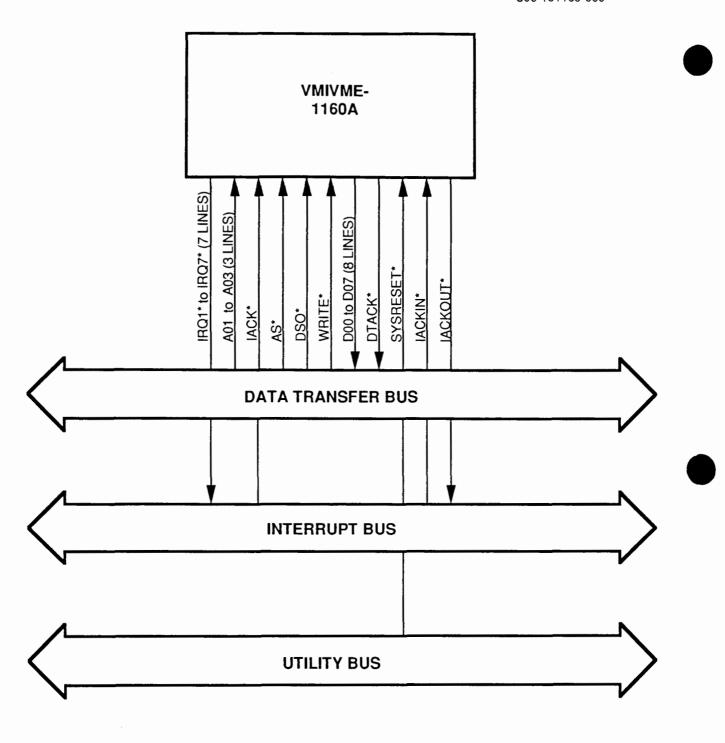

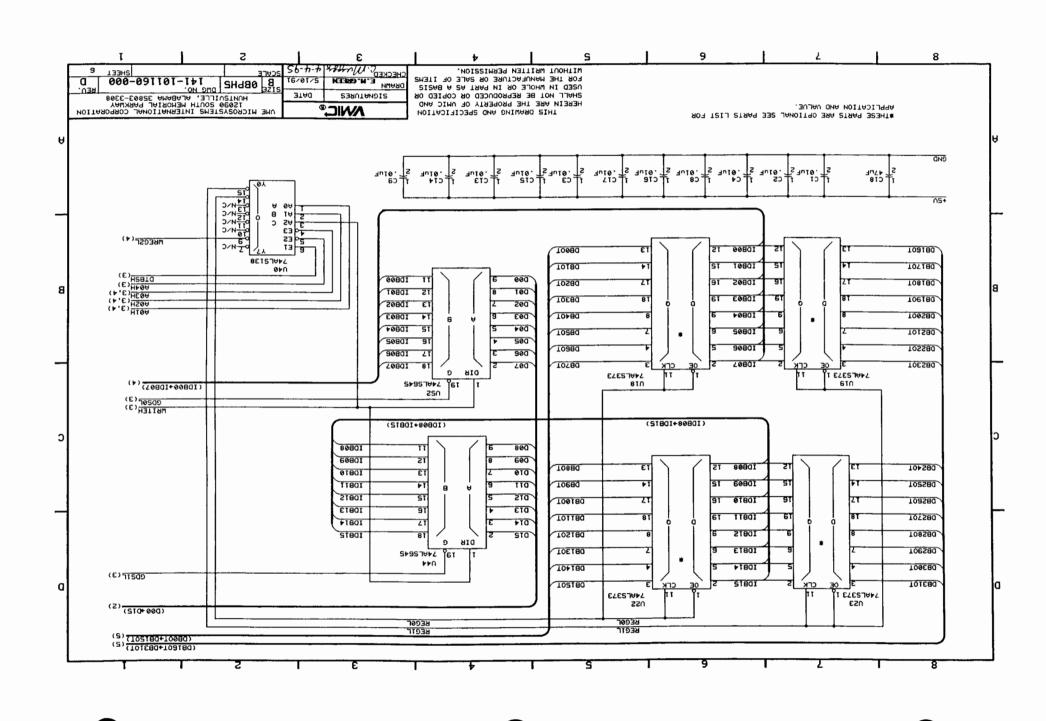

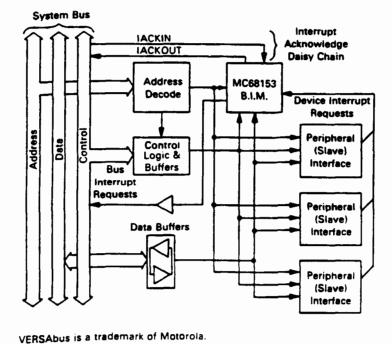

The VMIVME-1160A consists of eight functional building blocks as illustrated in Figure 3.1-1. The eight sections of the VMIVME-1160A are: (1) Address Logic; (2) Control Logic; (3) Data Logic; (4) Bus Interrupter Module (BIM) Logic; (5) Interrupt Enable Logic; (6) Change-of-State Detection Logic; (7) Input Data Registers; and (8) Input Buffers. Each section of the design is illustrated in further detail in Figures 3.1-2 through 3.1-10.

#### 3.2 INTERRUPT FUNCTIONS

Interrupts are generated on any Change-of-State (positive or negative transition). The polarity is determined by reading the input port after a Change-of-State interrupt occurs.

#### NOTE

STATE CHANGES THAT OCCUR DURING THE INTERRUPT PROCESSING WINDOW (INTERNAL REQUEST TO INTERRUPT ACKNOWLEDGE CYCLE COMPLETE) WILL NOT BE DETECTED. THE TIME BETWEEN USER INPUT STATE CHANGES MUST NOT BE LESS THAN THE COMPUTER INTERRUPT PROCESSING TIME; OTHERWISE, THE STATE CHANGES WILL BE LOST.

The reader should refer to "The VMEbus Specification" for a detailed explanation of the priority interrupt bus. "The VMEbus Specification" is available from the following source:

VITA

VMEbus International Trade Association

10229 N. Scottsdale Road

Scottsdale, AZ 85253

(602) 951-8866

The data transfer bus, the arbitration bus, and the interrupt bus are all used in the process of generating and handling bus interrupts.

<sup>\*</sup>Internal Enable Register

Figure 3.1-1. VMIVME-1160A Functional Block Diagram

<sup>\*\*</sup> Option Dependent

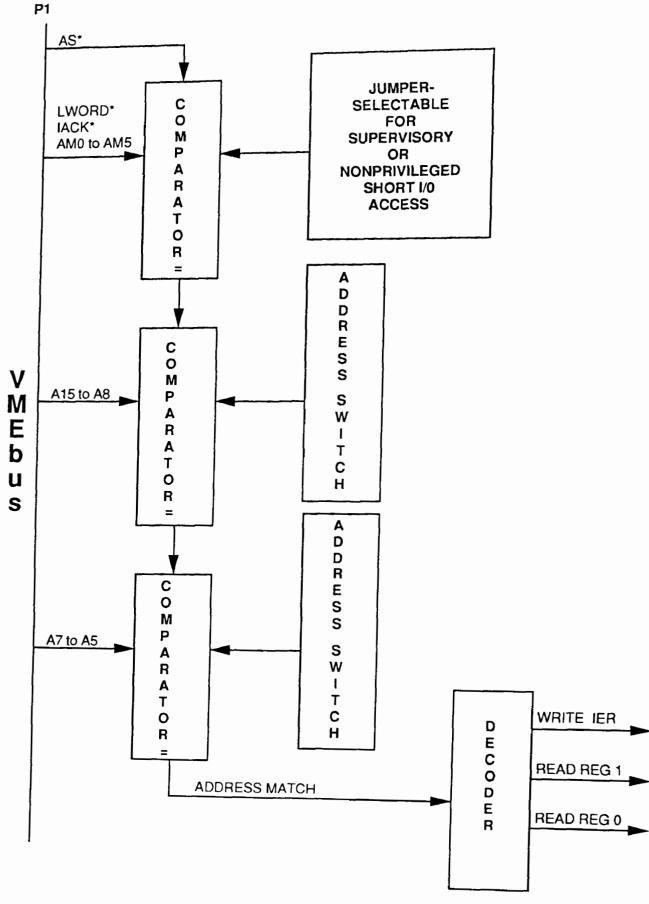

Figure 3.1-2. Address Section Block Diagram

M1160A/F3.1-2

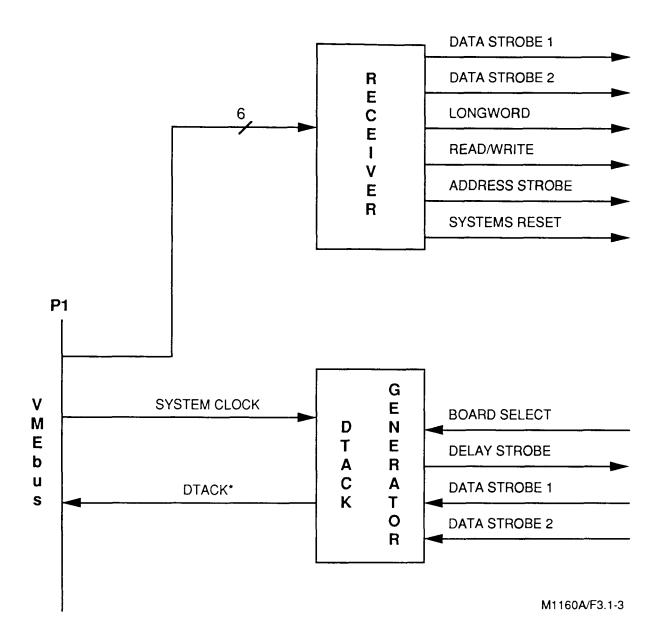

Figure 3.1-3. Control Section Block Diagram

M1160A/F3.1-4

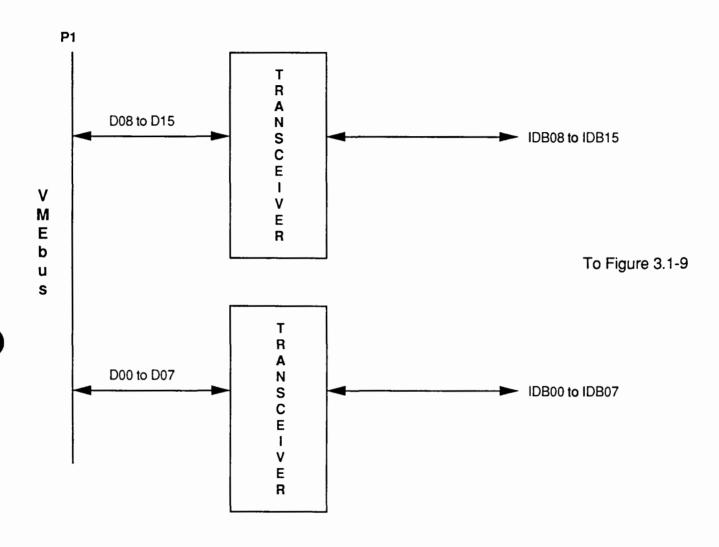

Figure 3.1-4. Data Section Block Diagram

M1160A/F3.1-5

Figure 3.1-5. VMEbus Signal Lines Used by the VMIVME-1160A

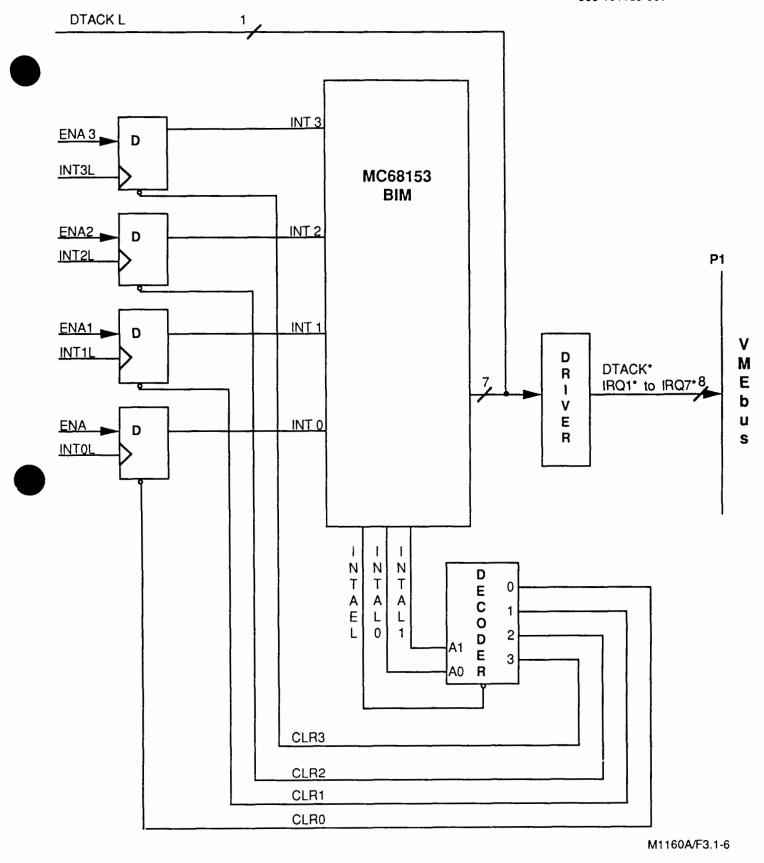

Figure 3.1-6. BIM Foundation Section Block Diagram

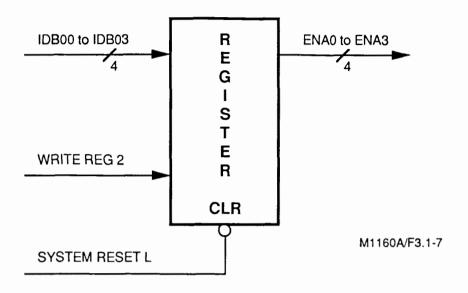

Figure 3.1-7. Typical IER Logic Section

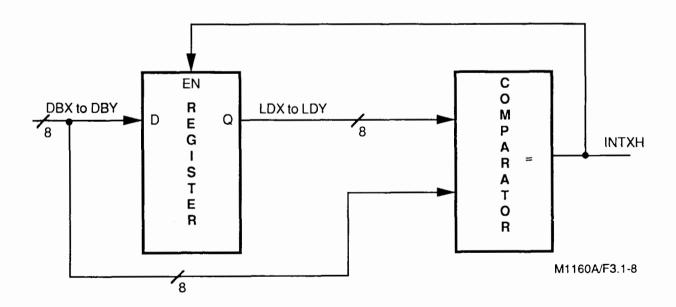

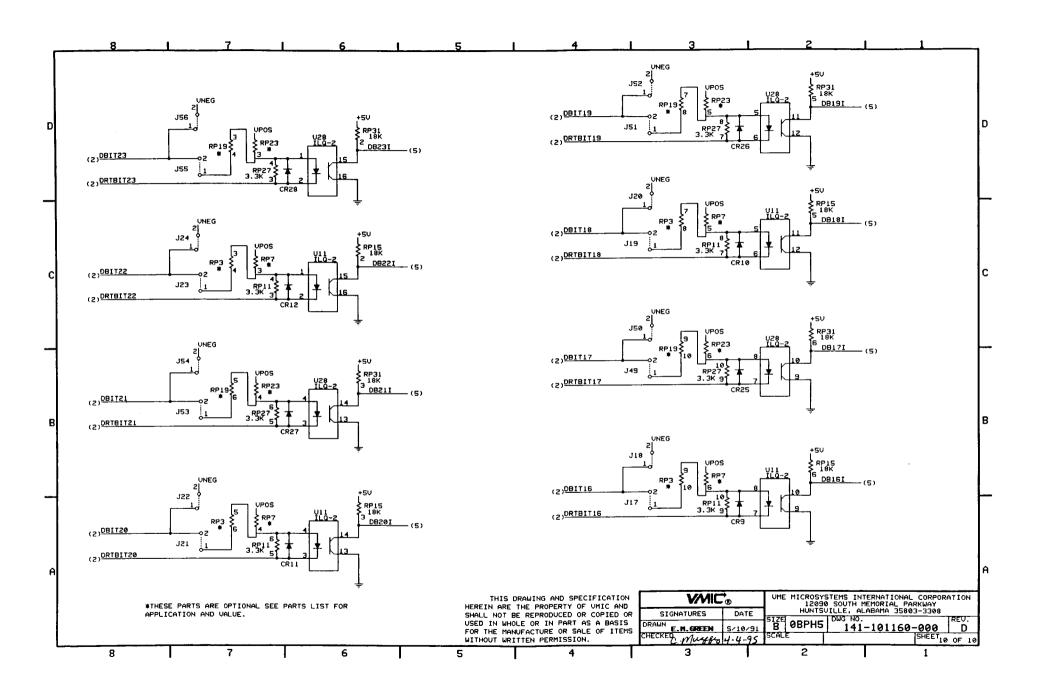

Figure 3.1-8. Typical Change-of-State Detection Logic Section

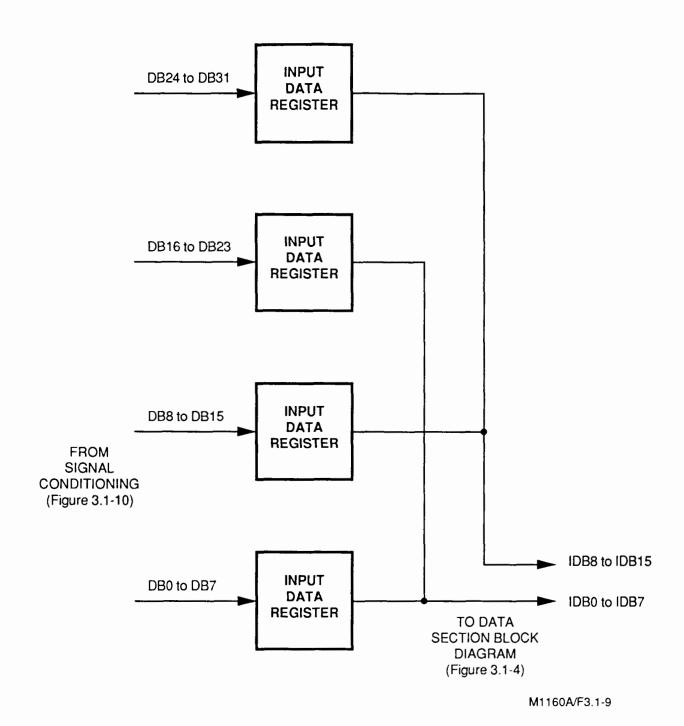

Figure 3.1-9. Input Data Registers Block Diagram

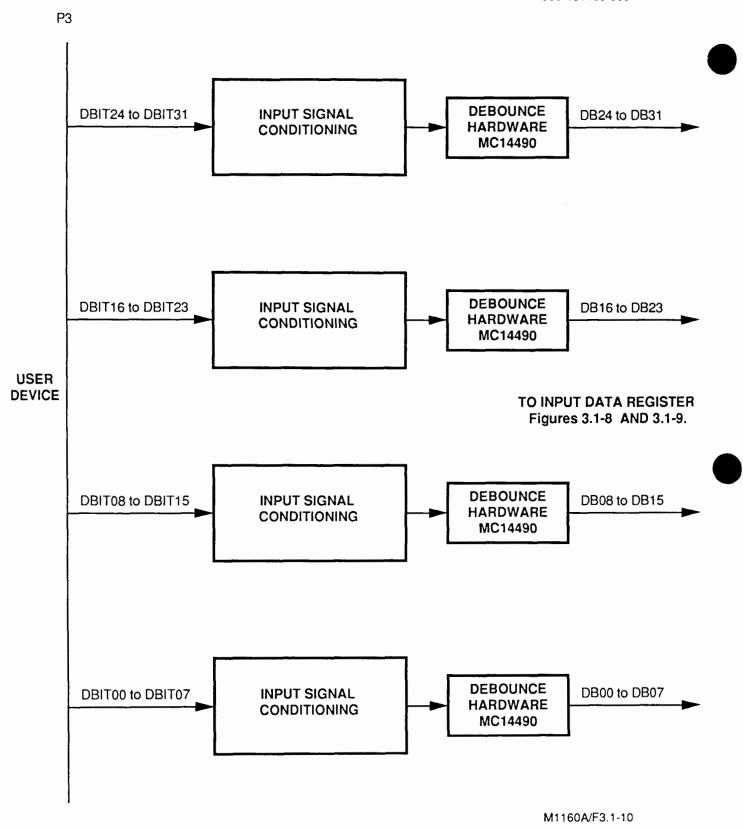

Figure 3.1-10. Signal Conditioning Block Diagram

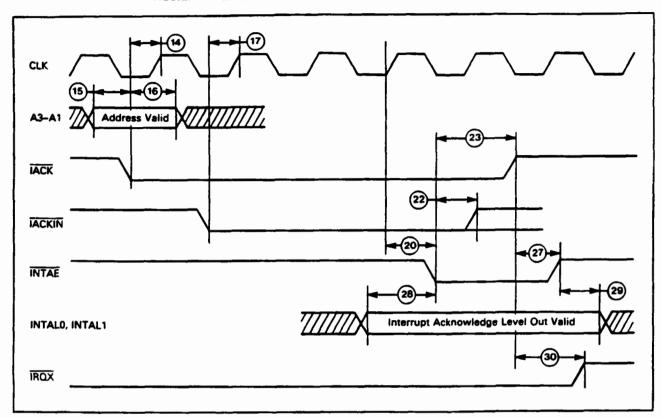

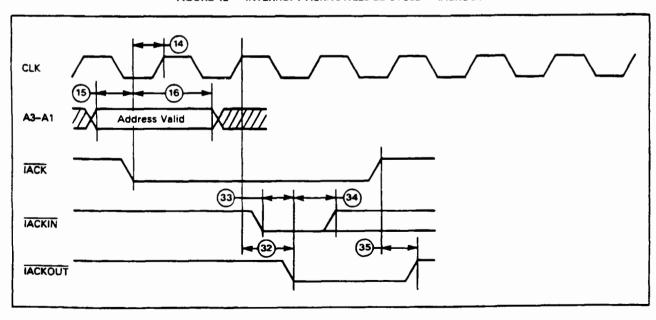

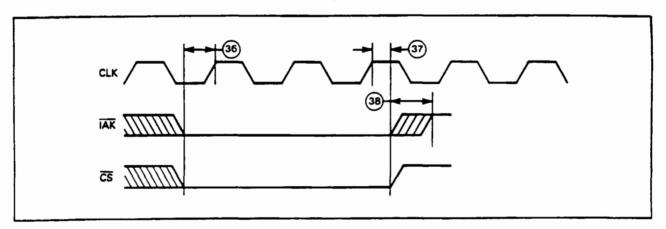

#### 3.3 PRIORITY INTERRUPT SUBSYSTEM

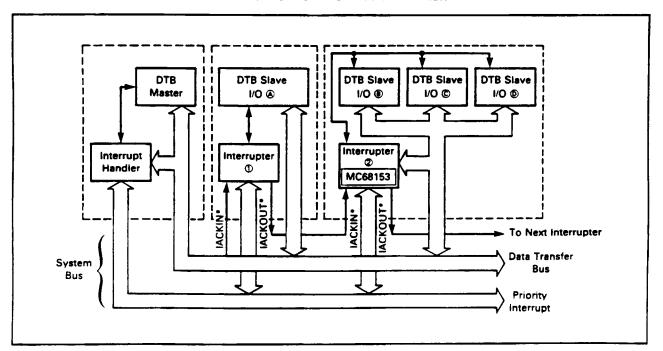

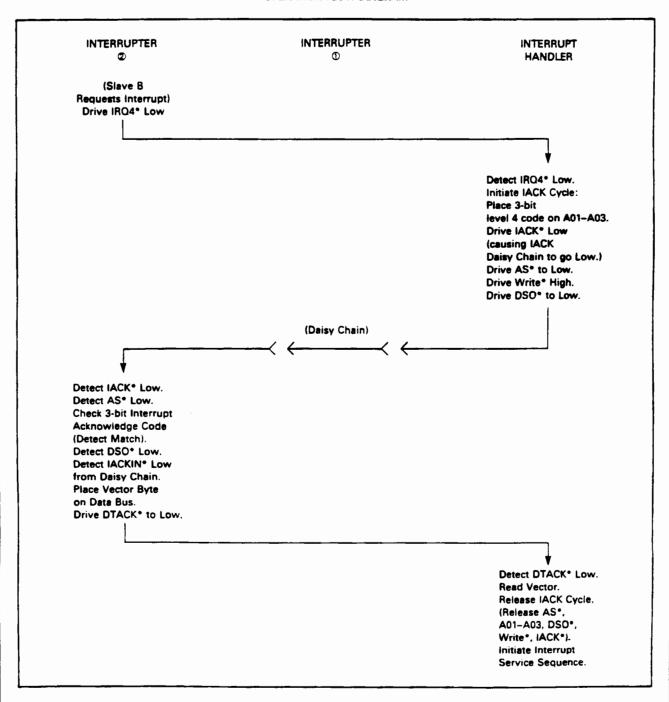

The following overview of the priority interrupt subsystem assumes that the reader understands the operation of both the data transfer bus and the arbitration bus.

The interrupt bus consists of seven interrupt request signal lines, one daisy-chain signal line, and one interrupt acknowledge line:

| IRQ1* | IRQ4* | IRQ7*            |

|-------|-------|------------------|

| IRQ2* | IRQ5* | IACK*            |

| IRQ3* | IRQ6* | IACKIN*/IACKOUT* |

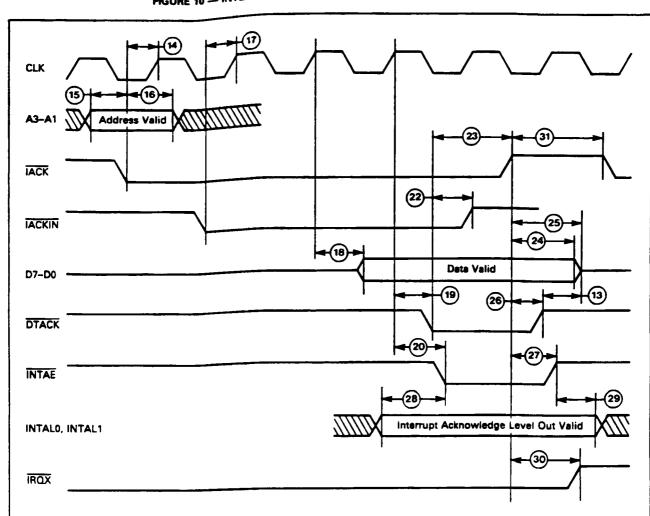

Each interrupt request line may be driven low by the VMIVME-1160A Board or other interrupter to request an interrupt. In a single handler system, these interrupt request lines are prioritized, with IRQ7\* having the highest priority.

The IACK\* line runs the full length of the bus and is connected to the IACKIN\* pin of slot A1. When it is driven low, it initiates a low-going transition down the interrupt acknowledge daisy-chain. This may not occur immediately, since additional constraints are placed on the propagation of IACKIN\*/IACKOUT\*.

Each of the seven interrupt request lines may be shared by two or more interrupter boards. Because of this, some method must be provided to ensure that only one of the boards is acknowledged. This is done by means of the interrupt acknowledge daisy-chain. The daisy-chain line passes through each board on the VMEbus. When an interrupt is acknowledged, IACKIN\* is driven low at slot A1. Each board that is driving an interrupt request line low must wait for the low level down the daisy-chain, thereby guaranteeing that only one board will be acknowledged.

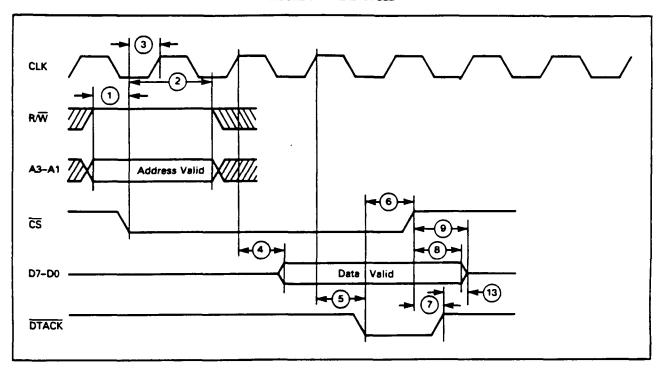

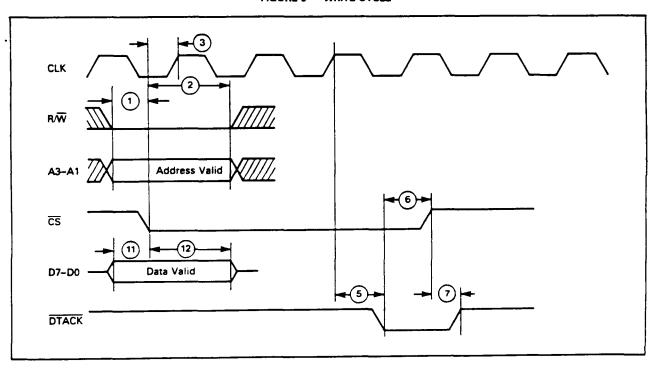

The VMIVME-1160A uses one of the seven IRQX\* lines to request an interrupt. It then monitors the DTB address bus, IACK\*, and the IACKIN\*/IACKOUT\* daisy-chain to determine when its interrupt is being acknowledged. When acknowledged, it places its status/ID byte on the lower eight lines of the data bus and signals the byte's validity to the interrupt handler via the DTACK\* line.

The VMEbus signal lines used by the VMIVME-1160A are shown in Figure 3.1-4.

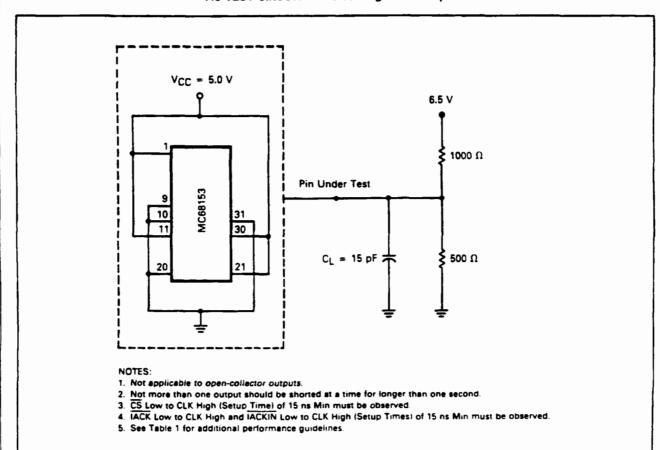

The reader should refer to Appendix B, which contains Motorola's application note on the MC68153, for a detailed explanation of the Bus Interrupter Module (BIM).

## SECTION 4 PROGRAMMING

#### 4.1 OPERATIONAL OVERVIEW

The VMIVME-1160A is designed to provide 32 channels of high voltage, optically coupled inputs with change-of-state detection. Each eight bits (byte) of input may have a unique interrupt vector that is generated upon a change-of-state of any bit in that byte. The VMIVME-1160A also has an Interrupt Enable Register which is used to allow interrupts on change-of-state to be enabled on a byte basis. The channels of input data may be accessed as two 16-bit words or four 8-bit bytes.

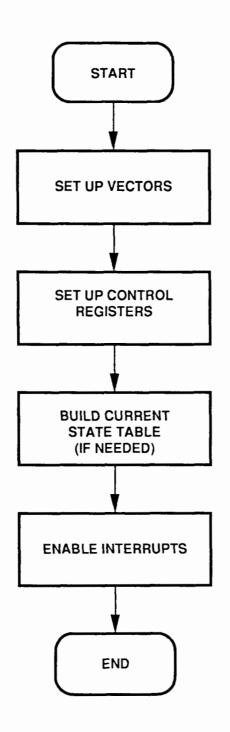

A register map is shown in Table 4.1-1. Detailed register bit definitions are shown in Tables 4.1-2, 4.1-3, and 4.1-4. A typical flow diagram is shown in Figure 4.1-1.

Table 4.1-1. Register Map

| RELATIVE ADDRESS | <u>MNEMONIC</u> | NAME/FUNCTION       |        |           |

|------------------|-----------------|---------------------|--------|-----------|

| \$XX00           | DR0             | Data Register 0     |        |           |

| \$XX01           | DR1             | Data Register 1     |        |           |

| \$XX02           | DR2             | Data Register 2     |        |           |

| \$XX03           | DR3             | Data Register 3     |        |           |

| \$XX05           | IER             | Interrupt Enable Re | gister |           |

| \$XX11           | CR0             | Control Register 0  |        |           |

| \$XX13           | CR1             | Control Register 1  |        |           |

| <b>\$XX</b> 15   | CR2             | Control Register 2  |        | MC68153   |

| \$XX17           | CR3             | Control Register 3  | >      | BIM       |

| \$XX19           | VR0             | Vector Register 0   |        | REGISTERS |

| \$XX1B           | VR1             | Vector Register 1   |        |           |

| \$XX1D           | VR2             | Vector Register 2   |        |           |

| \$XX1F           | VR3             | Vector Register 3   | 1      |           |

|                  |                 |                     | M116   | DA/T4.1-1 |

The reader may want to refer to Appendix B for detailed programming characteristics of the MC68153 BIM.

Table 4.1-2. Typical Input Data Register Bit Maps

| \$XX00 | DRO |

|--------|-----|

|--------|-----|

| BIT 15              | BIT 14     | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 |  |

|---------------------|------------|--------|--------|--------|--------|-------|-------|--|

| INPUT DATA          |            |        |        |        |        |       |       |  |

| ID31                | ID30       | ID29   | ID28   | ID27   | ID26   | ID25  | ID24  |  |

| \$XX01 DR1          | 1          |        |        |        |        |       |       |  |

| BIT 7               | BIT 6      | BIT 5  | BIT 4  | BIT 3  | BIT 2  | BIT 1 | BIT 0 |  |

|                     |            |        | INPUT  | DATA   |        |       |       |  |

| ID23                | ID22       | ID21   | ID20   | ID19   | ID18   | ID17  | ID16  |  |

| \$XX02 DR           | \$XX02 DB2 |        |        |        |        |       |       |  |

| BIT 15              | BIT 14     | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 |  |

|                     |            |        | INPUT  | DATA   |        |       |       |  |

| ID15                | ID14       | ID13   | ID12   | ID11   | ID10   | ID9   | ID8   |  |

| evvos DDs           |            |        |        |        |        |       |       |  |

| \$XX03 DR:<br>BIT 7 | BIT 6      | BIT 5  | BIT 4  | BIT 3  | BIT 2  | BIT 1 | BIT 0 |  |

|                     |            |        | INPUT  | DATA   |        |       |       |  |

| ID7                 | ID6        | ID5    | ID4    | ID3    | ID2    | ID1   | ID0   |  |

## \$XX05 IER

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2   | BIT 1     | BH 0 |

|-------|-------|-------|-------|-------|---------|-----------|------|

|       |       |       |       |       | INTERRU | JPT ENABL | E*   |

|       | RESE  | RVED  |       | DR0   | DR1     | DR2       | DR3  |

M1160A/T4.1-2

<sup>\*</sup> A "one" in the BIT location will enable the interrupts for the stated Data Register.

Table 4.1-3. Typical BIM Control Register Map

## \$XX11 CONTROL REGISTER 0 (Control for DR3 Inputs)

| BIT 7 | BIT 6                 | BIT 5                    | BIT 4         | BIT 3                | BIT 2           | BIT 1 | BIT 0 |

|-------|-----------------------|--------------------------|---------------|----------------------|-----------------|-------|-------|

| FLAG  | FLAG<br>AUTO<br>CLEAR | VECTOR                   | INT<br>ENABLE | INT<br>AUTO<br>CLEAR | INTERRUPT LEVEL |       | VEL   |

| F     | FAC                   | 0=INTERNAL<br>1=EXTERNAL | IRE           | 1=AUTO<br>0=NO       | L2              | L1    | LO    |

## \$XX13 CONTROL REGISTER 1 (Control for DR2 inputs)

| BIT 7 | BIT 6                 | BIT 5                    | BIT 4         | BIT 3                | BIT 2           | BIT 1 | BIT 0 |

|-------|-----------------------|--------------------------|---------------|----------------------|-----------------|-------|-------|

| FLAG  | FLAG<br>AUTO<br>CLEAR | VECTOR                   | INT<br>ENABLE | INT<br>AUTO<br>CLEAR | INTERRUPT LEVEL |       | VEL   |

| F     | FAC                   | 0=INTERNAL<br>1=EXTERNAL | IRE           | 1=AUTO<br>0=NO       | L2 L1 LC        |       | LO    |

#### \$XX15 CONTROL REGISTER 2 (Control for DR1 inputs)

| BIT 7 | BIT 6                 | BIT 5                    | BIT 4         | BIT 3                | BIT 2           | BIT 1 | BIT 0 |

|-------|-----------------------|--------------------------|---------------|----------------------|-----------------|-------|-------|

| FLAG  | FLAG<br>AUTO<br>CLEAR | VECTOR                   | INT<br>ENABLE | INT<br>AUTO<br>CLEAR | INTERRUPT LEVEL |       | VEL   |

| F     | FAC                   | 0=INTERNAL<br>1=EXTERNAL | IRE           | 1=AUTO<br>0=NO       | L2 L1 L0        |       | LO    |

#### \$XX17 CONTROL REGISTER 3 (Control for DR0 inputs)

| BIT 7 | BIT 6                 | BIT 5                    | BIT 4         | BIT 3                | BIT 2           | BIT 1 | BIT 0 |

|-------|-----------------------|--------------------------|---------------|----------------------|-----------------|-------|-------|

| FLAG  | FLAG<br>AUTO<br>CLEAR | VECTOR                   | INT<br>ENABLE | INT<br>AUTO<br>CLEAR | INTERRUPT LEVEL |       | VEL   |

| F     | FAC                   | 0=INTERNAL<br>1=EXTERNAL | IRE           | 1=AUTO<br>0=NO       | L2 L1 L         |       | LO    |

M1160A/T4.1-3

Table 4.1-4. Typical BIM Vector Register Map

| \$XX19 VR0 | (Vector for DR3 COS)* |

|------------|-----------------------|

|------------|-----------------------|

| VECTOR REGISTER |    |    |    |    |    |    |    |  |

|-----------------|----|----|----|----|----|----|----|--|

| V7              | V6 | V5 | V4 | V3 | V2 | V1 | V0 |  |

## \$XX1B VR1 (Vector for DR2 COS)\*

| VECTOR REGISTER |    |    |    |    |    |    |    |  |

|-----------------|----|----|----|----|----|----|----|--|

| V7              | V6 | V5 | V4 | V3 | V2 | V1 | V0 |  |

## \$XX1D VR2 (Vector for DR1 COS)\*

| VECTOR REGISTER |    |    |    |    |    |    |    |  |

|-----------------|----|----|----|----|----|----|----|--|

| <b>V</b> 7      | V6 | V5 | V4 | V3 | V2 | V1 | Vo |  |

## \$XX1F VR3 (Vector for DR0 COS)\*

| VECTOR REGISTER |    |    |    |    |    |    |    |  |

|-----------------|----|----|----|----|----|----|----|--|

| V7              | V6 | V5 | V4 | V3 | V2 | V1 | Vo |  |

\*COS = Change-of-State

M1160A/T4.1-4

M1160A/F4.1-1

Figure 4.1-1. VMIVME-1160A Programming Flow Diagram

#### 4.2 TYPICAL PROGRAMMING EXAMPLE

The following example code enables interrupts, processes interrupts, and displays the current input data when a change-of-state occurs.

```

/*

**

1160.h

* *

VMIVME-1160 32 BIT OPTICALLY COUPLED DIGITAL INPUT W/COS

*/

struct vmivme_1160_registers {

unsigned char offset[32];

};

typedef struct vmivme_1160_registers v1160 t;

/*

* *

register offset definitions

** note: defining register offsets using the above

* *

structure/array and defines facilitates

* *

skipping unused addresses in the board map.

* /

#define dr0

offset[0x00]

#define dr1

offset[0x01]

#define dr2

offset[0x02]

#define dr3

offset[0x03]

#define ier

offset[0x05]

#define cr0

offset[0x11]

#define crl

offset[0x13]

#define cr2

#define cr3

offset[0x15]

offset[0x17]

offset[0x19]

#define vr0

#define vrl

offset[0x1b]

#define vr2

offset[0x1d]

#define vr3

offset[0x1f]

interrupt enable control bits

#define

IE DR3

0x08

IE DR2

#define

0 \times 04

IE DR1

0 \times 02

#define

#define IE_DR0

0 \times 01

```

```

BIM control bits

#define FLAG_BIT

0 \times 80

#define FLAG AUTO CLEAR

0 \times 40

#define EXTERNAL_VECTOR

#define INTERRUPT_ENABLE

#define INTR_AUTO_CLEAR

#define REQUEST_LEVEL_7

/* don't use ! - see manual */

0x20

0x10

0 \times 08

0 \times 07

#define REQUEST_LEVEL_6

0x06

#define REQUEST_LEVEL_5

0 \times 05

#define REQUEST LEVEL 4

0 \times 04

#define REQUEST LEVEL 3

0 \times 03

#define REQUEST LEVEL 2

0 \times 02

#define REQUEST_LEVEL_1

#define INTERRUPTS_OFF

0x01

0 \times 00

```

```

** 1160.c

** VMIVME-1160 32 BIT OPTICALLY COUPLED DIGITAL INPUT W/COS

#include <stdio.h>

#include "1160.h"

** System dependent definitions ( Force Cpu-33 SBC )

#define SHORTIO 0xfbff0000 /* short io window */

#define USER_VECTOR( v ) v + 0x54 /* 1st available user vector

** Define global pointer to vmivme 1160 board

#define BASE ADDR 1160 0x0000 /* see manual section 5 */

v1160_t * board = ((v1160_t *)(SHORTIO + BASE_ADDR_1160));

** Define Global Change of State Flags and Data Storage

* *

** Note: COS flags and data variables are modified in the

* *

Interrupt Service Routines (ISR's) and therefore

* *

need to be global and/or visable to them.

* /

unsigned char cos flags;

#define COS 0

0 \times 01

#define COS 1

0 \times 02

#define COS 2 0x04

#define COS_3 0x08

unsigned char cos_0_data;

unsigned char cos_1_data;

unsigned char cos_2_data;

unsigned char cos_3_data;

```

```

** Declare external functions ( ISR's )

**

** Note: The interrupt service routines are written

**

in assembler and linked to the main C program.

**

They modify the globally defined variables

above that are visable to main and the ISR's.

* *

*/

void cos0isr( void );

void coslisr( void );

void cos2isr( void );

void cos3isr( void );

INITIALIZE 1160 BOARD AND DISPLAY CHANGE OF STATE INPUTS

*/

main()

Install ISR Addresses into CPU-33 Vector Table

**

** Note: Vector installation is system dependent. Our

**

method is through a libarary call that installs

* *

the ISR addresses according to the vector used.

*/

setvect( USER VECTOR( 0 ), &cos0isr );

setvect( USER VECTOR( 1 ), &coslisr );

setvect( USER_VECTOR( 2 ), &cos2isr );

setvect( USER VECTOR( 3 ), &cos3isr );

**

Initialize Vector Registers

* *

** Note: Vectors available to the user are system dependent.

*/

board->vr0 = USER VECTOR( 0 );

board->vrl = USER VECTOR( 1 );

board->vr2 = USER VECTOR( 2 );

board->vr3 = USER VECTOR( 3 );

/*

** Initialize Interrupt Control Registers

* *

** The change of state interrupts are enabled with request

** levels 3 through 6 where 6 is the highest priority. This

** is an arbitrary level selection that could have been a mix

or all the same level depending on the application ...

*/

```

```

board->cr0 = ( INTERRUPT ENABLE | INTR AUTO CLEAR | REQUEST LEVEL 3 );

board->crl = ( INTERRUPT ENABLE | INTR AUTO CLEAR | REQUEST LEVEL 4 );

board->cr2 = ( INTERRUPT ENABLE | INTR AUTO CLEAR | REQUEST LEVEL 5 );

board->cr3 = ( INTERRUPT_ENABLE | INTR_AUTO_CLEAR | REQUEST_LEVEL_6 );

/*

* *

Initialize Interrupt Enable Register

**

** Writing this register is necessary to enable COS information

** to cause interrupts. Each port has an associated interrupt

**

enable control bit so that COS interrupts may be enabled on

each bytewide port. This simple application enables interrupts

and leaves them enabled. These enables could be used to switch

interrupts on and off to capture or ignore data according to

**

the application.

*/

board->ier = ( IE DR3 | IE DR2 | IE DR1 | IE DR0 );

** Monitor Change of States and Print Input Data

for(;;) {

/* loop forever */

if (cos flags & COS 3) {

printf("\r\nDR3 COS data = %.2X", cos 3 data );

cos flags &= ~COS 3;

if ( cos_flags & COS_2 ) {

printf("\r\nDR2 COS data = %.2X", cos 2 data );

cos flags &= ~COS 2;

if (cos flags & COS 1 ) {

printf("\r\nDR1 COS data = %.2X", cos_1_data );

cos flags &= ~COS 1;

if (cos flags & COS 0 ) {

printf("\r\nDR0 COS data = %.2X", cos_0_data );

cos flags &= ~COS 0;

}

}

```

}

```

* *

**

VMIVME-1160 32 BIT OPTICALLY COUPLED DIGITAL INPUT W/COS

* *

external references and declarations

_board

xref

_cos_flags

xref

_cos_3_data

xref

_cos_2_data

xref

xref

_cos_1_data

_cos_0_data

xref

_cos0isr

xdef

_coslisr

xdef

_cos2isr

xdef

xdef

_cos3isr

offsets to board data registers

dr0

$00

equ

dr1

$01

equ

dr2

equ

$02

dr3

equ

$03

offsets to board intr ctrl registers

cr0

equ

$11

crl

equ

$13

cr2

equ

$15

cr3

equ

$17

section

code

service dr3 / cos3 interrupt

_cos3isr movem.l

a0,-(a7)

preserve registers

_board,a0

move.l

get pointer to board

move.b

(dr3,a0),_cos_3_data read COS data

\#4, (cr3, a\overline{0})

bset

re-enable interrupt

set COS intr flag

bset

#3,_cos_flags

movem.1

(a7) + , a0

restore registers

rte

return from exception

service dr2 / cos2 interrupt

_cos2isr movem.l

preserve registers

a0, -(a7)

board, a0

get pointer to board

move.l

move.b

(dr2,a0),_cos_2_data read COS data

re-enable interrupt

bset

#4, (cr2, a0)

#2,_cos_flags

set COS intr flag

bset

restore registers

(a7) + , a0

```

\*\*

1160isr.sa

return from exception

movem.l

rte

### \* service dr1 / cos1 interrupt

```

_coslisr movem.l a0,-(a7) preserve registers

move.l _board,a0 get pointer to board

move.b (dr1,a0),_cos_l_data read COS data

bset #4,(cr1,a0) re-enable interrupt

bset #1,_cos_flags set COS intr flag

movem.l (a7)+,a0 restore registers

rte return from exception

```

### \* service dr0 / cos0 interrupt

| _cos0isr | movem.1 | a0,-(a7)            | preserve registers    |

|----------|---------|---------------------|-----------------------|

|          | move.1  | _board,a0           | get pointer to board  |

|          | move.b  | (dr0,a0),_cos_0_dat | a read COS data       |

|          | bset    | #4, (cr0, a0)       | re-enable interrupt   |

|          | bset    | #0,_cos_flags       | set COS intr flag     |

|          | movem.1 | (a7) + , a0         | restore registers     |

|          | rte     |                     | return from exception |

### SECTION 5

### CONFIGURATION AND INSTALLATION

### 5.1 UNPACKING PROCEDURES

SOME OF THE COMPONENTS ASSEMBLED ON VMIC'S PRODUCTS MAY BE SENSITIVE TO ELECTROSTATIC DISCHARGE AND DAMAGE MAY OCCUR ON BOARDS THAT ARE SUBJECTED TO A HIGH ENERGY ELECTROSTATIC FIELD. UNUSED BOARDS SHOULD BE STORED IN THE SAME PROTECTIVE BOXES IN WHICH THEY WERE SHIPPED. WHEN THE BOARD IS TO BE LAID ON A BENCH FOR CONFIGURING, etc., IT IS SUGGESTED THAT CONDUCTIVE MATERIAL BE INSERTED UNDER THE BOARD TO PROVIDE A CONDUCTIVE SHUNT.

Upon receipt, any precautions found in the shipping container should be observed. All items should be carefully unpacked and thoroughly inspected for damage that might have occurred during shipment. The board(s) should be checked for broken components, damaged printed circuit board(s), heat damage, and other visible contamination. All claims arising from shipping damage should be filed with the carrier and a complete report sent to VMIC together with a request for advice concerning disposition of the damaged item(s).

#### 5.2 PHYSICAL INSTALLATION

DO NOT INSTALL OR REMOVE BOARDS WHILE POWER IS APPLIED.

De-energize the equipment and insert the board into an appropriate slot of the chassis. While ensuring that the board is properly aligned and oriented in the supporting card guides, slide the board smoothly forward against the mating connector until firmly seated.

### 5.3 CONFIGURATION SWITCHES

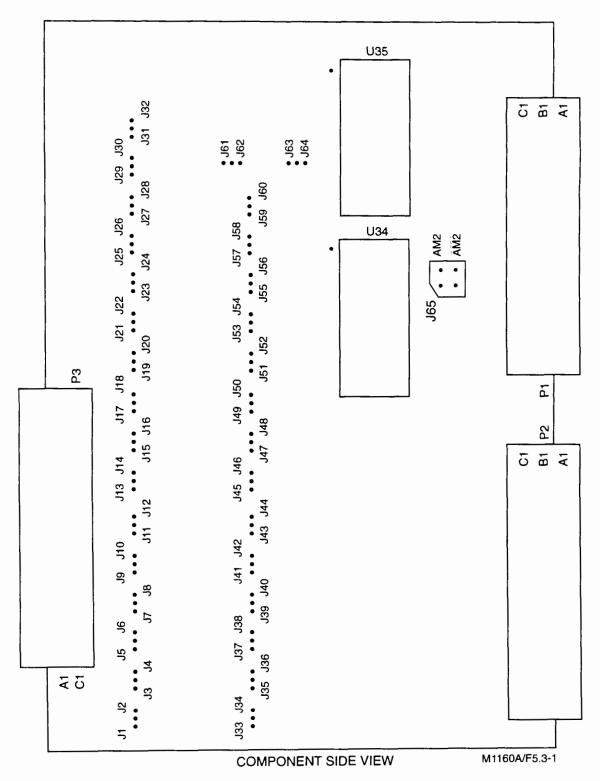

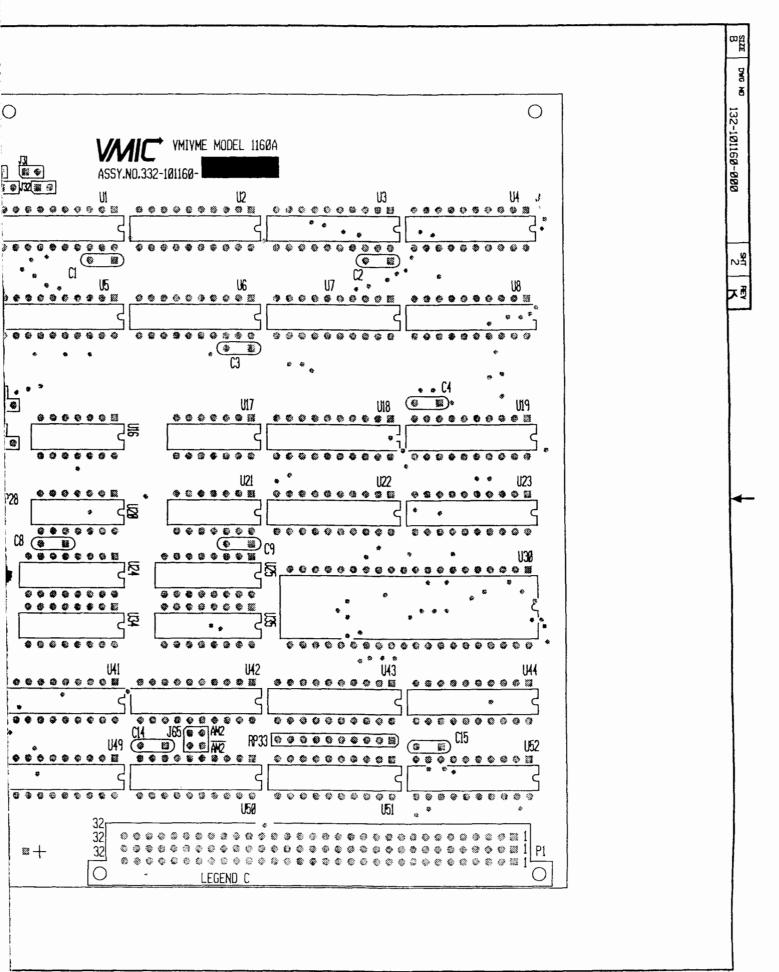

The reader should refer to Figure 5.3-1 for the locations of jumpers and address switches.

Figure 5.3-1. Location of Jumpers and Address Switches

M1160A/F5.6-1

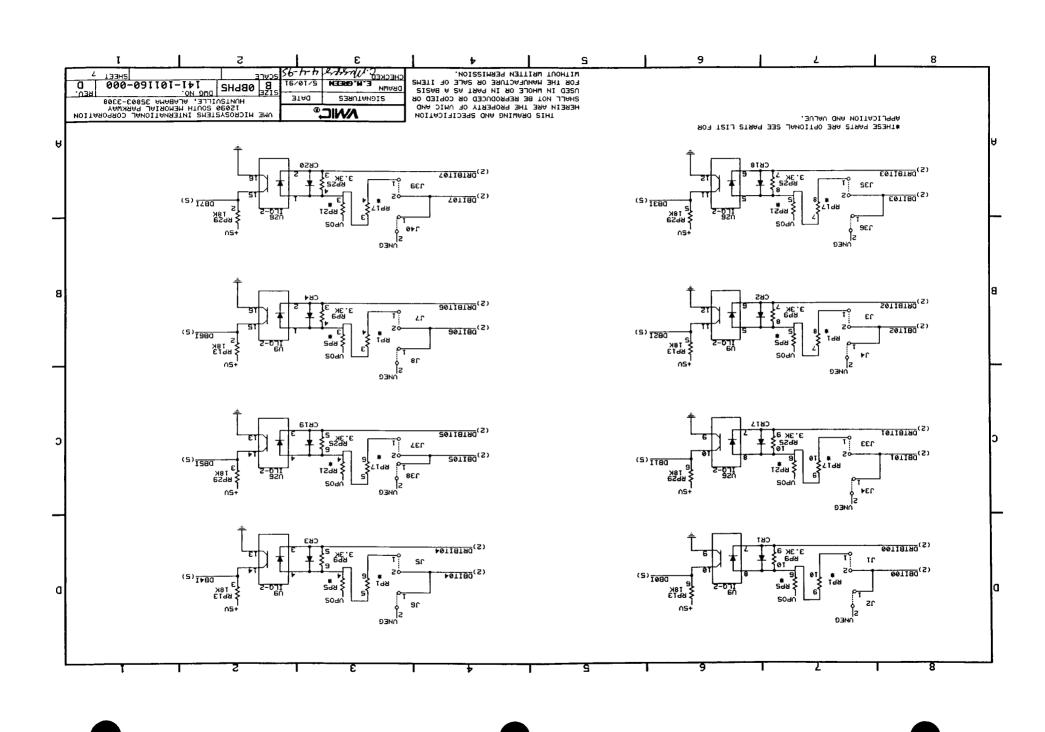

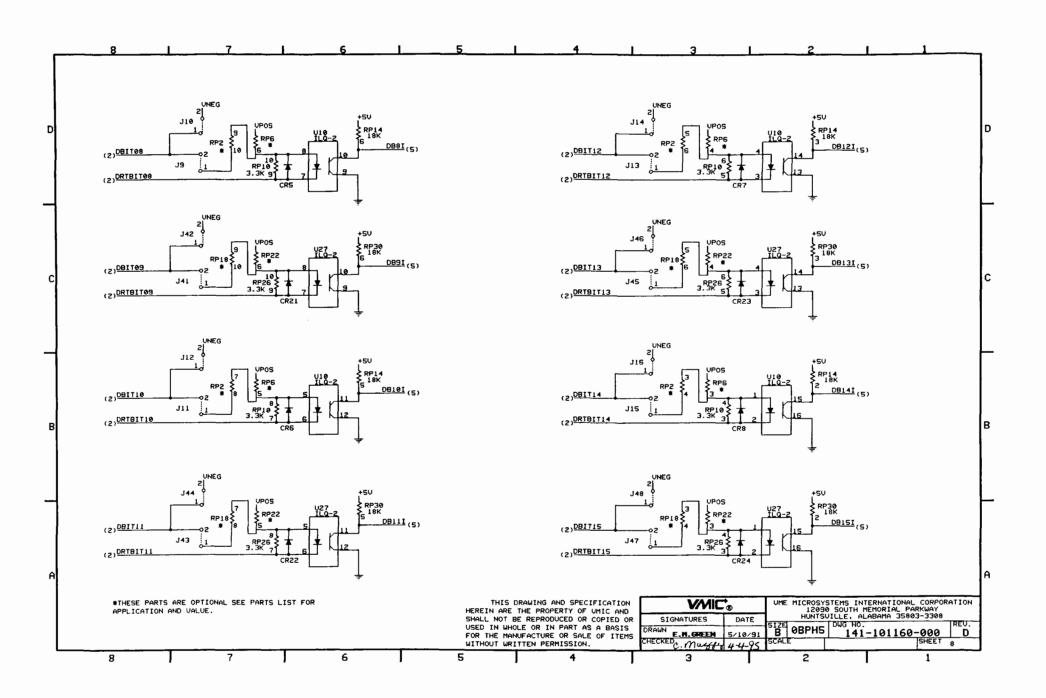

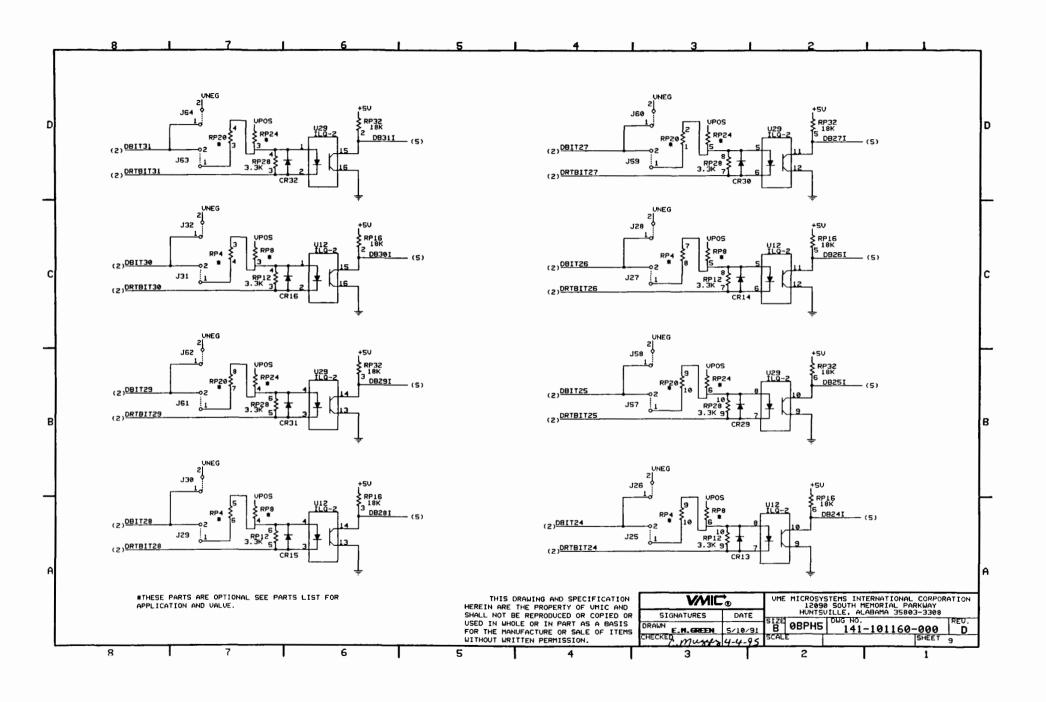

### 5.4 CONTACT SENSE, VOLTAGE SOURCE SELECTION

The VMIVME-1160A may be ordered with its input signal conditioning electronics factory configured for voltage source or contact sense input options. A wide range of input V (5 to 48 V) are supported, and the user may select from a variety of input filters. Refer to the document number 800-101160-000 for complete ordering information.

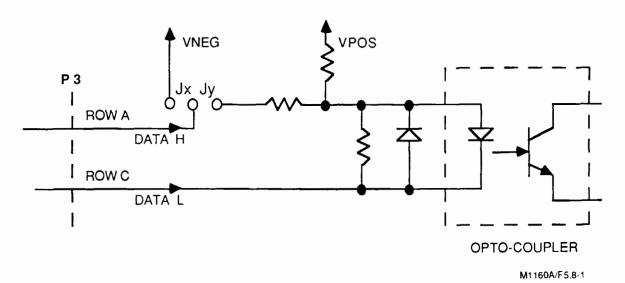

In Figure 5.8-1 Jx is the contact sense jumper. This jumper is installed at the factory when a contact sense board is ordered. Jx corresponds to the even numbered jumpers (J2, J4, etc.) on the schematic in the appendix of this manual. Jy is the voltage source jumper. It is installed for voltage source boards and corresponds to the odd numbered jumpers (J3, J5, etc.) except for jumper J65, which is the address modifier jumper.

### 5.5 EXTERNAL PULL-UP VOLTAGE

External voltage is connected through the P2 connector on pins C30, and C31 (VPOS uses P2 pin C30, VNEG uses P2 pin C31). This voltage is required on contact sense configurations only.

### 5.6 ADDRESS MODIFIERS

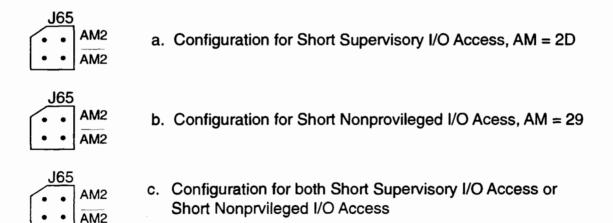

I/O Access Mode is configured by a dual header jumper post J65. Figures 5.6-1a, 5.6-1b, and 5.6-1c show how J65 can be configured for short supervisory I/O access, short I/O nonprivileged I/O access, or both. The VMIVME-1160A is factory configured to respond to short nonprivileged I/O access.

Figure 5.6-1. I/O Access Mode Selection

### 5.7 ADDRESS SELECTION SWITCHES

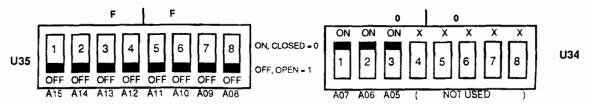

Figure 5.7-1 shows the two addressing DIP switches on board the VMIVME-1160A and their use in the addressing scheme.

A base address FF00 HEX is shown in this example.

M1160A/F5.7-1

Figure 5.7-1. Data Register Address Select Switches

### 5.8 CONNECTOR PIN CONFIGURATION

Figure 5.8-1 below shows a typical input channel.

Figure 5.8-1. Typical Input Channel

The input connector, P3, is a 64-pin connector designed with pins in two rows, Row A and Row C. Connection is accomplished by connecting the appropriate row pin to the appropriate user signal. For example, in the voltage source case the user is recommended to connect the equipment ground to the Row C pins, and bring each signal input in through Row A pins.

# 5.9 I/O CABLE AND FRONT PANEL CONNECTOR CONFIGURATION

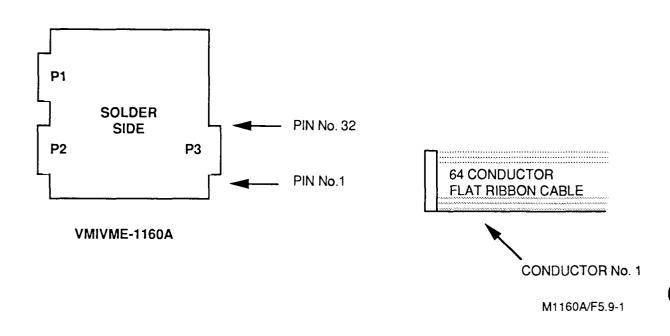

The I/O connector (P3) on the VMIVME-1160A is a 64-pin DIN standard and was selected by VMIC because of its high quality. Although these connectors are generally used with flat-ribbon cables, a variety of cables and mating connectors are available for most user requirements. The user should refer to VMIC's Connector and I/O Cable Application Guide (VMIC's Document 825-000000-006) for additional information concerning the variety of possible cabling and connector types available.

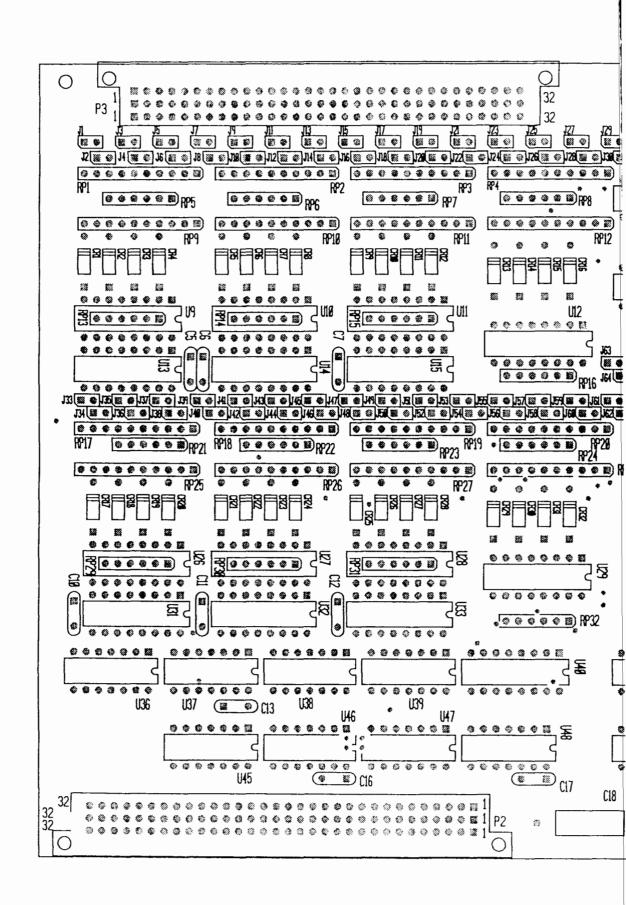

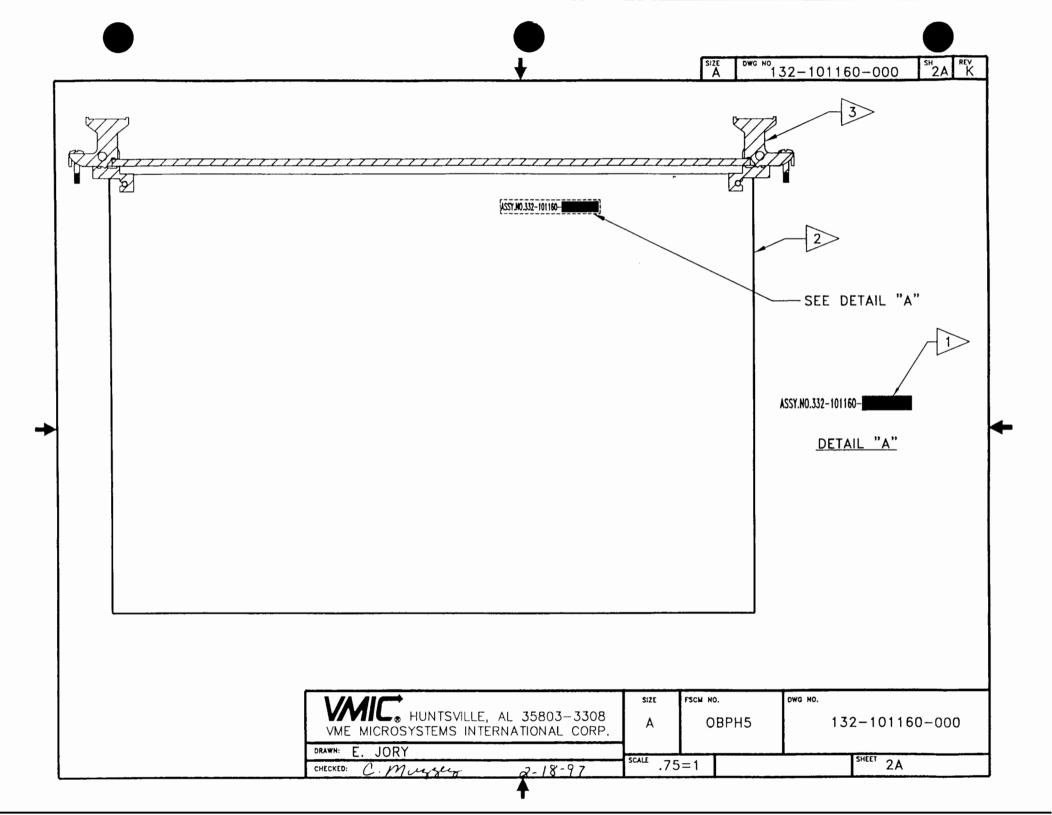

Details concerning I/O connections are shown in Figure 5.9-1. Conductor No. 1 is shown at the bottom of the connector as it plugs into the header, because pin No. 1 of P3 is mounted as shown.

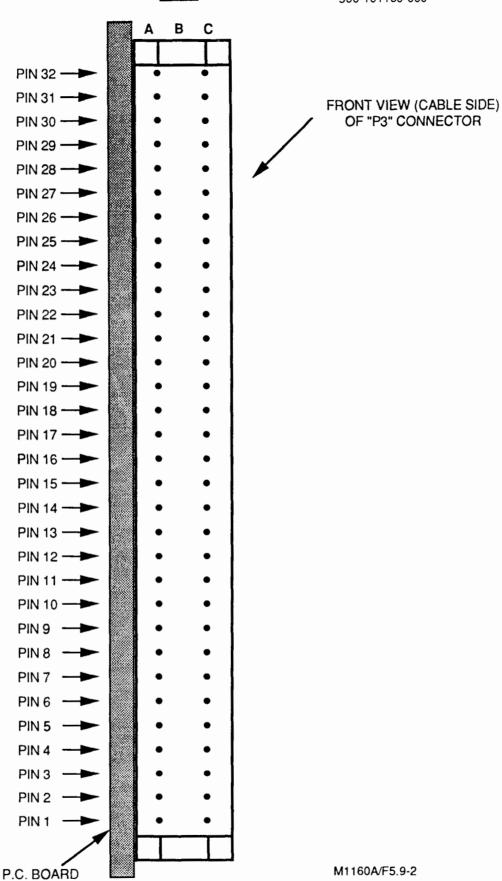

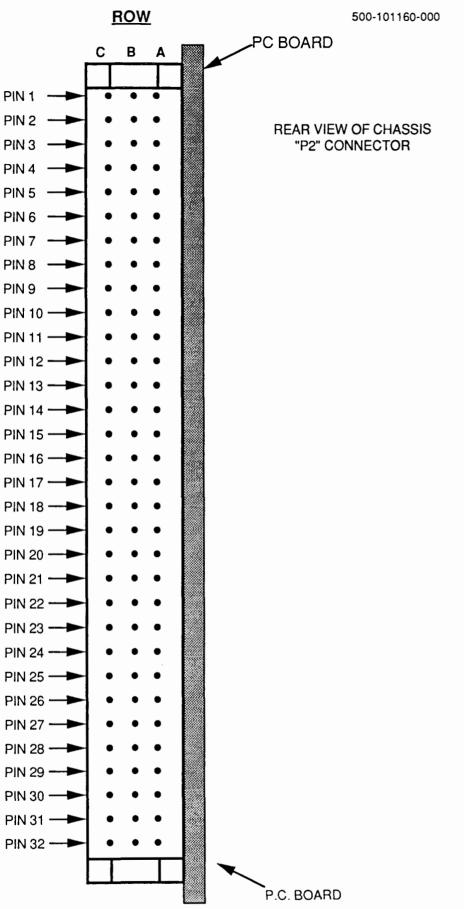

A compatible flat-ribbon cable connector for the VMIVME-1160A is Panduit No. 120-964-435E, and strain relief, Panduit No. 100-000-032. The Header Connector soldered to the PC board is Panduit No. 120-964-033A. Figure 5.9-2 shows the pin out of connector P3. Table 5.9-2 shows the P3 connector pin assignments for the inputs to the board. Figure 5.9-3 shows the pin out of connector P2. Table 5.9-1 shows the pertinent pin assignments for connector P2.

Figure 5.9-1. Cable Connector Configuration

Figure 5.9-2. P3 Connector Pin Layout

Figure 5.9-3. P2 Connector Pin Layout 5-8

Table 5.9-1. P2 Connector Pin Assignment

| PIN<br>NO.                                                     | ROW A <sup>1</sup> | ROW B <sup>2</sup> | ROW C          |

|----------------------------------------------------------------|--------------------|--------------------|----------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9                      |                    | +5 VOLTS<br>GND    |                |

| 11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21 |                    | GND<br>+5 VOLTS    |                |

| 22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31       |                    | GND                | V POS<br>V NEG |

| 32                                                             |                    | +5 VOLTS           |                |

M1160A/T5.9-1

NOTES: 1. External Reference is supplied by the user. 2. Inputs to the Board - not required.

Table 5.9-2. P3 Pin-Channel Assignment

| P3        |             |  |  |  |  |  |

|-----------|-------------|--|--|--|--|--|

| ROW A PIN | CHANNEL NO. |  |  |  |  |  |

| 32        | 31          |  |  |  |  |  |

| 31        | 30          |  |  |  |  |  |

| 30        | 29          |  |  |  |  |  |

| 29        | 28          |  |  |  |  |  |

| 28        | 27          |  |  |  |  |  |

| 27        | 26          |  |  |  |  |  |

| 26        | 25          |  |  |  |  |  |

| 25        | 24          |  |  |  |  |  |

| 24        | 23          |  |  |  |  |  |

| 23        | 22          |  |  |  |  |  |

| 22        | 21          |  |  |  |  |  |

| 21        | 20          |  |  |  |  |  |

| 20        | 19          |  |  |  |  |  |

| 19        | 18          |  |  |  |  |  |

| 18        | 17          |  |  |  |  |  |

| 17        | 16          |  |  |  |  |  |

| Р3        |             |  |  |  |  |  |

|-----------|-------------|--|--|--|--|--|

| ROW A PIN | CHANNEL NO. |  |  |  |  |  |

| 16        | 15          |  |  |  |  |  |

| 15        | 14          |  |  |  |  |  |

| 14        | 13          |  |  |  |  |  |

| 13        | 12          |  |  |  |  |  |

| 12        | 11          |  |  |  |  |  |

| 11        | 10          |  |  |  |  |  |

| 10        | 09          |  |  |  |  |  |

| 09        | 08          |  |  |  |  |  |

| 08        | 07          |  |  |  |  |  |

| 07        | 06          |  |  |  |  |  |

| 06        | 05          |  |  |  |  |  |

| 05        | 04          |  |  |  |  |  |

| 04        | 03          |  |  |  |  |  |

| 03        | 02          |  |  |  |  |  |

| 02        | 01          |  |  |  |  |  |

| 01        | 00          |  |  |  |  |  |

M1160A/T 5.9-2

### **SECTION 6**

### **MAINTENANCE**

### 6.1 MAINTENANCE

This section of the technical manual provides information relative to the care and maintenance of VMIC's products. Should the products malfunction, the user should verify the following:

- a. Software

- b. System configuration

- c. Electrical connections

- d. Jumper or configuration options

- e. Boards fully inserted into their proper connector location

- f. Connector pins are clean and free from contamination

- g. No components of adjacent boards are disturbed when inserting or removing the board from the VMEbus card cage

- h. Quality of cables and I/O connections

User level repairs are not recommended. Contact VMIC for a Return Material Authorization (RMA) Number. This RMA Number must be obtained prior to any return.

### 6.2 MAINTENANCE PRINTS

The appendix(ices) to this manual contain(s) drawings and diagrams for reference purposes.

# APPENDIX A ASSEMBLY DRAWING, PARTS LIST, AND SCHEMATIC

|   | 8I                         | 7 1                            | 6                            | I5_                   | 1                   | 41                   | 3                          | 2                                         |                                                                   | 1               |

|---|----------------------------|--------------------------------|------------------------------|-----------------------|---------------------|----------------------|----------------------------|-------------------------------------------|-------------------------------------------------------------------|-----------------|

|   |                            |                                |                              |                       |                     |                      |                            |                                           |                                                                   |                 |

| i |                            |                                |                              |                       |                     |                      |                            |                                           |                                                                   |                 |

| 1 |                            |                                |                              |                       |                     |                      |                            |                                           |                                                                   |                 |

| , | PIA                        | P18                            | PIC                          | P2A                   | P2B                 | P2C                  | РЗА                        | P3B                                       | P3C                                                               |                 |

|   | C 1 D00 (5)                | √ 1 N/C                        | <del>( 1</del> 008(6)        | (11 N/C               | ← 1 +5U             | € 1 N/C              | C DBIT00                   | ٠.                                        | . ! .                                                             |                 |

| 1 | 2 D01(6)                   | N/C                            | C 2 D09(6)                   | € E N/C               | GND                 | <del>√ iz</del> N/C  | C 12 DBIT01(               | 7) ( 2 N/C                                | ` ! a                                                             |                 |

|   | ( 3 D02 (6)                | <del>√3</del> N/C              | ( 1 D10(6)                   | ( 14 N/C              | <del>√ 3</del> N/C  | € 3 N/C              | C 3 DBIT02(                | 7) (3 N/C                                 |                                                                   |                 |

| 1 | D03(6)                     | BG0 CHAIN#                     | 011(6)                       | € 15 N/C              | 5 N/C               |                      | DBITØ3(                    | 7) ( 14 N/C                               | ` ' -                                                             |                 |

| ┨ | D05(E)                     | BG1 CHAIN*                     | ( 16 D13(6)                  | € B N/C               | √ 16 N/C            | <del>( i B</del> N∕C | / 15 pprzes                | 7 / 15 1/0                                | € DRTBIT05 (7)                                                    |                 |

| 1 | (F)                        | GI CHAIN#                      | (17 D14(6)                   | ( 18 N/C              | <del>( 17</del> N/C | <del>√ 17</del> N/C  | <del>( ; 7</del> DBITØ6 (  | 7) <del>( ; 7</del> N∕C                   | (7) ORTBIT06                                                      |                 |

|   | ( 8 D07(6)<br>( 9 GND      | BGZ CHAIN#                     | ( 19 GND (B)                 | N.C                   | 8 N/C               |                      | B   DBIT07(                | 7) <del>( ; N</del> /C                    |                                                                   |                 |

| 1 | GND SYSCLK (3)             | BGZ CHAIN#                     | GND<br>10 N/C                | (10 N/C               | 10 N/C              | €10 H×C              | 10 DB1108(                 | 8) (10 N/C                                | ORTBIT09 (8)                                                      |                 |

|   | ← ;11 GND                  | CHAINE                         | (11 BERR*(3)                 | 2 11 N/C              | < 111 N/C           | CILL N/C             | ( 111 DBIT10(              | B) <del>( 11</del> N∕C                    | (11 DRTBIT10 (8)                                                  |                 |

| 9 | (3)                        | ∠ 112 N/C                      | SYSRESET*(3)                 | (13 N/C               | (13 +50             | (13 N/C              | (12 DBI711 €               | B) (12 N/C                                |                                                                   |                 |

|   | 13 DSØ# (3)                | (13 N/C<br>(14 N/C             | (13 LWORD(3)                 | (14 N/C               | (14 N/C             | CITA N.C             | (13 DBIT12(                | 8) (13 N/C<br>8) (14 N/C                  | ORTBIT12 (8)                                                      |                 |

|   | ← 15 GND                   | ( 115 N/C                      | <del>(15</del> N/C           | € 15 N/C              | ( 115 N/C           | 15 N/C               | <del>( 115</del> DB1T14(   | B) <del>( ;15</del> N∕C                   | € 15 DRTBIT14 (8)                                                 |                 |

|   | (16 DTACK*(4)              | ∠ 116 oma (3)                  | 2 16 N/C                     | 2 116 N/C             | ∠ 116 N/C           | € 16 N/C             | (-116 OBIT15)              | $61  \leftarrow \frac{15}{15} \text{N/C}$ | <u> </u>                                                          |                 |

| _ | (17 GND<br>(18 AS#(3)      | (17 AM1 (3)                    | 17 N/C                       | 17 N/C                | 17 N/C              | 17 N/C               | (17 DBIT16(                | 10) (17 N/C<br>10) (18 N/C                | ORTBIT16 (10                                                      | )               |

| 1 | ∠ 119 GND                  | / 119 042 (2)                  | / 119                        | / i19 <sub>11/0</sub> | <u> </u>            | / 119 11/6           | (18 DBIT17(                | 10) / 119 1/0                             | (19 DETETTIS (10                                                  | )               |

| 1 | (3) IACK*(3)               | € 120 GND                      | 7 150 N/C                    | € 120 N/C             | ∠ 120 N/C           | ∠ 120 N/C            | ) E11180 ( )               | 10) (120 N/C                              | 20 DRIBITIS (10                                                   | )               |

| 1 | (3)                        | ∠ ·21 N/C                      | Z IST N/C                    | ∠ 121 N/C             | ∠ 121 N/C           | < 121 N C            | OBIT200                    | 10) <del>( 'E'</del> N/C                  | <del>€ 21</del> DRTBIT20 (10                                      | )               |

| 1 | ( 22 IACKOUT#(4)           | € 22 N/C                       | (   22 N/C<br>(   23 A15 (3) | (                     | € 23 N/C            | € 23 N/C             | ( 23 DBIT22 (              | 10) <del>22</del> N/C                     | C 22 DRTBIT21 (10                                                 |                 |

| В | (3)                        | (4)                            | (-124 A14 (3)                | <u> </u>              | 24 N/C              | 24 N/C               | <del>( '23</del> DBI T23 € | 10) (124 N/C                              | 4124 DRIBITZ3 (10                                                 | ,               |

|   | <del>← 25</del> A95 (3)    | ← 125 IRQ6*(4)                 | (3) A13                      | ( 125 N/C             | < 125 N∠C           | ( 125 N/C            | C 125 DRITZ4 (             | 9) $\frac{125}{125}$ N/C                  | (9) CTB1724                                                       |                 |

|   | 26 A05 (3)                 | <del>( 126</del> IRQ5*(4)      | (3) (3)                      | ₹ 25 N/C              | 26 H/C              | 26 N/C               | ← '26 DBIT25 (             | 9) (126 N/C                               | 26 DRTBIT25 (9)                                                   |                 |

|   | (27 A04 (3)<br>(28 A03 (3) | (127 IRQ4#(4)<br>(128 IRQ3#(4) | (27 A11 (3)<br>(28 A10 (3)   | / 128                 | Z 128 N/C           | 28 11.0              | ( 27 DB1726 ( 28 DB1727 (  | 9) (27 N/C<br>9) (28 N/C                  | 27 DRTBIT26 (9)                                                   |                 |

| 1 | (E) S0A PS (3)             | (129 IRQ2*(4)                  | (3)                          | ₹ 129 N/C             | 129 N/C             | <del>← i29</del> N/C | C 129 DBIT28 (             | 9) (129 N/C                               | (9) PTRITZ8                                                       |                 |

| ┪ | € 130 ca (3)               | (30 IRQ1*(4)                   | ∠ 130 Agg (3)                | 30 N/C                | Z 130 N/C           | √ i30 UPOS (7+10)    | <del>(30</del> DB1T29 €    | 9) (130 N/C                               | <del>(30</del> 0RTBIT29 (9)                                       |                 |

| 1 | ( 31 N/C ( 32 +50          | (131 N/C)                      | 131 N/C                      | 132                   | 31 GND              | (31 UNEG (7+10)      | (31 DBIT30 (               | 9) (31 N/C                                | (31 DRTBIT30 (9)                                                  |                 |

|   | <del>(   +5</del> 0        | +50                            | +50                          | ₩.c                   | +50                 | N/C                  | SELIBO SE                  | a) <del>(   N</del> /C                    | (9)                                                               |                 |

|   |                            |                                |                              |                       |                     |                      |                            |                                           |                                                                   |                 |

| ۵ |                            |                                |                              |                       |                     |                      |                            |                                           |                                                                   |                 |

| 7 |                            |                                |                              |                       |                     |                      |                            |                                           |                                                                   |                 |

|   |                            |                                |                              |                       |                     | AND SPECIFICATION    | V/MIC*                     | UME MICROSY                               | STEMS INTERNATIONAL                                               | CORPORATION     |

|   |                            |                                |                              | SHALI                 | NOT BE REPRO        | PERTY OF UMIC AND    | SIGNATURES DAT             | 1209<br>HUNTS                             | STEMS INTERNATIONAL<br>0 SOUTH MEMORIAL PA<br>UILLE, ALABAMA 3580 | RKWAY<br>3-3308 |

|   |                            |                                |                              | USED                  | IN WHOLE OR I       | N PART AS A BASIS    | DRAWN E.M.GREEN 5/10/      | al Size 0BbH2                             | 141-101160-                                                       |                 |

| L |                            |                                |                              | WITH                  | OUT WRITTEN PE      | RMISSION.            | CHECKED C. Muyer 4-4.      | 95 SCALE                                  |                                                                   | SHEET 2         |

|   | 8                          | 7                              | 6                            | 5                     | ı                   | 4                    | 3                          | 2                                         |                                                                   | 1               |

(DB12I+DB31I) (8+10) (DB160T+DB310T) (4) INT3H (DB0I+DB11I) (7,8,10) U14 (DB00T+DB150T) (6) MC14490P DB301 10 U4 74ALS688 74AL5373 DB311 12 DI H/C 148I H/C 1AI H/C 3CI H/C 5EI UG BO 2 N/C AO 15 N/C CO 13 N/C EO 11 N/C OE CLK 19 LD31 17 D D9310T U2 74ALS688 74ALS373 16 LD30 15 DB300T 18 OE CFK 13 FD12 DB150T DB140T 15 FDSB 13 DB290T 16 LD14 12 LD28 11 DB280T 9 LD27 8 6 LD26 6 5 LO25 4 2 LO24 2 15 LD13 DB130T DB270T 19 DB120T 12 LD12 DB260T DB110T a roii INTIH(4) DB100T LD10 DB240T U31 MC14490P DB90T LD9 U33 DBSOT DB310T MC14490P DB300T 16 1201 1481 DB7I DB150T DB24I 10 DB25I 12 DB26I 14 BI DB290T DO FO<sup>4</sup> DBSI DB140T BO DB280T 1 A C I E I A015 C013 E011 DB130T DB270T 80 DBIGI DB120T 08271 1AI 08281 3CI 08291 5ET DB260T 015 CO13 DB11I DB110T DB250T n DB240T DB291 ΕO DBSOT EIN DB80T C10 EIN (4)INT2H U3 74ALS688 74AL5373 18 OE CTK TO TOS3 US U1 74<u>ALS688</u> DB230T 74ALS373 16 LD22 15 DB220T 17 DB70T CLK 19 LD7 DB210T 12 LD20 DBGOT 16 LD6 DB200T 9 L019 DBSOT 15 LDS DB1301 19 e rois DB40T 12 LD4 DB180T DB30T 9 L03 V15 5 LD17 2 LD16 DB170T 19 INTOH(4) MC14490P DB20T 6 LO2 DB160T DBIOT 0818I 10 0819I 12 0820I 14 8I 0821I 1AI 0822I 3 CI 0823I 5 EI DB00T В DB230T pol DB22OT D870T RO DB210T AOLS DBGOT 16 DB200T CO<sub>IT3</sub> DBSOT DB190T α DB40T DB30T DB180T U13 DB1701 DB2OT MC14490P oso DB160T DB10T DB0I 10 DB1I 12 DB2I 14 BI DBOI DBOOT C7\* EIN **DB180T** DO 15 BO 15 CO 1 DBTOL 0B190T DB20T EIN DB200T DB31 DBBOT DBS10T U32 DB4I DB40T MC14490P D951 DBSOT DB230T DB12I 10 FI DB13I 12 DI DB14I 14 BI DB15I 14I DB1BI 3 CI DB17I 5 FI DB1201 **DB120T** DB130T DB130T DO 2 BO 15 AO 15 \_ €5 -|/ DB140T DB140T DBISOT A DB150T DB160T DB170T **VMIC**® THIS DRAWING AND SPECIFICATION UME MICROSYSTEMS INTERNATIONAL CORPORATION HEREIN ARE THE PROPERTY OF UMIC AND 12090 SOUTH MEMORIAL PARKWAY HUNTSUILLE, ALABAMA 35803-3308 SHALL NOT BE REPRODUCED OR COPIED OR SIGNATURES DATE #THESE PARTS ARE OPTIONAL SEE PARTS LIST FOR TOWG NO. USED IN WHOLE OR IN PART AS A BASIS SIZE B C11\* DRAWN 0BPH5 APPLICATION AND VALUE. CHECKED Muses 4-4-95 141-101160-000 D FOR THE MANUFACTURE OR SALE OF ITEMS SHEET 5 WITHOUT WRITTEN PERMISSION. SCALE 7 6 5 3 2 1 8

SIZE A DWG NO 132-101160-000 SH 1 REV K

## NOTES:

- 1. FOR SCHEMATIC DIAGRAM SEE 141-101160-000.

- 2. FOR TEST PROCEDURE SEE 510-001160-000.

- 3. FOR DOCUMENT SET SEE 110-101160-000.

| REVISIO <b>NS</b> |                                                    |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|-------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| REV               | DESCRIPTION                                        | DATE                                                                                                                                                                                                                                                                                                                                                        | APPROVED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| A                 | RELEASE PER ECO 92-0027                            | 2/14/92                                                                                                                                                                                                                                                                                                                                                     | A.J.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| В                 | MX BIM COPPER UPDATE PER ECO 92-0028               | 2/14/92                                                                                                                                                                                                                                                                                                                                                     | A.J.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |