Limited Availability

Used and in Excellent Condition

**Open Web Page**

https://www.artisantg.com/65489-1

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

TECHNOLOGY GROUP

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# RAM/ROM MEMORY MODULE

© XYCOM 1987

Printed in the United States of America Part Number 74100-001 XYCOM 750 North Maple Road Saline, Michigan 48176 (313) 429-4971

|                          | REVISION RECORD |      |  |  |  |  |  |  |

|--------------------------|-----------------|------|--|--|--|--|--|--|

| REVISION                 | DESCRIPTION     |      |  |  |  |  |  |  |

| Α                        | MANUAL RELEASED | 3/87 |  |  |  |  |  |  |

|                          |                 |      |  |  |  |  |  |  |

|                          |                 |      |  |  |  |  |  |  |

|                          |                 |      |  |  |  |  |  |  |

|                          |                 |      |  |  |  |  |  |  |

|                          |                 |      |  |  |  |  |  |  |

|                          |                 |      |  |  |  |  |  |  |

|                          |                 |      |  |  |  |  |  |  |

| MANUAL                   |                 |      |  |  |  |  |  |  |

| <b>P/N:</b><br>74100-001 |                 |      |  |  |  |  |  |  |

This document contains proprietary information of Xycom Incorporated (Xycom). It shall not be reproduced or copied without expressed written authorization from Xycom.

The information contained within this document is subject to change without notice. Xycom does not guarantee the accuracy of the information and makes no commitment toward keeping it up-to-date.

Address comments concerning this manual to:

xycom

Technical Publications Dept. 750 North Maple Rd. Saline, Michigan 48176

## TABLE OF CONTENTS

| CHAPTER                                                                                             | TITLE                                                                                                                                                                                                                                                                                                                                       | PAGE                                                                                            |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 1                                                                                                   | MODULE DESCRIPTION                                                                                                                                                                                                                                                                                                                          |                                                                                                 |

| 1.1<br>1.2<br>1.3<br>1.4                                                                            | Introduction Manual Structure Module Operational Description Specifications  XVME-100 INSTALLATION                                                                                                                                                                                                                                          | 1-1<br>1-1<br>1-2<br>1-3                                                                        |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.5<br>2.6<br>2.7 | Introduction Location of Components Relevant to Installation Jumpers Jumper Descriptions VME Address/Memory Chip Size Address Modifier Decode Memory Device Speed Memory Device Pinout Memory Backup Power Power Monitor Installing Memory Chips on the XVME-100 Cardcage Installation Procedure Installing a 6U Front Panel Kit (optional) | 2-1<br>2-1<br>2-4<br>2-5<br>2-5<br>2-10<br>2-11<br>2-12<br>2-15<br>2-17<br>2-19<br>2-20<br>2-21 |

| A                                                                                                   | VMEbus CONNECTOR/PIN DESCRIPTION                                                                                                                                                                                                                                                                                                            |                                                                                                 |

| В                                                                                                   | POWER MONITOR                                                                                                                                                                                                                                                                                                                               |                                                                                                 |

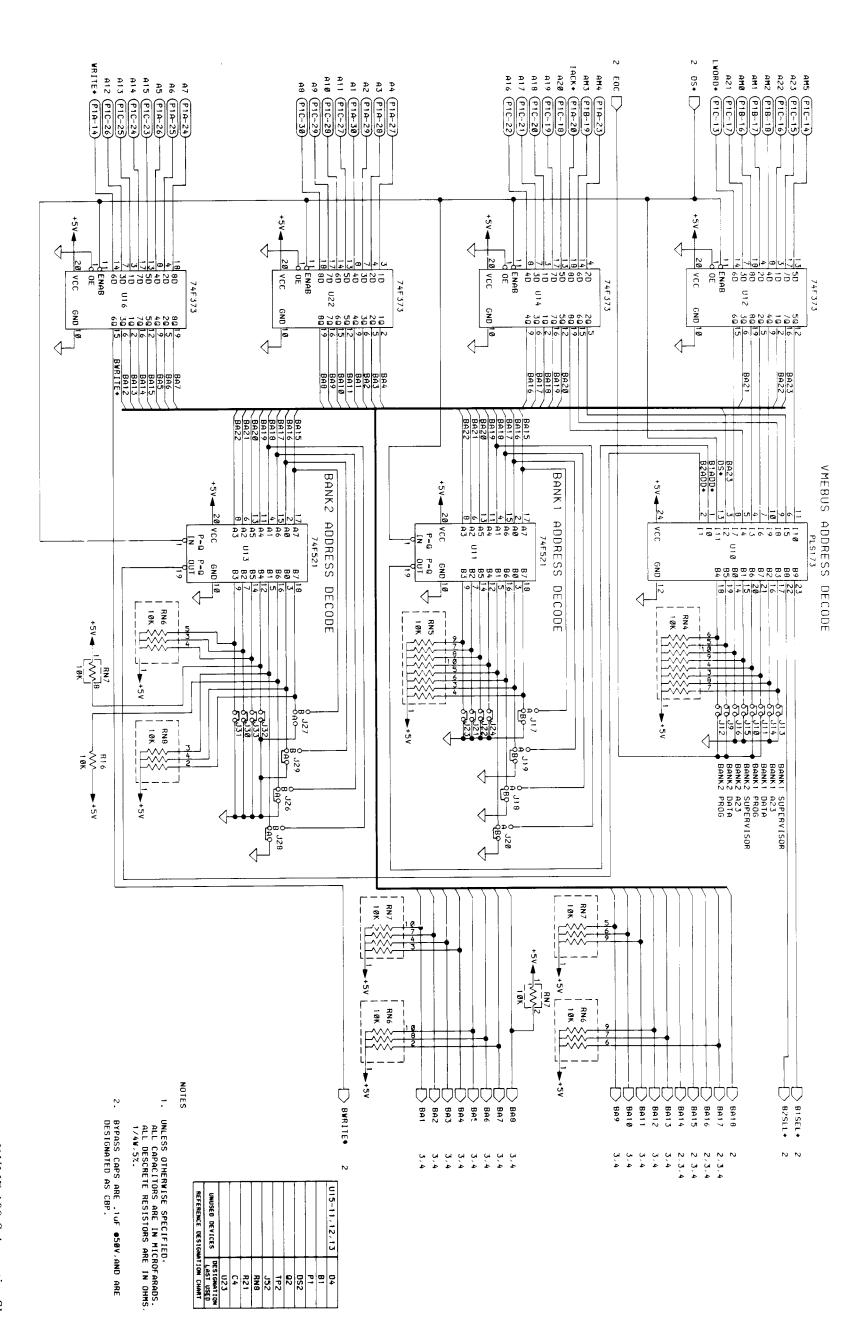

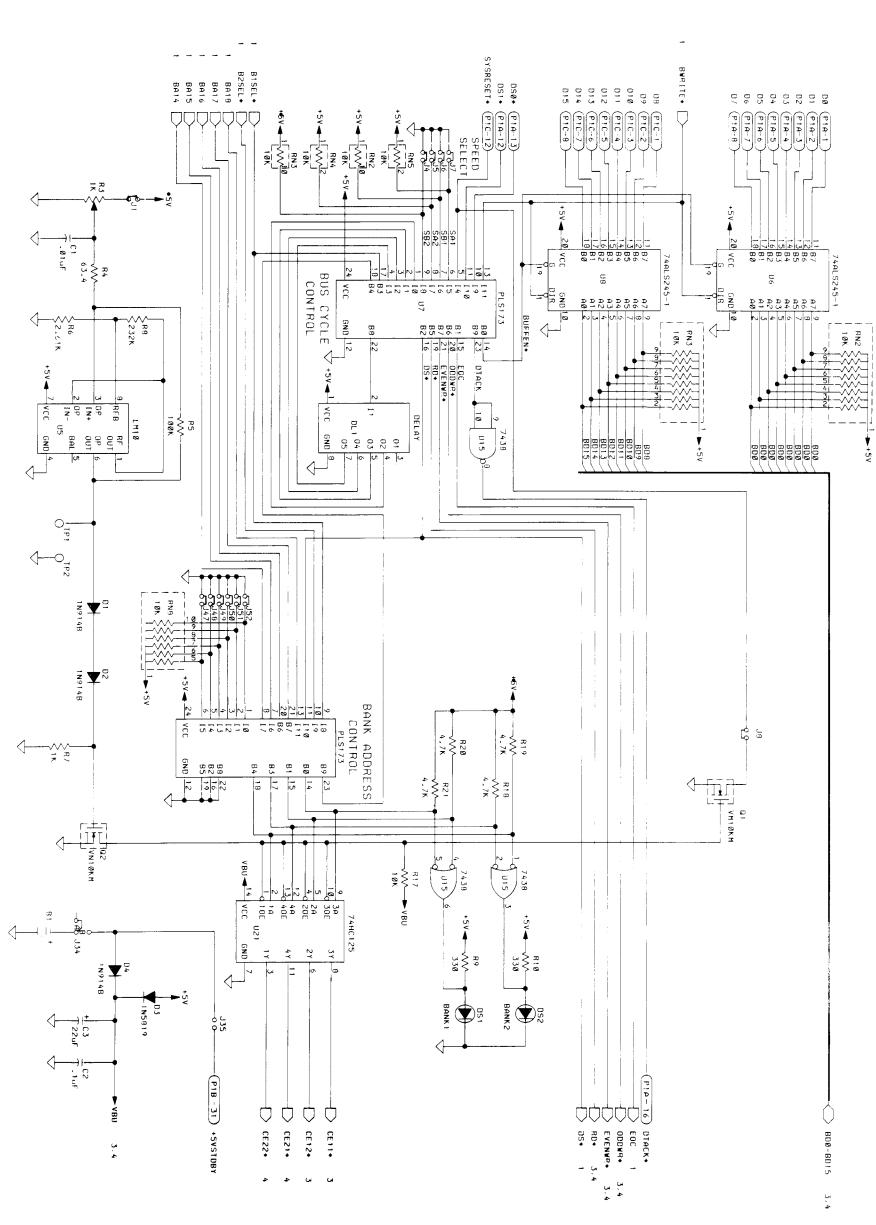

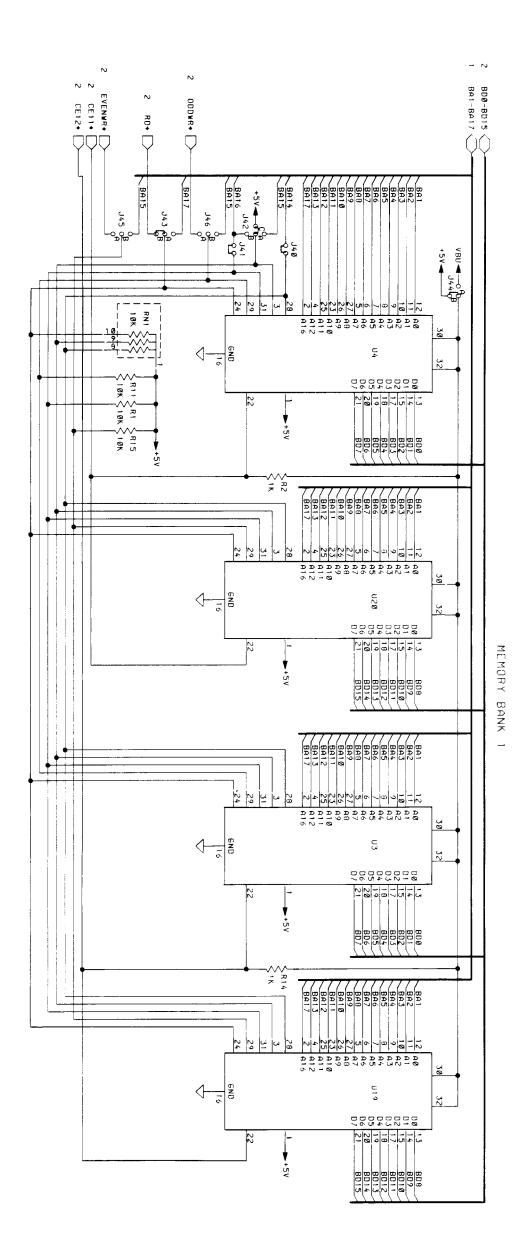

| С                                                                                                   | DIAGRAM AND SCHEMATICS                                                                                                                                                                                                                                                                                                                      |                                                                                                 |

| D                                                                                                   | QUICK REFERENCE GUIDE                                                                                                                                                                                                                                                                                                                       |                                                                                                 |

## LIST OF FIGURES

| FIGURE                                                               | TITLE                                                                                                                                                                                                                                                                                                              | PAGE                                                                    |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 1-1                                                                  | Operational Block Diagram                                                                                                                                                                                                                                                                                          | 1-2                                                                     |

| 2-1<br>2-1A<br>2-1B<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8 | Location of Jumpers, Sockets, and Connector Expanded Left Side of XVME-100 Expanded Right Side of XVME-100 XVME-100 Memory Map Addressing - 4 x Chip Size Memory Chip Pinouts Location of Jumper J34 Location of Jumpers and Test Points Notched End of the Memory Chip Installation of an XVME-945 6U Front Panel | 2-1<br>2-2<br>2-3<br>2-8<br>2-9<br>2-13<br>2-15<br>2-18<br>2-19<br>2-22 |

|                                                                      | LIST OF TABLES                                                                                                                                                                                                                                                                                                     |                                                                         |

| TABLE                                                                | TITLE                                                                                                                                                                                                                                                                                                              | PAGE                                                                    |

| 1-1                                                                  | Memory Module Specifications                                                                                                                                                                                                                                                                                       | 1-3                                                                     |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5                                      | Jumper List VME Base Address and Memory Chip Size Jumpers Address Modifier Jumpers Memory Device Speed Jumpers Memory Device Pinout Jumpers                                                                                                                                                                        | 2-4<br>2-6<br>2-10<br>2-11<br>2-12                                      |

#### Chapter 1

#### MODULE DESCRIPTION

## 1.1 INTRODUCTION

The XVME-100 RAM/ROM Memory Module is a single-high, VMEbus compatible board, which can accommodate up to 1M byte of RAM, EPROM, or mask programmable ROM or 256K bytes of EEPROM. The module is designed with an onboard battery backup circuit to provide power to CMOS RAM devices in the event of a power failure.

The XVME-100 has eight 28/32-pin JEDEC sockets which are logically arranged as 2 banks of 4 sockets each. Each bank is designed to employ memory devices of the same type and speed, and each bank can be independently configured (via jumpers) in terms of:

- VME Address/Memory Chip Size

- Address Modifier Decode

- Memory Device Speed

- Memory Device Pinout

- Memory Backup Power

The XVME-100 RAM/ROM Memory Module has power down protection circuitry which prevents data from being written to memory when the voltage falls below 4.75 Volts. The module also has the option of asserting SYSRESET under this condition.

#### 1.2 MANUAL STRUCTURE

The purpose of this first chapter is to introduce the user to the general specifications and functional capabilities of the XVME-100. Successive chapters will develop the various aspects of module installation and operation in the following progression:

- <u>Chapter One</u> A general description of the memory module, including complete functional and environmental specifications, VMEbus compliance information, and a block diagram.

- <u>Chapter Two</u> Module installation information covering the location of pertinent module components, jumper options, and standard board installation information.

The Appendices are designed to introduce and reinforce a variety of module-related topics including: Backplane signal/pin descriptions, a block diagram and schematics, a quick reference section, and power monitor calibration procedures.

# 1.3 MODULE OPERATIONAL DESCRIPTION

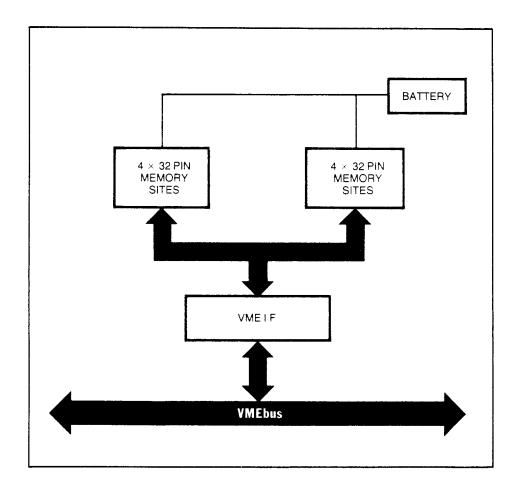

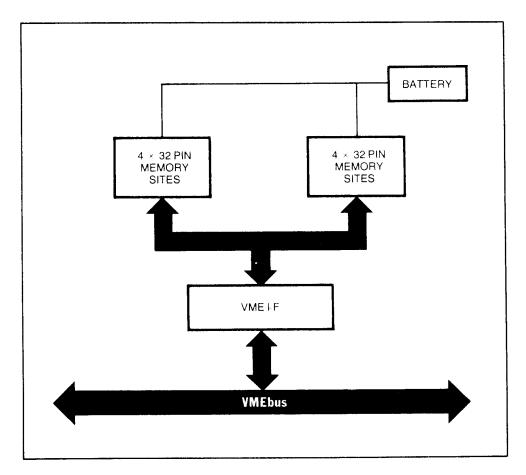

Figure 1-1 shows and operational block diagram of the memory module.

Figure 1-1. Operational Block Diagram

#### 1.4 SPECIFICATIONS

Table 1-1 lists the XVME-100 Memory Module's characteristics and specifications.

Table 1-1. Memory Module Specifications

| Characteristic                             | Specification                                                         |

|--------------------------------------------|-----------------------------------------------------------------------|

| Maximum Memory Capacity:                   | 2 banks of 4 sites                                                    |

| EPROM ———————————————————————————————————— | 1M byte<br>1M byte                                                    |

| Device Sizes Supported:                    |                                                                       |

| EPROM                                      | 8K by 8 up to 128K by 8<br>8K by 8 up to 128K by 8                    |

| Device Speeds Supported                    |                                                                       |

| Power Requirements                         | +5V @ 900mA typ., 1A max.                                             |

| Battery Rating                             | 1.4Amp hours                                                          |

| Battery Life                               | 6 years typ. (using an 8-6264<br>Hitachi RAM or equivalent<br>device) |

## VMEbus COMPLIANCE

Complies with VMEbus Specifications, Revision C.1

- A24:D16/D08(EO) DTB Slave

- 4 BUS GRANT INs are connected to their respective BUS GRANT OUTs

- IACKIN is connected to IACKOUT

- SINGLE 3U Form Factor

Table 1-1. Memory Module Specifications (continued)

| Characteristic                                                            | Specification                                                                                                                                                                                      |  |  |  |  |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ENVIRONMENTAL  Temperature Operating —————— Non-operating —————— Humidity | - 0 to 65 C (32 to 149 F)40 to 85 C (-40 to 158 F) 5 to 95% RH non-condensing (Extreme low humidity conditions may require special protection against static discharge)                            |  |  |  |  |

| Altitude Operating Non-operating Vibration Operating  Non-operating       | - Sca-level to 50,000 ft. (15240m)  - 5 to 2000Hz .015 inches peak-to-peak displacement 2.5 g peak (maximum) acceleration - 5 to 2000Hz .030 inches peak-to-peak displacement 5.0 g peak (maximum) |  |  |  |  |

| Shock                                                                     | duration                                                                                                                                                                                           |  |  |  |  |

#### Chapter 2

#### XVME-100 INSTALLATION

## 2.1 INTRODUCTION

This chapter explains how to configure the memory module prior to installation in a VMEbus system. Included in this chapter is information on jumper options, jumper locations, and power monitor circuit calibration and installation procedures.

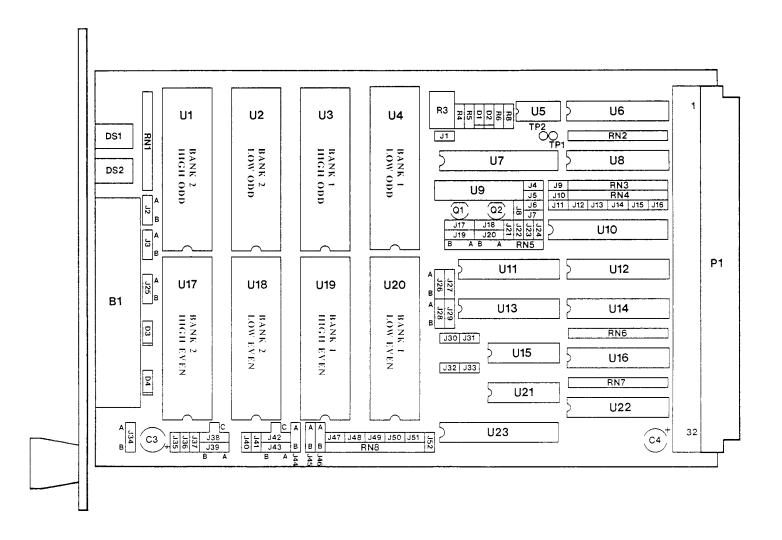

#### 2.2 LOCATION OF COMPONENTS RELEVANT TO INSTALLATION

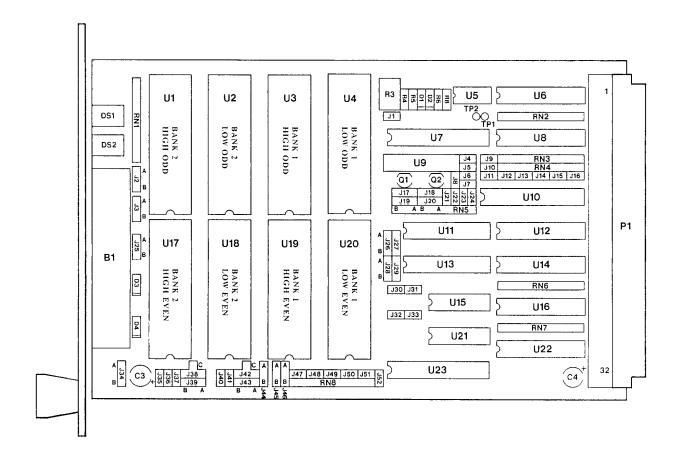

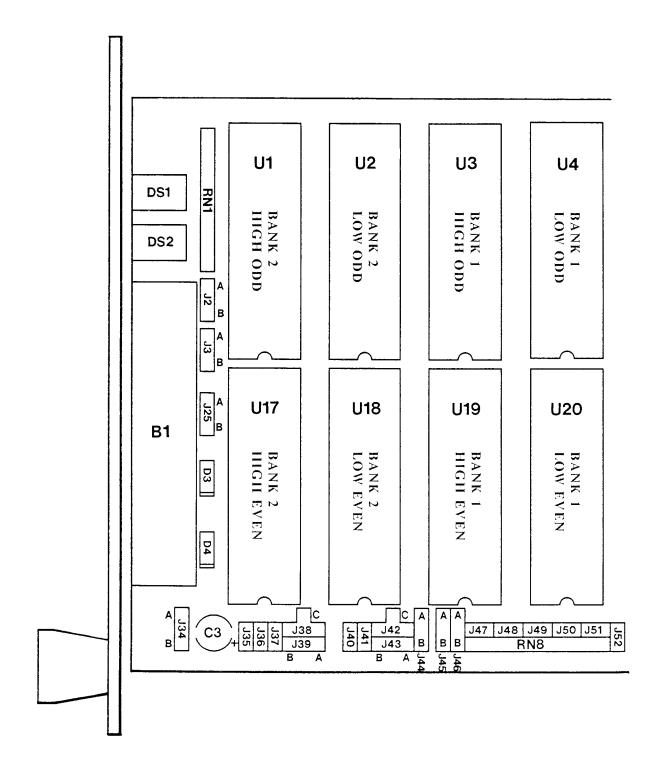

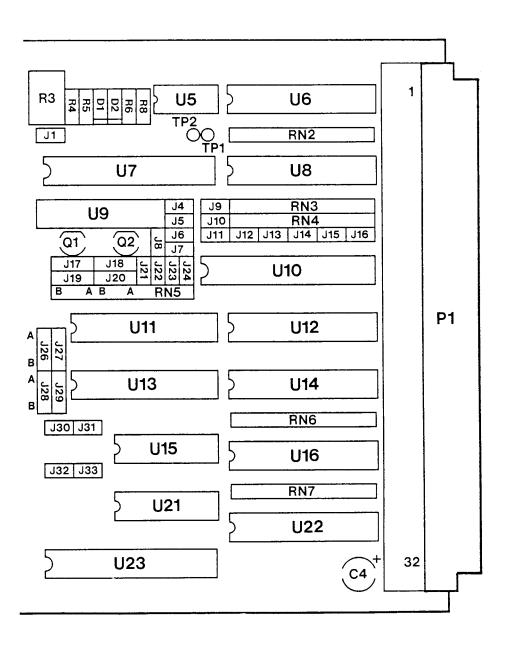

The jumpers, memory sockets, and the VMEbus P1 connector on the XVME-100 Memory Module are illustrated in Figure 2-1. Figure 2-1A show an expanded left side of the board, and Figure 2-1B the right for clarification purposes.

Figure 2-1. Location of Jumpers, Sockets, and Connector

Figure 2-1A. Expanded Left Side of XVME-100

Figure 2-1B. Expanded Right Side of XVME-100

## 2.3 JUMPERS

Prior to installing the XVME-100 Memory Module, it will be necessary to configure several jumper options. The configuration is dependant upon which type of memory devices to be used. The following table shows a list of the jumpers and a brief description of their use.

Table 2-1. Jumper List

| Jumper | Description                       | Section |

|--------|-----------------------------------|---------|

| J1     | Power Monitor Calibration         | 2.4.6   |

| J2     | Memory Type - bank 2              | 2.4.4   |

| J3     | Memory Type - bank 2              | 2.4.4   |

| J4     | Speed Select - bank 2             | 2.4.3   |

| J5     | Speed Select - bank 2             | 2.4.3   |

| Ј6     | Speed Select - bank 1             | 2.4.3   |

| J7     | Speed Select - bank 1             | 2.4.3   |

| Ј8     | SYSRESET* Driver, enable          | 2.4.6   |

| Ј9     | Data Access - bank 2              | 2.4.2   |

| J10    | Program Access - bank 1           | 2.4.2   |

| J11    | Data Access - bank 1              | 2.4.2   |

| J12    | Program Access - bank 2           | 2.4.2   |

| J13    | Supervisor Only - bank 1          | 2.4.2   |

| J14    | VME Address - bank 1              | 2.4.1   |

| J15    | Supervisor Only - bank 2          | 2.4.2   |

| J16    | VME Address - bank 2              | 2.4.1   |

| J17    | VME Address - bank 1              | 2.4.1   |

| J18    | VME Address - bank 1              | 2.4.1   |

| J19    | VME Address - bank 1              | 2.4.1   |

| J20    | VME Address - bank 1              | 2.4.1   |

| J21    | VME Address - bank 1              | 2.4.1   |

| J22    | VME Address - bank 1              | 2.4.1   |

| J23    | VME Address - bank 1              | 2,4,1   |

| J24    | VME Address - bank 1              | 2.4.1   |

| J25    | Memory Type - bank 2              | 2.4.4   |

| J26    | VME Address - bank 2              | 2.4.1   |

| J27    | VME Address - bank 2              | 2.4.1   |

| J28    | VME Address - bank 2              | 2.4.1   |

| J29    | VME Address - bank 2              | 2.4.1   |

| J30    | VME Address - bank 2              | 2.4.1   |

| J31    | VME Address - bank 2              | 2.4.1   |

| J32    | VME Address - bank 2              | 2.4.1   |

| J33    | VME Address - bank 2              | 2.4.1   |

| J34    | Battery, alternate power source   | 2.4.5   |

| J35    | +5V STDBY, alternate power source |         |

| J36    | Memory Type - bank 2              | 2.4.4   |

| J37    | Memory Type - bank 2              | 2.4.4   |

| J38    | Memory Type - bank 2              | 2.4.4   |

| J39    | Memory Type - bank 2              | 2.4.4   |

|        | inemory Type bank 2               | ۵,٦,٦   |

Table 2-1. Jumper List (continued)

| Jumper | Description          | Section |

|--------|----------------------|---------|

| J40    | Memory Type - bank 1 | 2.4.4   |

| Ј41    | Memory Type - bank 1 | 2.4.4   |

| J42    | Memory Type - bank 1 | 2.4.4   |

| J43    | Memory Type - bank 1 | 2.4.4   |

| J44    | Memory Type - bank 1 | 2,4,4   |

| J45    | Memory Type - bank 1 | 2.4.4   |

| J46    | Memory Type - bank 1 | 2.4.4   |

| J47    | Size Select - bank 2 | 2.4.1   |

| J48    | Size Select - bank 2 | 2,4,1   |

| J49    | Size Select - bank 2 | 2.4.1   |

| J50    | Size Select - bank 1 | 2.4.1   |

| J51    | Size Select - bank 1 | 2.4.1   |

| J52    | Size Select - bank 1 | 2.4.1   |

|        | Size series bunk i   | 2, 1, 1 |

#### 2.4 JUMPER DESCRIPTIONS

The two banks are independently configurable, via jumpers to define five different memory module parameters, these parameters are:

- 1. VME Address/Memory Chip Size

- 2. Address Modifier Decode

- 3. Memory Device Speed

- 4. Memory Device Pinout

- 5. Memory Backup Power

The following five subsections examines these jumper options in closer detail, showing specifically when and how jumpers should be configured.

## 2.4.1 VME Address/Memory Chip Size

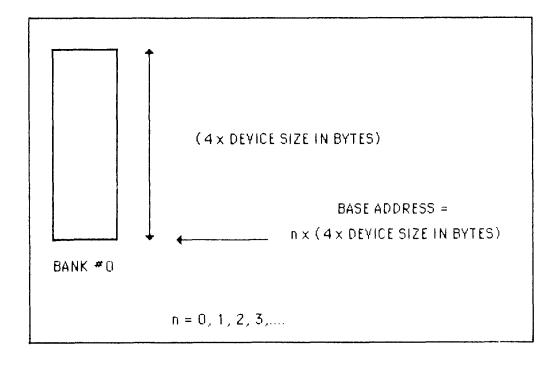

12 jumpers exist for each bank (24 total) to define the VMEbus address and memory chip size. Table 2-2 lists the jumpers and their definitions. The bank will occupy a VMEbus address space of four times the memory chip size. The bank must be assigned to a boundary which is a multiple of four times the memory chip size.

Table 2-2. VME Base Address and Memory Chip Size Jumpers

BANK 1

| BASE ADDRESS BIT                                            | = 1                                                                           |                                        |                       | = 0                                                             |                                       |                              |                              |                  |                  |                  |                  |                       |

|-------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------|-----------------------|-----------------------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------------------|------------------|------------------|------------------|-----------------------|

| A23<br>A22<br>A21<br>A20<br>A19<br>A18<br>A17<br>A16<br>A15 | J14 (<br>J23 (<br>J21 (<br>J22 (<br>J24 (<br>J20 (<br>J18 (<br>J19 (<br>J17 ( | Out<br>Out<br>Out<br>Out<br>Out<br>Out |                       | J14<br>J23<br>J21<br>J22<br>J24<br>J20E<br>J18E<br>J19E<br>J17E | In*<br>In*<br>In*<br>In*<br>In*<br>3* | * F:                         | actory<br>conf               | shipp<br>igura   |                  |                  |                  |                       |

| Device Size In Bits                                         | <u>J17</u>                                                                    | <u>J19</u>                             | <u>J18</u>            | <u>J20</u>                                                      | <u>J50</u>                            | <u>J51</u>                   | <u>J52</u>                   | <u>J14</u>       | <u>J23</u>       | <u>J21</u>       | <u>J22</u>       | <u>J24</u>            |

| 8K x 8<br>16K x 8<br>32K x 8<br>64K x 8<br>128K x 8         | X<br>A<br>A<br>A                                                              | X<br>X<br>A<br>A                       | X<br>X<br>X<br>A<br>A | X<br>X<br>X<br>X<br>A                                           | In<br>In<br>In<br>In<br>Out           | In<br>In<br>Out<br>Out<br>In | In<br>Out<br>In<br>Out<br>In | X<br>X<br>X<br>X | X<br>X<br>X<br>X | X<br>X<br>X<br>X | X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X |

X = Use to define state of corresponding base address bit per above chart

BANK 2

| BASE ADDRESS BIT                                            | =_1                                                         |                                        |                  | = 0                                                             |                                      |                              |                              |                  |                  |                       |                       |                  |

|-------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------|------------------|-----------------------------------------------------------------|--------------------------------------|------------------------------|------------------------------|------------------|------------------|-----------------------|-----------------------|------------------|

| A23<br>A22<br>A21<br>A20<br>A19<br>A18<br>A17<br>A16<br>A15 | J16<br>J31<br>J30<br>J33<br>J32<br>J28<br>J26<br>J29<br>J27 | Out<br>Out<br>Out<br>Out<br>Out<br>Out |                  | J16<br>J31<br>J30<br>J33<br>J32<br>J28A<br>J26A<br>J29A<br>J27A | In*<br>In*<br>In*<br>In*<br>A*<br>A* | * F                          | actory<br>conf               | y ship<br>igura  |                  |                       |                       |                  |

| Device Size In Bits                                         | <u>J27</u>                                                  | <u>J29</u>                             | <u>J26</u>       | <u>J28</u>                                                      | <u>J47</u>                           | <u>J48</u>                   | <u>J49</u>                   | <u>J16</u>       | <u>J31</u>       | <u>J30</u>            | <u>J33</u>            | <u>J32</u>       |

| 8K x 8<br>16K x 8<br>32K x 8<br>64K x 8<br>128K x 8         | X<br>B<br>B<br>B                                            | X<br>X<br>B<br>B                       | X<br>X<br>X<br>B | X<br>X<br>X<br>X<br>B                                           | In<br>In<br>In<br>In<br>Out          | In<br>In<br>Out<br>Out<br>In | In<br>Out<br>In<br>Out<br>In | X<br>X<br>X<br>X | X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X |

X = Use to define state of corresponding base address list per above chart XVME-100 Manual March, 1987

The following is an example of the jumpering required to install  $32K \times 8$  EPROMs in bank 1.

## EXAMPLE:

$27256\ 32K\ x\ 8$  EPROMs are to installed in bank 1 with a VMEbus base address of 8E0000 Hex.

| J17 | A   | İ  |    |

|-----|-----|----|----|

| J19 | A   | !  |    |

| J18 | OUT | i. |    |

| J20 | OUT | i  |    |

| J50 | IN  |    |    |

| J51 | OUT |    |    |

| J52 | IN  |    |    |

| J14 | OUT | ì  | 25 |

| J23 | IN  |    | 1  |

| J21 | IN  |    |    |

| J22 | IN  | 2  |    |

| J24 | OUT | 1  |    |

Bank 1 will reside in memory address:

8E0000 Hex. through 8FFFFF Hex.

Figure 2-2 shows the memory map for the XVME-100, and Figure 2-3 shows the bank addressing four times the memory chip size.

|            |           | WORD ADDRESS                                                       |

|------------|-----------|--------------------------------------------------------------------|

| EVEN BYTES | ODD BYTES | BASE ADDRESS +4 X DEVICE SIZE - 2                                  |

| U 19       | U 3       | BASE ADDRESS + 2 × DEVICE SIZE                                     |

| U 20       | U 4       | BASE ADDRESS + 2 x DEVICE SIZE - 2                                 |

|            |           | BASE ADDRESS                                                       |

| ВА         | NK 1      |                                                                    |

|            |           | WORD ADDRESS                                                       |

| EVEN BYTES | ODD BYTES | BASE ADDRESS +4 X DEVICE SIZE - 2                                  |

| U 17       | U 1       |                                                                    |

|            |           | BASE ADDRESS + 2 × DEVICE SIZE  BASE ADDRESS + 2 × DEVICE SIZE - 2 |

| U 18       | U 2       |                                                                    |

|            |           | BASE ADDRESS                                                       |

| ВА         | NK 2      |                                                                    |

Figure 2-2. XVME-100 Memory Map

Figure 2-3. Addressing - 4 x Chip Size

## 2.4.2 Address Modifier Decode

The address modifier decode uses three jumpers for each bank (6 total). Both banks reside in the standard A24 address space. The first jumper is the supervisor select, when the jumper is in, the bank will respond only to supervisor accesses, when the jumper is out, the bank will respond to supervisor and non-privileged accesses. During each access of a bank, that bank's LED (green) on the front panel, will momentarily light.

The second jumper is the data space select, when this jumper is in, the bank will respond to data accesses, when out, the bank won't respond to data accesses.

The third jumper is the program space select, when the jumper is in, the module will respond to program accesses, when out, the module won't respond to program accesses.

Table 2-3 lists these three jumpers and their definitions.

Table 2-3. Address Modifier Jumpers

#### BANK 1

| <u>Jumpers</u>     | Description                                                             |

|--------------------|-------------------------------------------------------------------------|

| J13 In*            | Supervisor Only AM2 = 1                                                 |

| J13 Out            | Supervisor & Non-privileged AM2 = don't care                            |

| Jll In*            | Data Access Responds to Address Modifier codes                          |

| Jll Out            | No Data Access Won't respond to 3DH or 39H                              |

| J10 In*<br>J10 Out | Program Access 3EH or 3AH No Program Access Won't respond to 3EH or 3AH |

#### BANK 2

| <u>Jumpers</u>     | Description                                                             |

|--------------------|-------------------------------------------------------------------------|

| J15 In*            | Supervisor Only AM2 = 1                                                 |

| J15 Out            | Supervisor & Non-privileged AM2 = don't care                            |

| J9 In*             | Data Access Responds to Address Modifier codes                          |

| J9 Out             | No Data Access Won't respond to 3DH or 39H                              |

| J12 In*<br>J12 Out | Program Access 3EH or 3AH No Program Access Won't respond to 3EH or 3AH |

<sup>\* =</sup> Factory shipped configuration

These three jumpers are independent of each other. When both the data space select and the program space select jumpers are out, the bank will be disabled from VMEbus accesses.

## 2.4.3 Memory Device Speed

Two jumpers exist for each bank (4 total) to define the speed of the memory devices. Selections are 100, 150, 200, and 250 ns devices. Table 2-4 lists the jumpers and speed definition for each device.

Table 2-4. Memory Device Speed Jumpers

#### BANK 1

| Speed Select | <u>Jumpers</u><br><u>J6 J7</u> |

|--------------|--------------------------------|

| 100ns        | Out Out                        |

| 150ns        | Out In                         |

| 200ns        | In Out                         |

| 250ns        | In* In*                        |

BANK 2

| Speed Select                     | <u>Jumpers</u><br><u>J4</u> <u>J5</u> |

|----------------------------------|---------------------------------------|

| 100ns<br>150ns<br>200ns<br>250ns | Out Out Out In In Out In*             |

<sup>\* =</sup> Factory shipped configuration

VMEbus access timing is a function of the memory device speed of the bank being accessed. Data strobe asserted to DTACK\* asserted will typically be 100 ns plus the chosen access time. Data strobe negated to DTACK\* negated will be 50 ns typical.

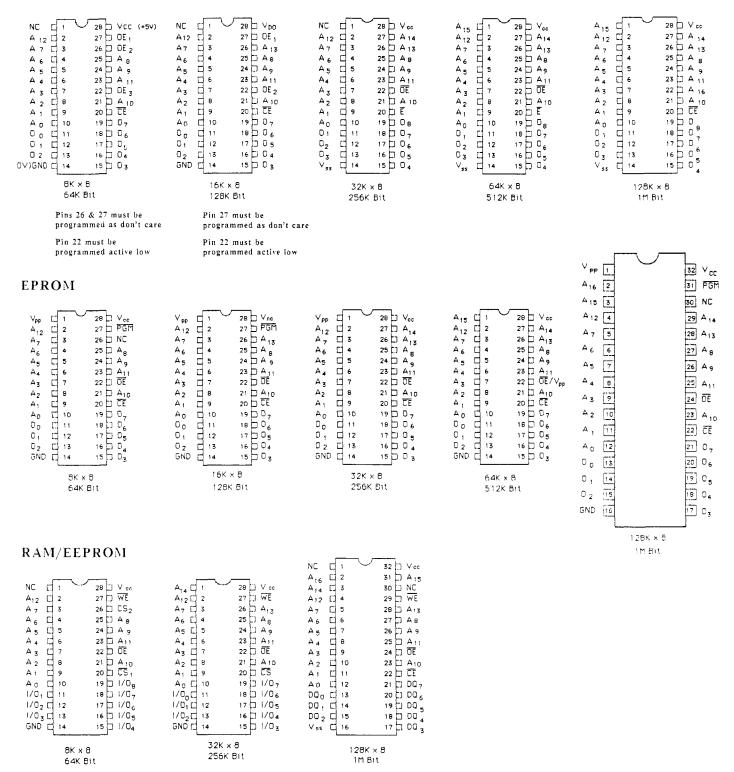

## 2.4.4 Memory Device Pinout

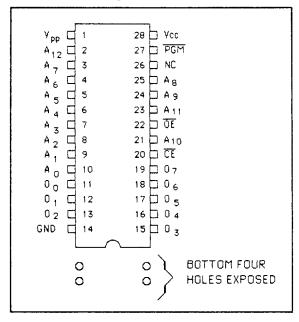

There are seven jumpers for each of the banks (14 total) on the XVME-100 which define the memory device pinout. Table 2-5 lists the jumpers and memory type. Figure 2-4 and show chip pinouts.

Table 2-5. Memory Device Pinout Jumpers

BANK 1

| Memory Type                                                                                                   |              | Jumpers    |              |              |                        |                  |                        |

|---------------------------------------------------------------------------------------------------------------|--------------|------------|--------------|--------------|------------------------|------------------|------------------------|

|                                                                                                               | <u>J45</u>   | <u>J43</u> | <u>J46</u>   | <u>J41</u>   | <u>J42</u>             | <u>J40</u>       | <u>J44</u>             |

| 64k/128k EPROM<br>256K EPROM<br>1 M ROM<br>64K RAM<br>256K/1M RAM<br>512K/1 M EPROM<br>64K/128K/256K/512K ROM | Out* B B A A | B* B A B B | Out* B B A A | In* X X X In | C*<br>C<br>B<br>X<br>A | In* In In Out In | B*<br>B<br>B<br>@<br>B |

BANK 2

| Memory Type                                                                                                   |              | Jumpers    |                |              |                        |                  |                             |

|---------------------------------------------------------------------------------------------------------------|--------------|------------|----------------|--------------|------------------------|------------------|-----------------------------|

|                                                                                                               | <u>J25</u>   | <u>J39</u> | <u>J2</u>      | <u>J37</u>   | <u>J38</u>             | <u>J36</u>       | <u>J3</u>                   |

| 64k/128k EPROM<br>256K EPROM<br>1 M ROM<br>64K RAM<br>256K/1M RAM<br>512K/1 M EPROM<br>64K/128K/256K/512K ROM | Out* B B A A | B* B A B B | Out* B B A A B | In* X X X In | C*<br>C<br>B<br>X<br>A | In* In In Out In | B*<br>B<br>B<br>@<br>@<br>B |

X = Don't Care

@ = For alternate power source J3A (See section 2.4.5 (BANK 2))

= For alternate power source J44A (See section 2.4.5 (BANK 1))

For System Vcc J3B (BANK 2) For System Vcc J44B (BANK 1)

<sup>\* =</sup> Factory shipped configuration

#### MASK PROGRAMMABLE ROM

Figure 2-4. Memory Chip Pinouts

## EXAMPLE:

Bank 1 8K x 8 RAM Memory device pinout jumpers

Memory Type J45 J43 J46 J41 J42 J40 J44

64k Bits A B A X X OUT @

Bank 2 Memory device pinout jumpers

$\underline{Memory\ Type} \quad \underline{J25} \quad \underline{J39} \quad \underline{J2} \quad \underline{J37} \quad \underline{J38} \quad \underline{J36} \quad \underline{J3}$

64K Bits A B A X X OUT @

X = Don't care

@ = Alternate power source

## 2.4.5 Memory Backup Power

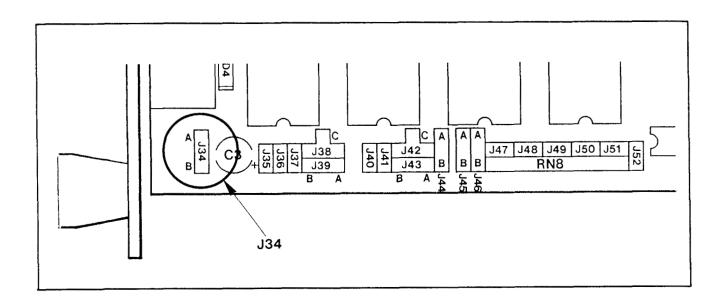

During power loss, the CMOS RAM chips may have an alternative power source connected to retain the data stored. Two alternative power sources are available: the on board battery and the +5V standby signal from the VMEbus. The following chart shows the jumper configuration for each option:

| Alternative |            |            |

|-------------|------------|------------|

| Power       |            |            |

| Source      | <u>J34</u> | <u>J35</u> |

|             |            |            |

| None        | A*         | Out*       |

| Battery     | В          | Out        |

| +5V Standby | A          | In         |

<sup>\*</sup> Factory shipped configuration

Figure 2-5. Location of Jumper J34

In order to achieve maximum battery life, RAM chips must have a small data retention current. Most static RAM suppliers have chips that guarantee very low data retention currents. These should be used to prolong battery life.

To calculate the typical battery life, use the following equation:

Hours of battery life =

$$\frac{1,400,000}{((n \times I_SB) + 10)}$$

where: I<sub>S</sub>B is the data retention current required by the particular RAM chips, in micro amperes

n = the # of RAM chips selected to be battery backed.

#### Example:

8 Hitachi 6264LP-15 are used, they have a typical I<sub>S</sub>B of 2 uA.

Battery Life =

$$\frac{1,400,000}{((8 \times 2) + 10)}$$

= 53850 hrs.

= 6.1 years

The shelf life of the battery is 10 years, so data retention cannot be guaranteed to be over 10 years regardless of the RAM chips used.

#### **CAUTION**

The following are some general precautions about batteries which should be adhered to:

- Do not short your battery

- Do not place module on a metal (conductive) surface

- Do not charge the battery

- Do not connect in wrong polarity (+, -) of the battery

- Do not directly solder onto the battery

- Do not use the battery at temperatures other than those specified

- Do not use with other types of batteries

- Do not heat the battery

- Do not incincrate the battery

The user has three different options available for choosing alternate power source of each bank. These options depend on the configurations of J34 and J35 and are as follows:

Alternate Power Source = Battery (J34B, J35 OUT)

| Bank 1 Power | <u>J44</u> |

|--------------|------------|

| Battery      | A          |

| Vcc*         | B          |

| Bank 2 Power | <u>J3</u>  |

| Battery      | A          |

| Vec*         | B          |

Alternate Power Source = +5V Standby (J34A, J35 IN)

| Bank 1 Power | <u>J44</u> |

|--------------|------------|

| +5V Standby  | A          |

| Vcc*         | B          |

| Bank 2 Power | <u>J3</u>  |

| +5V Standby  | A          |

| Vcc*         | B          |

Alternate Power Source = None (J34A, J35 OUT factory shipped configuration)

| Bank 1 Power | <u>J44</u> |

|--------------|------------|

| Vcc*         | В          |

| Bank 2 Power | <u>J3</u>  |

| Vcc*         | В          |

<sup>\*</sup> If EEPROM or EPROM are installed in any bank, the Vcc Jumper should be installed to prevent drawing current from the alternate power source.

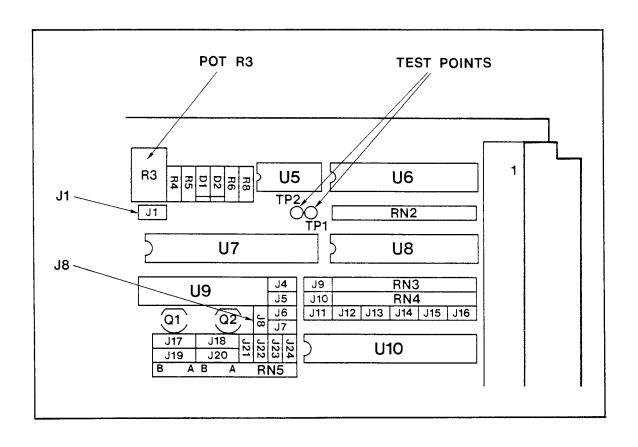

#### 2.4.6 Power Monitor

A power monitor is provided to disable the memory chips when Vcc falls below 4.75V. This monitor sometimes requires calibration. It is calibrated when it leaves the factory, however if the user has need to recalibrate, use the following procedure:

#### NOTE

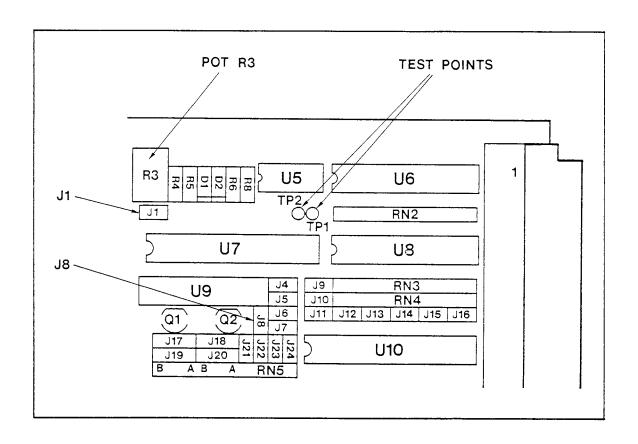

Refer to Figure 2-6 for location of jumpers and test points.

- 1) Apply power to the module while on an extender board.

- 2) Remove J1.

- 3) Connect the negative side of a 4.75V power reference to TP2 (ground).

- 4) Connect the positive side of the 4.75V power reference to the left terminal of J1.

- 5) Connect a volt meter or a scope to TP1.

- 6) If the voltage of TP1 is high ( > 4V ) then turn POT R3 counterclockwise, until the voltage of TP1 goes low ( < 0.8V ).

- 7) Slowly turn POT R3 clockwise until the point where the voltage of TP1 goes high. Stop turning POT R3 at this point.

- 8) Remove voltage reference, voltage meter and install J1.

- 9) The power monitor is now calibrated, apply glip to the POT's screw to prevent it from loosening.

A SYSRESET\* driver is provided to assert SYSRESET\* when the power monitor circuitry detects that Vcc is less than 4.75V. To enable the SYSRESET\* driver, install J8, and to disable the SYSRESET\* driver remove J8.

Figure 2-6 Location of Jumpers and Test Points

#### 2.5 INSTALLING MEMORY CHIPS ON THE XVME-100

As was previously mentioned, there are a total of eight 32-pin sockets intended for use by RAM, EPROM, EEPROM, and Mask Programmable ROM devices on the XVME-100 Module.

Installing memory in any of the sockets is simply a matter of setting the proper jumpers and installing the memory devices.

The following is the procedure for installing memory devices in the sockets on the XVME-100 Memory Module.

- 1) With all power removed form the board, locate the proper socket (see Figure 2-1 for location of sockets and banks).

- 2) Reference the notched end of the memory chips as shown in Figure 2-7. When installing a 28 pin chip, the chip should be oriented towards the bottom of the board, leaving the bottom holes exposed as shown below.

Figure 2-7. Notched End of the Memory Chip

3) Line up the pins on each chip with the socket holes found to the inside top of each socket location, and push each chip firmly, and evenly into place.

#### NOTE

Static precautions should be exerc sed when handling the memory chips, especially the CMOS RAM chips.

4) Check to make sure that the chips are fully seated in the bottom of the sockets, with no pins bent or out of alignment in the sockets.

#### 2.6 CALDCAGE INSTALLATION PROCEDURE

#### **CAUTION**

Do not attempt to install or remove any boards without first turning off the power to the bus, and all related external power supplies.

Prior to installing a module, you should determine and verify all relevant jumper configurations. (Please check the jumper configuration with the diagram and lists in the manual.)

To install a board in the cardcage, perform the following steps:

- 1) Make certain that the particular cardcage slot which you are going to use is clear and accessible.

- 2) Center the board on the plastic guides in the slot so that the handle on the front panel is towards the bottom of the cardcage.

- 3) Push the card slowly toward the rear of the chassis until the connector is fully engaged and properly seated.

#### NOTE

It should not be necessary to use excess pressure or force to engage the connectors. If the board does not properly connect with the backplane, remove the module and inspect all connectors and guide slots for possible damage or obstructions.

Once the board is properly seated, it should be secured by tightening the two machine screws at the extreme top and bottom of the front panel.

#### 2.7 INSTALLING A 6U FRONT PANEL KIT (optional)

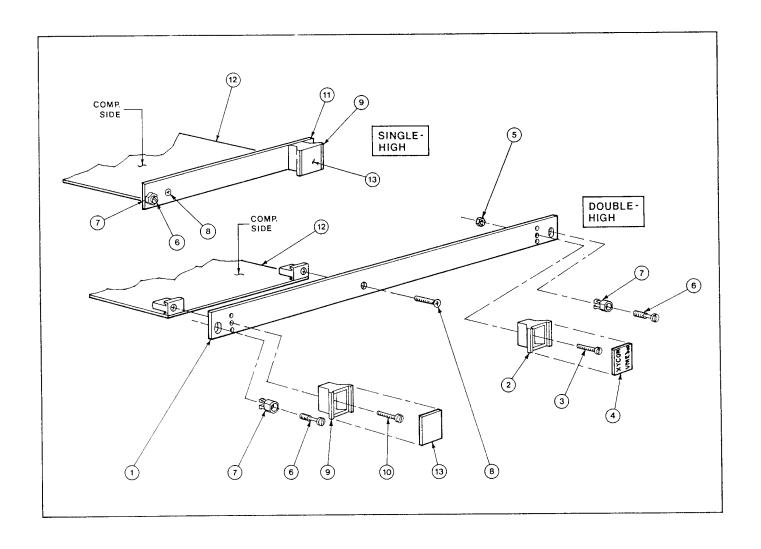

XYCOM Model Number XVME-945 is an optional 6U front panel kit designed to replace the existing 3U front panel on the XVME-100. The 6U front panel facilitates the <u>secure</u> installation of single-high modules in those chassis which are designed to accommodate double-high modules. The following is a step-by-step procedure for installing the 6U front panel on an XVME-100 Module (refer to figure 2-8 for a graphic depiction of the installation procedure).

- 1. Disconnect the module from the bus.

- 2. Remove the screw and plastic collar assemblies (labeled #6 and #7) from the extreme top and bottom of the existing 3U front panel (#11), and install the screw assemblies in their corresponding locations on the 6U front panel.

- 3. Slide the module identification plate (labeled #13) from the handle (#9) on the 3U front panel. By removing the screw/nut found inside the handle, the entire handle assembly will separate from the 3U front panel. Remove the counter-sunk screw (#8) to separate the 3U front panel from the printed circuit board (#12).

- 4. Line-up the plastic support brackets on the printed circuit board with the corresponding holes in the 6U front panel (i.e. the holes at the top and top-center of the panel). Install the counter-sunk screw (#8) in the hole near the top center of the 6U panel, securing it to the lower support bracket on the printed circuit board.

- 5. Install the handle assembly (which was taken from the 3U panel) at the top of the 6U panel, using the screw and nut previously attached inside the handle. After securing the top handle, slide the module identification plate in place.

- 6. Finally, install the bottom handle (i.e. the handle that accompanies the kit labeled #2) using the screw and nut (#3 & #5) provided. Slide the XYCOM VMEbus I.D. plate (#4) in place on the bottom handle. The module is now ready to be re-installed in the backplane.

Figure 2-8. Installation of an XVME-945 6U Front Panel

# Appendix A

# VMEbus CONNECTOR/PIN DESCRIPTION

Table A-1. P1 - VMEbus Signal Identification

| Signal<br>Mnemonic | Connector<br>and<br>Pin Number       | Signal Name and Description                                                                                                                                                                                   |

|--------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACFAIL*            | 1B:3                                 | AC FAILURE: Open-collectors driven signal which indicates that the AC input to the power supply is no longer being provided, or that the required input voltage levels are not being met.                     |

| IACKIN*            | 1A:21                                | INTERRUPT ACKNOWLEDGE IN: Totem-pole driven signal. IACKIN* and IACKOUT* signals form a daisy-chained acknowledge. The IACKIN* signal indicates to the VME board that an acknowledge cycle is in progress.    |

| IACKOUT*           | 1A:22                                | INTERRUPT ACKNOWLEDGE OUT: Totem-pole driven signal. IACKIN* and IACKOUT* signals form a daisy-chained acknowledge. The IACKOUT* signal indicates to the next board that an acknowledge cycle is in progress. |

| AM0-AM5            | 1A:23<br>1B:16,17,<br>18,19<br>1C:14 | ADDRESS MODIFIER (bits 0-5): Three-state driven lines that provide additional information about the address bus, such as: size, cycle type, and/or DTB master identification.                                 |

| AS*                | 1A:18                                | ADDRESS STROBE: Three-state driven signal that indicates a valid address is on the address bus.                                                                                                               |

Table A-1. VMEbus Signal Identification (cont'd)

| Signal<br>Mnemonic  | Connector<br>and<br>Pin Number | Signal Name and Description                                                                                                                                                                                                                |

|---------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A01-A23             | 1A:24-30<br>1C:15-30           | ADDRESS BUS (bits 1-23): Three-state driven address lines that specify a memory address.                                                                                                                                                   |

| A24-A31             | 2B:4-11                        | ADDRESS BUS (bits 24-31): Three-state driven bus expansion address lines.                                                                                                                                                                  |

| BBSY*               | 1B:1                           | BUS BUSY: Open-collector driven signal generated by the current DTB master to indicate that it is using the bus.                                                                                                                           |

| BCLR*               | 1B:2                           | BUS CLEAR: Totem-pole driven signal generated by the bus arbitrator to request release by the DTB master if a higher level is requesting the bus.                                                                                          |

| BERR*               | 1C:11                          | BUS ERROR: Open-collector driven signal generated by a slave. It indicates that an unrecoverable error has occurred and the bus cycle must be aborted.                                                                                     |

| BG0IN*-<br>BG3IN*   | 1B:4,6,<br>8,10                | BUS GRANT (0-3) IN: Totem-pole driven signals generated by the Arbiter or Requesters. Bus Grant In and Out signals form a daisy-chained bus grant. The Bus Grant In signal indicates to this board that it may become the next bus master. |

| BG0OUT*-<br>BG3OUT* | 1B:5,7,<br>9,11                | BUS GRANT (0-3) OUT: Totem-pole driven signals generated by Requesters. These signals indicate that a DTB master in the daisy-chain requires access to the bus.                                                                            |

Table A-1. VMEbus Signal Identification (cont'd)

| Signal<br>Mnemonie | Connector<br>and<br>Pin Number                                  | Signal Name and Description                                                                                                                                                                                                                                          |

|--------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR0*-BR3*          | 1B:12-15                                                        | BUS REQUEST (0-3): Open-collector driven signals generated by Requesters. These signals indicate that a DTB master in the daisy-chain requires access to the bus.                                                                                                    |

| DS0*               | 1A:13                                                           | DATA STROBE 0: Three-state driven signal that indicates during byte and word transfers that a data transfer will occur on data buss lines (D00-D07).                                                                                                                 |

| DS1*               | 1A:12                                                           | DATA STROBE 1: Three-state driven signal that indicates during byte and word transfers that a data transfer will occur on data bus lines (D0-D15).                                                                                                                   |

| DTACK*             | 1A:16                                                           | DATA TRANSFER ACKNOWLEDGE: Open-collector driven signal generated by a DTB slave. The falling edge of this signal indicates that valid data is available on the data bus during a read cycle, or that data has been accepted from the data bus during a write cycle. |

| D00-D15            | 1A:1-8<br>1C:1-8                                                | DATA BUS (bits 0-15): Three-state driven, bidirectional data lines that provide a data path between the DTB master and slave.                                                                                                                                        |

| GND                | 1A:9,11,<br>15,17,19,<br>1B:20,23,<br>1C:9<br>2B:2,12,<br>22,31 | GROUND                                                                                                                                                                                                                                                               |

Table A-1. VMEbus Signal Identification (cont'd)

| Signal<br>Mnemonic | Connector<br>and<br>Pin Number | Signal Name and Description                                                                                                                                                                                                                                             |

|--------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IACK*              | 1A:20                          | INTERRUPT ACKNOWLEDGE: Open-collector or three-state driven signal from any master processing an interrupt request. It is routed via the backplane to slot 1, where it is looped-back to become slot 1 IACKIN* in order to start the interrupt acknowledge daisy-chain. |

| IRQ1*-<br>IRQ7*    | 1B:24-30                       | INTERRUPT REQUEST (1-7): Open-collector driven signals, generated by an interrupter, which carry prioritized interrupt requests. Level seven is the highest priority.                                                                                                   |

| LWORD*             | 1C:13                          | LONGWORD: Three-state driven signal indicates that the current transfer is a 32-bit transfer.                                                                                                                                                                           |

| (RESERV-<br>ED)    | 2B:3                           | RESERVED: Signal line reserved for future VMEbus enhancements. This line must not be used.                                                                                                                                                                              |

| SERCLK             | 1B:21                          | A reserved signal which will be used as the clock for a serial communication bus protocol which is still being finalized.                                                                                                                                               |

| SERDAT             | 1B:22                          | A reserved signal which will be used as the transmission line for serial communication bus messages.                                                                                                                                                                    |

| SYSCLK             | 1A:10                          | SYSTEM CLOCK: A constant 16-MHz clock signal that is independent of processor speed or timing. It is used for general system timing use.                                                                                                                                |

Table A-1. VMEbus Signal Identification (cont'd)

| Signal<br>Mnemonic | Connector<br>and<br>Pin Number        | Signal Name and Description                                                                                                                                                                         |

|--------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSFAIL*           | 1C:10                                 | SYSTEM FAIL: Open-collector driven signal that indicates that a failure has occurred in the system. It may be generated by any module on the VMEbus.                                                |

| SYSRESET*          | 1C:12                                 | SYSTEM RESET: Open-collector driven signal which, when low, will cause the system to be reset.                                                                                                      |

| WRITE*             | 1A:14                                 | WRITE: Three-state driven signal that specifies the data transfer cycle in progress to be either read or written. A high level indicates a read operation, a low level indicates a write operation. |

| +5V STDBY          | 1B:31                                 | +5 VDC STANDBY: This line supplies +5 VDC to devices requiring battery backup.                                                                                                                      |

| +5V                | 1A:32<br>1B:32<br>1C:32<br>2B:1,13,32 | +5 VDC POWER: Used by system logic circuits.                                                                                                                                                        |

| +12V               | 1C:31                                 | +12 VDC POWER: Used by system logic circuits.                                                                                                                                                       |

| -12V               | 1A:31                                 | -12 VDC POWER: Used by system logic circuits.                                                                                                                                                       |

### **BACKPLANE CONNECTOR P1**

The following table lists the P1 pin assignments by pin number order. (The connector consists of three rows of pins labeled rows A, B, and C.)

Table A-2. P1 Pin Assignments

| Pin<br>Number                                                                          | Row A<br>Signal<br>Mnemonic                                                                                                                            | Row B<br>Signal<br>Mnemonic                                                                                                                                                                                         | Row C<br>Signal<br>Mnemonic                                                                                                                      |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 | D00 D01 D02 D03 D04 D05 D06 D07 GND SYSCLK GND DS1* DS0* WRITE* GND DTACK* GND AS* GND IACK* IACKIN* IACKOUT* AM4 A07 A06 A05 A04 A03 A02 A01 -12V +5V | BBSY* BCLR* ACFAIL* BG0IN* BG0OUT* BG1IN* BG1OUT* BG2IN* BG2OUT* BG3IN* BG3OUT* BR0* BR1* BR2* BR3* AM0 AM1 AM2 AM3 GND SERCLK(1) SERDAT(1) GND IRQ7* IRQ6* IRQ7* IRQ6* IRQ5* IRQ4* IRQ3* IRQ2* IRQ1* +5V STDBY +5V | D08 D09 D10 D11 D12 D13 D14 D15 GND SYSFAIL* BERR* SYSRESET* LWORD* AM5 A23 A22 A21 A20 A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A09 A08 +12V +5V |

#### Appendix B

#### POWER MONITOR

A power monitor is provided to disable the memory chips when VCC falls below 4.75V. This monitor sometimes requires calibration. It is calibrated when it leaves the factory, however it may be necessary to recelebrate after an extended amount of time. To calibrate the power monitor perform the following steps:

#### NOTE

Refer to Figure B-1 for location of jumpers and test points.

- 1) Apply power to the module while on an extender board.

- 2) Remove J1.

- 3) Connect the negative side of a 4.75V power reference to TP2 (ground).

- 4) Connect the positive side of the 4.75V power reference to the left terminal of J1.

- 5) Connect a volt meter or a scope to TP1.

- 6) If the voltage of TP1 is high ( > 4V ) then turn POT R3 counterclockwise, until the voltage of TP1 goes low ( < 0.8V ).

- 7) Slowly turn POT R3 clockwise until the point where the voltage of TP1 goes high. Stop turning POT R3 at this point.

- 8) Remove voltage reference, voltage meter and install J1.

- 9) The power monitor is now calibrated, apply glip to the POT's screw to prevent it from loosening.

A SYSRESET\* driver is provided to assert SYSRESET\* when the power monitor detects that VCC is less than 4.75V. To enable the SYSRESET\* driver, install J8, and to disable the SYSRESET\* driver remove J8.

Figure B-1. Location of Jumpers and Test Points

Appendix C

DIAGRAM AND SCHEMATICS

Operational Block Diagram

## Appendix D

## QUICK REFERENCE GUIDE

Table D-1. Jumper List

| Jumper   | Description                       | Section |

|----------|-----------------------------------|---------|

| T 1      | Power Monitor Calibration         | 2.4.6   |

| J1<br>J2 | i i                               | 2.4.4   |

|          | Memory Type - bank 2              | 2.4.4   |

| J3       | Memory Type - bank 2              | 2.4.4   |

| J4       | Speed Scleet - bank 2             | 2.4.3   |

| J5       | Speed Select - bank 2             |         |

| J6       | Speed Select - bank 1             | 2.4.3   |

| J7       | Speed Select - bank 1             | 2.4.3   |

| J8       | SYSRESET* Driver, enable          | 2.4.6   |

| J9       | Data Access - bank 2              | 2.4.2   |

| J10      | Program Access - bank 1           | 2.4.2   |

| J11      | Data Access - bank 1              | 2.4.2   |

| J12      | Program Access - bank 2           | 2.4.2   |

| J13      | Supervisor Only - bank 1          | 2.4.2   |

| J14      | VME Address - bank 1              | 2.4.1   |

| J15      | Supervisor Only - bank 2          | 2.4.2   |

| J16      | VME Address - bank 2              | 2.4.1   |

| J17      | VME Address - bank 1              | 2.4.1   |

| J18      | VME Address - bank 1              | 2.4.1   |

| J19      | VME Address - bank 1              | 2.4.1   |

| J20      | VME Address - bank 1              | 2.4.1   |

| J21      | VME Address - bank 1              | 2.4.1   |

| J22      | VME Address - bank 1              | 2.4.1   |

| J23      | VME Address - bank 1              | 2.4.1   |

| J24      | VME Address - bank 1              | 2.4.1   |

| J25      | Memory Type - bank 2              | 2.4.4   |

|          | • •                               | 2.4.1   |

| J26      | VME Address - bank 2              |         |

| J27      | VME Address - bank 2              | 2.4.1   |

| J28      | VME Address - bank 2              | 2.4.1   |

| J29      | VME Address - bank 2              | 2.4.1   |

| J30      | VME Address - bank 2              | 2.4.1   |

| J31      | VME Address - bank 2              | 2.4.1   |

| J32      | VME Address - bank 2              | 2.4.1   |

| J33      | VME Address - bank 2              | 2.4.1   |

| J34      | Battery, alternate power source   | 2.4.5   |

| J35      | +5V STDBY, alternate power source |         |

| J36      | Memory Type - bank 2              | 2.4.4   |

| J37      | Memory Type - bank 2              | 2.4.4   |

| Ј38      | Memory Type - bank 2              | 2.4.4   |

| J39      | Memory Type - bank 2              | 2.4.4   |

| J40      | Memory Type - bank 1              | 2.4.4   |

| J41      | Memory Type - bank 1              | 2.4.4   |

| J42      | Memory Type - bank 1              | 2.4.4   |

Table 3- umper List (continued)

| Jumper | Description          | Section |  |

|--------|----------------------|---------|--|

| J43    | Memory Type - bank 1 | 2.4.4   |  |

| J44    | Memory Type - bank 1 | 2.4.4   |  |

| J45    | Memory Type - bank 1 | 2.4.4   |  |

| J46    | Memory Type - bank 1 | 2.4.4   |  |

| J47    | Size Select - bank 2 | 2.4.1   |  |

| J48    | Size Select - bank 2 | 2.4.1   |  |

| J49    | Size Select - bank 2 | 2.4.1   |  |

| J50    | Size Select - bank 1 | 2.4.1   |  |

| J51    | Size Select - bank 1 | 2.4.1   |  |

| J52    | Size Select - bank 1 | 2.4.1   |  |

Table D-2. VME Base Address and Memory Chip Size Jumpers

BANK 1

| BASE ADDRESS BIT                                            | = 1                                                                           |                                 |                       | = 0                                                             |                                       |                              |                              |                  |                  |                  |                  |                  |

|-------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------|-----------------------|-----------------------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------------------|------------------|------------------|------------------|------------------|

| A23<br>A22<br>A21<br>A20<br>A19<br>A18<br>A17<br>A16<br>A15 | J14 (<br>J23 (<br>J21 (<br>J22 (<br>J24 (<br>J20 (<br>J18 (<br>J19 (<br>J17 ( | Out Out Out Out Out Out Out Out |                       | J14<br>J23<br>J21<br>J22<br>J24<br>J20E<br>J18E<br>J19E<br>J17E | In*<br>In*<br>In*<br>In*<br>In*<br>}* | * Fa                         | ectory<br>conf               | ship;<br>igura   |                  |                  |                  |                  |

| Device Size In Bits                                         | <u>J17</u>                                                                    | <u>J19</u>                      | <u>J18</u>            | <u>J20</u>                                                      | <u>J50</u>                            | <u>J51</u>                   | <u>J52</u>                   | <u>J14</u>       | <u>J23</u>       | <u>J21</u>       | <u>J22</u>       | <u>J24</u>       |

| 8K x 8<br>16K x 8<br>32K x 8<br>64K x 8<br>128K x 8         | X<br>A<br>A<br>A                                                              | X<br>X<br>A<br>A                | X<br>X<br>X<br>A<br>A | X<br>X<br>X<br>X<br>A                                           | In<br>In<br>In<br>In<br>Out           | In<br>In<br>Out<br>Out<br>In | In<br>Out<br>In<br>Out<br>In | X<br>X<br>X<br>X | X<br>X<br>X<br>X | X<br>X<br>X<br>X | X<br>X<br>X<br>X | X<br>X<br>X<br>X |

X = Use to define state of corresponding base address bit per above chart

BANK 2

| BASE ADDRESS BIT                                            | = 1                                                                           |                                        |                  | = 0                                                                 |                                       |                              |                              |                  |                       |                       |                       |                       |

|-------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------|------------------|---------------------------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| A23<br>A22<br>A21<br>A20<br>A19<br>A18<br>A17<br>A16<br>A15 | J16 (<br>J31 (<br>J33 (<br>J33 (<br>J32 (<br>J28 (<br>J26 (<br>J29 (<br>J27 ( | Out<br>Out<br>Out<br>Out<br>Out<br>Out |                  | J16<br>J31<br>J30<br>J33<br>J32<br>J28 A<br>J26 A<br>J29 A<br>J27 A | In*<br>In*<br>In*<br>In*<br>In*<br>A* | * F                          | actor <u>y</u><br>conf       | y ship<br>igura  | -                     |                       |                       |                       |

| Device Size In Bits                                         | <u>J27</u>                                                                    | <u>J29</u>                             | <u>J26</u>       | <u>J28</u>                                                          | <u>J47</u>                            | <u>J48</u>                   | <u>J49</u>                   | <u>J16</u>       | <u>J31</u>            | <u>J30</u>            | <u>J33</u>            | <u> 132</u>           |

| 8K x 8<br>16K x 8<br>32K x 8<br>64K x 8<br>128K x 8         | X<br>B<br>B<br>B                                                              | X<br>X<br>B<br>B                       | X<br>X<br>X<br>B | X<br>X<br>X<br>X<br>B                                               | In<br>In<br>In<br>In<br>Out           | In<br>In<br>Out<br>Out<br>In | In<br>Out<br>In<br>Out<br>In | X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X |

X = Use to define state of corresponding base address list per above chart

Table D-3. Address Modifier Jumpers

### BANK 1

| <u>Jumpers</u>     | <u>Description</u>                                                      |

|--------------------|-------------------------------------------------------------------------|

| J13 In*<br>J13 Out | Supervisor Only AM2 = 1<br>Supervisor & Non-privileged AM2 = don't care |

| Jll In*            | Data Access Responds to Address Modifier codes 3DH or 39H               |

| J11 Out            | No Data Access Won't respond to 3DH or 39H                              |

| J10 In*<br>J10 Out | Program Access 3EH or 3AH No Program Access Won't respond to 3EH or 3AH |

### BANK 2

| Jumpers            | <u>Description</u>                                                      |

|--------------------|-------------------------------------------------------------------------|

| J15 In*<br>J15 Out | Supervisor Only AM2 = 1<br>Supervisor & Non-privileged AM2 = don't care |

| J9 In*             | Data Access Responds to Address Modifier codes 3DH or 39H               |

| J9 Out             | No Data Access Won't respond to 3DH or 39H                              |

| J12 In*<br>J12 Out | Program Access 3EH or 3AH No Program Access Won't respond to 3EH or 3AH |

<sup>\* =</sup> Factory shipped configuration

Table D-4. Memory Device Speed Jumpers

BANK 1

| Speed Select | <u>Jumpers</u><br><u>J6</u> <u>J7</u> |

|--------------|---------------------------------------|

| 100ns        | Out Out                               |

| 150ns        | Out In                                |

| 200ns        | In Out                                |

| 250ns        | In* In*                               |

BANK 2

| Speed Select | <u>Jumpers</u><br><u>J4 J5</u> |

|--------------|--------------------------------|

| 100ns        | Out Out                        |

| 150ns        | Out In                         |

| 200ns        | In Out                         |

| 250ns        | In* In*                        |

<sup>\* =</sup> Factory shipped configuration

| Alternative<br>Power |            |            |

|----------------------|------------|------------|

| Source               | <u>J34</u> | <u>J35</u> |

| None                 | <b>A*</b>  | Out*       |

| Battery              | В          | Out        |

| +5V Standby          | Α          | In         |

<sup>\*</sup> Factory shipped configuration

The user has three different options available for choosing alternate power source of each bank. These options depend on the configurations of J34 and J35 and are as follows:

Alternate Power Source = Battery (J34B, J35 OUT)

| Bank 1 Power | <u>J4</u> |

|--------------|-----------|

| Battery      | A         |

| Vcc*         | B         |

| Bank 2 Power | <u>J3</u> |

| Battery      | A         |

| Vcc*         | B         |

Alternate Power Source = +5V Standby (J34A, J35 IN)

| Bank 1 Power | <u>J4</u> . |

|--------------|-------------|

| +5V Standby  | A           |

| Vcc*         | B           |

| Bank 2 Power | <u>J3</u>   |

| +5V Standby  | A           |

| Vcc*         | B           |

Alternate Power Source = None (J34A, J35 OUT factory shipped configuration)

| Bank 1 Power | <u>J44</u>                                                             |

|--------------|------------------------------------------------------------------------|

| Vcc*         | В                                                                      |

| Bank 2 Power | <u>J3</u>                                                              |

| Vcc*         | Binstalled to prevent drawing current from the alternate power source. |

<sup>\*</sup> If EEPROM or EPROM are installed in any bank, the Vcc Jumper should be installed to prevent drawing current from the alternate power source.

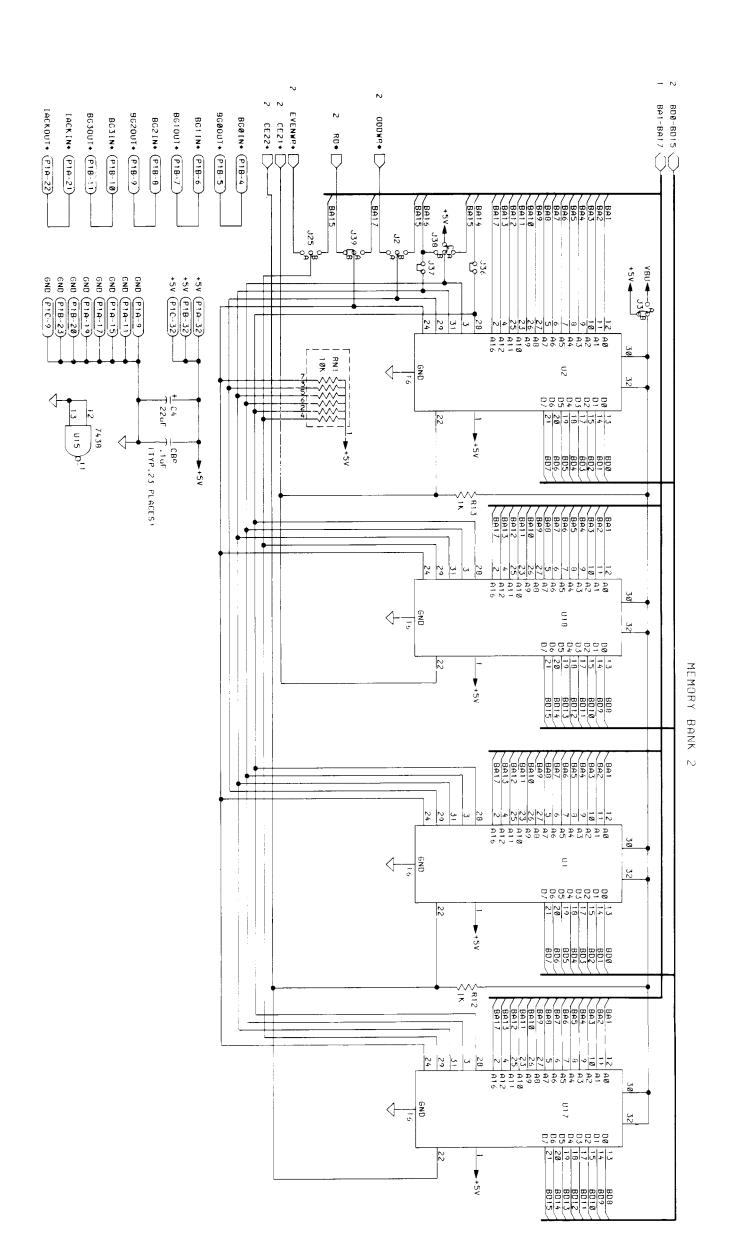

XVME-100 Schematic, Sheet 2 of 4

# Artisan Technology Group is an independent supplier of quality pre-owned equipment

## **Gold-standard solutions**

Extend the life of your critical industrial, commercial, and military systems with our superior service and support.

# We buy equipment

Planning to upgrade your current equipment? Have surplus equipment taking up shelf space? We'll give it a new home.

### Learn more!

Visit us at artisantg.com for more info on price quotes, drivers, technical specifications, manuals, and documentation.

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

We're here to make your life easier. How can we help you today? (217) 352-9330 | sales@artisantg.com | artisantg.com