### **4-Channel FFT Dynamic Signal Analyzer**

\$6450.00

In Stock

Oty Available: 1

Used and in Excellent Condition

**Open Web Page**

https://www.artisantg.com/85085-4

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

- Critical and expedited services

- In stock / Ready-to-ship

- We buy your excess, underutilized, and idle equipment

- Full-service, independent repair center

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

· Press the following keys:

```

[ System Utility ]

[ MORE ]

[ SERVICE TESTS ]

[ ADJUSTMTS ]

[ ADC ADJUSTMNT ]

[ OFFSET ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

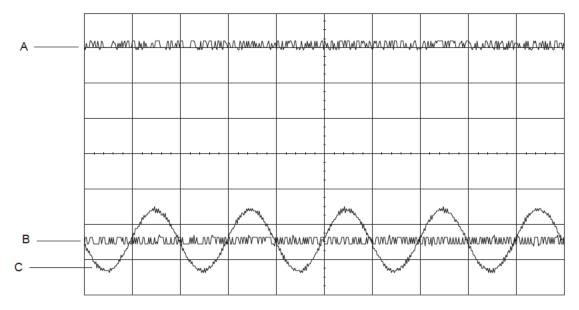

• If the oscilloscope display looks like the following figure, go to step 17. The following describes the signals shown on the oscilloscope display:

<sup>&</sup>quot;C" A clean sine wave in the lower half of the display.

R431 and R405 Correctly Adjusted

- If trace "B" is not flat, adjust A5 R431.

- If trace ''C'' is not centered over trace ''B,'' adjust A5 R405.

- Set the power switch to off (O).

- Disconnect the jumper from A5 TP8 and A5 TP300. Reconnect the cable to A5 P4.

<sup>&#</sup>x27;A' A straight, horizontal trace in the upper half of the display.

<sup>&</sup>quot;B" A "noisy" flat trace at the center of the sine wave trace.

## To adjust the input dc offset

This procedure minimizes the residual dc response of the A1/A2 Input assemblies. The standard two channel analyzer has one A1 Input assembly. The optional four channel analyzer has two A2 Input assemblies: channel 1 and 3 are routed to the A2 Input assembly in the lower slot and channel 2 and 4 are routed to the A2 Input assembly in the upper slot.

#### **Equipment Required:** None

- ☐ For the standard two channel analyzer, do the following to adjust input dc offset:

- Set the power switch to on ( 1 ).

- Press the following keys:

```

[ System Utility ]

[ MORE ]

[ SERVICE TESTS ]

[ ADJUSTMTS ]

[ CHANNEL 1 ADJUSTMNT ]

[ OFFSET ]

```

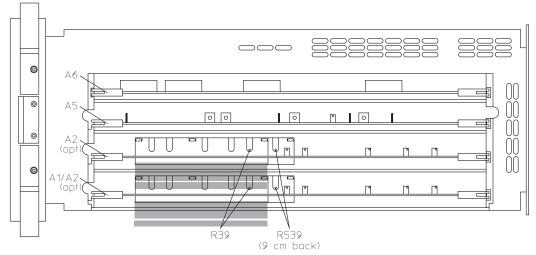

- Adjust A1 R39 for a Y: reading of 90 dBVrms or less.

- Press the following keys:

```

[ Rtn ]

[ CHANNEL 2 ADJUSTMNT ]

[ OFFSET ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

• Adjust A1 R539 for a Y: reading of 90 dBVrms or less.

- ☐ For the optional four channel analyzer, do the following to adjust input dc offset:

- Set the power switch to on (1).

- Press the following keys:

```

[ System Utility ]

[ MORE ]

[ SERVICE TESTS ]

[ ADJUSTMTS ]

[ CHANNEL 1 ADJUSTMNT ]

[ OFFSET ]

```

- Adjust A2 R39 in the lower slot for a Y: reading of 90 dBVrms or less.

- Press the following keys:

```

[ Rtn ]

[ CHANNEL 2 ADJUSTMNT ]

[ OFFSET ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

- Adjust A2 R39 in the upper slot for a Y: reading of 90 dBVrms or less.

- Press the following keys:

```

[ Rtn ]

[ CHANNEL 3 ADJUSTMNT ]

[ OFFSET ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

- Adjust A2 R539 in the lower slot for a Y: reading of 90 dBVrms or less.

- Press the following keys:

```

[ Rtn ]

[ CHANNEL 4 ADJUSTMNT ]

[ OFFSET ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

• Adjust A2 R539 in the upper slot for a Y: reading of 90 dBVrms or less.

# To adjust common mode rejection

This procedure optimizes the common mode rejection of the A1/A2 Input assemblies. The standard two channel analyzer has one A1 Input assembly. The optional four channel analyzer has two A2 Input assemblies: channel 1 and 3 are routed to the A2 Input assembly in the lower slot and channel 2 and 4 are routed to the A2 Input assembly in the upper slot.

Equipment Required: BNC-to-BNC Cable

BNC(f)-to-Minigrabber Adapter

- ☐ For the standard two channel analyzer, do the following to adjust common mode rejection:

- Set the power switch to off (O).

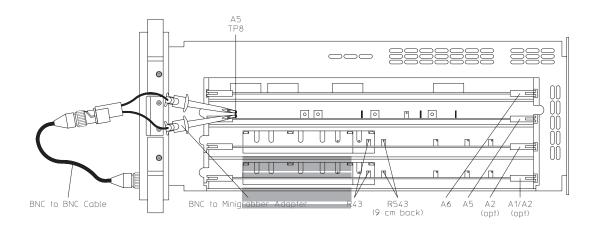

- Connect the BNC(f)-to-minigrabber adapter to the BNC cable. Connect both minigrabber clips (signal and ground) to A5 TP8 and the BNC connector to the analyzer's CH 1 connector.

- Set the power switch to on (1).

- Press the following keys:

```

[ System Utility ]

[ MORE ]

[ SERVICE TESTS ]

[ ADJUSTMTS ]

[ CHANNEL 1 ADJUSTMNT ]

[ CMRR ]

```

- While monitoring the Y: value, adjust A1 R43 for a minimum marker value.

- Disconnect the BNC cable from the analyzer's CH 1 connector and connect to the CH 2 connector.

- Press the the following keys:

```

[ Rtn ]

[ CHANNEL 2 ADJUSTMNT ]

[ CMRR ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

• While monitoring the Y: value, adjust A1 R543 for a minimum marker value.

- ☐ For the optional four channel analyzer, do the following to adjust common mode rejection:

- Set the power switch to off (O).

- Connect the BNC(f)-to-minigrabber adapter to the BNC cable. Connect both minigrabber clips (signal and ground) to A5 TP8 and the BNC connector to the analyzer's CH 1 connector.

- Set the power switch to on (1).

- Press the following keys:

```

[ System Utility ]

[ MORE ]

[ SERVICE TESTS ]

[ ADJUSTMTS ]

[ CHANNEL 1 ADJUSTMNT ]

[ CMRR ]

```

- While monitoring the Y: value, adjust A2 R43 in the lower slot for a minimum marker value.

- Disconnect the BNC cable from the analyzer's CH 1 connector and connect to the CH 2 connector.

- Press the the following keys:

```

[ Rtn ]

[ CHANNEL 2 ADJUSTMNT ]

[ CMRR ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

- While monitoring the Y: value, adjust A2 R43 in the upper slot for a minimum marker value.

- Disconnect the BNC cable from the analyzer's CH 2 connector and connect to the CH 3 connector.

- Press the the following keys:

```

[ Rtn ]

[ CHANNEL 3 ADJUSTMNT ]

[ CMRR ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

- While monitoring the Y: value, adjust A2 R543 in the lower slot for a minimum marker value.

- Disconnect the BNC cable from the analyzer's CH 3 connector and connect to the CH 4 connector.

- Press the the following keys:

```

[ Rtn ]

[ CHANNEL 4 ADJUSTMNT ]

[ CMRR ]

```

- While monitoring the Y: value, adjust A2 R543 in the upper slot for a minimum marker value.

- Set the power switch to off (  ${\bf O}$  ) and disconnect the minigrabber clips from A5 TP8.

## To adjust filter flatness

This procedure adjusts the anti-alias filter on the A1/A2 Input assemblies. The standard two channel analyzer has one A1 Input assembly. The optional four channel analyzer has two A2 Input assemblies: channel 1 and 3 are routed to the A2 Input assembly in the lower slot and channel 2 and 4 are routed to the A2 Input assembly in the upper slot.

Equipment Required: None

- ☐ For the standard two channel analyzer, do the following to adjust filter flatness:

- Set the power switch to on ( 1 ).

- Press the following keys:

```

[ System Utility ]

[ MORE ]

[ SERVICE TESTS ]

[ ADJUSTMTS ]

[ CHANNEL 1 ADJUSTMNT ]

[ 50 kHz ]

```

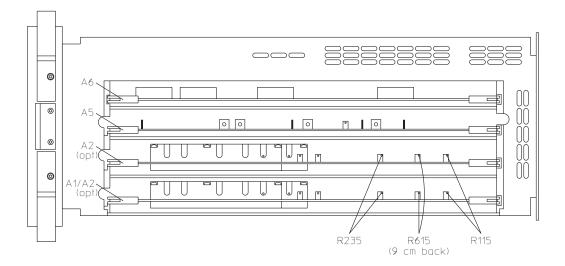

- While monitoring the Yr: value, adjust A1 R115 for a marker value of 0 0.1 dB.

- Press the [ 100 kHz FLATNESS ] softkey.

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

- While monitoring the Yr: value, adjust A1 R235 for a marker value of 0 0.1 dB.

- Press the following keys:

```

[ Rtn ]

[ CHANNEL 2 ADJUSTMNT ]

[ 50 kHz FLATNESS ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

While monitoring the Yr. value, adjust A1 R615 for a marker value of 0 0.1 dB.

- ☐ For the optional four channel analyzer, do the following to adjust filter flatness:

- Set the power switch to on ( 1 ).

- Press the following keys:

```

[ System Utility ]

[ MORE ]

[ SERVICE TESTS ]

[ ADJUSTMTS ]

[ CHANNEL 1 ADJUSTMNT ]

[ 25 kHz ]

```

- While monitoring the Yr: value, adjust A2 R115 in the lower slot for a marker value of 0  $\pm$ 0.1 dB.

- Press the [ 50 kHz FLATNESS ] softkey.

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

- While monitoring the Yr: value, adjust A2 R235 in the lower slot for a marker value of 0  $\pm$ 0.1 dB.

- Press the following keys:

```

[ Rtn ]

[ CHANNEL 2 ADJUSTMNT ]

[ 25 kHz FLATNESS ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

- While monitoring the Yr. value, adjust A2 R115 in the upper slot for a marker value of 0 ±0.1 dB.

- Press the [ 50 kHz FLATNESS ] softkey.

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

• While monitoring the Yr. value, adjust A2 R235 in the upper slot for a marker value of 0  $\pm$ 0.1 dB.

• Press the following keys:

```

[ Rtn ]

[ CHANNEL 3 ADJUSTMNT ]

[ 25 kHz FLATNESS ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

- While monitoring the Yr: value, adjust A2 R615 in the lower slot for a marker value of 0 0.1 dB.

- Press the following keys:

```

[ Rtn ]

[ CHANNEL 4 ADJUSTMNT ]

[ 25 kHz FLATNESS ]

```

Wait for the analyzer to set up the adjustment. The analyzer is ready when the adjustment message appears on the screen.

• While monitoring the Yr. value, adjust A2 R615 in the upper slot for a marker value of 0 0.1 dB.

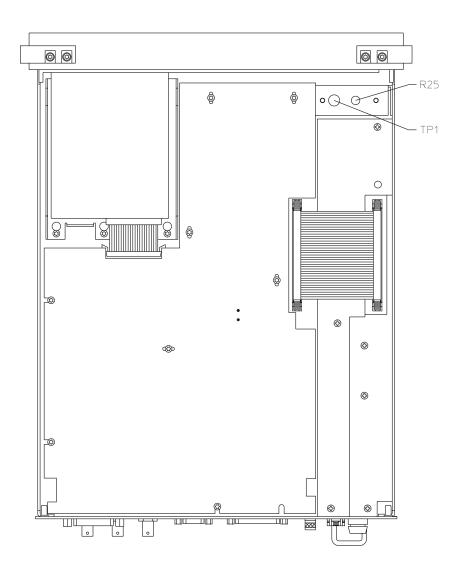

## To adjust the display voltage

This procedure adjusts the A102 DC-DC Converter assembly's display voltage to match the voltage required by the A101 Display assembly. This adjustment is only required when the DC-DC Converter assembly or the Display assembly is replaced.

**Equipment Required:** Multimeter

#### Warning

The display voltage is +210 Vdc 10 Vdc nominal. Use caution when performing this adjustment to avoid personal injury.

- Set the power switch to off (O).

- Record the V(ALL ON): voltage.

The V(ALL ON): voltage is printed on a sticker on the component side of the Display assembly. The V(ALL ON): voltage is normally between +200 Vdc and +220 Vdc.

#### Caution

Do not adjust the display voltage above +230 Vdc. The Display assembly can be damaged if the voltage is adjusted above +230 Vdc.

- Turn A102 R25 clockwise to its stop.

- Set the multimeter to a range greater than 220 Vdc and connect to A102 TP1 using a shielded test clip.

- Set the power switch to on (1).

- Using a non-metalic flat-edge adjustment tool, adjust A102 R25 for the voltage recorded in step 2.

- Set the power switch to off.

6

Replacing Assemblies

|         | Replacing Assemblies                                                                                                                                                                                                                |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|         | This chapter tells you what to do before and after you replace an assembly and shows you how to disassemble the analyzer.                                                                                                           |  |  |

| Warning | Disconnect the power cord from the rear panel before disassembly or assembly of the Agilent 35670A.                                                                                                                                 |  |  |

|         | Even with power removed, there can be sufficient stored energy in some circuits to cause personal injury. These voltages will discharge to a relatively safe level approximately five seconds after the power cord is disconnected. |  |  |

| Caution | Do not connect or disconnect cables from circuit assemblies with the line power turned on (1).                                                                                                                                      |  |  |

|         | To protect circuits from static discharge, remove or replace assemblies only at static-protected work stations.                                                                                                                     |  |  |

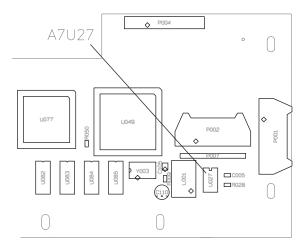

# What to do before replacing the CPU assembly

The analyzer's serial number and firmware options are stored in EEPROM (U27) on the A7 CPU assembly. Before replacing the CPU assembly, remove A7 U27 from the faulty assembly and insert into the new assembly.

#### Caution

All firmware options will be lost if A7 U27 is not removed from the faulty assembly and inserted into the new assembly.

# What to do after replacing an assembly

- Reinstall all assemblies and cables that were removed during troubleshooting.

- Do the required adjustments listed in the following table.

- Do the self test, page 4-31.

- Do the required performance tests listed in the following table.

| <b>Assembly Replaced</b> | Required Adjustment                                                                                                                      | Required Performance Test                                                                                                                                                                                 |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1 Input                 | ADC gain, offset and reference, page 5-7<br>Input dc offset, page 5-10<br>Common mode rejection, page 5-13<br>Filter flatness, page 5-17 | DC offset Noise Spurious signals Amplitude accuracy Flatness Amplitude linearity A-weight filter Channel match ICP supply                                                                                 |

| A2 Input                 | ADC gain, offset and reference, page 5-7<br>Input dc offset, page 5-10<br>Common mode rejection, page 5-13<br>Filter flatness, page 5-17 | DC offset Noise Spurious signals Amplitude accuracy Flatness Amplitude linearity A-weight filter Channel match ICP supply                                                                                 |

| A5 Analog                | Source, page 5-6<br>ADC, page 5-7<br>Input dc offset, page 5-10                                                                          | DC offset Noise Spurious signals Amplitude accuracy Flatness Amplitude linearity Channel match Single channel phase accuracy External trigger Source amplitude accuracy Source flatness Source distortion |

| A6 Digital               |                                                                                                                                          | Source amplitude accuracy<br>Source dc offset<br>Source flatness                                                                                                                                          |

| Assembly Replaced          | Required Adjustment           | Required Performance Test                           |

|----------------------------|-------------------------------|-----------------------------------------------------|

| A7 CPU                     | Frequency reference, page 5-5 | Frequency accuracy                                  |

| A8 Memory                  |                               |                                                     |

| A9 NVRAM                   |                               |                                                     |

| A10 Rear Panel             |                               | Tach function (option 1D0 only)<br>External trigger |

| A11 Keyboard<br>Controller |                               |                                                     |

| A12 BNC                    |                               |                                                     |

| A13 Primary Keypad         |                               |                                                     |

| A14 Secondary<br>Keypad    |                               |                                                     |

| A22 BNC                    |                               |                                                     |

| A90 Fan                    |                               |                                                     |

| A98 Power Supply           |                               |                                                     |

| A99 Motherboard            |                               |                                                     |

| A100 Disk Drive            |                               |                                                     |

| A101 Display               | Display voltage, page 5-21    |                                                     |

| A102 DC-DC<br>Converter    | Display voltage, page 5-21    |                                                     |

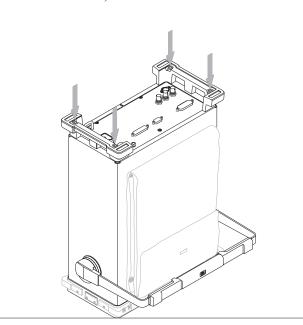

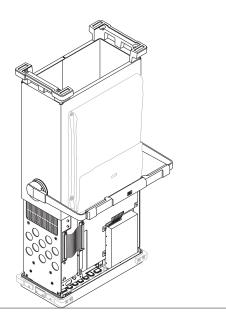

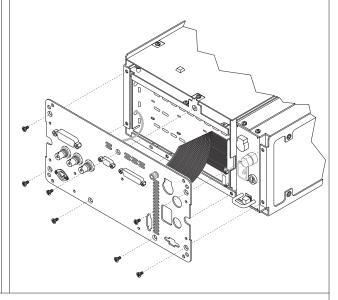

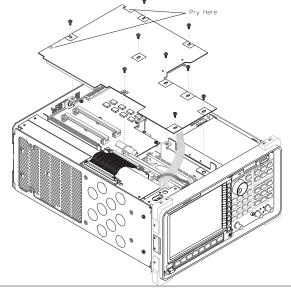

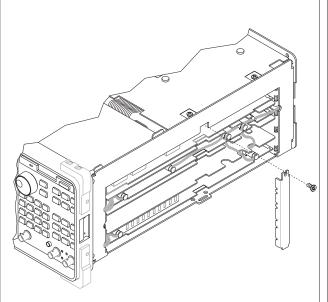

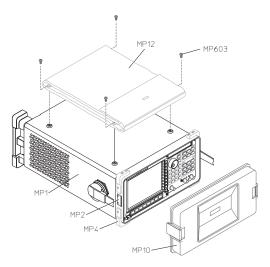

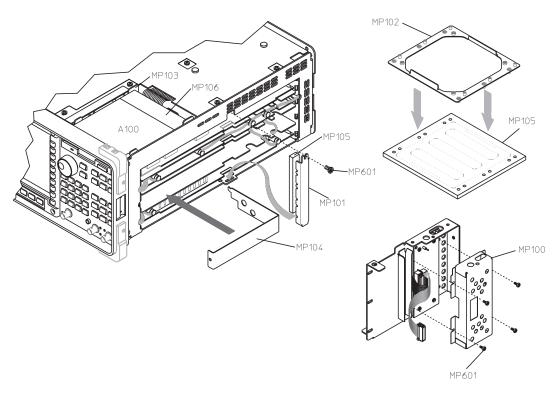

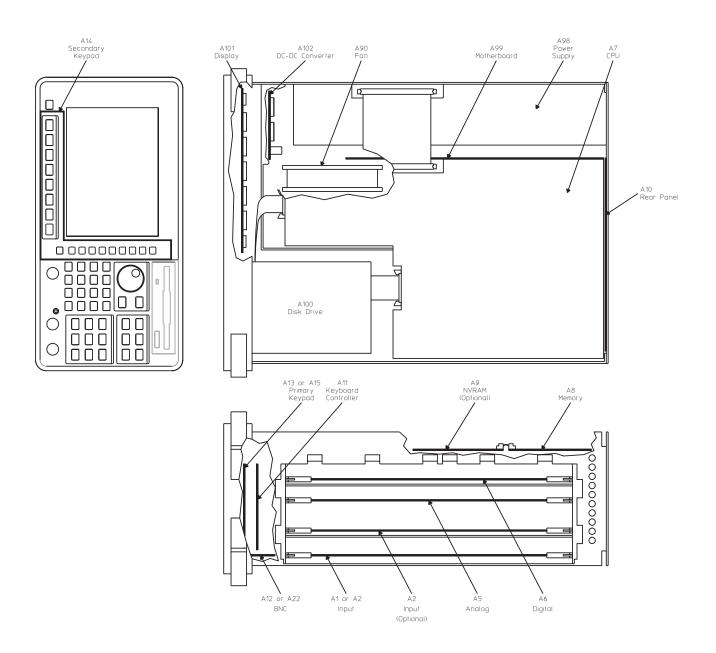

### To remove cover

$\begin{array}{c} 1 \\ \text{4 mm hex driver, loosen the four corner screws.} \end{array}$

2 Slide the cover straight up.

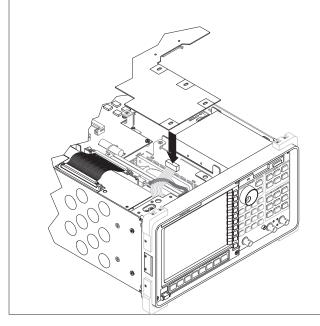

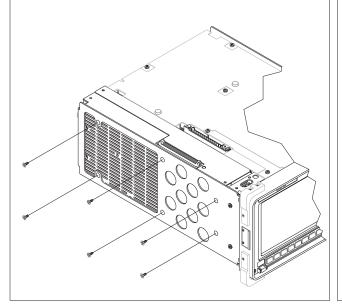

## To remove rear panel

Remove cover (see ''To remove cover'').

2 Using a T-15 torx driver, remove the seven screws from the rear panel. Pull the rear panel straight off.

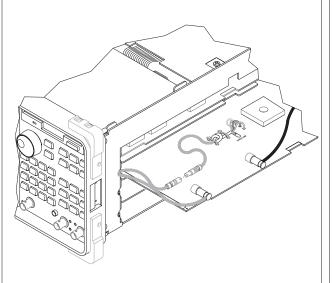

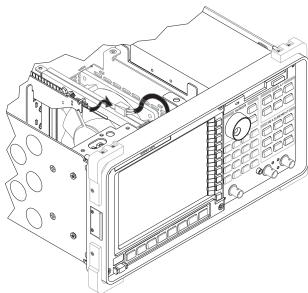

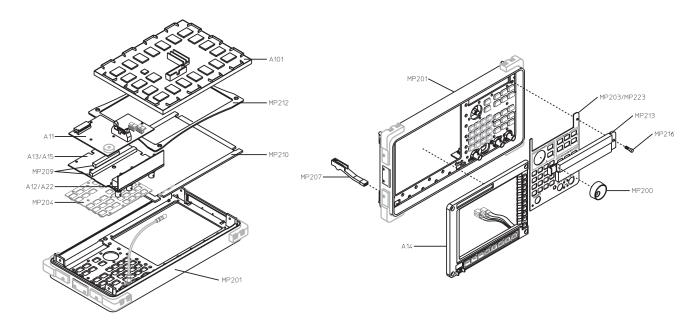

## To remove front panel

Remove cover (see ''To remove cover'').

3 Slide A5 Analog assembly part way out and disconnect gray mic cable.

4 Using a T-15 torx driver, remove the two screws on each side of the front panel.

| 5 Pull the top of the front panel out of the frame. | 6 Disconnect the ribbon cables from the front panel. Disconnect the coaxial cables connected to the A12/A22 BNC assembly. |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|                                                     |                                                                                                                           |

|                                                     |                                                                                                                           |

|                                                     |                                                                                                                           |

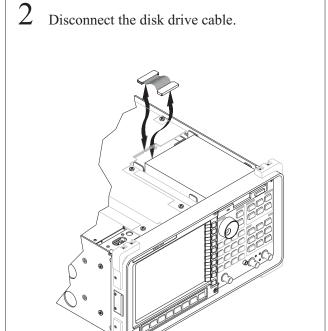

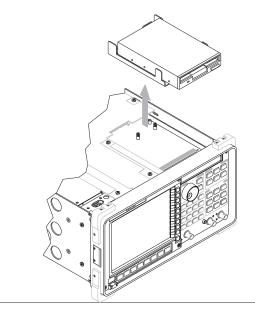

# To remove disk drive

Remove cover (see ''To remove cover'').

3 Using a T-10 torx driver, loosen the three screws at the back of the disk drive bracket.

4 Slide the disk drive back and lift up.

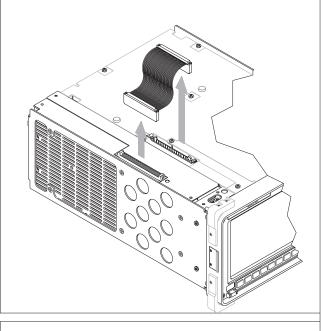

#### To remove CPU

Remove cover (see ''To remove cover'').

Using a T-10 torx driver, remove the nine screws from the A7 CPU assembly. Lift the assembly up, unpluging the A7 CPU assembly from the A8 Memory assembly and A99 Motherboard.

3 Disconnect the ribbon cables from the A7 CPU assembly.

The analyzer's serial number and firmware options are stored in EEPROM (U27) on the A7 CPU assembly. Before replacing the CPU assembly, remove A7 U27 from the faulty assembly and insert into the new assembly. See "What to do before replacing the CPU assembly" on page 6-3.

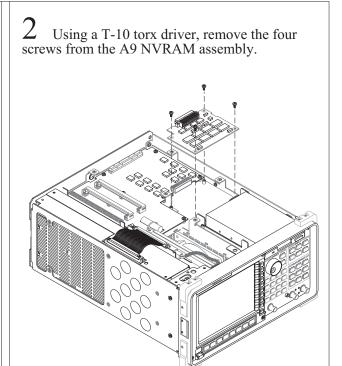

### To remove NVRAM

Remove A7 CPU assembly (see ''To remove CPU'').

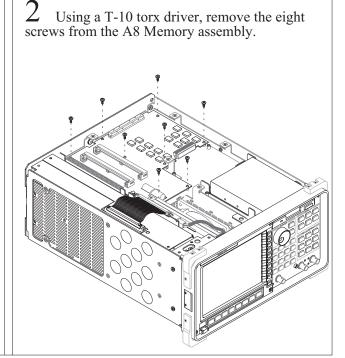

### To remove memory

Remove A7 CPU assembly (see ''To remove CPU''). Remove optional A9 NVRAM assembly (see ''To remove NVRAM'').

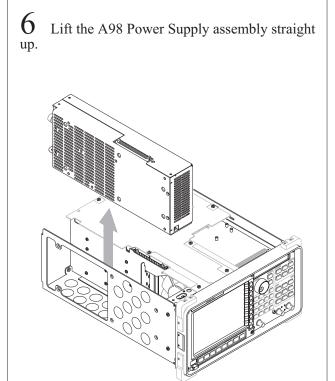

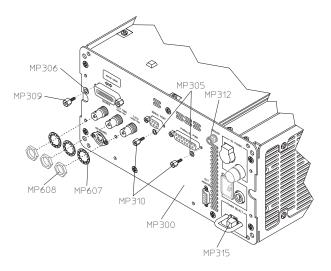

## To remove power supply

Remove rear panel (see "To remove rear panel").

2 Disconnect the ribbon cable from the A98 Power Supply assembly.

3 Using a T-15 torx driver, remove the six screws from the A98 Power Supply assembly.

4 Set the front panel power switch in the off (O) position (switch in the out position).

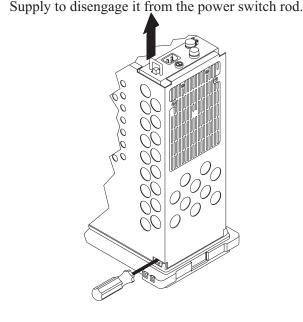

5 Using a straight-edge screw driver, hold the power switch rod in position and lift the A98 Power Supply to disengage it from the power switch rod.

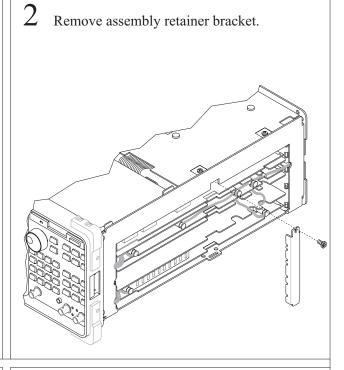

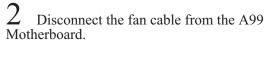

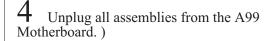

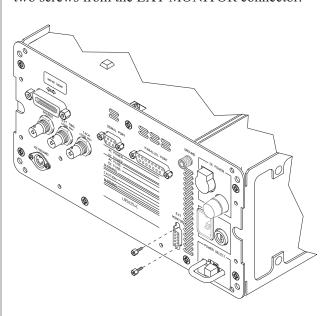

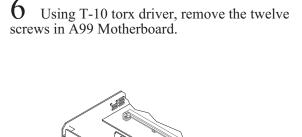

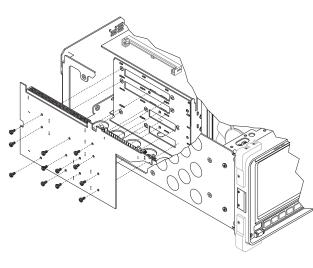

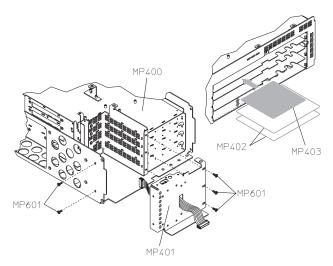

### To remove motherboard

Remove A98 Power Supply assembly (see "To remove power supply"). Remove A7 CPU assembly (see "To remove CPU").

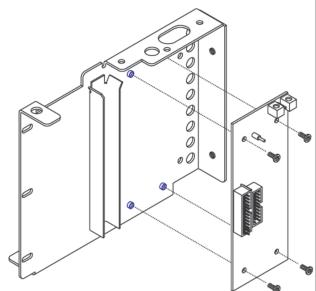

3 Remove assembly retainer bracket.

5 Using a 5 mm open-ended wrench, remove the two screws from the EXT MONITOR connector.

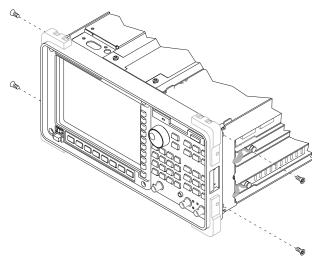

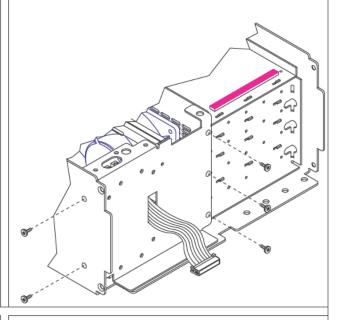

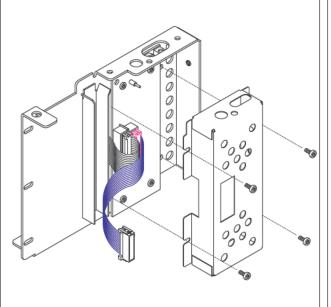

### To remove dc-dc converter

Remove front panel (see "To remove front panel"). Remove A7 CPU assembly (see "To remove CPU").

2 Using a T-10 torx driver, remove the five screws from the front wall.

3 Using a T-10 torx driver, remove the four screws from the shield. Unplug ribbon cables.

4 Using a T-10 torx driver, remove the four screws from the A102 DC-DC Converter assembly.

7

Replaceable Parts

### Replaceable Parts

This chapter contains information for ordering replacement parts for the Agilent 35670A Dynamic Signal Analyzer.

### **Ordering Information**

Replacement parts are listed in the following ten tables:

- Assemblies

- Cables

- Instrument Covers and Handles

- Assembly Covers and Brackets

- Front Panel Parts

- · Rear Panel Parts

- · Chassis Parts

- Card Nest Parts

- Screws, Washers, and Nuts

- Miscellaneous Parts

To order a part listed in one of the tables, quote the Agilent Technologies part number (HP Part Number), the check digit (CD), indicate the quantity required, and address the order to the nearest Agilent Technologies sales and service office (see the inside back cover of this guide). The check digit verifies that an order has been transmitted correctly, ensuring accurate and timely processing of the order. The first time a part is listed in the table, the quantity column (Qty) lists the total quantity of the part used in the analyzer. For definitions of the abbreviations and the corresponding name and address of the manufacturers' codes shown in the tables, see 'Code Numbers.'

Caution

Many of the parts listed in this chapter are static sensitive. Use the appropriate precautions when removing, handling, and installing all parts to avoid unnecessary damage.

#### **Non-Listed Parts**

To order a part that is NOT listed in the replaceable parts tables, indicate the instrument model number, instrument serial number, description and function of the part, and the quantity of the part required. Address the order to the nearest Agilent Technologies sales and service office (see the inside back cover of this guide).

#### **Direct Mail Order System**

Within the U.S.A., Agilent Technologies can supply parts through a direct mail order system. Advantages of the Direct Mail Order System are:

- Direct ordering and shipment from the Agilent Parts Center.

- No maximum or minimum on any mail order. There is a minimum order for parts ordered through a local Agilent sales and service office when the orders require billing and invoicing.

- Transportation charges are prepaid. A small handling charge is added to each order.

- No invoicing. A check or money order must accompany each order.

- Mail order forms and specific ordering information are available through your local Agilent Technologies sales and service office. See the inside back cover of this guide for a list of Agilent Technologies sales and service office locations and addresses.

#### **Code Numbers**

The following table provides the name and address for the manufacturers' code numbers (Mfr Code) listed in the replaceable parts tables.

| LEMO USA, Inc.                   | Santa Rosa, CA 95406 U.S.A.                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Amp Inc.                         | Harrisburg, PA 17105 U.S.A.                                                                                                                                                                                                                                                                                                                                                   |

| Koszegi Industries Inc.          | South Bend, IN 46624 U.S.A.                                                                                                                                                                                                                                                                                                                                                   |

| Lyn-Tron Inc                     | Burbank, CA 91505 U.S.A.                                                                                                                                                                                                                                                                                                                                                      |

| C & K Components Inc             | Newton, MA 02158 U.S.A.                                                                                                                                                                                                                                                                                                                                                       |

| Epson America Inc.               | Dallas, TX 75284 U.S.A.                                                                                                                                                                                                                                                                                                                                                       |

| Computer Products Inc.           | Chicago, IL 60693 U.S.A.                                                                                                                                                                                                                                                                                                                                                      |

| Fuji Polymer Industries Co. Inc. | Nagoya-Shi Japan                                                                                                                                                                                                                                                                                                                                                              |

| Specialty Connector Co           | Franklin, IN 46131 U.S.A.                                                                                                                                                                                                                                                                                                                                                     |

| Agilent Technologies Company     | Palo Alto, CA 94304 U.S.A.                                                                                                                                                                                                                                                                                                                                                    |

| Instrument Specialties Co. Inc.  | Placentia, CA 92670 U.S.A.                                                                                                                                                                                                                                                                                                                                                    |

| Dek Inc.                         | St Charles, IL 60174 U.S.A.                                                                                                                                                                                                                                                                                                                                                   |

| Thomas & Betts Corp              | Bridgewater, NJ 08807 U.S.A                                                                                                                                                                                                                                                                                                                                                   |

| Chomerics Shielding Technology   | Carson, CA 90745 U.S.A.                                                                                                                                                                                                                                                                                                                                                       |

| Cooper Industries Inc            | St Louis, MO 63178 U.S.A.                                                                                                                                                                                                                                                                                                                                                     |

| Federal Screw Products Co.       | Chicago, IL 60618 U.S.A.                                                                                                                                                                                                                                                                                                                                                      |

| Littelfuse Inc.                  | Des Plaines, IL 60016 U.S.A.                                                                                                                                                                                                                                                                                                                                                  |

| 3M Co.                           | Seattle, WA 98124 U.S.A.                                                                                                                                                                                                                                                                                                                                                      |

|                                  | Amp Inc.  Koszegi Industries Inc.  Lyn-Tron Inc  C & K Components Inc  Epson America Inc.  Computer Products Inc.  Fuji Polymer Industries Co. Inc.  Specialty Connector Co  Agilent Technologies Company  Instrument Specialties Co. Inc.  Dek Inc.  Thomas & Betts Corp  Chomerics Shielding Technology  Cooper Industries Inc  Federal Screw Products Co.  Littelfuse Inc. |

#### Assemblies

After replacing an assembly, see "What to do after replacing an assembly" in chapter 6 for required adjustments and performance tests.

The reference designator for the screws that fasten the A90 Fan assembly is MP600. The reference designator for the screws that fasten the A98 Power Supply assembly is MP603. The reference designator for the screws that fasten all other assemblies is MP601.

| Ref<br>Des | Agilent Part<br>Number | CD | Qty | Description                          | Mfr<br>Code | Mfr Part<br>Number |

|------------|------------------------|----|-----|--------------------------------------|-------------|--------------------|

|            |                        |    |     |                                      |             |                    |

| A1         | 35670 69501            | 9  | 1   | INPUT ASSEMBLY 2 CHANNEL             | 28480       | 35670 69501        |

| A2         | 35670 69502            | 0  | 2   | INPUT ASSEMBLY 4 CHANNEL             | 28480       | 35670 69502        |

| A5         | 35670 69505            | 3  | 1   | ANALOG ASSEMBLY                      | 28480       | 35670 69505        |

| A6         | 35670 69506            | 4  | 1   | DIGITAL ASSEMBLY                     | 28480       | 35670 69506        |

| A7         | 35670 69507            | 5  | 1   | CPU ASSEMBLY †                       | 28480       | 35670 69507        |

| A8         | 35670 66508            | 6  | 1   | MEMORY ASSEMBLY                      | 28480       | 35670 66508        |

| A9         | 35670 66509            | 7  | 1   | NVRAM ASSEMBLY                       | 28480       | 35670 66509        |

| A10        | 35670 66510            | 4  | 1   | REAR PANEL ASSEMBLY                  | 28480       | 35670 66510        |

| A11        | 35670 66511            | 5  | 1   | KEYBOARD CONTROLLER                  | 28480       | 35670 66511        |

| A12        | 35670 66512            | 6  | 1   | BNC ASSEMBLY 2 CHANNEL               | 28480       | 35670 66512        |

| A13        | 35670 66513            | 7  | 1   | PRIMARY KEYPAD ASSEMBLY 2<br>CHANNEL | 28480       | 35670 66513        |

| A14        | 35670 64300            | 6  | 1   | SECONDARY KEYPAD ASSEMBLY            | 28480       | 35670 64300        |

| A15        | 35670 66515            | 9  | 1   | PRIMARY KEYPAD ASSEMBLY 4<br>CHANNEL | 28480       | 35670 66515        |

| A22        | 35670 66522            | 8  | 1   | BNC ASSEMBLY 4 CHANNEL               | 28480       | 35670 66522        |

| A90        | 03585 68501            | 6  | 1   | FAN ASSEMBLY                         | 28480       | 03585 68501        |

| A98        | 0950 2357              | 9  | 1   | POWER SUPPLY ASSEMBLY                | 11919       | NFS177 7630        |

| A99        | 35670 66599            | 9  | 1   | MOTHERBOARD                          | 28480       | 35670 66599        |

| A100       | 0950 2141              | 9  | 1   | DISK DRIVE ASSEMBLY                  | 10421       | SMD 340            |

| A101       | 2090 0340              | 9  | 1   | DISPLAY ASSEMBLY                     | 28480       | 2090 0340          |

| A102       | 0950 2335              | 3  | 1   | DC DC CONVERTER ASSEMBLY             | 28480       | 0950 2335          |

$<sup>\</sup>dagger$  The analyzer's serial number and firmware options are stored in EEPROM (U27) on the A7 CPU assembly. Before replacing the CPU assembly, remove A7 U27 from the faulty assembly and insert into the new assembly. See ''What to do before replacing the CPU assembly'' on page 6 3.

### Cables

| Ref<br>Des | Agilent Part<br>Number | CD | Qty | Description                    | Mfr<br>Code | Mfr Part<br>Number |

|------------|------------------------|----|-----|--------------------------------|-------------|--------------------|

|            |                        |    |     |                                |             |                    |

| W1         | 03585 61603            | 5  | 2   | CBL ASM CXL FSMB/FSMB 100MM OR | 28480       | 03585 61603        |

| W2         | 03585 61604            | 6  | 3   | CBL ASM CXL FSMB/FSMB 177MM YL | 28480       | 03585 61604        |

| W3         | 03586 61678            | 5  | 2   | CBL ASM CXL FSMB/FSMB 205MM GY | 28480       | 03586 61678        |

| W4         | 35665 61601            | 7  | 1   | CBL ASM CDIN/FHSG 80MM MULT    | 28480       | 35665 61601        |

| W5         | 8120 6243              | 9  | 1   | CBL POWER 60POS RIBBON 75MM LG | 28480       | 8120 6243          |

|            |                        |    |     |                                |             |                    |

| W6         | 8120 6236              | 0  | 2   | CBL KEYBOARD 16POS RIBBON      | 28480       | 8120 6236          |

| W7         | 8120 6242              | 8  | 1   | CBL REAR PANEL 60POS RIBBON    | 28480       | 8120 6242          |

| W8         | 8120 6241              | 7  | 1   | CBL DISC DRIVE 34POS RIBBON    | 28480       | 8120 6241          |

| W9         | 8120 6240              | 6  | 1   | CBL DISPLAY 20POS RIBBON       | 28480       | 8120 6240          |

| W10        | 03586 61677            | 4  | 2   | CBL ASM CXL FSMB/FSMB 265MM BL | 28480       | 03586 61677        |

|            |                        |    |     |                                |             |                    |

| W11        | 35670 61620            | 7  | 1   | CBL FRT PNL ADAPTER 4 CON LEMO | 28480       | 35670 61620        |

| W12        | 35670 61621            | 8  | 1   | CBL ADAPTER PLUG 4 COND W/LEMO | 28480       | 35670 61621        |

|            |                        |    |     |                                |             |                    |

# Instrument Covers and Handles

| Ref<br>Des | Agilent Part<br>Number | CD | Qty | Description                   | Mfr<br>Code | Mfr Part<br>Number |

|------------|------------------------|----|-----|-------------------------------|-------------|--------------------|

|            |                        |    |     |                               |             |                    |

| MP1        | 35670 64101            | 5  | 1   | SHTF ASSY COVER ALV           | 28480       | 35670 64101        |

| MP2        | 5021 5483              | 4  | 2   | COVER LATCHES                 | 28480       | 5021 5483          |

| MP4        | 5062 4806              | 9  | 1   | MOLD BUMPER SET 4PC FF CORNRS | 28480       | 5062 4806          |

| MP10       | 35670 64102            | 6  | 1   | IMPACT COVER 35670A           | 28480       | 35670 64102        |

| MP12       | 1540 0292              | 9  | 1   | PKG CASE ACCESSORY            | 00955       | 1051 B 2           |

|            |                        |    |     |                               |             |                    |

| MP13       | 1530 0272              | 4  | 1   | VIEWING HOOD                  | 28480       | 1530 0272          |

| MP15       | 8160 0689              | 9  | 2   | STMP RFI GASKET.228LNG BECUZN | 30817       | 0097 954 15        |

|            |                        |    |     |                               |             |                    |

# Assembly Covers and Brackets

| Ref<br>Des | Agilent Part<br>Number | CD | Qty | Description                 | Mfr<br>Code | Mfr Part<br>Number |

|------------|------------------------|----|-----|-----------------------------|-------------|--------------------|

|            |                        |    |     |                             |             |                    |

| MP100      | 35670 00605            | 0  | 1   | SHTF SHIELD DISP PWR SUPPLY | 28480       | 35670 00605        |

| MP101      | 35670 01203            | 6  | 1   | SHTF BRKT,PCB RETAINER      | 28480       | 35670 01203        |

| MP102      | 35670 01204            | 7  | 1   | SHTF BRACKET FAN AL         | 28480       | 35670 01204        |

| MP103      | 35670 01205            | 8  | 1   | SHTF DISC BRKT              | 28480       | 35670 01205        |

| MP104      | 35670 04102            | 0  | 1   | SHTF SLOT PLUG              | 28480       | 35670 04102        |

|            |                        |    |     |                             |             |                    |

| MP105      | 35670 44701            | 9  | 2   | GSKT FAN MOUNT W/SLUGS      | 28480       | 35670 44701        |

| MP106      | 4040 2321              | 2  | 1   | DUST COVER DISC DRIVE       | 28480       | 4040 2321          |

|            |                        |    |     |                             |             |                    |

### Front Panel Parts

The reference designator for the screws that fasten the bezel (MP208) to the front frame (MP201) is MP604. The reference designator for the nuts that fasten the A101 Display assembly to the front frame is MP611. The reference designator for the screws that fasten the front frame to the chassis is MP603.

| Ref<br>Des | Agilent Part<br>Number | CD | Qty | Description                               | Mfr<br>Code | Mfr Part<br>Number |

|------------|------------------------|----|-----|-------------------------------------------|-------------|--------------------|

|            |                        |    |     |                                           |             |                    |

| MP200      | 0370 3069              | 2  | 1   | MOLD KNB 1.12DRD RPG .25ID                | 28480       | 0370 3069          |

| MP201      | 35670 22001            | 6  | 1   | CSTG FRT FRAME MACH&PAINTED               | 28480       | 35670 22001        |

| MP203      | 35670 34305            | 8  | 1   | PNL OVRLY DRESS 2CHAN PLCR                | 28480       | 35670 34305        |

| MP204      | 35670 41901            | 5  | 1   | KYPD HARDKEY HINGED                       | 28480       | 35670 41901        |

| MP207      | 35670 43701            | 7  | 1   | MOLD PUSHROD PWR WHT                      | 28480       | 35670 43701        |

|            |                        |    |     |                                           |             |                    |

| MP209      | 1252 4960              | 5  | 2   | CONNECTOR MULTICONTACT                    | 12690       | 05 10108           |

| MP210      | 35670 29301            | 3  | 1   | LNZ FLTR RFI/OPTICAL                      | 28480       | 35670 29301        |

| MP212      | 35670 44703            | 1  | 1   | DISPLAY GASKET                            | 28480       | 35670 44703        |

| MP213      | 35670 44101            | 3  | 1   | MOLD COVER DISC DRIVE PCMT SLS            | 28480       | 35670 44101        |

| MP214      | 8160 0423              | 9  | 3   | RFI ROUND STRIP MNL/SIL RBR<br>.125 IN OD | 57003       | 01 0501 1891       |

|            |                        |    |     |                                           |             |                    |

| MP215      | 8160 0467              | 1  | 1   | RFI STRIP FINGERS BE CU BRIGHT DIP        | 30817       | 97 555 A X         |

| MP216      | 0515 0482              | 5  | 1   | SCREW SKT HD CAP M3 X 0.5 8MM LG          | 28480       | 0515 0482          |

| MP223      | 35670 34302            | 5  | 1   | PNL OVRLY DRESS 4CHAN PLCR                | 28480       | 35670 34302        |

|            |                        |    |     |                                           |             |                    |

#### Rear Panel Parts

The reference designator for the screws that fasten the KEYBOARD connector and A10 Rear Panel assembly to the rear panel is MP601. The reference designator for the screws that fasten the rear panel to the chassis is MP603.

Caution

The POWER SELECT switch must be in the DC position (out position) when the key cap (MP315) is removed. If the switch is not in the DC position when the key cap is removed, the switch may be damaged.

| Ref<br>Des | Agilent Part<br>Number | CD | Qty | Description                      | Mfr<br>Code | Mfr Part<br>Number |

|------------|------------------------|----|-----|----------------------------------|-------------|--------------------|

|            |                        |    |     |                                  |             |                    |

| MP300      | 35670 00201            | 2  | 1   | SHTF REAR PANEL W/SILKSCREEN     | 28480       | 35670 00201        |

| MP305      | 2190 0913              | 9  | 6   | WASHER LK HLCL NO. 4 .115 IN ID  | 28480       | 2190 0913          |

| MP306      | 2190 0586              | 2  | 2   | WASHER LK HLCL 4.0 MM 4.1 MM ID  | 28480       | 2190 0586          |

| MP309      | 0380 0643              | 3  | 2   | STANDOFF HEX .255 IN LG 6 32 THD | 28480       | 0380 0643          |

| MP310      | 0380 1832              | 4  | 4   | STDF HXMF MIXED 4.8MMLG STLZN    | 00779       | 747404 3           |

|            |                        |    |     |                                  |             |                    |

| MP312      | 1510 0038              | 8  | 1   | BINDING POST ASSY SGL THD STUD   | 28480       | 1510 0038          |

| MP314      | 2950 0072              | 3  | 1   | NUT HEX DBL CHAM 1/4 32 THD      | 28480       | 2950 0072          |

|            |                        |    |     | .062 IN THK                      |             |                    |

| MP315      | 5041 0564              | 4  | 1   | KEYCAP                           | 28480       | 5041 0564          |

|            |                        |    |     |                                  |             |                    |

# Chassis Parts

| Ref<br>Des | Agilent Part<br>Number | CD | Qty | Description               | Mfr<br>Code | Mfr Part<br>Number |

|------------|------------------------|----|-----|---------------------------|-------------|--------------------|

|            |                        |    |     |                           |             |                    |

| MP400      | 35670 00101            | 1  | 1   | SHTF CHASSIS ASSY         | 28480       | 35670 00101        |

| MP401      | 35670 00102            | 2  | 1   | SHTF WALL ASSY FRONT      | 28480       | 35670 00102        |

| MP402      | 35670 04103            | 1  | 2   | INPUT BD INSULATOR        | 28480       | 35670 04103        |

| MP403      | 35650 00601            | 2  | 1   | SHTF CVR SHLD MUFL        | 28480       | 35650 00601        |

| MP404      | 35670 64302            | 8  | 1   | LBL CABLE 2CH CBL ROUTINE | 28480       | 35670 64302        |

| MP405      | 35670 64304            | 0  | 2   | LBL CABLE 4CH CBL ROUTINE | 28480       | 35670 64304        |

# Screws, Washers, and Nuts

| Ref<br>Des | Agilent Part<br>Number | CD | Qty | Description                                | Mfr<br>Code | Mfr Part<br>Number |

|------------|------------------------|----|-----|--------------------------------------------|-------------|--------------------|

|            |                        |    |     |                                            |             |                    |

| MP600      | 0515 0374              | 4  | 16  | SCREW MACHINE ASSEMPLY M3 X 0.5<br>10MM LG | 28480       | 0515 0374          |

| MP601      | 0515 0430              | 3  | 66  | SCREW MACHINE ASSEMPLY M3 X 0.5<br>6MM LG  | 28480       | 0515 0430          |

| MP602      | 0515 1940              | 2  | 4   | SCR MCH M2.5 6MMLG PHTX SST *              | 28480       | 0515 1940          |

| MP603      | 0515 2043              | 8  | 21  | SCR MCH M4.0 8MMLG FHTX SST *              | 28480       | 0515 2043          |

| MP604      | 0515 1622              | 7  | 4   | SCR CAP M4.0 8MMLG SKHX SSTBL              | 28480       | 0515 1622          |

|            |                        |    |     |                                            |             |                    |

| MP607      | 2190 0099              | 2  | 3   | WASHER LK INTL T 7/16 IN .472 IN ID        | 28480       | 2190 0099          |

| MP608      | 2950 0035              | 8  | 3   | NUT HEX DBL CHAM 15/32 32 THD              | 28480       | 2950 0035          |

| MP611      | 0535 0031              | 2  | 4   | NUT HEX W/LKWR M3 X 0.5 2.4MM THK          | 28480       | 0535 0031          |

| MP613      | 2190 0060              | 7  | 1   | WASHER LK INTL T 1/4 IN .256 IN ID         | 28480       | 2190 0060          |

| MP619      | 1252 0699              | 9  | 2   | SCR JCK 4 40 .25LG THRD STLZN              | 05791       | ST 9411 36         |

# Miscellaneous Parts

| Ref<br>Des | Agilent Part<br>Number | CD | Qty | Description                         | Mfr<br>Code | Mfr Part<br>Number |

|------------|------------------------|----|-----|-------------------------------------|-------------|--------------------|

|            |                        |    |     |                                     |             |                    |

| MP702      | 1400 1122              | 0  | 1   | CLAMP CABLE .187 DIA .735 WD NYL    | 34785       | 021 0188           |

| MP703      | 1400 1229              | 8  | 1   | CLAMP CABLE .375 DIA 1 WD NYL       | 34785       | 021 0375           |

| MP704      | 0403 0285              | 9  | 4   | BUMPER FOOT ADH MTG 12.7 MM WD      | 76381       | SJ 5018 GRAY       |

| MP705      | 1400 0249              | 0  | 1   | CABLE TIE .062 .625 DIA .091 WD NYL | 56501       | TY 23M 8           |

| MP707      | 0403 0179              | 0  | 18  | BUMPER FOOT ADH MTG                 | 76381       | SJ 5012            |

|            |                        |    |     |                                     |             | BLACK              |

|            |                        |    |     |                                     |             |                    |

| A8B200     | 1420 0336              | 8  | 1   | BATTERY                             | 55002       | T06/46             |

| A10F20     | 2110 0665              | 0  | 1   | FUSE 1A 125V NTD .28X.096           | 75915       | R251001T1          |

| 0          |                        |    |     |                                     |             |                    |

| A98 F1     | 2110 0342              | 0  | 1   | FUSE 8A 250V NTD 1.25X.25 UL        | 71400       | ABC 8              |

| A98 F2     | 2110 0920              | 0  | 1   | FUSE 30A 32VDC NORMAL BLOW 3AG      | 75915       | 311 030            |

|            |                        |    |     |                                     |             |                    |

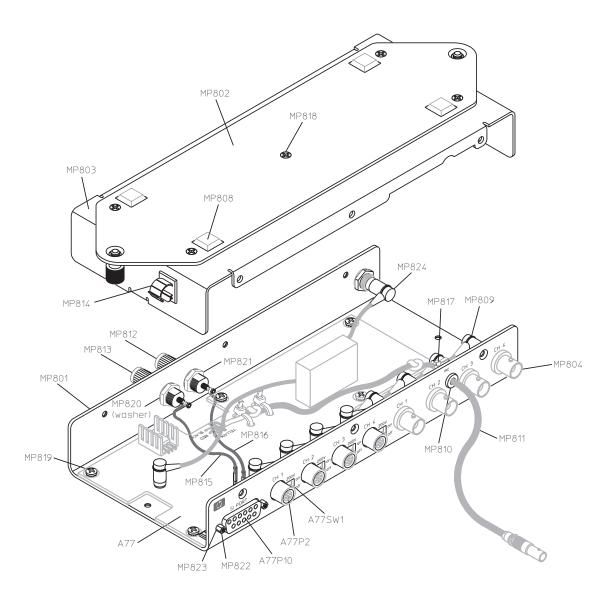

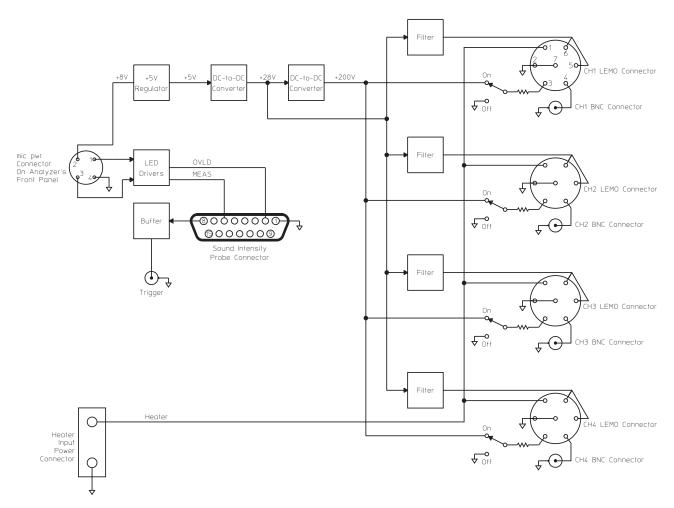

# Option UK4 Parts

| Ref<br>Des | Agilent Part<br>Number | CD | Qty                                    | Description                               | Mfr<br>Code | Mfr Part Number    |

|------------|------------------------|----|----------------------------------------|-------------------------------------------|-------------|--------------------|

| A 77       | 25(70)((577            | ,  | 1                                      | MICHODIONE DO ACCEMBIA                    | 29490       | 25(70) ((577       |

| A77        | 35670 66577            | 3  | $\begin{bmatrix} 1 \\ 4 \end{bmatrix}$ | MICROPHONE PC ASSEMBLY                    | 28480       | 35670 66577        |

| A77P2      | 1252 5280              | 4  | 4                                      | CONN LEMO 7 CNT FEMALE RT PC              | 00268       | EPG.1B.307.HL<br>N |

| A77P10     | 1252 1481              | 9  | 1                                      | CON RECT D SUB 15CKT 15PN THL             | 00779       | 748876 1           |

| A77SW<br>1 | 3101 3124              | 4  | 4                                      | SW SL .02A 20VA1D                         | 09353       | 1101 M2S4AV2<br>BE |

| MP801      | 35670 00121            | 5  | 1                                      | SHTF BTTM OUTBOX W/SILKSCREEN             | 28480       | 35670 00121        |

| MP802      | 35670 01206            | 9  | 1                                      | SHTF BRKT MNTG OUTBOX                     | 28480       | 35670 01206        |

| MP803      | 35670 00120            | 4  | 1                                      | SHTF LID OUTBOX PAINTED                   | 28480       | 35670 00120        |

| MP804      | 1250 1558              | 7  | 5                                      | ADAPTER COAX STR F BNC<br>F RCA PHONO     | 24931       | 29ЈЈ126 3          |

| M0808      | 0403 0285              | 9  | 4                                      | BUMPER FOOT ADH MTG 12.7 MM WD            | 76381       | SJ 5018 GRAY       |

| MP809      | 8120 4891              | 9  | 4                                      | CBL RCA 153MM BK                          | 28480       | 8120 4891          |

| MP810      | 0400 0009              | 9  | 1                                      | GROMMET RND .125 IN ID .25 IN GRV OD      | 28480       | 0400 0009          |

| MP811      | 35670 61621            | 8  | 1                                      | CBL ADAPTER PLUG 4 COND W/LEMO            | 28480       | 35670 61621        |

| MP812      | 1510 0091              | 3  | 1                                      | BINDING POST SGL SGL TUR JGK RED          | 28480       | 1510 0091          |

| MP813      | 1510 0107              | 2  | 1                                      | BINDING POST SGL SGL TUR JGK CBK          | 28480       | 1510 0107          |

| MP814      | 1400 1122              | 0  | 1                                      | CLAMP CABLE .187 DIA .735 WD NYL          | 34785       | 021 0188           |

| MP815      | 8120 3828              | 0  | 1                                      | LJPR 22GA BLK 100MM Dx8                   | 28480       | 8120 3828          |

| MP816      | 8120 3860              | 0  | 1                                      | LJPR 22GA RED 100MM Dx8                   | 28480       | 8120 3860          |

| MP817      | 1400 0249              | 0  | 3                                      | CABLE TIE .062 .625 DIA .091 WD NYL       | 56501       | TY 23M 8           |

| MP818      | 0515 1946              | 8  | 13                                     | SCR MCH M3.0 6MMLG FHTX SST               | 28480       | 0515 1946          |

| MP819      | 0515 0430              | 3  | 7                                      | SCR MCH ASSEMPLY M3 X 0.5 6MM LG          | 28480       | 0515 0430          |

| MP820      | 2190 0016              | 3  | 2                                      | WASHER LK INTL T 3/8 IN .377 IN ID        | 28480       | 2190 0016          |

| MP821      | 2950 0001              | 8  | 2                                      | NUT HEX DBL CHAM 3/8 32 THD .094 IN THK   | 73734       | 9002 NP            |

| MP822      | 1252 0699              | 9  | 2                                      | SCR JCK 4 40 .25LG THRD STLZN             | 05791       | ST 9411 36         |

| MP823      | 2190 0583              | 9  | $\begin{bmatrix} 2 \\ 2 \end{bmatrix}$ | WASHER LK HLCL 2.5 MM 2.6 MM ID           | 28480       | 2190 0583          |

| MP824      | 8120 2587              | 6  | 1                                      | CABLE ASSY COAX 50 OHM 1.5KV<br>8.5 IN LG | 28480       | 8120 2587          |

|            | 35670 90014            | 4  | 1                                      | MICROPHONE & POWER OP NOTE                | 28480       | 35670 90051        |

|            | 8120 1839              | 9  | 1                                      | CABLE ASSY COAX 50 OHM 24 IN LG<br>JGK    | 28480       | 8120 1839          |

|            | 8120 6237              | 1  | 4                                      | CBL ASM CXL BNC                           | 28480       | 8120 6237          |

8

Circuit Descriptions

### Circuit Descriptions

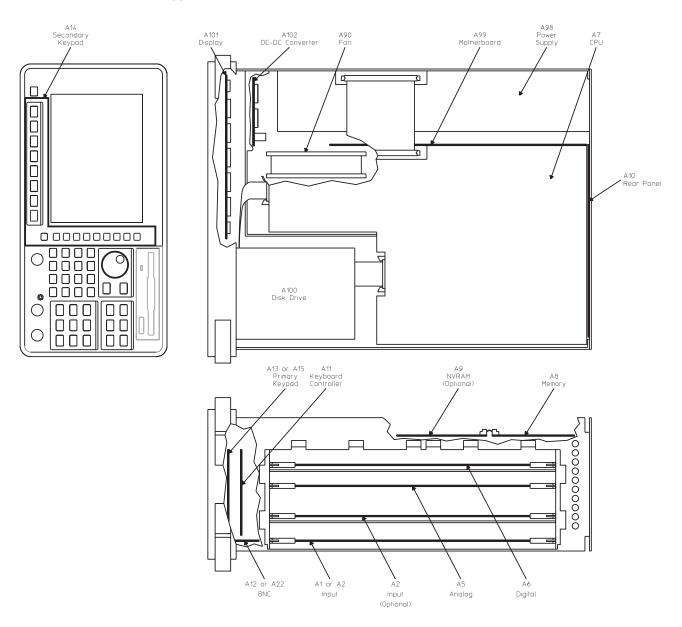

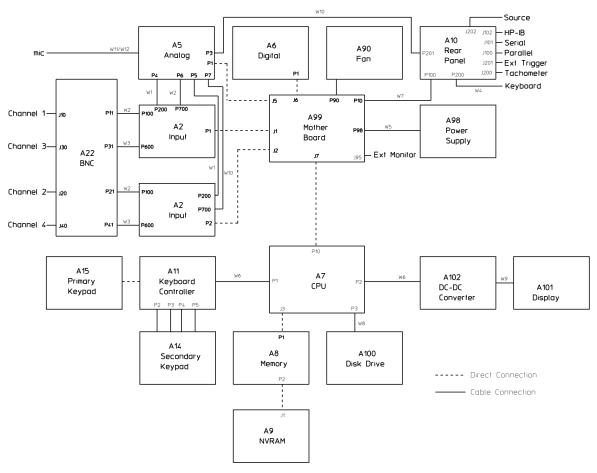

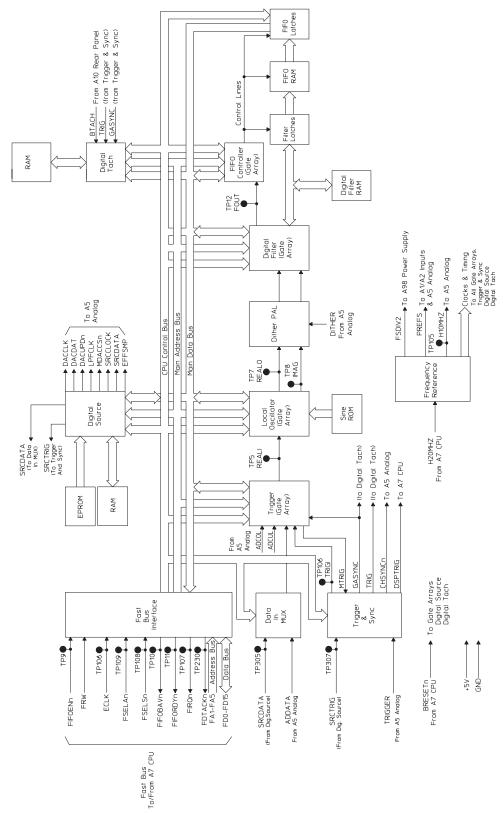

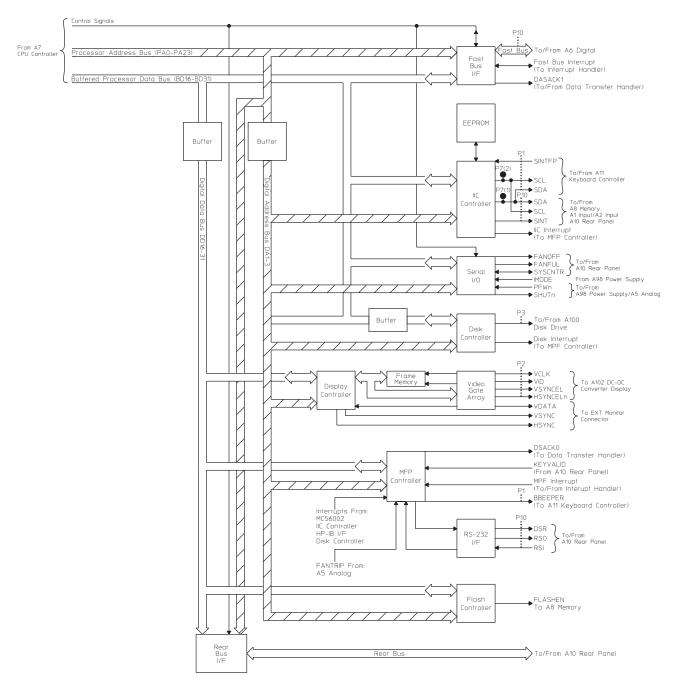

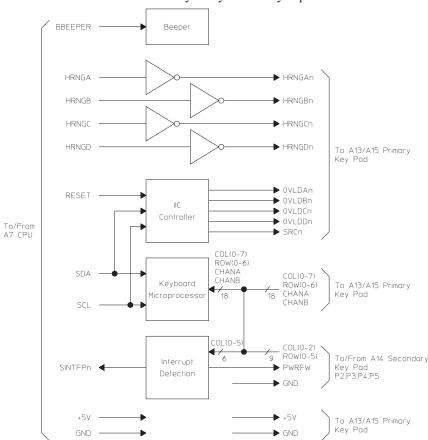

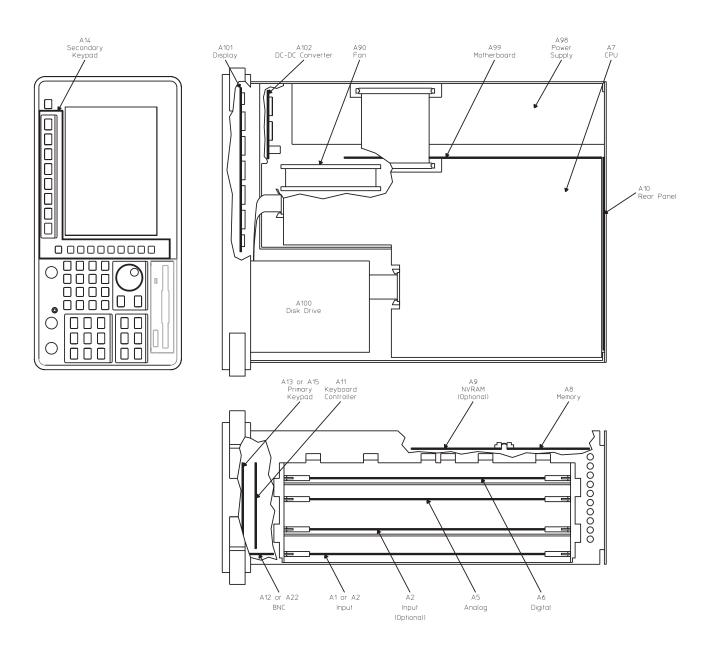

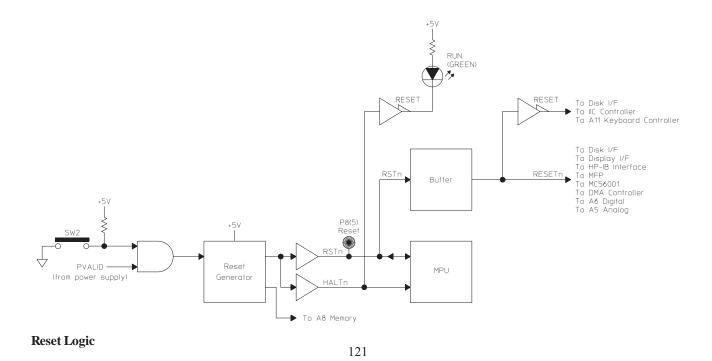

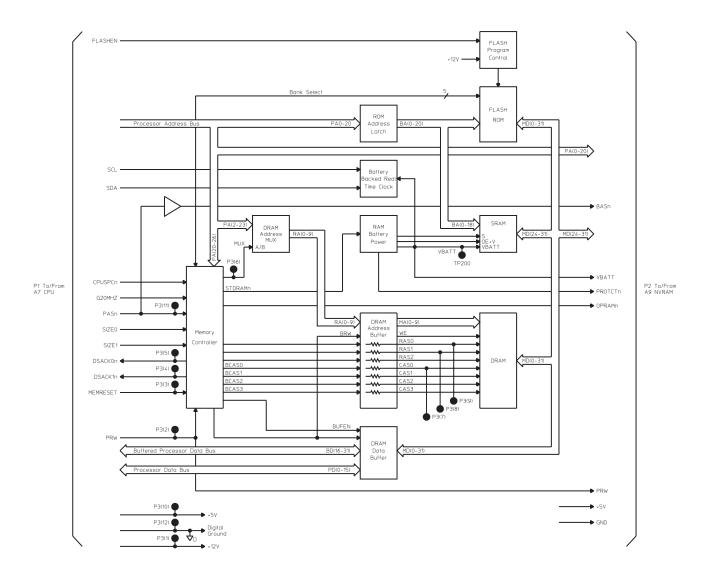

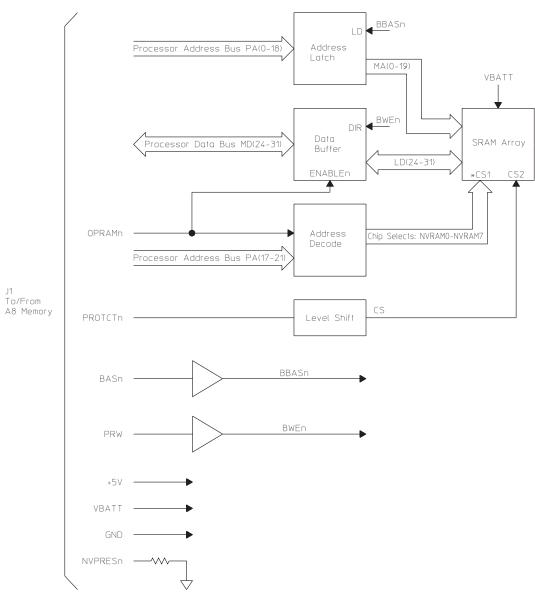

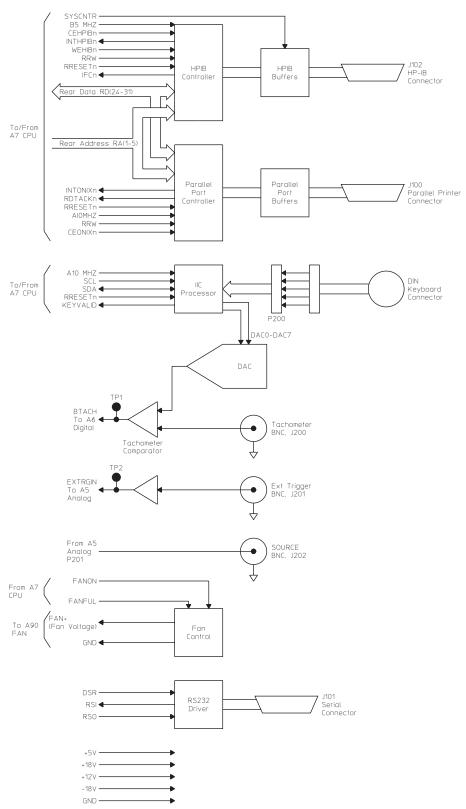

This chapter contains the overall instrument description and individual assembly descriptions for the Agilent 35670A Dynamic Signal Analyzer. The overall instrument description lists the assemblies in the analyzer and describes the analyzer's overall block diagrams. The assembly descriptions give additional information for each assembly. For signal connections and descriptions, see chapter 9, "Voltages and Signals."

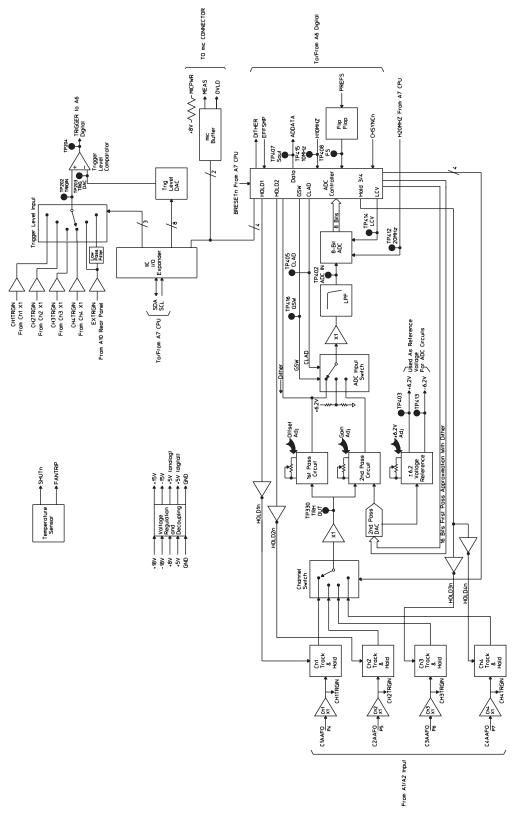

### Overall Instrument Description

The Agilent 35670A Dynamic Signal Analyzer is an FFT spectrum/network analyzer with a frequency range that extends from 0.19531 Hz to 102.4 kHz in single channel mode and from 0.097656 Hz to 51.2 kHz in two channel mode. The optional four channel analyzer has a frequency range that extends from 0.097656 Hz to 51.2 kHz in two channel mode and from 0.048828 Hz to 25.6 kHz in four channel mode. The analyzer has a built-in signal source providing random noise, burst random noise, periodic chirp, burst chirp, pink noise, and fixed sine. Measurements can be saved to an internal 3.5-inch flexible disk drive, an external HP SS-80 disk drive, or to internal non-volatile memory. Plots and prints of the measurements can be made directly to printers and plotters with GPIB, parallel, or serial interfaces. The analyzer also supports the Instrument Basic programming language (IBASIC).

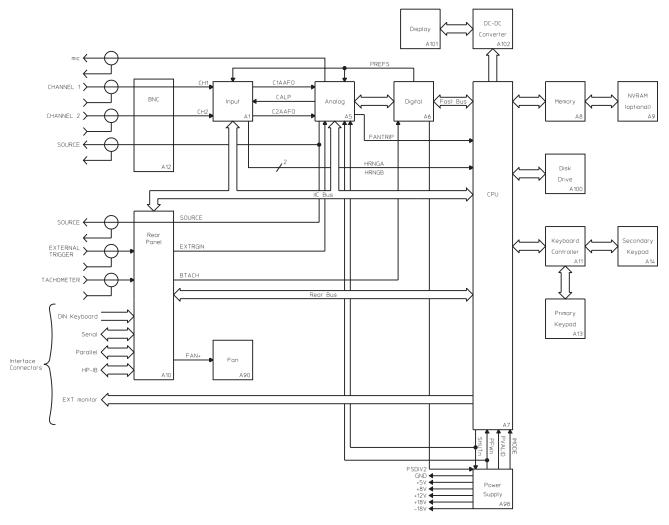

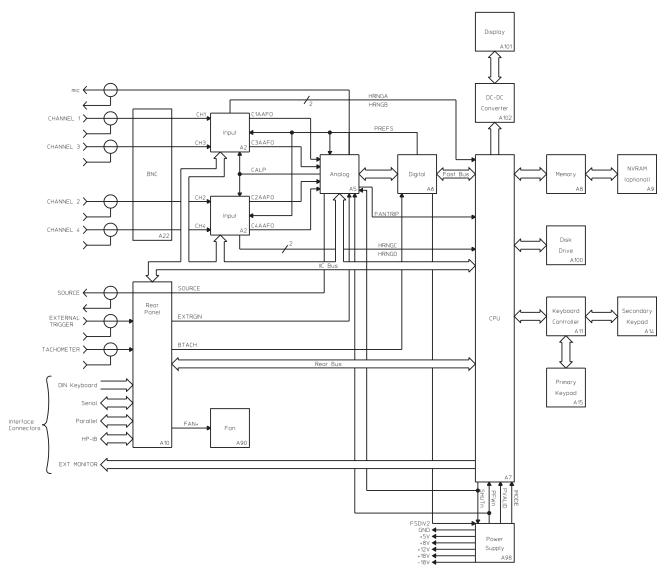

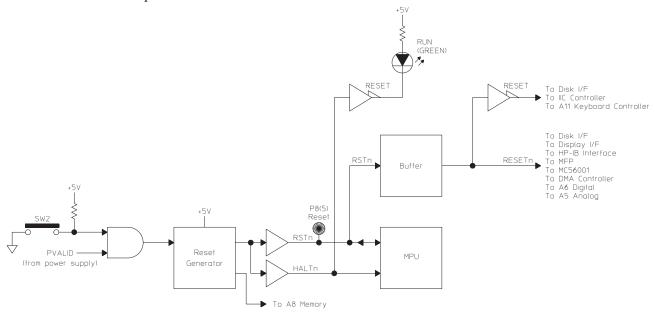

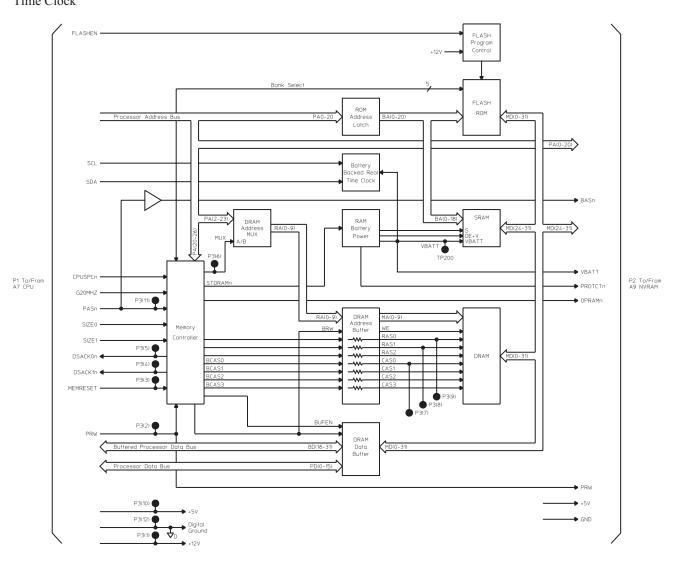

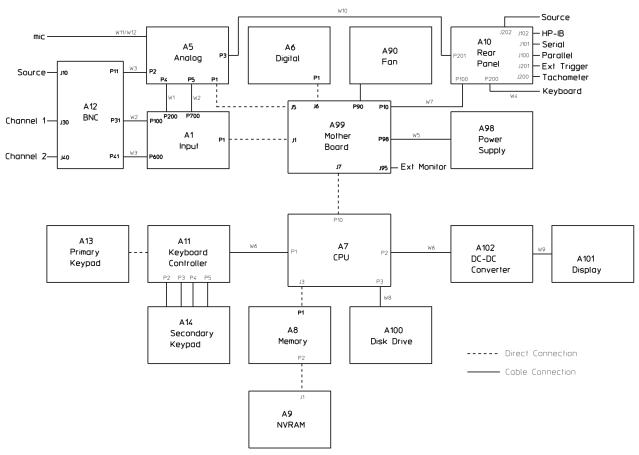

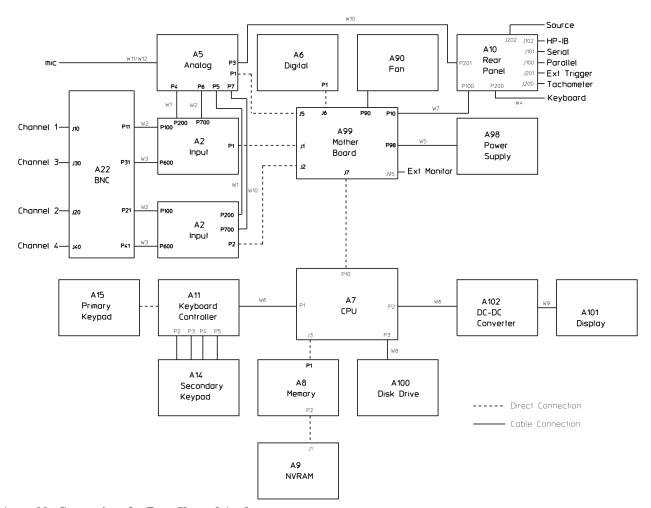

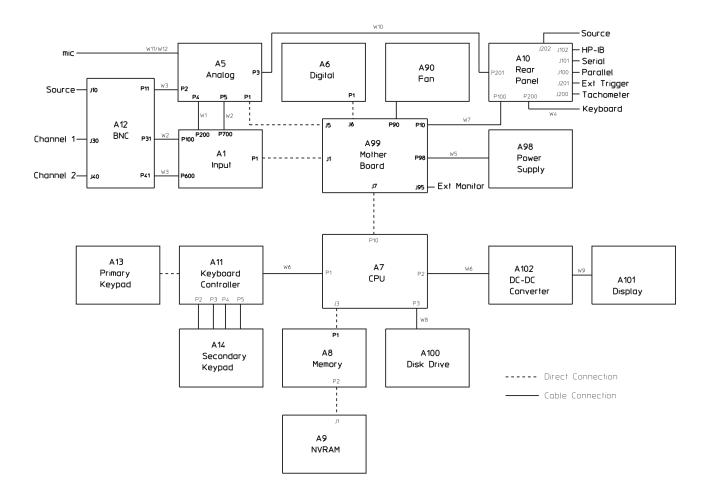

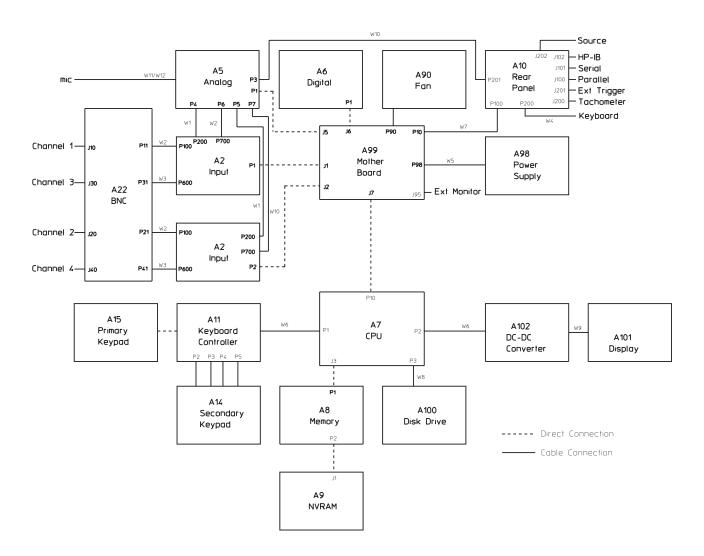

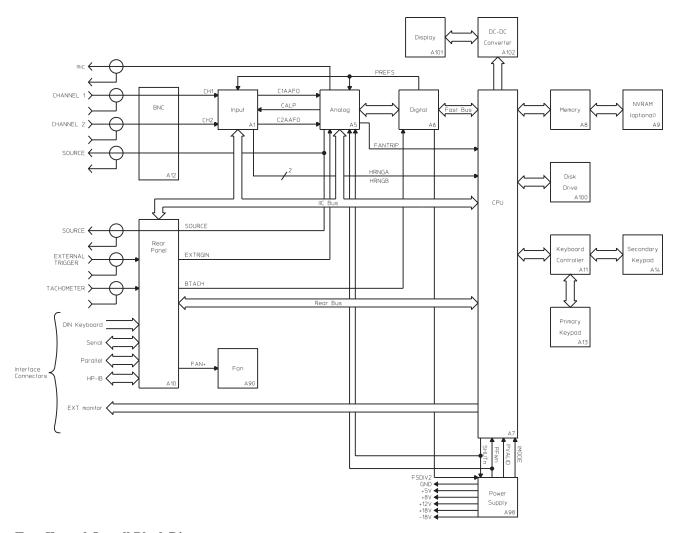

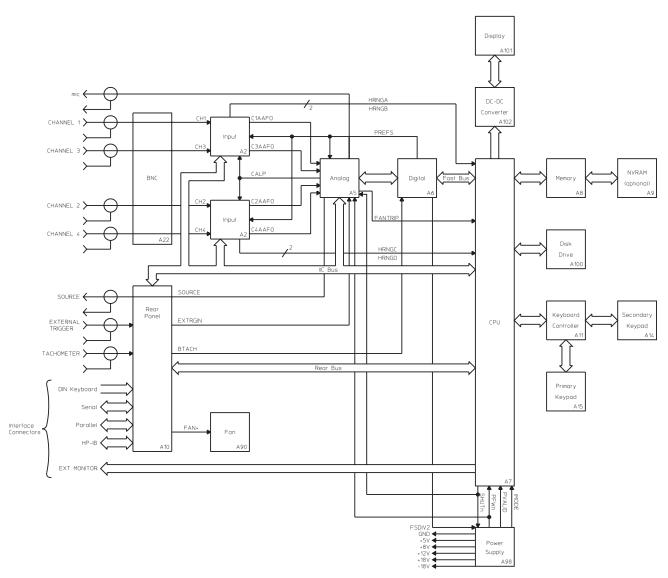

#### **Overall Block Diagram**

The following figures show the overall block diagrams for both the two channel and the four channel analyzer. Each block in the diagrams represents a functional block in

the analyzer. The assembly that performs the function is listed in the block.

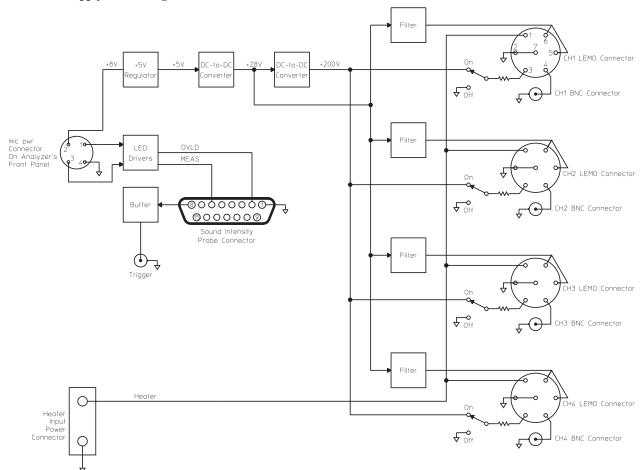

Contains the BNC connectors for both input channels and the source. For the four channel analyzer, the BNC assembly contains the BNC connectors for all four input channels. Both BNC assemblies filter the input channels HIGH (BNC center conductor) and LOW (BNC shell)

input signals to reduce noise at the inputs.

Buffers, attenuates, amplifies, and filters the input signals. The input assembly also provides

common mode and differential overload detection, and half-range detection. The two channel analyzer contains one A1 Input assembly and the four channel analyzer contains two A2 Input

assemblies.

Analog Converts the input signals from the Input assembly (or assemblies) to digital data. The Analog

assembly also converts the digital data from the Digital assembly's digital source to the analog source signal. For the two channel analyzer, the analog source signal is routed to the Rear Panel assembly and to the BNC assembly. For the four channel analyzer, the analog source

signal is routed only to the Rear Panel assembly.

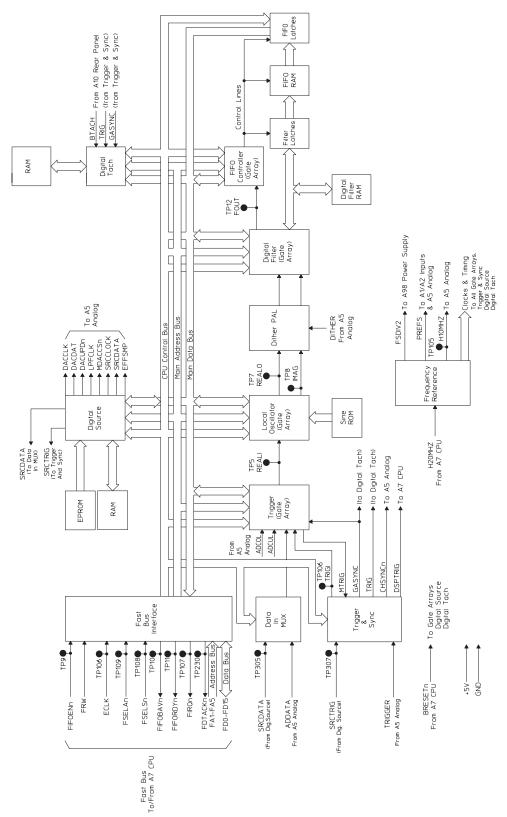

Prepares the digital data from the Analog assembly for the CPU assembly. This assembly also

generates the digital source data for the Analog assembly.

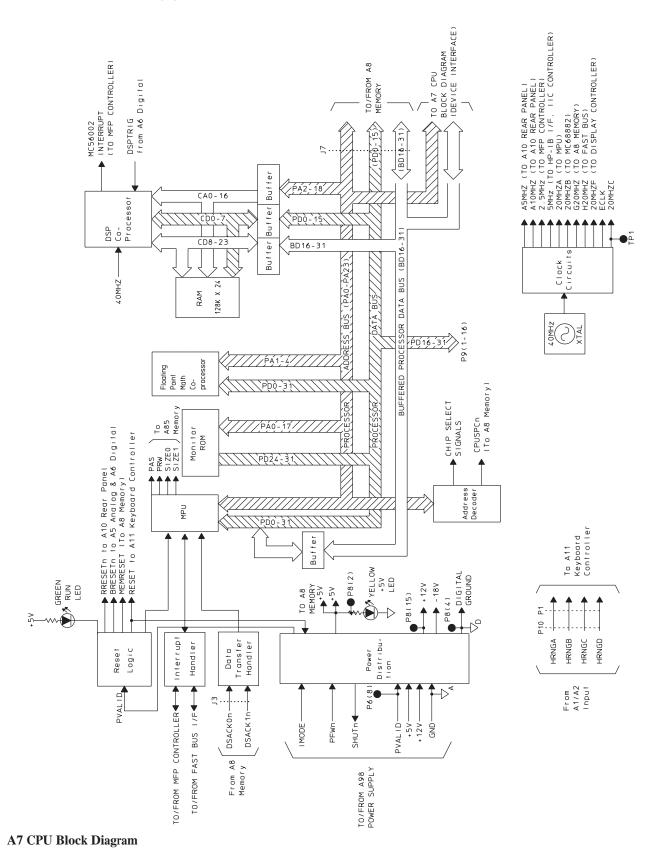

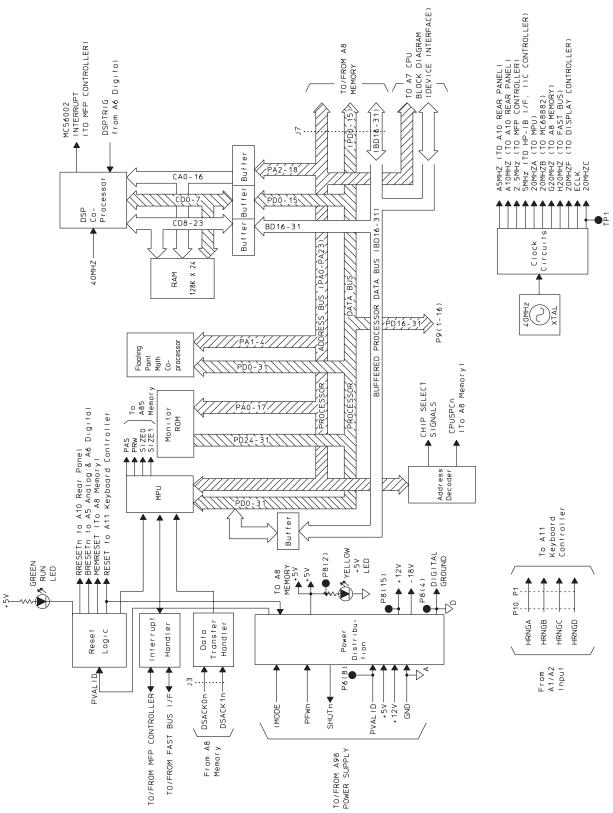

CPU Controls the analyzer. The following is a partial list of the operations it performs:

• Configures the assemblies

• Controls the Disk Drive assembly

• Controls the Display assembly

• Initiates the power-up sequence and calibration routine

Processes digital data from the Digital assembly

• Computes the Fast Fourier Transform (FFT)

• Monitors for a keystroke

Monitors the assemblies for overloads or other error conditions

• Runs the self tests

DC-DC Converter Generates the driver supply voltages for the Display assembly.

Display Offers a view of the processed data. See the description of the Display Controller for the "A7

CPU" later in this chapter for further details.

Memory Contains RAM, NVRAM, ROM, and the battery-backed real time clock for the CPU assembly.

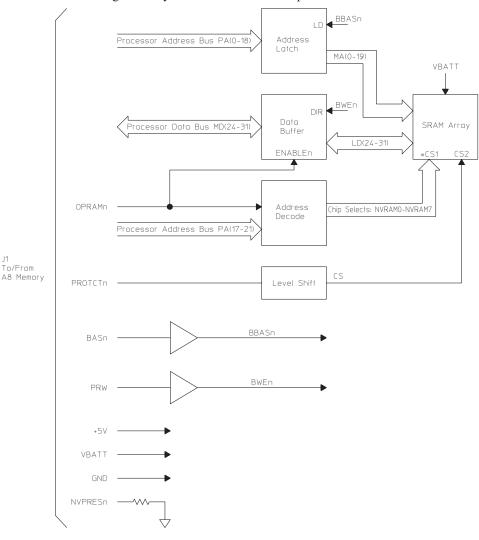

Provides the CPU assembly with additional NVRAM. This assembly is optional. **NVRAM**

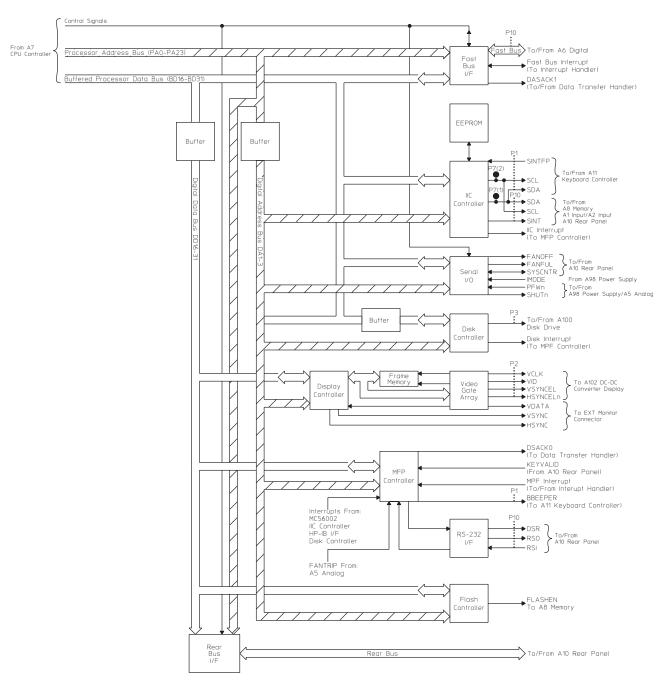

Disk Drive Stores and retrieves information on 3.5-inch flexible disks.

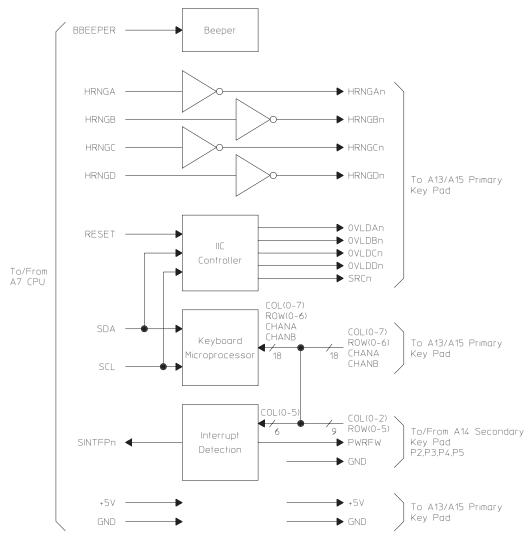

Keyboard Controller Tells the CPU assembly which key was pressed.

Primary Keypad Consists of hardkeys and an RPG.

8-3

**BNC**

Input

Digital

Circuit Descriptions

Overall Instrument Description

Secondary Keypad Consists of hardkeys and softkeys.

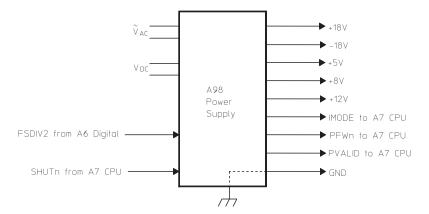

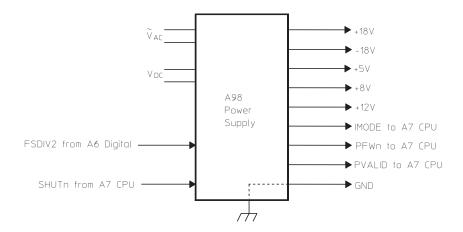

Power Supply Supplies the dc voltages shown in the block diagram. See "Power Supply Voltage

Distribution" in chapter 9 for additional information.

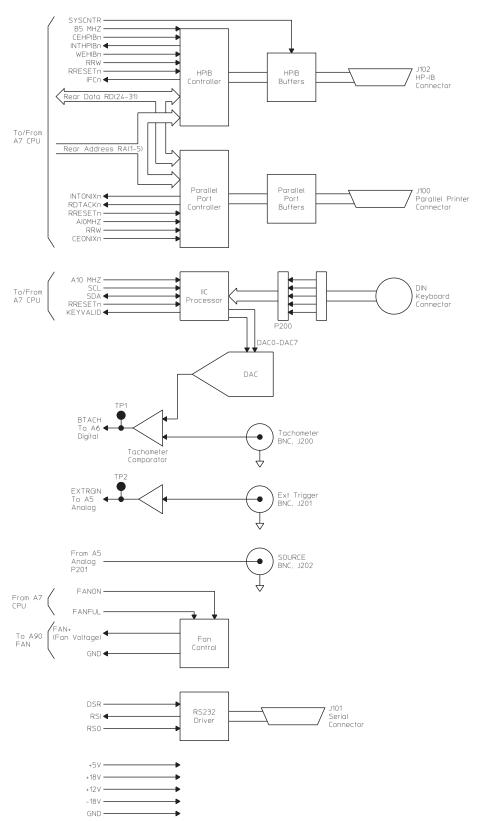

Rear Panel Provides the interface for devices connected to its GPIB connector, parallel connector, serial

connector, and DIN keyboard connector. The Rear Panel assembly also provides the fan control, external trigger connector, source connector, and tachometer connector and counter.

Two Channel Overall Block Diagram

Four Channel Overall Block Diagram

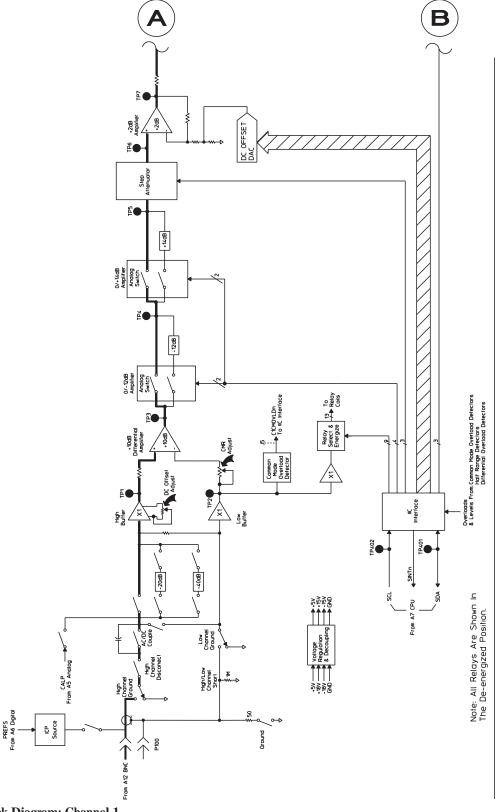

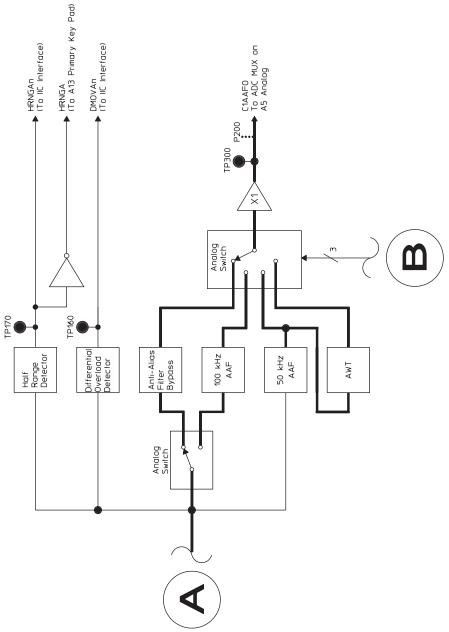

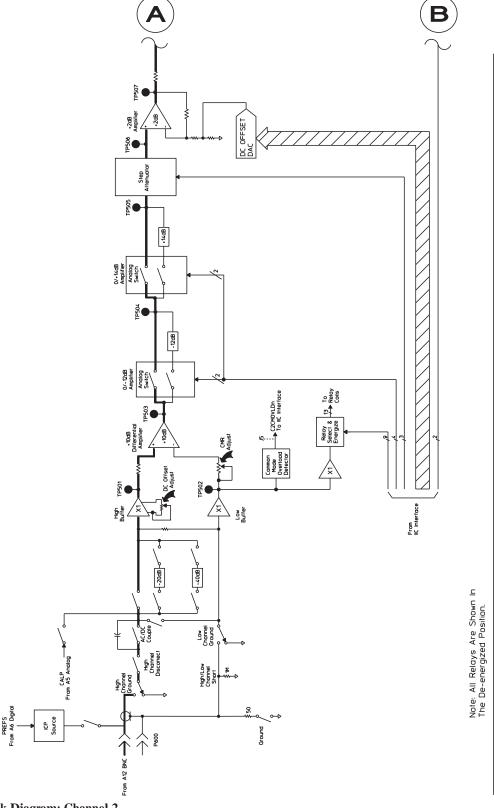

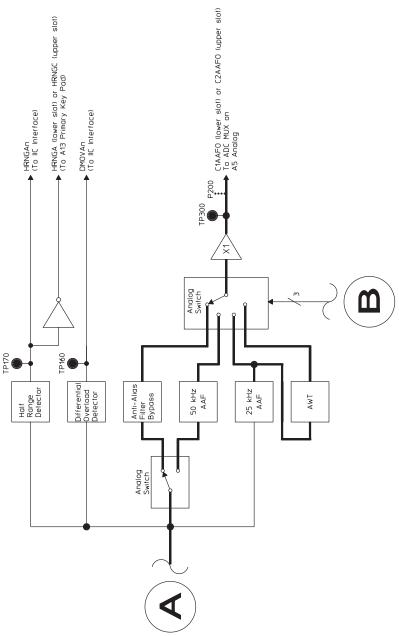

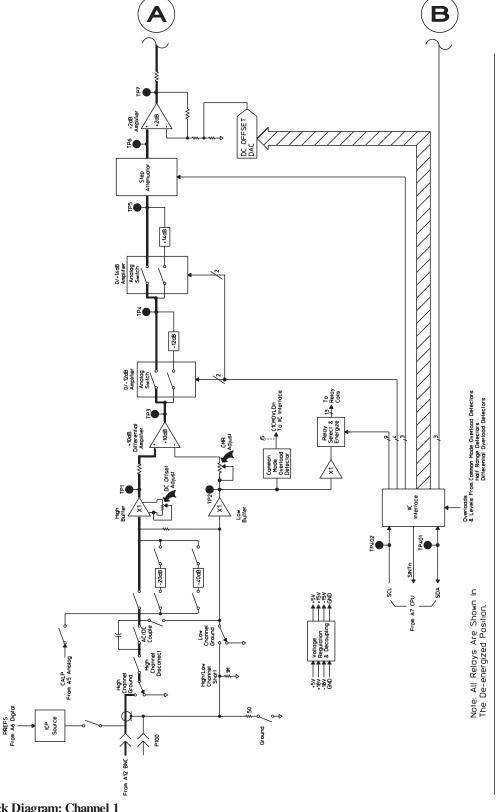

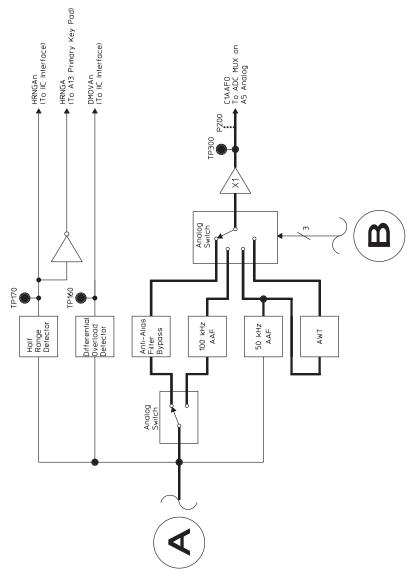

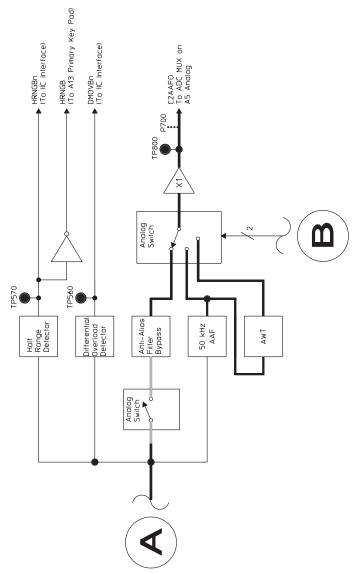

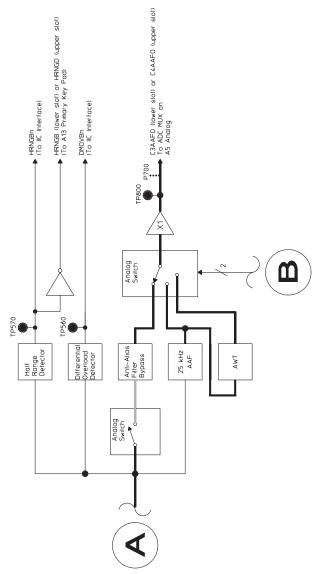

### A1 Input

The A1 Input assembly is the input assembly for the two channel analyzer. The A1 Input assembly conditions the channel 1 and channel 2 input signals before they are sent to the analog-to-digital converter on the A5 Analog assembly. The A1 Input assembly sets the voltage ranges, conditions the input signals, and filters out alias components. Signal conditioning is done with relays, high and low buffers, and a series of amplifiers and attenuators. In addition, autozero DACs compensate for any dc offset added to the signals by the circuits on this assembly. This assembly also monitors the input signals for common mode or differential overloads and for half-range conditions. Unless stated otherwise, the following description applies to the block diagrams for both channel 1 and channel 2.

**ICP Source**

Supplies power to transducers such as accelerometers when enabled. The ICP Source is a 4.25 (1.5 mA floating current source. The power for the current source is obtained by switching the (15 V supplies at the sample frequency (262 kHz), isolating through a 1:1 transformer, rectifying and filtering. When disabled, the source is disconnected by a relay and the switching power supply is disabled.

Input Relays

Select one of the 0 dB, 20 dB, or 40 dB pads and configure the input. The relays are controlled by Relay Select & Energize.

Relay Select & Energize

Selects and energizes the input relays. Relay Select & Energize is controlled by the IIC

Interface.

High Buffer

Buffers the HIGH input signal (BNC center conductor). The High Buffer contains a bootstrap circuit that prevents harmonic distortion and large common mode signals from saturating the

buffer

Low Buffer

Buffers the LOW input signal (BNC shell). The operation of the Low Buffer is identical to the High Buffer.

+10 dB Differential Amplifier

Begins the gain and attenuation stages. This amplifier subtracts the HIGH and LOW input signals from the high and low buffers. The common mode rejection adjustment, adjusts the +10 dB Differential Amplifier to reject common mode signals.

0 /-12 dB Amplifier 0 /+14 dB Amplifier

Can attenuate the signal by 12 dB. Can amplify the signal by 14 dB.

Step Attenuator

Can attenuate the input signal from 0 dB to -14 dB, in 2 dB steps.

+2 dB Amplifier

Adds a gain of 2 dB and allows the DC Offset DAC to vary the dc offset of the input signal. The purpose of the amplifiers and attenuators up to this point is to ensure that the input signal does not overdrive the anti-alias filter or analog-to-digital converter.

Agilent 35670A Circuit Descriptions

A1 Input

DC Offset DAC Compensates for any dc offset added to the input signal due to circuitry in the signal path. The

required dc offset is calculated during the analyzer's calibration routine and is added to the input signal in 0.345~mV increments by varying the dc offset at the inverting input of the +2~dB

Amplifier (see "Calibration Routine Description" in chapter 10).

Anti-Alias Filter Bypass Bypasses all filters.

100 kHz Anti-Alias Prilter in

Provides alias protection up to 100 kHz for single channel measurements. Only the channel 1 input path has a 100 kHz Anti-Alias Filter.

50 kHz Anti-Alias Filter Provides alias protection up to 50 kHz for two channel measurements.

A-Weight Filter Provides additional filtering in the 50 kHz anti-alias filter path for acoustic measurements.

Analog Switch Selects one of four possible signals in the channel 1 input path to send to the ADC — the signal from the Anti-Alias Filter Bypass, 100 kHz Anti-Alias Filter, 50 kHz Anti-Alias Filter, or

A-Weight Filter. In the channel 2 input path, the Analog Switch selects one of three possible signals to send to the ADC — the signal from the Anti-Alias Filter Bypass, 50 kHz Anti-Alias

Filter, or A-Weight Filter.

Half Range and Differential Overload Detectors Sense the signal at the anti-alias filters. When a detector detects a half-range or overload condition, a digital low is sent to the IIC Interface by the detector. The half-range detector also sends a control signal to the A13 Primary Keypad assembly when a half-range condition

occurs.

IIC (Inter-IC) Interface Contains 32 ports and connects the A1 Input assembly to the serial IIC bus. The A7 CPU

assembly uses the IIC bus to configure the input circuits. When a common mode or differential overload occurs, the IIC Interface forces SINTn low to interrupt the CPU assembly. The CPU assembly then reads the IIC Interface to determine the type of interrupt and the channel it occurred on. During up/down autoranging, the A7 CPU queries the A1 Input assembly for half range status. For a description of the IIC bus, see the description of the IIC Controller for the

"A7 CPU" later in this chapter.

A1 Input Block Diagram: Channel 1

A1 Input Block Diagram: Channel 1 (continued)

A1 Input Block Diagram: Channel 2

A1 Input Block Diagram: Channel 2 (continued)

A1 Input

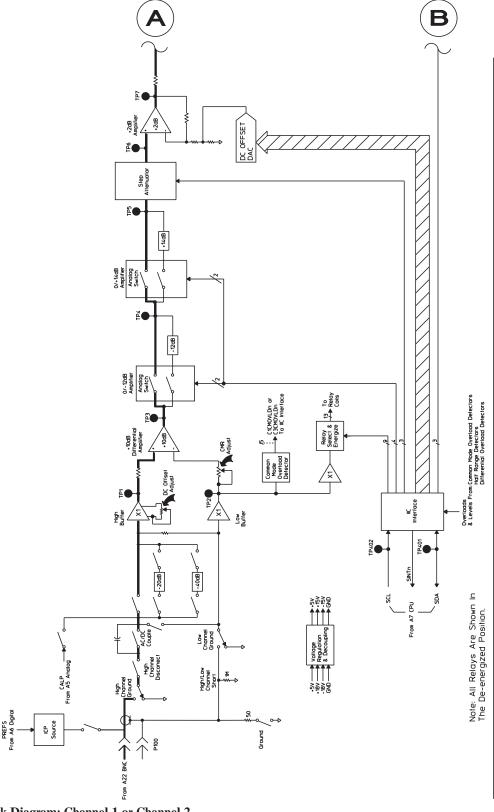

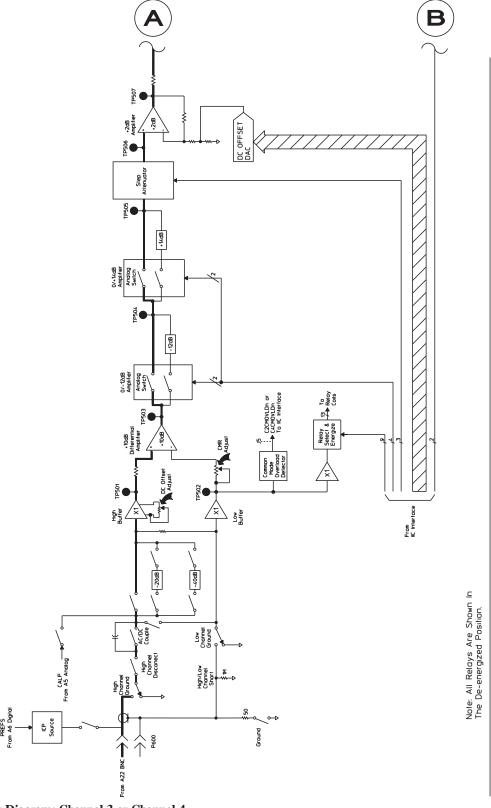

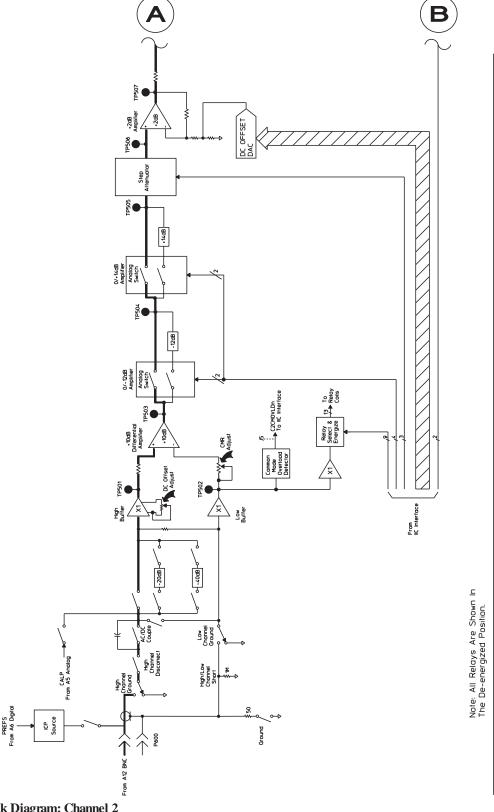

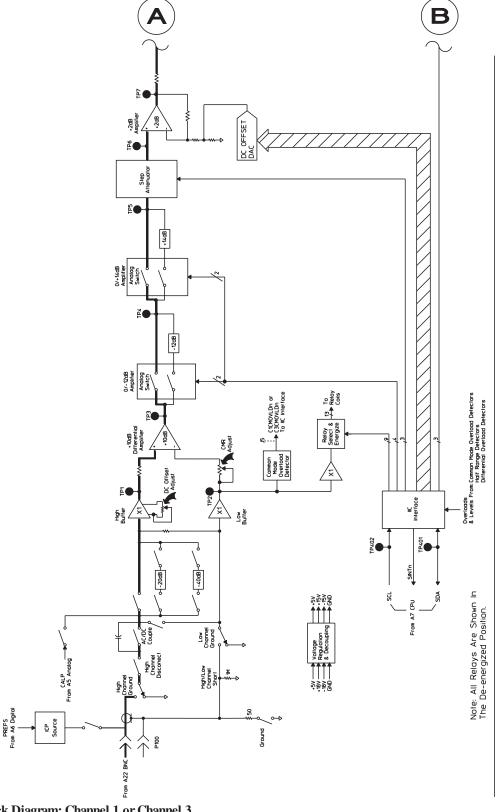

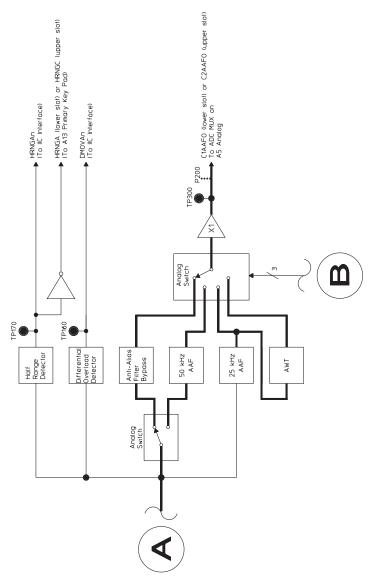

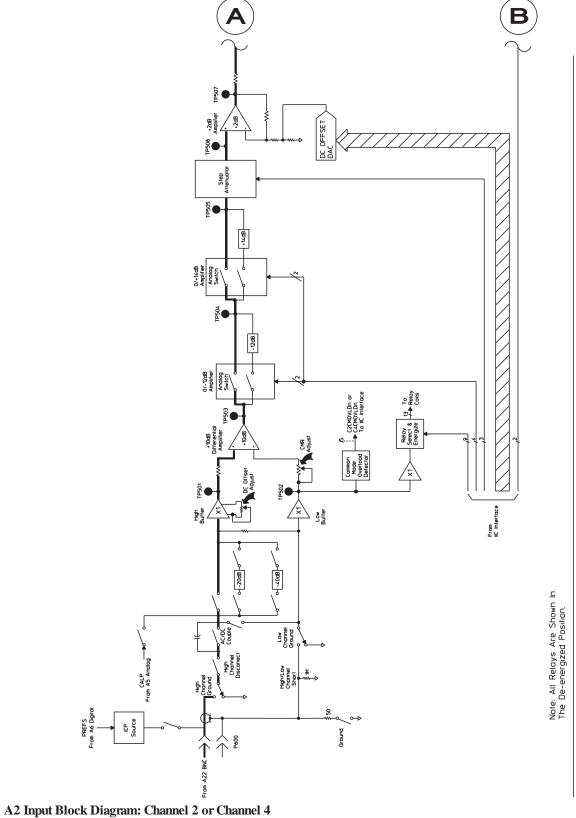

### A2 Input

The A2 Input assembly is the input assembly for the four channel analyzer. The four channel analyzer contains two A2 Input assemblies. The A2 Input assembly connected to J1 on the Motherboard conditions the channel 1 and channel 3 input signals before they are sent to the analog-to-digital converter on the A5 Analog assembly. The A2 Input assembly connected to J2 on the Motherboard conditions the channel 2 and channel 4 input signals before they are sent to the analog-to-digital converter on the A5 Analog assembly. The Input assembly sets the voltage ranges, conditions the input signals, and filters out alias components. Signal conditioning is done with relays, high and low buffers, and a series of amplifiers and attenuators. In addition, autozero DACs compensate for any dc offset added to the signals by the circuits on this assembly. The assembly also monitors the input signals for common mode or differential overloads and for half-range conditions. Unless stated otherwise, the following description applies to the block diagrams for all four channels.

ICP Source

Supplies power to transducers such as accelerometers when enabled. The ICP Source is a 4.25 (1.5 mA floating current source. The power for the current source is obtained by switching the (15 V supplies at the sample frequency (262 kHz), isolating through a 1:1 transformer, rectifying and filtering. When disabled, the source is disconnected by a relay and the switching power supply is disabled.

Input Relays

Select one of the 0 dB, 20 dB, or 40 dB pads and configure the input. The relays are controlled by Relay Select & Energize.

Relay Select & Energize

Selects and energizes the input relays. Relay Select & Energize is controlled by the IIC

Interface.

High Buffer

Buffers the HIGH input signal (BNC center conductor). The High Buffer contains a bootstrap circuit that prevents harmonic distortion and large common mode signals from saturating the buffer.

Low Buffer

Buffers the LOW input signal (BNC shell). The operation of the Low Buffer is identical to the High Buffer.

+10 dB Differential Amplifier

Begins the gain and attenuation stages. This amplifier subtracts the HIGH and LOW input signals from the high and low buffers. The common mode rejection adjustment, adjusts the +10 dB Differential Amplifier to reject common mode signals.

0 /-12 dB Amplifier 0 /+14 dB Amplifier Can attenuate the signal by 12 dB. Can amplify the signal by 14 dB.

Step Attenuator

Can attenuate the input signal from 0 dB to -14 dB, in 2 dB steps.

+2 dB Amplifier

Adds a gain of 2 dB and allows the DC Offset DAC to vary the dc offset of the input signal. The purpose of the amplifiers and attenuators up to this point is to ensure that the input signal does not overdrive the anti-alias filter or analog-to-digital converter.

8-12

Agilent 35670A Circuit Descriptions

A2 Input

DC Offset DAC Compensates for any dc offset added to the input signal due to circuitry in the signal path. The

required dc offset is calculated during the analyzer's calibration routine and is added to the input signal in 0.3.45 mV increments by varying the dc offset at the inverting input of the

+2 dB Amplifier (see "Calibration Routine Description" in chapter 10).

Anti-Alias Filter Bypass Bypasses all filters.

50 kHz Anti-Alias Filter Provides alias protection up to 50 kHz for two channel measurements.

25 kHz Anti-Alias Filter Provides alias protection up to 25 kHz for four channel measurements.

A-Weight Filter Provides additional filtering in the 25 kHz anti-alias filter path for acoustic measurements.

Analog Switch Selects one of four possible signals in the channel 1 or channel 2 input path to send to the ADC

— the signal through the Anti-Alias Filter Bypass, 50 kHz Anti-Alias Filter, 25 kHz Anti-Alias Filter, or A-Weight Filter. In the channel 3 or 4 input path, the Analog Switch selects one of three possible signals to send to the ADC — the Anti-Alias Filter Bypass, 25 kHz Anti-Alias

Filter, or the A-Weight Filter.

Half Range and Differential Overload Detectors Sense the signal at the anti-alias filters. When a detector detects a half-range or overload condition, a digital low is sent to the IIC Interface by the detector. The half-range detector also sends a control signal to the A13 Primary Keypad assembly that lights an LED when a

half-range condition occurs.

IIC (Inter-IC) Interface Contains 32 ports and connects the A2 Input assembly to the serial IIC bus. The A7 CPU

assembly uses the IIC bus to configure the input circuits. When a common mode or differential overload occurs, the IIC Interface forces SINTn low to interrupt the CPU assembly. The CPU assembly then reads the IIC Interface to determine the type of interrupt and the channel it occurred on. During up/down autoranging, the A7 CPU queries the A1 Input assembly for half range status. For a description of the IIC bus, see the description of the IIC Controller for the

"A7 CPU" later in this chapter.

A2 Input Block Diagram: Channel 1 or Channel 2

A2 Input Block Diagram: Channel 1 or Channel 2 (continued)

A2 Input Block Diagram: Channel 3 or Channel 4

A2 Input Block Diagram: Channel 3 or Channel 4 (continued)

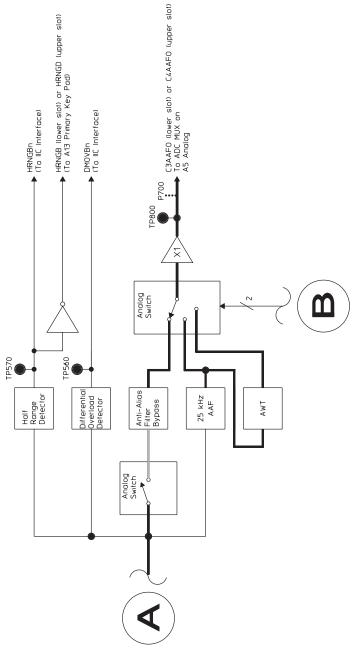

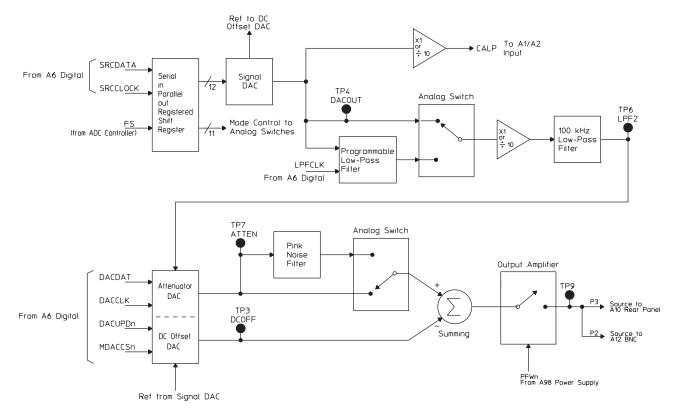

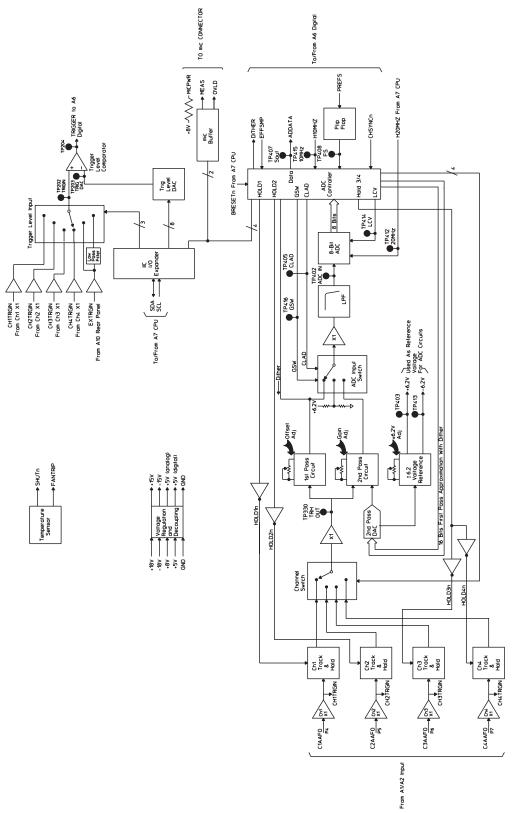

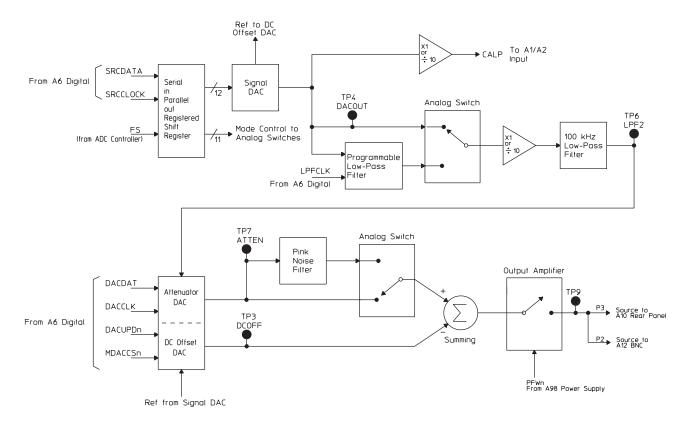

### A5 Analog

The A5 Analog assembly converts the analog input from the A1 Input assembly or A2 Input assemblies to 16-bit serial, digital data. The Analog assembly also converts digital data from the A6 Digital assembly to the analog source output.

The input conversion process passes the analog inputs from all active channels through an 8-bit ADC (analog-to-digital converter) twice adding dither (noise) to improve linearity and the accuracy of low-level signals. All active inputs are sampled simultaneously and held until all have been converted. For the first-pass conversion, the input is scaled then converted to 8-bit serial, digital data. Dither is added to the first-pass data and the sum is converted to an analog voltage. The analog voltage is subtracted from the input and the difference is scaled then converted to 8-bit, serial data in the second pass. The first-pass and second-pass values are added to get the final 16-bit data word. A third conversion clears the 8-bit ADC.

Channel 1 Track & Hold

Holds a voltage sample of the channel 1 input signal for the period of time required by the ADC circuits to digitize the voltage.

Channel 2 Track & Hold

Holds a voltage sample of the channel 2 input signal for the period of time required by the ADC circuits to digitize the voltage.

Channel 3 Track & Hold

Holds a voltage sample of the channel 3 input signal for the period of time required by the ADC circuits to digitize the voltage.

Channel 4 Track & Hold

Holds a voltage sample of the channel 4 input signal for the period of time required by the ADC circuits to digitize the voltage.

Channel Switch

For the two channel analyzer, the Channel Switch multiplexes the channel 1 and channel 2 input signals during two channel measurements . During single channel measurements, the channel 1 and channel 2 signals are not multiplexed. Instead, the Channel Switch is fixed to the output of the Channel 1 Track & Hold. For the four channel analyzer, the Channel Switch multiplexes the channel 1 and channel 2 input signals during two channel measurements. During four channel measurements, the Channel Switch multiplexes the channel 1, 2, 3, and 4 input signals. The output of the Channel Switch is converted to a 16-bit digital word by passing the signal through an 8-bit ADC twice.

1st Pass Circuit

Divides the Channel Switch output by four and level shifts it to the 8-bit ADC input range of 0 to -0.5 V.

ADC Controller

Adds dither (noise) to the first pass signal to increase the accuracy and reduce the non-linearity of the Analog-to-Digital conversion. After the first pass signal is filtered and converted to an 8-bit word, the ADC Controller adds the dither and outputs a 16-bit word to the 2nd Pass DAC. After the second pass signal is filtered and converted to an 8-bit word, the ADC Controller adds the second pass word to the first pass word to obtain a 16-bit data word. The ADC Controller then sends the converted data as ADDATA to the A6 Digital assembly. The ADC Controller also detects an ADC overload when the signal to the analog-to-digital converter is too high. The overload information is sent as ADCOL and ADCUL to the A6 Digital assembly.

A5 Analog Block Diagram: ADC and Trigger

A5 Analog

ADC Input Switch Connects the first pass signal to the low pass filter on the first pass. On the second pass, the

> ADC Input Switch connects the second pass signal to the low pass filter. After the second pass, the ADC Input Switch connects a 0.34 Vdc signal to the low pass filter to reset the 8-Bit ADC.

Low Pass Filter Reduces noise and prevents high frequency signals from overdriving the 8-bit ADC.

8-Bit ADC Converts the signal to an 8-bit word.

2nd Pass DAC Converts the first pass word plus dither to a voltage that is sent to the 2nd Pass Circuit.

2nd Pass Circuit Compares the output of the 2nd Pass DAC (converted first pass signal plus dither) to the

original input signal (which is still held by the Track & Hold) and produces a difference

voltage. This difference voltage is the second pass signal.

Reduces the error due to temperature variations. This voltage reference is used by the 1st Pass ±6.2 Voltage Reference

Circuit, 2nd Pass Circuit, ADC Input Switch, 8-bit ADC, and Track & Hold. Since the 8-bit ADC's gain is derived from this voltage reference, the adjustment for this voltage reference is

also the gain adjustment for the 8-bit ADC.

Trigger-Level Input Connects the appropriate signal to the Trigger-Level Comparator.

Temperature Sensor Senses the analyzer's internal temperature. If the internal temperature exceeds a set point, this

> circuit sets FANTRIP high which turns the fan back on if the fan was turned off by the user. If the temperature becomes excessive, this circuit sets SHUTn low which forces all A98 Power

Supply assembly output voltages to zero.

Trigger-Level

Comparator Trigger Level DAC Compares the signal level with the value from the Trigger Level DAC.

Provides the trigger level. The A7 CPU assembly sets the trigger level via the IIC bus using

the value set with the [TRIGGER SETUP] and [LEVEL] softkeys.

Mic Buffer Buffers control signals for the optional sound intensity probe. When a measurement is being

> made, the MEAS line goes high to turn on the probe's green LED. If an overload occurs during the measurement, the OVLD line goes high to turn on the probe's yellow LED.

IIC Interface Provides the interface between the A7 CPU assembly and the A5 Analog assembly.

Serial In Parallel Out

Shift Register Signal DAC