## Motorola MPC566EVB Evaluation Board

Limited Availability

New From Surplus Stock

**Open Web Page**

https://www.artisantg.com/81488-2

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

TECHNOLOGY GROUP

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# MPC566EVB User's Manual

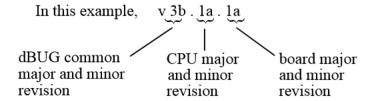

MPC566EVBUM Rev. 1.2, 3/2003

## **Revision History**

| Version<br>Number | Revision<br>Date | Description of Changes                                                                                             |

|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------|

| 1.1               | 11/2002          | Initial Version                                                                                                    |

| 1.2               | 3/2003           | Fixed typos. Added appendix describing dBUG ethernet configuration. Added appendix for emulating the MPC53X parts. |

|                   |                  |                                                                                                                    |

|                   |                  |                                                                                                                    |

DigitalDNA and Mfax are trademarks of Motorola, Inc.

IBM PC and IBM AT are registered trademark of IBM Corp.

All other trademark names mentioned in this manual are the registered trade mark of respective owners

No part of this manual and the dBUG software provided in Flash ROM's/EPROM's may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise. Use of the program or any part thereof, for any purpose other than single end user by the purchaser is prohibited.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

**USA/EUROPE/Locations Not Listed:** Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447

**JAPAN:** Motorola Japan Ltd.; SPS, Technical Information Center, 3–20–1, Minami–Azabu. Minato–ku, Tokyo 106–8573 Japan. 81–3–3440–3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852–26668334

Technical Information Center: 1-800-521-6274

HOME PAGE: http://www.motorola.com/semiconductors

Document Comments: FAX (512) 895-2638, Attn: RISC Applications Engineering

World Wide Web Addresses: http://www.motorola.com/PowerPC http://www.motorola.com/NetComm http://www.motorola.com/ColdFire

Axiom Manufacturing: http://www.axman.com

## **Cautionary Notes**

Axiom Manufacturing (http://www.axman.com) reserves the right to make changes without further notice to any products to improve reliability, function or design. Axiom does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under patent rights or the rights of others. Axiom products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which failure of the Axiom product could create a situation where personal injury or death may occur. Should Buyer purchase or use Axiom manufacturing products for any such unintended or unauthorized application, Buyer shall indemnify and hold Axiom Manufacturing and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Axiom Manufacturing was negligent regarding the design or manufacture of the part or system.

#### **EMC Information on MPC566EVB**

- This product as shipped from the factory with associated power supplies and cables, has been tested and meets with requirements of EN5022 and EN 50082-1: 1998 as a CLASS A product.

- 2. This product is designed and intended for use as a development platform for hardware or software in an educational or professional laboratory.

- 3. In a domestic environment this product may cause radio interference in which case the user may be required to take adequate measures.

- 4. Anti-static precautions must be adhered to when using this product.

- 5. Attaching additional cables or wiring to this product or modifying the products operation from the factory default as shipped may effect its performance and also cause interference with other apparatus in the immediate vicinity. If such interference is detected, suitable mitigating measures should be taken.

## WARNING

This board generates, uses, and can radiate radio frequency energy and, if not installed properly, may cause interference to radio communications. As temporarily permitted by regulation, it has not been tested for compliance with the limits for class a computing devices pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference. Operation of this product in a residential area is likely to cause interference, in which case the user, at his/her own expense, will be required to correct the interference.

## **Contents**

| Paragraph<br>Number | Title                                            | Page<br>Number |

|---------------------|--------------------------------------------------|----------------|

|                     | Chapter 1<br>MPC566 EVB Board                    |                |

| 1.1                 | Processor                                        | 1-3            |

| 1.2                 | System Memory                                    | 1-4            |

| 1.2.1               | External Flash                                   | 1-4            |

| 1.2.2               | SRAM                                             | 1-5            |

| 1.2.3               | Internal SRAM                                    | 1-5            |

| 1.2.4               | Internal Flash                                   | 1-5            |

| 1.2.5               | MPC566EVB Memory Map                             | 1-5            |

| 1.2.5.1             | Memory Device / Bank Selection and Configuration | 1-6            |

| 1.2.5.2             | Memory Bank Chip Select Configuration            | 1-7            |

| 1.2.5.3             | Reset Vector Mapping                             | 1-7            |

| 1.3                 | Support Logic                                    | 1-8            |

| 1.3.1               | Reset Logic                                      | 1-8            |

| 1.3.2               | Clock Circuitry                                  | 1-8            |

| 1.3.3               | Watchdog Timer                                   | 1-8            |

| 1.3.4               | Exception Sources                                | 1-8            |

| 1.3.5               | TA Generation                                    | 1-9            |

| 1.3.6               | User's Program                                   | 1-9            |

| 1.3.7               | Power Oak K/I/S Hardware Options                 |                |

| 1.4                 | Communication Ports                              | 1-11           |

| 1.4.1               | COM1 - COM4                                      |                |

| 1.4.2               | CAN PORTs and Options                            |                |

| 1.4.3               | 10/100T Ethernet Port                            | 1-14           |

| 1.4.4               | BDM and NEXUS Development Ports                  | 1-15           |

| 1.4.4.1             | BDM Port Options                                 | 1-15           |

| 1.4.4.2             | Nexus Connector                                  | 1-16           |

| 1.5                 | Connectors and User Components                   | 1-19           |

| 1.5.1               | Keypad                                           |                |

| 1.5.2               | LCD Port                                         |                |

| 1.5.3               | User Components                                  |                |

| 1.5.4               | MPC566EVB Hardware Options                       |                |

| 1.5.5               | Signals Available on Board                       | 1-22           |

| 1.5.5.1             | IRQ PORT                                         | 1-22           |

| 1.5.5.2             | BUS_PORT                                         |                |

| 1.5.5.3             | TPU_PORTs                                        |                |

| 1.5.5.4             | CONTROL_PORT                                     |                |

| 1.5.5.5             | MIOS_PORT                                        |                |

| 1.5.5.6             | QADC_PORTs                                       |                |

| 1.5.5.7             | QSM_PORTs                                        |                |

| 1.5.5.8             | MICTOR 1 – 3 PORTs                               | 1-28           |

**MOTOROLA**

## **Contents**

| Paragraph<br>Number | Title                                                         | Page<br>Number |

|---------------------|---------------------------------------------------------------|----------------|

| 1.6                 | Reference Documents                                           | 1-28           |

| 1.7                 | Software Development                                          | 1-28           |

|                     | Chapter 2 Initialization and Setup                            |                |

| 2.1                 | System Configuration                                          | 2-1            |

| 2.2                 | Installation And Setup                                        |                |

| 2.2.1               | Unpacking                                                     |                |

| 2.2.2               | Preparing the Board for Use                                   |                |

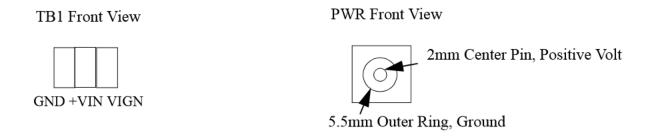

| 2.2.3               | Providing Power to the Board                                  |                |

| 2.2.4               | Selecting Terminal Baud Rate                                  |                |

| 2.2.5               | The Terminal Character Format.                                |                |

| 2.2.6               | Connecting the Terminal                                       |                |

| 2.2.7               | Using a Personal Computer as a Terminal                       | 2-6            |

| 2.3                 | MPC566EVB Jumper and Switch Setup                             |                |

| 2.3.1               | Reset Configuration Word and Configuration Switch (CONFIG_SW) |                |

| 2.3.2               | Memory Configuration (MAP_SW)                                 |                |

| 2.4                 | System Power-up and Initial Operation                         | 2-10           |

|                     | Chapter 3 Using the Monitor/Debug Firmware                    |                |

| 3.1                 |                                                               | 2.1            |

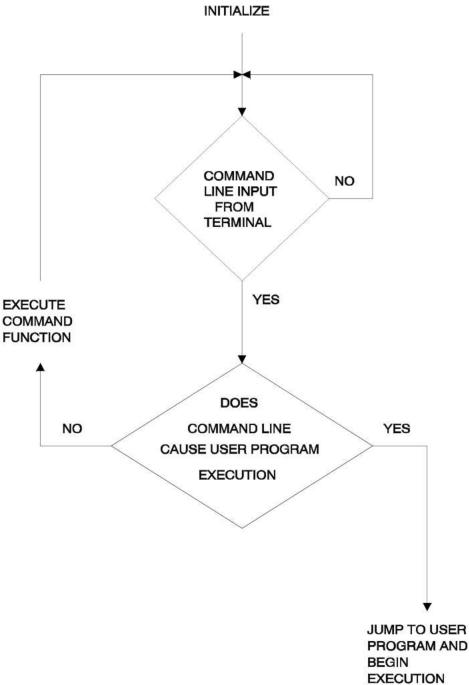

| 3.1                 | What Is dBUG?                                                 |                |

| 3.2.1               | Operational Procedure                                         |                |

| 3.2.1               | System Power-up                                               |                |

| 3.2.2.1             | System Initialization                                         |                |

| 3.2.2.1             |                                                               |                |

| 3.2.2.2             | Non-Maskable Interrupt ButtonSoftware Reset Command           |                |

| 3.2.2.3             |                                                               |                |

| 3.4                 | Command Line Usage Commands                                   |                |

| 3.5                 | System Call Functions                                         |                |

| 3.5.1               | OUT CHAR                                                      |                |

| 3.5.2               | IN CHAR                                                       |                |

| 3.5.3               | IN_CHAR IN STAT                                               |                |

| 3.5.4               | IN_STAT                                                       |                |

| 3.5.5               | ISR_REGISTERISR_REMOVE                                        |                |

| 3.5.6               | EXIT TO dBUG                                                  |                |

| 3.3.0               | EATI_TO_ubUU                                                  | 3-41           |

|                     | A management A                                                |                |

# Appendix A MPC535/536 Emulation

## **Contents**

| Paragraph<br>Number | Title Nur                                         |     |  |  |

|---------------------|---------------------------------------------------|-----|--|--|

|                     | Appendix B Configuring dBUG for Network Downloads |     |  |  |

| B.1                 | Required Network Parameters                       | B-1 |  |  |

| B.2                 | Configuring dBUG Network Parameters               |     |  |  |

| B.3                 | Troubleshooting Network Problems                  |     |  |  |

## **Contents**

Paragraph Page Number Title Number

# Chapter 1

### MPC566 EVB Board

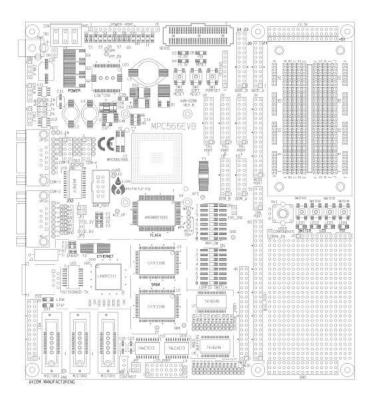

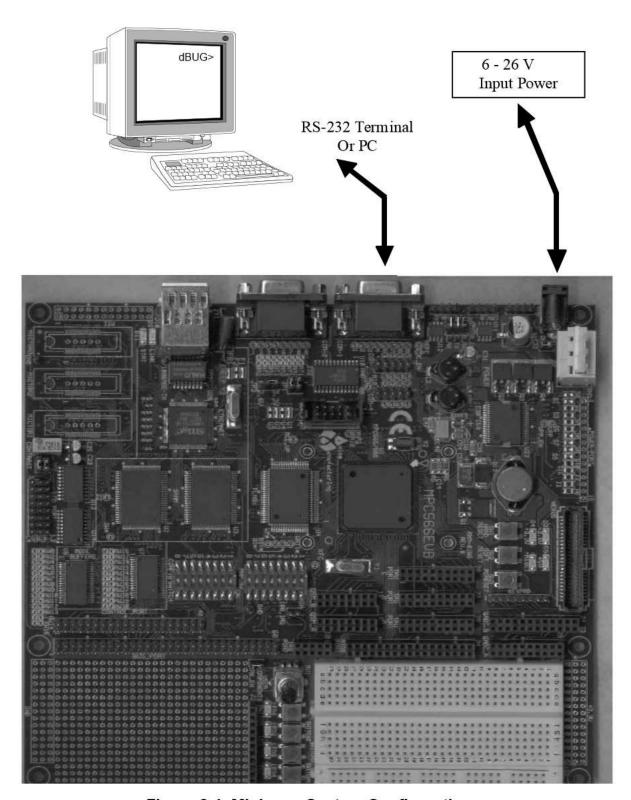

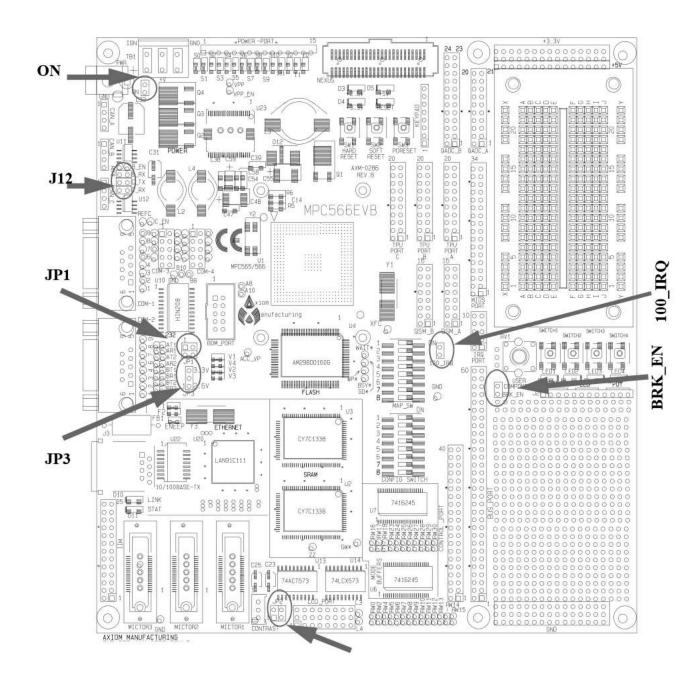

The MPC566EVB is an MPC566-based evaluation board that can be used for the development and test of microcontroller systems<sup>1</sup> (see Figure 1-1). The MPC566 is a member of the Motorola MPC500 RISC microcontroller family. It is a 32-bit processor with a 32-bit internal address bus and 32 lines of data.

The evaluation board is a development and test platform for software and hardware for the MPC566<sup>1</sup>. The system provides for development of target applications for the similar MPC561, MPC562, or MPC563 microcontrollers also. It can be used by software and hardware developers to test programs, tools, or circuits without having to develop a complete microcontroller system themselves. All special features of the MPC566<sup>1</sup> are supported.

The heart of the evaluation board is the MPC566. The MPC566EVB has 1Mbyte (256K x 32) external SRAM for development or application memory, 2Mbyte (512K x 32) external Flash memory, and numerous hardware expansion possibilities. The MPC566EVB board also provides an Ethernet interface (10/100BaseT), TouCAN, and RS232 interface in addition to the built-in I/O functions of the MPC566¹ device for programming and evaluating the attributes of the microprocessor. To support development and test, the evaluation board can be connected to debuggers and emulators produced by different manufacturers.

The MPC566EVB provides for low cost software testing with the use of a ROM resident debug monitor, dBUG, programmed into the external Flash device. Operation allows the user to load code in the on-board RAM, execute applications, set breakpoints, and display or modify registers or memory. After software is operational, the user may program the MPC566 Internal Flash EEPROM or the on-board FLASH memory for dedicated operation of new software application. No additional hardware or software is required for basic operation. For high level debug, extensive third-party tools are available for the MPC500 series. The Nexus and BDM debug ports are available to connect the tool sets.

#### **Specifications**

Clock: 56 MHz Maximum, 4Mhz reference

Operating temperature: 0°C to +70°C

Power requirement: 6 – 26V DC @ 300 ma Typical

Power output: 5.8V @ 1.5A output with 5V, 3.3V, and 2.6V regulated supplies

Board Size: 7.00 x 7.60 inches, 8 layers

<sup>&</sup>lt;sup>1</sup>The MPC566E∨B can be used to emulate the MPC535 and MPC536. See Appendix A and MPC566 Electrical Spec for limitations.

### •Memory Devices:

1M Byte (256K x 32) Sync. SRAM

2M Byte (512K x 32) Sync. FLASH

1M Byte FLASH internal to MPC566 device

36K Byte SRAM internal to MPC566 device

- •POWER OAK (PC33394 P2.6) regulated power supply for 5V, 3.3V and 2.6V supplies.

- •MAP Switch provides easy assignment of chip selects and memory mapping.

- •CONFIG Switch Basic necessary Reset Word Configuration options.

- •COM1 SCIA1 with RS232 type DB9-S Connection

- •COM2 SCIA2 with RS232 type DB9-S Connection, TX / RX polarity option.

- •COM3 & 4 SCIB1 and SCIB2 with RS232 type DB9-S Connection, 10 pin IDC ribbon header connectors.

- •CAN Ports<sup>1</sup> 3 CAN transceiver interfaced ports, 1 x 4 headers.

- •10/100T Ethernet Port LAN91C111 based MAC+PHY, memory mapped.

- •DEVELOPMENT Ports Nexus 50 pin and dual voltage BDM Port.

- •LCD Port LCD Module Interface Connector w/ Contrast Adjust, Buffered and Memory Mapped

- •KEYPAD Port<sup>1</sup> 16 Key passive interface, applies QADC B channels for operation.

- •BUS Port 32 data and 24 address lines on 60 pin header.

- •CONTROL Port Bus Controls with 40 pin header.

- •QSM Ports 2 Serial I/O ports with 16 pin socket headers.

- •MIOS Port MDA, PWM, and MGPIO ports with 34 pin socket header.

- •TPU Ports<sup>1</sup> 3 Timing Processor I/O ports with 20 pin socket headers.

- •QADC Ports<sup>1</sup> 2 Analog I/O ports, one 20 pin and one 24 pin socket header.

- •**IRQ Port** Interrupt or MPC566 port I/O with 10 pin socket header.

- •POWER Port Primary and standby power supply access port, no header.

- •I/O Connectors in .1 grid, pin headers for bus and control provide easy ribbon cable connection for external connections. Socket headers provide easy wire connection to breadboard prototype area with 22ga solid wire.

- •Large Prototyping Area with +5V and ground connection grids.

- •Mictor Logic Probe connectors for the Address and Data bus (Not installed default)

- •Breadboard Prototyping area (2.5 x 1.5 inch) for easy installation of test connections.

- •System Indicators Reset Indicator, Supply voltage indications for 5V, 3.3V, and 2.6V supplies

- •Reset Switches POReset, Hard, Soft reset buttons.

- •User Components 4 user LEDs (one with debounce), 4 user Switches, 1 user Potentiometer with socket header for I/O connection.

<sup>&</sup>lt;sup>1</sup>The MPC535/6 has limited or no functionality for this module. See Appendix A

Figure 1-1. MPC566 EVB top view

## 1.1 Processor

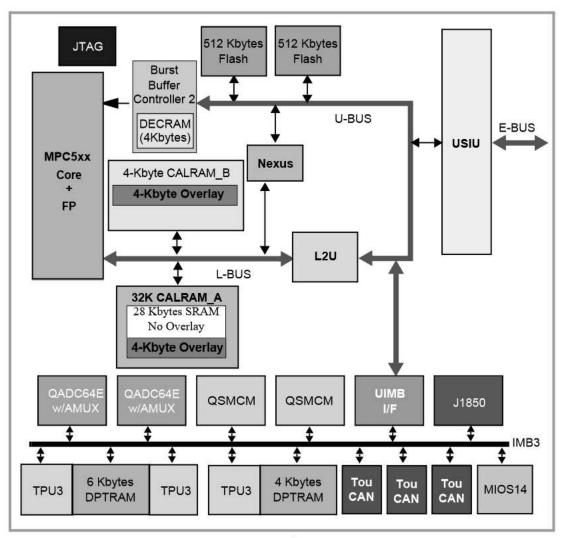

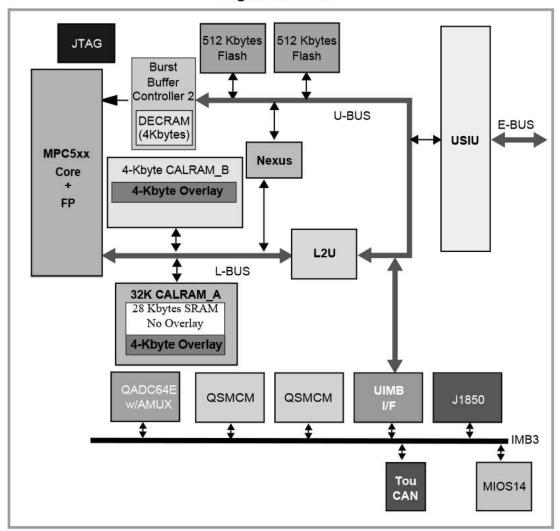

The microprocessor used on the MPC566EVB is the highly integrated Motorola PowerPC MPC566 32-bit microcontroller. The MPC566 implements a PPC ISA core with 1MByte UC3F flash, four UART channels, three Timing Processor Units (TPUs)<sup>1</sup>, 36 KBytes of SRAM plus 4KBytes DECRAM, a QSPI (Queued Serial Peripheral Interface) module, three TouCAN modules<sup>1</sup>, 12 PWMs and 6 counter submodules in the MIOS, enhanced QADC64E, PPM module<sup>1</sup>, a Nexus debug interface port, and 6KByte DPTRAM<sup>1</sup>. This processor communicates with external devices over a 32-bit wide data bus, D[0:31]. The MPC566 can address a 32 bit address range. Only 24 bits are available on the bus however. There are internally generated chip selects to allow the full 32 bit address range to be selected. There are regions that can be decoded to allow superviser, user, instruction, and data each to have the 32-bit address range. All the processor's signals are available through the expansion connector (BUS\_PORT). Refer to the schematic for their pin assignments.

The MPC566 processor has the capability to support both an IEEE-ISTO 5001-1999 NEXUS port and a BDM debug port. These ports are multiplexed and can be used with third party tools to allow the user to download code to the board. The board is configured to boot up in the normal/BDM mode of operation. The BDM signals are available at the port labeled BDM\_PORT. The NEXUS connector is near the reset switches on the board. It is the 2002 50 pin standard I/O connections and connector. The BDM and NEXUS ports can not be used at the same time.

<sup>&</sup>lt;sup>1</sup>The MPC535/6 has limited or no functionality for this module. See Appendix A.

#### **System Memory**

Figure 1-2 shows the MPC566 block diagram.

Figure 1-2. MPC566<sup>1</sup> Block Diagram

## 1.2 System Memory

## 1.2.1 External Flash

One on-board Flash ROM (U4) is used in the system. The Am29BDD160G device contains 16Mbits of non-volatile storage (1 M x 16-bit/512 K x 32-bit) giving a total of 2MBytes of Flash memory. This device requires a 32 bit wide port and must be written in 32 bit word size data. It may be read in bytes, half words, or words. Wait states are required to access in asynchronous mode and the same wait state delay is required during the first cycle of a burst type access. Refer to the specific device data sheet for configuring the flash memory. User should note that the debug monitor firmware is installed in this flash device. Development tools or user application programs

<sup>&</sup>lt;sup>1</sup>See Appendix A for block diagram of MPC535/6

**System Memory**

may erase or corrupt the debug monitor. If the debug monitor becomes corrupted and it's operation is desired, the firmware must be programmed into the flash by applying a development port tool such as BDM or Nexus. User should use caution to avoid this situation. The upper 1 MByte is used to store the MPC566EVB dBUG debugger/monitor firmware (0x0090 0000 to 0x009F FFFF).

### 1.2.2 SRAM

The MPC566EVB has two 512 KByte device on the board (U2). It's starting address is 0xFFF0 0000.

The synchronous SRAM Memory Bank is composed of two128K x 32 memory devices. These memory devices are connected in linear order from U2 to U3 if more than one is available, so that the low order address of the memory bank will access U2 and the high order addresses of the memory bank will access U3. This memory bank must be configured as a 32 bit wide port but is byte, half word, and word accessible for read or write operations.

Also see Section 1.2.5, "MPC566EVB Memory Map".

### 1.2.3 Internal SRAM

The MPC566 processor has 36-KBtyes of internal memory which may be used as data or instruction memory. This memory is mapped to  $0x003F_8000$  and configured as data space but is not used by the dBUG monitor except during system initialization. After system initialization is complete, the internal memory is available to the user. The memory is relocatable to any 32-KByte boundary.

### 1.2.4 Internal Flash

The MPC566 has a U-bus CDR3 flash EEPROM module (UC3F). The primary function of the UC3F flash EEPROM module is to serve as electrically programmable and erasable non-volitle memory (NVM) to store program instructions and/or data. The MPC566 flash EEPROM array has 1 Mbytes of NVM that is divided into sixteen 64-Kbyte array blocks. If the flash array is disabled in the IMMR register (FLEN=0), then neither the UC3F array or the UC3F control registers are accessible. This feature allows the MPC566 to emulate the MPC561/562.

Please refer to the MPC566 User's Manual for more details.

## 1.2.5 MPC566EVB Memory Map

Interface signals to support interface to external memory and peripheral devices are generated by the memory controller. It supports four regions on four chip-select pins. The general purpose chip-selects are available on lines  $\overline{CS[0]}$  through  $\overline{CS[3]}$ .  $\overline{CS[0]}$  also functions as the global (boot) chip-select for booting out of external flash.

Since the MPC566 chip selects are fully programmable, the memory banks can be located at any location in the MPC5xx memory space.

#### **System Memory**

Following is the default memory map for this board as configured by the Debug Monitor located in the external flash bank. The internal memory space of the MPC566 is detailed further in the MPC565-6 Users Manual. Chip Selects 0-3 can be changed by user software to map the external memory in different locations but the chip select configuration such as wait states and transfer acknowledge for each memory type should be maintained.

### Possible Chip Select usage:

| Synchronous SRAM Memory Bank  | CS0 or CS1 | default CS1, MAP SW. 1,2   |

|-------------------------------|------------|----------------------------|

| Synchronous FLASH Memory Bank | CS0 or CS2 | default CS0, MAP SW. 3,4   |

| 10/100T / LCD Port            | CS3        | default CS3, MAP SW. 6,7   |

| MPC566 Internal Flash         | N/A        | MAP_SW. 8, may effect mem- |

| ory map of chip selects       |            |                            |

The MPC566EVB Default Memory Map shows the MPC566EVB memory map.

Table 1-1. The MPC566EVB Default Memory Map

| Address Range             | Signal and Device                                                   |

|---------------------------|---------------------------------------------------------------------|

| 0x0000_0000 - 0x0007_FFFF | 1MB UC3F Flash                                                      |

| 0x0010_0000 - 0x002F_7FFF | Reserved for Flash                                                  |

| 0x002F_8000 - 0x002F_8FFF | BBC DECRAM 4 KBytes                                                 |

| 0x002F_9000 - 0x002F_9FFF | Reserved for BBC                                                    |

| 0x002F_A000 - 0x002F_BFFF | BBC Control                                                         |

| 0x002F_C000 - 0x002F_FFFF | USIU & Flash Control                                                |

| 0x0030_0000 - 0x0030_7FFF | UIMB I/F & IMB Modules 32KBytes                                     |

| 0x0030_8000 - 0x0037_FFFF | Reserved for IMB                                                    |

| 0x0038_0000 - 0x0038_007F | CALRAM/READI Control                                                |

| 0x0038_0080 - 0x0038_3FFF | Reserved (L-bus Control)                                            |

| 0x0038_4000 - 0x003F_6FFF | Reserved (L-bus Memory)                                             |

| 0x003F_7000 - 0x003F_FFFF | CALRAM (internal SRAM)                                              |

| 0x0080_0000 - 0x00A0_0000 | External Flash 2MByte (0x0090_0000 - 0x00A0_0000 reserved for dBUG) |

| 0x0100_0000 - 0x0108_0000 | Ethernet                                                            |

| 0xFFF0_0000 - 0xFFFF_FFFF | External SRAM 1MB                                                   |

## 1.2.5.1 Memory Device / Bank Selection and Configuration.

The MPC566EVB board has one internal memory bank, two external memory banks and a Peripheral memory bank that provide:

- 36KByte Internal SRAM

- MPC566 512K byte Internal FLASH Memory (U1)

- 256K x 32bit (1MByte) Synchronous Static RAM (U2/3).

- 512K x 32bit (2MByte) Synchronous Flash EEPROM (U4)

- Peripherals 10/100T Ethernet and LCD Port

Each external RAM or Flash memory bank can be configured individually to operate from the MPC566 chip selects. Caution should be used not to place more than one memory bank on the CS0 chip select and to properly configure the chip select to control the memory devices provided in the memory bank correctly. **Failure to observe precautions may render the external memory bus inoperable.**

The MAP Switch (MAP\_SW) connects MPC566 chip selects to the different external memory banks. If memory access problems occur, the settings of these options and the associated chip select configurations should be reviewed with some detail. Information to configure the chip selects and memory is detailed in the following section.

### 1.2.5.2 Memory Bank Chip Select Configuration

Application software that executes on Reset must configure each memory bank chip select properly for correct operation. Chip Select Memory Options shows the default memory settings programmed by the dBUG ROM monitor and may be applied for most user applications:

Table 1-2. Chip Select Memory Options

| Memory Bank                                | Reg. | Default Value | Notes                                                                                                                                                                                                                                                                  |

|--------------------------------------------|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS1 = SRAM                                 | BR1  | 0xFFF0_0003   | Base Address = 0xFFF0_0000, Port width = 32 bit *Default                                                                                                                                                                                                               |

| CS1 = SRAM, asynchronous access mode       | ·    |               | Memory Range = 0xFFF0_0000 > 0xFFFF_FFFF, wait state = 0.                                                                                                                                                                                                              |

| CS0 = FLASH                                | BR0  | 0x0080_0003   | Base address 0x0080_0000, Port width = 32 bit * <b>Default</b>                                                                                                                                                                                                         |

| CS0 = FLASH, asynchro-<br>nous access mode | OR0  | 0xFFE0_0030   | Memory range = 0x0080_0000 > 0x009F_FFFF, wait state = 3, asynchronous operation 40Mhz clock, 95ns device.  Note U4 = 2M bytes and will mirror 2x with this setting.  Usable range = 0x0080_0000 > 0x008F_FFFF (dBUG monitor is in upper half starting at 0x0090_0000) |

| CS3 = Peripheral                           | BR3  | 0x0100_0807   | Base address = 0x0100_0000, Port width = 16 bit *Default External TA* generation provided.                                                                                                                                                                             |

| CS3 = Peripheral, asyn-<br>chronous        | OR3  | 0xFFFF_80F0   | Memory Range 0x0100_0000 > 0100_7FFF, wait state = External Terminate (TA*) *Default Note Peripheral memory map.                                                                                                                                                       |

## 1.2.5.3 Reset Vector Mapping

After reset, the processor attempts to execute at physical address  $0x0000\_0100$  if the hard reset configuration word IP bit is cleared to 0 or physical address  $0xFFF0\_0100$  if the hard reset configuration word IP bit is set to 1. This requires the board to have a non-volatile memory device in this range with the correct information stored in it. The MPC566 processor chip-select zero ( $\overline{CS0}$ ) responds to any accesses after reset until the OR0 is written. Since  $\overline{CS0}$  (the global chip select) is connected to the Flash ROM (U6), the Flash ROM initially appears at address  $0xFFF0\_0000$ . The initialization routine then programs the chip-select logic, locates the Flash

#### Support Logic

ROM to start at 0x0080\_0000 and configures the rest of the internal and external peripherals. Please refer to the MPC565 user's manual (Global (Boot) Chip-Select Operation) for more information.

## 1.3 Support Logic

## 1.3.1 Reset Logic

The reset logic provides system initialization. Reset occurs during power-on or via assertion of the signal RESET which causes the MPC566 to reset. HRESET is triggered by the reset switch (SW1) which resets the entire processor/system.

dBUG configures the MPC566 microprocessor internal resources during initialization. The contents of the exception table are copied to address 0xFFF0\_0000 in the SDRAM. The Software Watchdog Timer is disabled, the Bus Monitor is enabled, and the internal timers are placed in a stop condition. A memory map for the entire board can be seen in Table 1-1., "The MPC566EVB Default Memory Map".

### RW0-30: External Reset Configuration Word (RCW) Options

RW0, RW2, RW4 – 18, RW23 – 30 provide the user access to external Reset Configuration Word (RCW) bits not normally required for default MPC566EVB operation. The RW0 – 30 designations reflect the data bus D0 – D30 bit effected when the RCW word is enabled externally. All RW0 – 30 option bits are defaulted to the logic low value during external RCW word operation. The user may apply a wire jumper between the 2 pad positions of each RW0 – 30 option to provide a logic high level on the respective bit position during external RCW operation. Refer to the MPC566 user manual Reset chapter for the respective RCW bit definitions.

## 1.3.2 Clock Circuitry

The MPC566EVB board uses a 4MHz crystal (Y1 on the schematics) to provide the clock to the on-chip oscillator of the MPC566. In addition to the 4MHz crystal, there is also a 25MHz oscillator (Y3) which feeds the Ethernet chip (U20).

## 1.3.3 Watchdog Timer

The duration of the Watchdog is selected by the SWT[1:0] bits in the System Protection and Control Register (SYPCR), SWT[1:0] = 0b11 gives a maximum timeout period of 2<sup>28</sup>/System frequency. The dBUG monitor initializes these bits with the value 0b11, which provides the maximum time-out period, but dBUG does **NOT** enable the watchdog timer via the SYPCR register SWE bit.

## 1.3.4 Exception Sources

The MPC500 family of processors can receive exceptions as a result of external signals, errors, interrupts, or unusual conditions arising in the execution of instructions. When the processor receives an exception, information about the state of the processor is saved and, after switching to supervisor mode, the processor begins handling the exception based on instructions in the

Support Logic

Exception Vector Table in memory. Exceptions are handled in program order based on PowerPC architecture requirements. When an exception occurs that was caused by an instruction, any unexecuted instructions that appear earlier in the instruction stream are required to complete before the exception is taken. Exceptions no associated with a specific instruction (asynchronous exceptions) are recognized when they occur. Exception handlers should save the information in SRR0 and SRR1 soon after the exception is taken to prevent this information from being lost due to another exception being taken.

The processor goes to an exception routine via the exception table. This table is stored in the Flash EEPROM. The address of the table location is set by the IP bit (switch 5 of MAP\_SWITCH). The dBUG ROM monitor writes a copy of the exception table into the RAM starting at 0xFFF0\_0000. To set an exception vector, the user places the address of the exception handler in the appropriate vector in the vector table located at 0xFFF0\_0000.

The MPC566's interrupt controller supports up to 8 external interrups (0 - 7), eight levels for all internal USIU interrupt sources and 32 levels for internal peripheral modules. It has an enhanced mode of operation, which simplifies the MPC566 interrupt structure and speeds up interrupt processing.

### NOTE:

No interrupt sources should have the same level and priority as another. Programming two interrupt sources with the same level and priority can result in undefined operation.

The MPC566EVB hardware uses  $\overline{IRQ}[0]/SGPIOC[0]$  to support the ABORT (Non Maskable Interrupt) function using the ABORT switch (SWITCH1 when BRK\_EN jumper is inserted). This switch is used to force a non-maskable interrupt if the user's program execution should be aborted without issuing a RESET.

Refer to MPC566 User's Manual for more information about the interrupt controller.

### 1.3.5 TA Generation

The TA signal is driven by the slave device from which the current transaction was addressed. It indicates that the slave has received the data on the write cycle or returned data on the read cycle. If the transaction is a burst,  $\overline{TA}$  should be asserted for each one of the transaction beats. The MPC566 drives  $\overline{TA}$  when the slave device is controlled by the on-chip memory controller or when an external master initiated a transaction to an internal slave module.  $\overline{TA}$  is used to indicate the completion of the bus cycle. It also allows devices with different access times to communicate with the processor properly (i.e. asynchronously) like the Ethernet controller. The internal TA generator is used for all external memories. External TA is only used for Ethernet/LCD.

## 1.3.6 User's Program

Switch 5 on the MAP\_SW bank of switches allows users to test code from boot/PORESET without having to overwrite the ROM Monitor. The user's code will boot from internal flash (0x0000\_0000) needs to contain the start of the Exception Vector Table).

When the switch is ON (IP is set), the behavior of the system is normal, dBUG boots and then runs from 0x0090 0000.

Procedure:

#### Support Logic

- Compile and link as though the code was to be placed at the base of the internal flash, but setup so that it will download to the SRAM starting at address 0xFFF0\_8000. The user should refer to their compiler documentation for this, since it will depend upon the compiler used.

- 2. Set IP bit (Switch 5 ON).

- 3. Download to SRAM (If using serial or ethernet, start the ROM Monitor first. If using BDM via a wiggler cable, download first, then start ROM Monitor by pointing the program counter (PC) to 0x0090 0100 and run.)

- 4. In the ROM Monitor, execute the 'upuser' command.

- 5. Turn off IP bit (Switch 5 OFF). User code should now be running from reset/POR.

## 1.3.7 Power Oak K/I/S Hardware Options

Several hardware options surround the Power Oak supply to allow the user access to many of the features. The options are sorted by leading character to indicate functionality. 'K' designated options refer to VKAM and MPC566 back-up supply options. 'I' designated options refer to Interrupt operation options. 'S' designated options refer to MPC566 Reset or I/O signal connection options. Following is the summary table (also refer to MPC566EVB schematic):

Table 1-3. K/I/S Option Table

| Option<br>Designator | Power Oak Signal | MPC566 signal | Associated<br>Option <sup>1</sup> | Default Connection  Closed, Note: REV B board has 0 ohm resistor installed |  |

|----------------------|------------------|---------------|-----------------------------------|----------------------------------------------------------------------------|--|

| K0                   | VKAM             | KAPWR         | K1                                |                                                                            |  |

| K1                   | 2.6V             | KAPWR         | K0                                | Open                                                                       |  |

| К2                   | VKAM             | VDDSRAM1      | K3                                | Closed                                                                     |  |

| К3                   | 2.6V             | VDDSRAM1      | K2                                | Open                                                                       |  |

| K4                   | VKAM             | VDDSRAM2 K5   |                                   | Closed                                                                     |  |

| K5                   | +2.6V            | VDDSRAM2      | K4                                | Open                                                                       |  |

| K6                   | VKAM             | VDDSRAM3      | K7                                | Closed                                                                     |  |

| K7                   | 2.6V             | VDDSRAM3      | K6                                | Open                                                                       |  |

| K8                   | VKAM             | VDDSYN        | К9                                | Open                                                                       |  |

| K9                   | 2.6V             | VDDSYN        | K8                                | Closed                                                                     |  |

| K10                  | VKAM             | VDDRTC        | K11                               | Closed                                                                     |  |

| K11                  | 2.6V             | VDDRTC        | K10                               | Open                                                                       |  |

| 10                   | WAKEUP           | IRQ4          |                                   | Open                                                                       |  |

| 11                   | WAKEUP           | IRQ0          | I2                                | Open                                                                       |  |

| I2                   | PRERESET         | IRQ0          | I1                                | Open                                                                       |  |

**Communication Ports**

| Option<br>Designator | Power Oak Signal | MPC566 signal | Associated<br>Option <sup>1</sup> | Default Connection |

|----------------------|------------------|---------------|-----------------------------------|--------------------|

| S0                   | PORESETB         | PORESET       |                                   | Closed             |

| S1                   | HRESETB          | HRESET        |                                   | Closed             |

| S2                   | SLEEP            | RSTCONF_TEXP  |                                   | Open               |

| S3                   | REGON            | MGPIO15       |                                   | Open               |

| S4                   | CANTXD           | B_CANTX0      | A_CANTX0                          | Open               |

| S5                   | CANRXD           | B_CANRX0      | A_CANRX0                          | Open               |

| S6                   | CS               | A_QSPI_PCS1   |                                   | Closed             |

| S7                   | DO               | A_QSPI_MISO   |                                   | Closed             |

| S8                   | DI               | A_QSPI_MOSI   |                                   | Closed             |

| S9                   | VREF3            | BOEPEE        | S11                               | Open               |

| S10                  | VREF3            | EPEE          | S10                               | Open               |

The MPC535/6 has limited or no functionality for this module. See Appendix A

## 1.4 Communication Ports

The MPC566EVB provides external interfaces for 4 SCI serial ports, 3 CAN ports and a 10/100T ethernet port.

## 1.4.1 COM1 - COM4

The MPC566 processor has two queued serial multi-channel modules (QSMCM\_A and QSMCM\_B) which provides four serial communications interfaces (SCI/UART). These submodules communicate with the CPU via a common slave bus interface unit (SBIU). The signals of COM1 and COM2 pass through external Driver/Receivers to make the channels RS-232 compatible. COM3 and COM4 serial ports with 10 pin IDC to DB9 connector headers are available for RS232 operation of MPC566 SCI B channels 1 and 2. An RS-232 serial cable with DB9 connectors is included with the board. The signals of both channels are available on the QSM\_PORT connector. SCI0 (COM-1) is the "TERMINAL" channel used by dBUG for communication with an external terminal/PC. The "TERMINAL" baud rate defaults to 19200.

#### Notes:

- COM ports provide connection pads 1 9 behind the DB9 cable connectors so the user

may modify operation of the serial connection. Each connection pad is numbered for the

associated serial connector pin. Each connection pad can be isolated from the others if

grouped above, by cutting the associated trace to the pad on the bottom side of the board.

See the MPC566EVB schematic.

- COM-2 has the JP1 DCE/DTE option, see below.

#### **Communication Ports**

3. RS232 translators available to COM3 and COM4 that are not required by user application may be applied to other COM ports by isolating the MPC566 SCI signals to the RS232 transceiver and applying the associated RS232 level input or output to another COM port. User should refer to the schematic diagrams of the board to make sure correct signals and connections are isolated and reconnected for the new application.

### JP1 – COM2 DCE/DTE Option:

COM-2 is optioned as a DCE type RS232 connection by default (same as COM-1). This allows direct connection to a standard 9 pin PC COM serial port.

COM-2 DTE option. This requires a NULL modem adapter to connect to a standard 9 pin PC COM serial port.

### AT1/2, AR1/2, BT1/2, BR1/2 - Serial Port Configuration

The Axx and Bxx cut-away options provide a means of isolating the individual SCI RXD and TXD signals from the RS232 interface translator device (U10) and COM port operation. This allows the SCI channels to be used for other purposes, possibly on the QSM port connector. Following is a table of the SCI signals and AT/R\_ positions used for enabling RS232 and COM port operation. Note: 2mm header maybe installed after cutaways are cut to allow jumper option.

Table 1-4. Serial Port Configuration

| AT_ Position | SCI Channel<br>Signal | RS232 COM Port<br>Connection | COM_PORT Signal<br>Direction to RS232<br>interface translator |  |

|--------------|-----------------------|------------------------------|---------------------------------------------------------------|--|

| AT1          | SCI_A_ TXD1           | COM-1                        | Output                                                        |  |

| AR1          | SCI_A_ RXD1           | COM-1                        | Input                                                         |  |

| AT2          | SCI_A_ TXD2           | COM-2                        | Output                                                        |  |

| AR2          | SCI_A_ RXD2           | COM-2                        | Input                                                         |  |

| BT1          | SCI_B_ TXD1           | COM-3                        | Output                                                        |  |

| BR1          | SCI_B_RXD1            | COM-3                        | Input                                                         |  |

| BT2          | SCI_B_ TXD2           | COM-4                        | Output                                                        |  |

| BR2          | SCI_B_RXD2            | COM-4                        | Input                                                         |  |

## 1.4.2 CAN PORTs and Options<sup>1</sup>

The MPC566EVB board provides 3 CAN transceivers with I/O ports: CAN\_A, CAN\_B, and CAN\_C. CAN\_A is supported by the PC33394 Power Oak CAN transceiver. The CAN\_B and CAN\_C ports are supported by Philips PCA82C250 1M Baud CAN transceivers. The MPC566 CAN\_A port is directly interfaced to the Power Oak transceiver and can not be isolated easily. The MPC566 CAN\_B and C ports are interfaced to the MPC566 TOUCAN channels B and C by option jumpers B\_RX, C\_TX, and C\_RX.

### CAN\_A

The CAN\_A channel transceiver is provided by the Power Oak (PC33394). This transceiver has software selectable options via the QSPI 0 channel which may communicate with the Power Oak device. See the PC33394 data sheet for details. A 4.7K ohm pull-up is provided on the CAN\_A TX signal. Options S4 and S5 are provided near the Power Oak device to provide both MPC566 CAN\_A and CAN\_B channels for messaging on the Power Oak transceiver. If S4 and S5 are connected, the B RX option from the CAN\_B port must be open.

### **B** RX Option Jumper

This option jumper enables the receive connection from the CAN\_B port transceiver to the MPC566 CAN B RX channel. The option allows the isolation of the CAN\_B port transceiver RX signal so that the user may use a different connection or transceiver for the MPC566 CAN B port.

### C\_RX and C\_TX Option Jumpers

These options enable the CAN\_C port transceiver RX and TX signals to be placed on the MPC566 MGPIO port CAN C signals. The CAN C operation on the MPC566 MGPIO port must be enabled in software, see example source code. The MPC566 MGPIO Port bits 13 and 14 are effected along with the MPC566EVB MIOS Port pins 32 and 33 respectfully.

#### B EN and C EN Option Pads, CN1 and CN2 Option Cut-Aways

These options provide access to the output enable and slew rate control of the respective CAN transceiver. By default the transceivers are set to provide minimum slew rate (fast edge) and to be constantly enabled for output. The configuration of the transceivers maybe modified for slew rate or output control or both. Signaling CAN bus slew rate can be modified by increasing the value of R66 and R67 for CAN\_B and CAN\_C respectfully. Opening the CN1 and CN2 away options for CAN\_B and CAN\_C respectfully allows a MPC566 I/O port to be applied to the B\_EN and C\_EN option pads to provide output control. A high level on the B\_EN or C\_EN would disable the respective CAN transceiver output. See the PCA82C250 data sheet on the support CD for additional information.

### CAN\_A, CAN\_B, and CAN\_C Port Connectors

These ports provide the CAN transceiver input and output connection to the CAN bus. The bias or termination for the CAN bus is provided on the EVB board but not pupualted. If required the user must install these components in the RAx, RBx, or RCx locations near the respective CAN port.. Following are the pin connections for the ports:

Pin 1 = CAN-Hi level signal

Pin 2 = CAN-Lo level signal

Pin 3 = Ground or common (this is required for proper return path on CAN bus)

<sup>&</sup>lt;sup>1</sup>The MPC535/6 has limited or no functionality for this module. See Appendix A

#### **Communication Ports**

Pin 4 = +5V supply for remote use or bias of CAN bus.

### CAN\_A, CAN\_B, and CAN\_C Port Termination Options

The RA1-3, RB1-3, and RC1-3 option locations provide the respective CAN A, B, or C port with the ability to add bias and/or termination resistance. RA1, RB1, and RC1 locations provide low bias (to ground) on the respective CAN Port CAN Hi signal. RA3, RB3, and RC3 locations provide high bias (to +5V) on the respective CAN Port CAN Low signal. RA2, RB2, and RC2 locations provide termination between the respective CAN Port CAN Hi and CAN Low signals.

### 1.4.3 10/100T Ethernet Port

The MPC566EVB has an Ethernet controller (SMSC LAN91C111 U20) operating at 10M bits/sec or 100Mbits/sec (see the device data sheet on the support CD forr operation details). The dBUG ROM monitor is programmed to allow a user to download files over a network to memory in different formats. The compiler-formats currently supported are S-Record, COFF, ELF, or Image (raw binary). Refer to Appendix B, "Configuring dBUG for Network Downloads", for details on how to configure the board for network download.

The Ethernet registers are located at chip select CS3 base address in the address range 0x0000 - 0x000F. The access is 16 bits wide or half word transfers only. The LAN91C111 device applies a register bank selection technique to provide a minimum memory space size. Users should review the device data sheet in detail for operation notes. The debug monitor applies the Ethernet for file downloads only, no high level stacks are applied in the sample source code.

RJ45 jack J3 of the Ethernet port provides a direct to HUB type connection. The Ethernet cable provided with the MPC566EVB kit is a crossover type for direct connection of the EVB to a PC host network card. If connection to a HUB is desired, a standard Ethernet cable should be applied.

Table 1-5. Ethernet Jack J3

| PIN | SIGNAL        |

|-----|---------------|

| 1   | TX+           |

| 2   | TX-           |

| 3   | RX+           |

| 4   | Term 1 75 ohm |

| 5   | Term 1 75 ohm |

| 6   | RX-           |

| 7   | Term 2 75 ohm |

| 8   | Term 2 75 ohm |

100\_IRQ Option Jumper

**Communication Ports**

The 100\_IRQ Option jumper provides Ethernet Interrupt capability to the MPC566 processor. With the option installed and the LAN91C111 device properly configured, the MPC566 IRQ1 interrupt can be applied to service the port.

#### LINK and STAT Indicators

The LAN91C111 Ethernet controller provides two indication drivers under software control. The LINK indicator is driven by the LAN91C111 LEDA output and the STAT indicator is driven by the LEDB output.

#### **MII Connector**

The MII connector location is for testing and the connection of an external Ethernet PHY device. This connector is not installed or supported by the EVB application.

## 1.4.4 BDM and NEXUS Development Ports

Both NEXUS (MPC566 Readi Module) and standard BDM (background debug module) development ports are provided on the MPC566EVB for application of integrated software debug tool suites. In order to use the BDM, simply connect the 10-pin debug connector on the board, BDM\_PORT, to the P&E BDM wiggler cable provided in the kit. No special setting is needed. Refer to the MPC566 User's Manual BDM Section for additiona instructions. The NEXUS interface provides the IEEE-ISTO 5001 50 pin standard I/O connections and connector and the BDM port provides the standard 10 pin interface (refer to MPC566EVB schematic sheet 3 for details). User should observe that both ports can not be applied at the same time. Note that the NEXUS interface applies some of the MPC566 standard I/O signals from the MIOS module as alternate development port I/O signals. Following are the I/O effected:

#### NOTE:

BDM functionality and use is supported via third party developer software tools. Details may be found on CD-ROM included in this kit

## 1.4.4.1 BDM Port Options

The BDM Port provides several options for flexibility of operation.

#### JP3 - BDM Port Interface Level

JP3 provides the option of 2.6V or 3.3V interface levels on the BDM port. This allows the use of legacy MPC555 BDM tools on the MPC566. The option is set for 3.3V interface from the factory. The following JP3 reference is with the MPC566EVB setting with the COM ports facing left.

#### **Communication Ports**

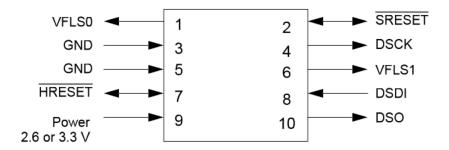

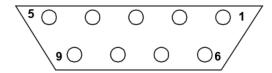

The signals which are neccessary for debug are available at connector (BDM\_PORT). Figure 1-3 shows the (BDM\_PORT) Connector pin assignment.

Figure 1-3. The BDM PORT Connector pin assignment

#### V1, V2, V3, and V4

The V1 – V4 options provide a way to use the alternate VFLS0 and VFLS1 BDM signals from the MPC566. By default, the primary VFLS0 and VFLS1 signals are applied by V1 and V2 default connections. To modify the BDM port to apply the alternate VFLS0 and VFLS1 signals, options V1 and V2 should be cut and options V3 and V4 connected.

#### 1.4.4.2 Nexus Connector

The 2001-Nexus standard defines several different standards for different speed accesses to a microcontroller in a target system. These standards have been revised since that release. The new connectors come in both a robust and a non-robust configuration. In addition, each connector has 2 definitions depending upon whether the connection is an Auxiliary only (Auxiliary In and Auxiliary Out) connection or a JTAG IEEE 1149.1 port with an Auxiliary Output port.

#### NOTE

The MPC56x parts do not support the JTAG IEEE 1149.1 configuration.

Table 1-6. MPC56x Nexus 50-Pin Definition (Full-Port Mode)

| MPC56x<br>Signal           | Nexus Auxiliary<br>Signal | 1/0             | Pin<br>Number | Pin<br>Number | 1/0          | Nexus Auxiliary<br>Signal | MPC56x<br>Signal |

|----------------------------|---------------------------|-----------------|---------------|---------------|--------------|---------------------------|------------------|

| _                          | UBATT                     | OUT             | 1             | 2             | OUT          | UBATT                     | _                |

| VSTBY2.6                   | VSTBY                     | OUT             | 3             | 4             | IN or<br>OUT | TOOL_IO0                  | _                |

| _                          | TOOL_IO1                  | IN or<br>OUT    | 5             | 6             | IN or<br>OUT | TOOL_IO2                  | _                |

| HRESET                     | /RESET <sup>1</sup>       | IN <sup>2</sup> | 7             | 8             | OUT          | VREF                      | VDD2.6           |

| EVTI                       | /EVTI                     | IN <sup>2</sup> | 9             | 10            | _            | GND                       | GND              |

| RSTI                       | /RSTI                     | IN <sup>2</sup> | 11            | 12            |              | GND                       | GND              |

| MSEI                       | /MSEI                     | IN <sup>2</sup> | 13            | 14            | _            | GND                       | GND              |

| MDI[0]                     | MDI0                      | IN <sup>2</sup> | 15            | 16            | _            | GND                       | GND              |

| MCKI                       | мскі                      | IN <sup>2</sup> | 17            | 18            | _            | GND                       | GND              |

| MDO[0]                     | MD00                      | OUT             | 19            | 20            | _            | GND                       | GND              |

| мско                       | мско                      | OUT             | 21            | 22            | _            | GND                       | GND              |

| LWP[1]                     | /EVTO                     | OUT             | 23            | 24            | _            | GND                       | GND              |

| MSEO                       | /MSEO0                    | OUT             | 25            | 26            | IN or<br>OUT | VENDOR_IO0                | LWP[0]           |

| MDO[1]                     | MDO1                      | OUT             | 27            | 28            | _            | GND                       | GND              |

| MDO[2]                     | MDO2                      | OUT             | 29            | 30            | _            | GND                       | GND              |

| MDO[3]                     | MDO3                      | OUT             | 31            | 32            | _            | GND                       | GND              |

| MDI[1]                     | MDI1                      | IN <sup>2</sup> | 33            | 34            | _            | GND                       | GND              |

| _                          | /MSEO1                    | OUT             | 35            | 36            | _            | GND                       | GND              |

| MDO[4]                     | MDO4                      | OUT             | 37            | 38            | _            | GND                       | GND              |

| MDO[5]                     | MDO5                      | OUT             | 39            | 40            | _            | GND                       | GND              |

| MDO[6]                     | MDO6                      | OUT             | 41            | 42            | _            | GND                       | GND              |

| MDO[7]                     | MDO7                      | OUT             | 43            | 44            | _            | GND                       | GND              |

| _                          | MDI2                      | IN <sup>2</sup> | 45            | 46            | _            | GND                       | GND              |

| _                          | MDI3                      | IN <sup>2</sup> | 47            | 48            | _            | GND                       | GND              |

| EPEE & BOEPEE <sup>3</sup> | VENDOR_IO1                | IN or<br>OUT    | 49            | 50            | _            | GND                       | GND              |

The Nexus specification labels active low signals with a forward slash (/) before the signal name.

The Nexus standard recommends that inputs should have 10K  $\Omega$  pull-up resistors to VREF (2.6 volts). Exception: The RSTI input should have a 10K  $\Omega$  pull-down resistor. This is in line with the proposed new standard.

This signal is needed only if control of EPEE or B0EPEE is required by the Nexus tool.

#### **Communication Ports**

On the MPC56x devices, some of the Nexus signals are shared with other pin functions. Table 1-7 shows the Nexus signal versus the MPC565/566 pins.

Table 1-7. MPC56x Signal Sharing

|                             |              | MPC565/566                  |             |  |  |  |

|-----------------------------|--------------|-----------------------------|-------------|--|--|--|

| ı                           | Nexus Signal | Signal                      | Ball        |  |  |  |

|                             | /RESET       | HRESET                      | AB23        |  |  |  |

|                             | /RSTI        | RSTI                        | M3          |  |  |  |

|                             | MCKI         | MCKI                        | L4          |  |  |  |

| ort                         | /MSEI        | MSEI                        | M4          |  |  |  |

|                             | MDI0         | MDI[0]                      | L1          |  |  |  |

| Aux In Port                 | MDI1         | MDI[1]                      | L3          |  |  |  |

| Aux                         | MDI2         | _1                          | =           |  |  |  |

|                             | MDI3         | _1                          | _           |  |  |  |

|                             | /EVTI        | EVTI                        | M2          |  |  |  |

|                             | мско         | мско                        | P3          |  |  |  |

|                             | /MSEO        | MSEO                        | T2          |  |  |  |

|                             | MDO0         | MDO[0]                      | P4          |  |  |  |

|                             | MDO1         | MDO[1]                      | R1          |  |  |  |

|                             | MDO2         | MDO[2]                      | R3          |  |  |  |

| ort                         | MDO3         | MDO[3]                      | T1          |  |  |  |

| Aux Out Port                | MDO4         | MDO[4]/<br>MPIO32B[10]      | N2          |  |  |  |

| An                          | MDO5         | MDO[5]/<br>MPIO32B[9]       | N4          |  |  |  |

|                             | MDO6         | MDO[6]/<br>MPIO32B[8]       | N3          |  |  |  |

|                             | MDO7         | MDO[7]/<br>MPIO32B[7]       | P1          |  |  |  |

|                             | /EVTO        | BG/VF0/LWP1                 | AF14        |  |  |  |

| Port                        | PORT0        | _1                          | _           |  |  |  |

|                             | VENDOR_IO0   | SGPIOC[7]/<br>IRQOUT/LWP[0] | AC14        |  |  |  |

| Tool Defined Vendor Defined | VENDOR_IO1   | EPEE & B0EPEE <sup>2</sup>  | AF21 & AD20 |  |  |  |

| peu                         | TOOL_IO0     | _3                          | _           |  |  |  |

| Defi                        | TOOL_IO1     | -                           | _           |  |  |  |

| <u> </u>                    | TOOL_102     | -                           | -           |  |  |  |

|                             | VREF         | VDD2.6                      | VDD         |  |  |  |

|                             | VALTREF      | VSTBY2.6                    | _4          |  |  |  |

**Connectors and User Components**

- This optional signal is not available on the MPC56x devices.

- This signal is needed only if control of EPEE or B0EPEE is required by the Nexus tool.

- 3 This optional signal is defined for use by tool vendors and has no defined connection to the MPC56x device.

- <sup>4</sup> This signal depends on the following system requirements: KAPWR (Y26), VDDSRAM1 (E3), VDDSRAM2 (D2), or VDDSRAM3 (G4). This pin should be connected to the standby supply used in a particular system.

## 1.5 Connectors and User Components

## 1.5.1 Keypad<sup>1</sup>

The Keypad port provides MPC566 I/O connections for a passive 16 key 4x4 matrix keypad (Axiom HC-KP). The port is applied as 4 column drivers and 4 row inputs. The MPC566 QADC B Ports PQA[4:7] are column outputs and PQB[4:7] are row inputs. The row inputs have 10K ohm pull-down resistance applied to idle the row inputs low. A simple keypad scan will enable each column output high one at a time and test the input rows for a high input. Column and row position can then determine the value of the key pressed. Sample software for driving the Keypad Port is provided on the MPC5xx support CD.

Table 1-8. Keypad

| PIN | MPC566 I/O SIGNAL |

|-----|-------------------|

| 1   | QADC_B PQA4 out   |

| 2   | QADC_B PQA5 out   |

| 3   | QADC_B PQA6 out   |

| 4   | QADC_B PQA7 out   |

| 5   | QADC_B PQB4 in    |

| 6   | QADC_B PQB5 in    |

| 7   | QADC_B PQB6 in    |

| 8   | QADC_B PQB7 in    |

## 1.5.2 LCD Port

The LCD Port provides a versatile connector to attach 80 or 160 character display modules and some graphics display modules with embedded controllers. Most LCD modules operate very

<sup>&</sup>lt;sup>1</sup>The MPC535/6 has limited or no functionality for this module. See Appendix A

#### Connectors and User Components

slowly compared to the MPC566 bus operation speeds so the LCD port provides a 16 bit wide register port for access. The registered port allows writing the LCD module control signals and full Read and Write capability for LCD module command and data bytes without the CPU waiting for LCD access time. LCD Port access are performed as a 3 or 4 bus cycle transaction as follows:

Access cycle 1: Write LCD control bits RS, R/W, LCD data byte. LCD1 and 2 select bits = 0.

Access cycle 2: Write LCD control bits LCD1 select, LCD2 select active as required. RS, R/W, LCD data byte values do not change but must be written again.

Access cycle 3 = READ: Read LCD Port if a Read access type, determined by R/W = 1 in first access cycles.

Access cycle 3 = WRITE: Write LCD control bits LCD1 select, LCD2 select idle. RS, R/W, LCD data byte do not change but must be written again. This terminates a Write access sequence.

Access cycle 4 = READ end: Write LCD control bits LCD1 select, LCD2 select idle, RS, R/W bits do not change but must be written again. This terminates a Read access sequence.

Table 1-9. LCD PORT REGISTER Definition (MPC500 core register aligned)

| BIT#     | FUNCTION                                                                                    |

|----------|---------------------------------------------------------------------------------------------|

| D0       | LCD1 select, 80 character or first 80 characters of 160 character module select. 1 = Active |

| D1       | LCD2 select, second 80 characters of 160 character module select. 1 = Active                |

| D2 – D5  | N/A, not applied                                                                            |

| D6       | LCD RS or Register Select. 0 = Command, 1 = Display Data access                             |

| D7       | LCD Read / Write select. 0 = Write, 1 = Read access                                         |

| D8 > D15 | LCD Data Byte D7 > D0, Write output to LCD if D7 = 0, Read input if D7 = 1.                 |

See LCD Module data sheet for command codes

Example source code for the LCD and Keypad drivers are provided on the Axiom MPC5xx support CD. The LCD Port is assigned on chip select CS3 if enabled with MAP Switch position 6. Memory map offset for the LCD Port = CS3 base + 0x0010.

### LCD Display CONTRAST

The CONTRAST adjustment allows a contrast Vee voltage to be presented to the LCD\_PORT of -5V to +5V DC.

### JP2 - LCD PORT Power Polarity Select

JP2 determines the display power pin polarity on the LCD\_PORT. Depending on the type and location of the IDC connector on your display module, the power connections may need to be reversed. Care should be used to verify proper connection and signal matching at the IDC Cable Connector and LCD\_PORT.

See the schematic to match this jumper setting to your LCD device connector. Contact support@axman.com for assistance applying a LCD module.

**Connectors and User Components**

|    | Typical JP2 positions for 80 character or smaller LCD | <ol><li>Rotate 90 degrees for 160</li></ol> |

|----|-------------------------------------------------------|---------------------------------------------|

| ĻU | character type modules.                               |                                             |

**USE CAUTION** when connecting your LCD to the LCD-PORT - make sure the power polarity (JP2) and correct placement of the LCD cable so that signals are correctly matched.

## 1.5.3 User Components

The EVB provides a set of user components that maybe applied in user applications or for testing purposes. The components are interfaced via the J2 Socket Header and are not dedicated to any particular MPC566 I/O signal. Provided are 4 push button switches (SW1 - 4), 4 LED Indicators (LED1 - 4), and the user POT (RV1). Following are J2 connections and interface notes:

J2 PIN COMPONENT NOTES SW1 1 Active Low, also drives BRK EN option 2 SW2 Active high, +5V 3 SW3 Active high, +5V 4 SW4 Active high, +5V 5 LED1 Active High LED2 6 Active High 7 LED3 Active High 8 LED4 Active High 9 RV1 - Center Tap 0 - 5V10 +5V, open O4 option to change RV1 +Input or reference Ground, open O5 option to change 11 RV1 -Input or reference 12 GROUND Meter or probe ground / common

Table 1-10. J2 User Component I/O

### **BRK EN Option**

The BRK\_EN or Break Enable option is provided to allow an IRQ0 NMI interrupt to occur on SW1 being pressed. This feature is provided to support the Monitor ABORT operation to stop user code execution and return to the Monitor command prompt. When the option jumper is installed, depressing SW1 will cause a low active level to be applied to the MPC566 IRQ0.

**Connectors and User Components**

## 1.5.4 MPC566EVB Hardware Options

### XFC Filter Capacitor C5

Capacitor C5 provides the XFC filtering for the PLL circuits. The capacitor may be changed by the user if PLL locking problems are experienced at the frequency of operation selected or if the reference crystal is replaced. Current value is 3.3nF.

### VRH and VRL QADC Reference Supplies

EVB zero ohm resistors R4 and R5 provide connection to MPC566 VDDA and VSSA for VRH and VRL reference signals respectfully. One or both of these resistors can be removed to apply an external reference voltage to the QADC\_A Port.

#### **EPEE and BOEPEE CUTAWAY E0**

The MPC566EVB board has the EPEE and BOEPEE signals connected by CUT\_AWAY pad E0. This connection is for NEXUS port programming of the MPC566 internal flash. This connection will cause the CONFIG\_SW position 7 or 8 to enable both signals. If this operation is not desired by the user, cut the CUT-AWAY E0 pad to isolate the signals from each other.

## 1.5.5 Signals Available on Board

### 1.5.5.1 IRQ PORT

The IRQ Port provides access to the MPC566 Port C I/O or IRQ inputs on a 10 pin socket header.

| SIGNAL                  | PIN | PIN | SIGNAL                 |

|-------------------------|-----|-----|------------------------|

| IRQOUT / SGPI07         | 10  | 9   | FRZ / SGPIO6           |

| IRQ7                    | 8   | 7   | IRQ6                   |

| IRQ5 / SGPIO5           | 6   | 5   | IRQ4 / SGPIO4          |

| IRQ3 / SGPIO3           | 4   | 3   | IRQ2 / SGPIO2          |

| IRQ1 / SGPIO1 (IRQ_100) | 2   | 1   | IRQ0 / SGPIO0 (BRK_EN) |

## 1.5.5.2 BUS\_PORT

The BUS Port provides the data and address line access to the MPC566 memory bus on a 60 pin header.

#### **BUS PORT**

| SIGNAL | PIN | PIN | SIGNAL |

|--------|-----|-----|--------|

| GND    | 60  | 59  | +2.6V  |

| A31    | 58  | 57  | A30    |

| A29    | 56  | 55  | A28    |

### **Connectors and User Components**

### **BUS PORT** (Continued)

| SIGNAL | PIN | PIN | SIGNAL |

|--------|-----|-----|--------|

| A27    | 54  | 53  | A26    |

| A25    | 52  | 51  | A24    |

| A23    | 50  | 49  | A22    |

| A21    | 48  | 47  | A20    |

| A19    | 46  | 45  | A18    |

| A17    | 44  | 43  | A16    |

| A15    | 42  | 41  | A14    |

| A13    | 40  | 39  | A12    |

| A11    | 38  | 37  | A10    |

| A9     | 36  | 35  | A8     |

| D31    | 34  | 33  | D30    |

| D29    | 32  | 31  | D28    |

| D27    | 30  | 29  | D26    |

| D25    | 28  | 27  | D24    |

| D23    | 26  | 25  | D22    |

| D21    | 24  | 23  | D20    |

| D19    | 22  | 21  | D18    |

| D17    | 20  | 19  | D16    |

| D15    | 18  | 17  | D14    |

| D13    | 16  | 15  | D12    |

| D11    | 14  | 13  | D10    |

| D9     | 12  | 11  | D8     |

| D7     | 10  | 9   | D6     |

| D5     | 8   | 7   | D4     |

| D3     | 6   | 5   | D2     |

| D1     | 4   | 3   | D0     |

| GND    | 2   | 1   | 2.6V   |

**Connectors and User Components**

## 1.5.5.3 TPU\_PORTs1

The TPU (Timing Processor Unit) Ports provide access to the MPC566 TPU A, B and C channels on 3 identical socket headers, TPU PORT A, TPU PORT B and TPU PORT C.

### **TPU PORT**

| SIGNAL   | PIN | PIN | SIGNAL   |

|----------|-----|-----|----------|

| GND      | 20  | 19  | GND      |

| +5V      | 18  | 17  | T2CLK    |

| TPU CH15 | 16  | 15  | TPU CH14 |

| TPU CH13 | 14  | 13  | TPU CH12 |

| TPU CH11 | 12  | 11  | TPU CH10 |

| TPU CH9  | 10  | 9   | TPU CH8  |

| TPU CH7  | 8   | 7   | TPU CH6  |