### Bus Analyzer and Exerciser

Limited Availability

Used and in Excellent Condition

**Open Web Page**

https://www.artisantg.com/80882-7

., ...

Critical and expedited services

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- We buy your excess, underutilized, and idle equipment

- In stock / Ready-to-ship

Full-service, independent repair center

ARTISAN'

TECHNOLOGY GROUP

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

## VANGUARD User Guide

PCI/PCI-X Bus Analyzer & Exerciser

For BusView® 5 October 24, 2007

#### **Notice**

The information in this document is subject to change without notice and should not be construed as a commitment by VMETRO. While reasonable precautions have been taken, VMETRO assumes no responsibility for any errors that may appear in this document.

#### **Trademarks**

Trademarked names appear throughout this document. Rather than list the names and entities that own the trademarks or insert a trademark symbol with each mention of the trademarked name, we hereby state that the names are used only for editorial purposes and to the benefit of the trademark owner with no intention of improperly using the trademark.

The mention of any trademarked name is not intended to imply that VMETRO products are affiliated, endorsed or sponsored by such trademark owner.

#### **Software and Firmware Licensing**

Any Software and Firmware code provided by VMETRO described herein is proprietary to VMETRO or its licensors. The use of this Software and Firmware is governed by a licensing agreement included on the media on which the Software and Firmware was supplied. Use of the Software or Firmware assumes that the user has agreed to the terms of the licensing agreement. VMETRO retains all rights to the Software and Firmware under the copyright laws of the United States of America and other countries. This Software or Firmware may not in contravention of the licensing agreement be furnished or disclosed to any third party and may not be copied or reproduced by any means, electronic, mechanical, or otherwise, in whole or in part, without specific authorization in writing from VMETRO.

#### Copyright © 2007 VMETRO

This document may not be furnished or disclosed to any third party and may not be copied or reproduced in any form, electronic, mechanical, or otherwise, in whole or in part, without the prior written consent of VMETRO.

#### Warranty

VMETRO products are warranted against defective materials and workmanship within the warranty period of 1 (one) year from date of invoice. Within the warranty period, VMETRO will, free of charge, repair or replace any defective unit covered by this warranty. A Return to Manufacturer Authorization (RMA) number should be obtained from VMETRO prior to return of any defective product. With any returned product, a written description of the nature of malfunction should be enclosed. The product must be shipped in its original shipping container or similar packaging with sufficient mechanical and electrical protection in order to maintain warranty. The product should be returned at the user's expense (including insurance for the full product value). This warranty assumes normal use. Products subjected to unreasonably rough handling, negligence, abnormal voltages, abrasion, unauthorized parts replacement and repairs, or theft are not covered by this warranty and will if possible be repaired for time and material charges in effect at the time of repair. Any customer modification to VMETRO products, including conformal coating, voids the warranty unless agreed to in writing by VMETRO.

If boards that have been modified are returned for repair, this modification should be removed prior to the board being shipped back to VMETRO for the best possibility of repair. Boards received without the modification removed will be reviewed for reparability. If it is determined that the board is not repairable, the board will be returned to the customer. All review and repair time will be billed to the customer at the current time and materials rates for repair actions.

This product has been designed to operate with modules, carriers or compatible user-provided equipment. Connection of incompatible hardware is likely to cause serious damage. VMETRO assumes no liability for any damages caused by such incompatibility. For products that have failed or malfunctioned due to abuse, miss-use or accident or for products that have failed or malfunctioned after the expiry of the warranty, the costs of repair or replacement will not be covered by VMETRO.

VMETRO specifically disclaims any implied warranty of merchantability and fitness for a particular purpose. The warranty provided herein for electronic equipment products is the user's sole and exclusive remedy. In no event shall VMETRO, or its distributors and agents, be liable for direct, indirect, special, incidental, or consequential damages (including but not limited to lost profits, penalties or damages payable to third parties) suffered or incurred, whether based on contract, tort or any other legal theory, even if VMETRO has been informed of the possibility of such damages. This limitation of liability may not be enforceable in certain jurisdictions; therefore the limitations may not apply. This warranty gives you specific rights. You may have other rights that vary from jurisdiction to jurisdiction.

VMETRO's warranty is limited to the repair or replacement policy described above and neither VMETRO nor its agent shall be responsible for consequential or special damages related to the use of their products.

#### **Limited Liability**

VMETRO does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights nor the rights of others. VMETRO products are not designed, intended, or authorized for use as components in systems intended to support or sustain life, or for any application in which failure of the VMETRO product could create a situation where personal injury or death may occur. Should Buyer purchase or use VMETRO products for any such unintended or unauthorized application, Buyer shall indemnify and hold VMETRO and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that VMETRO was negligent regarding the design or manufacture of the part.

#### **Contact Us**

#### Worldwide HQ

VMETRO asa Østensjøveien 32 0667 OSLO, Norway Phone: +47 22 10 60 90 Fax: +47 22 10 62 02 info@vmetro.no

#### **United Kingdom**

VMETRO Ltd Manor Courtyard Hughenden Avenue High Wycombe HP13 5RE United Kingdom Phone: +44 (0) 1494 476000 Fax: +44 (0) 1494 464472 sales@vmetro.co.uk

#### North American HQ

VMETRO, Inc. 1880 Dairy Ashford, Suite 400, Houston TX 77077, U.S.A. Phone: (281) 584-0728 Fax: (281) 584-9034 info@vmetro.com

#### VMETRO, Inc.

Suite 275 171 E. State St, Box 120 Ithaca, New York 14850 Phone: (607) 272 5494 Fax: (607) 272 5498 info@ymetro.com

#### **Asia Pacific**

VMETRO Pte Ltd 175A Bencoolen Street #06-09 Burlington Square Singapore 189650 Phone: +65 6238 6010 Fax: +65 6238 6020 info@vmetro.com.sg

#### **Nordic & Baltic Countries**

VSYSTEMS AB

Drottninggatan 104

SE-111 60 Stockholm

Contact: Bengt-Olof Larsson

Phone: +46 8 444 15 50

Fax: +46 8 444 15 60

info@vsystems.se

#### Germany

VSYSTEMS Electronic GmbH Elisabethstrasse 30 80796 München Contact: Ralf Streicher Phone: +49 89 273 763 0 Fax: +49 89 273 763 10 info@vsystems.de

#### France

VSYSTEMS SAS

P.A. du Pas du Lac

5, rue Michaël Faraday

78180 Montigny-le-Bretonneux

Contact: Alain D'Aux

Phone: +33 1 30 07 00 60

Fax: +33 1 30 07 00 69

info@vsystems.fr

#### Italy

VSYSTEMS srl via Cavour 123 10091 Alpignano (TO) Contact: Luca Ravera Phone: +39 11 9661319 Fax: +39 11 9662368 info@vsystems.it

www.vmetro.com

## Preface

This User Guide explains the process of preparing, installing, and using your Vanguard. It is divided into the following sections:

- Product Overview

- Hardware Description

- Getting Started with BusView®

- State Analyzer

- Statistics Functions

- Protocol Checker

- Exerciser

- Simulator

- Compliance Checker

- · Zero Slot Adapter

- Appendixes: Specifications, Signals, Embedded Systems.

#### **Style Conventions Used**

- Code samples are Courier font and at least one size less than context.

- Directory path names are *italicized*.

- File names are in **bold**.

- Absolute path file names are *italicized and in bold*.

**Warning!** Information contained in this box must be observed. It will provide information about situations that may be dangerous.

**Note** – Information contained in this box is important and will help you get the best performance from your Vanguard.

#### **Symbols**

Tip – This information offers guidance in using your Vanguard for certain situations.

#### **Quality Assurance**

VMETRO is dedicated to supplying our customers with products and services of the highest quality.

We therefore, continually review and assess our products and services with the aim to improve the processes involved in the development of our world-class products.

If you have any comments or feedback with respect to our products and services, please feel free to contact us through the support channels listed here, or E-mail us at analyzercomments@vmetro.com

#### **Technical Support**

Please see the section Technical Support at the end of this guide.

#### **Related Documentation**

Installation Guide

## **Contents**

| 1.1 Overview                                                                                                                                                                                                                                       | 2                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Vanguard                                                                                                                                                                                                                                           | 2                                      |

| The Tools                                                                                                                                                                                                                                          |                                        |

| The Hardware                                                                                                                                                                                                                                       |                                        |

| The Software - BusView®                                                                                                                                                                                                                            |                                        |

| 1.2 Functional Overview                                                                                                                                                                                                                            |                                        |

| Analyzer                                                                                                                                                                                                                                           |                                        |

| Protocol Checker                                                                                                                                                                                                                                   |                                        |

| Statistics Functions                                                                                                                                                                                                                               |                                        |

| Exerciser (PCI & VME)                                                                                                                                                                                                                              |                                        |

| Host Exerciser                                                                                                                                                                                                                                     |                                        |

| Description                                                                                                                                                                                                                                        |                                        |

| •                                                                                                                                                                                                                                                  |                                        |

| 2.1 Vanguard PCI Assembly - PCI Carrier and SAM                                                                                                                                                                                                    | 10                                     |

| 2.1 Vanguard PCI Assembly - PCI Carrier and SAM                                                                                                                                                                                                    | 10                                     |

| 2.1 Vanguard PCI Assembly - PCI Carrier and SAM                                                                                                                                                                                                    |                                        |

| 2.1 Vanguard PCI Assembly - PCI Carrier and SAM                                                                                                                                                                                                    | 10<br>10<br>12                         |

| 2.1 Vanguard PCI Assembly - PCI Carrier and SAM  5V Adapter Card  2.2 Vanguard PMC Assembly  Vanguard PMC board                                                                                                                                    | 10<br>10<br>12<br>12                   |

| 2.1 Vanguard PCI Assembly - PCI Carrier and SAM  5V Adapter Card  2.2 Vanguard PMC Assembly  Vanguard PMC board  Top Spacer                                                                                                                        | 10<br>12<br>12<br>13                   |

| 2.1 Vanguard PCI Assembly - PCI Carrier and SAM  5V Adapter Card  2.2 Vanguard PMC Assembly  Vanguard PMC board  Top Spacer  2.3 Vanguard cPCI Assembly - cPCI Carrier and SAM                                                                     | 10<br>12<br>12<br>13<br>16             |

| 2.1 Vanguard PCI Assembly - PCI Carrier and SAM  5V Adapter Card  2.2 Vanguard PMC Assembly  Vanguard PMC board  Top Spacer  2.3 Vanguard cPCI Assembly - cPCI Carrier and SAM  System Slot functions                                              | 10<br>12<br>12<br>13<br>16<br>16       |

| 2.1 Vanguard PCI Assembly - PCI Carrier and SAM  5V Adapter Card  2.2 Vanguard PMC Assembly  Vanguard PMC board  Top Spacer  2.3 Vanguard cPCI Assembly - cPCI Carrier and SAM  System Slot functions  Hot Swap                                    | 10<br>12<br>13<br>16<br>16<br>17       |

| 2.1 Vanguard PCI Assembly - PCI Carrier and SAM  5V Adapter Card  2.2 Vanguard PMC Assembly  Vanguard PMC board  Top Spacer  2.3 Vanguard cPCI Assembly - cPCI Carrier and SAM  System Slot functions  Hot Swap  2.4 Zero Slot Adapter (VG-PCI0SL) | 10<br>12<br>13<br>16<br>16<br>17<br>18 |

|                   | Reset                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|                   | Ethernet Connector                                                                                                                                                                                                                                                                                                                                                               |                                                          |

|                   | LAN LEDs                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

|                   | Trigger Output                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

|                   | External I/O                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

|                   | Temperature Input                                                                                                                                                                                                                                                                                                                                                                |                                                          |

|                   | USB Mini-B port                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

|                   | 2.6 External Power.                                                                                                                                                                                                                                                                                                                                                              |                                                          |

|                   | 2.7 Miscellaneous Parts                                                                                                                                                                                                                                                                                                                                                          | 24                                                       |

|                   | External Temperature Probe                                                                                                                                                                                                                                                                                                                                                       |                                                          |

|                   | Patch Cords                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

|                   | 50Ω BNC Coax External Trigger Output cable                                                                                                                                                                                                                                                                                                                                       |                                                          |

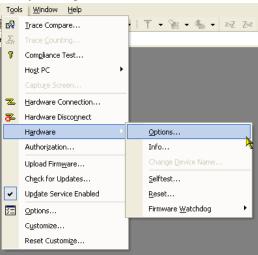

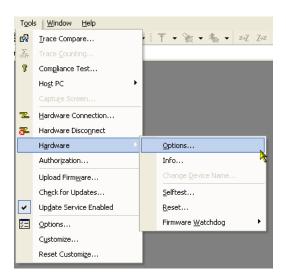

|                   | 2.8 Hardware Menu                                                                                                                                                                                                                                                                                                                                                                | 25                                                       |

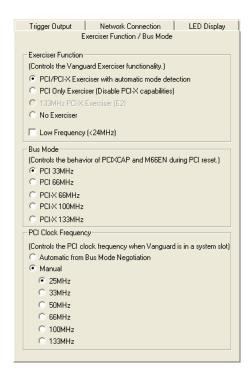

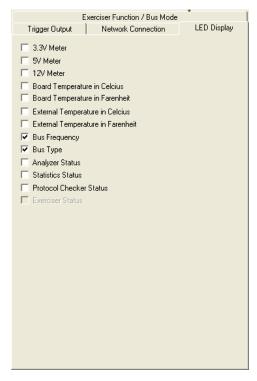

|                   | Options                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

|                   | Hardware Info                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

|                   | Change Device Name                                                                                                                                                                                                                                                                                                                                                               | 31                                                       |

|                   | Selftest                                                                                                                                                                                                                                                                                                                                                                         | 31                                                       |

|                   | Reset                                                                                                                                                                                                                                                                                                                                                                            | 31                                                       |

|                   | Firmware Watchdog                                                                                                                                                                                                                                                                                                                                                                | 31                                                       |

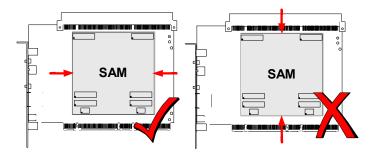

|                   | 2.9 Moving the SAM                                                                                                                                                                                                                                                                                                                                                               | 32                                                       |

|                   | Removing a SAM                                                                                                                                                                                                                                                                                                                                                                   | 32                                                       |

|                   | Installing a SAM                                                                                                                                                                                                                                                                                                                                                                 | 33                                                       |

|                   |                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

| 3 Getting Started | d with BusView®                                                                                                                                                                                                                                                                                                                                                                  | 35                                                       |

| 3 Getting Started | d with BusView®                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

| 3 Getting Started |                                                                                                                                                                                                                                                                                                                                                                                  | 36                                                       |

| 3 Getting Started | 3.1 Starting BusView®                                                                                                                                                                                                                                                                                                                                                            | 36                                                       |

| 3 Getting Started | 3.1 Starting BusView®                                                                                                                                                                                                                                                                                                                                                            | 36<br>36                                                 |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems                                                                                                                                                                                                                                                                                                         | 36<br>36<br>37                                           |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems.  Using a fixed IP address                                                                                                                                                                                                                                                                              | 36<br>36<br>37                                           |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting .  Connection Problems .  Using a fixed IP address  Connecting through a Firewall                                                                                                                                                                                                                                            | 36<br>36<br>37<br>37<br>38                               |

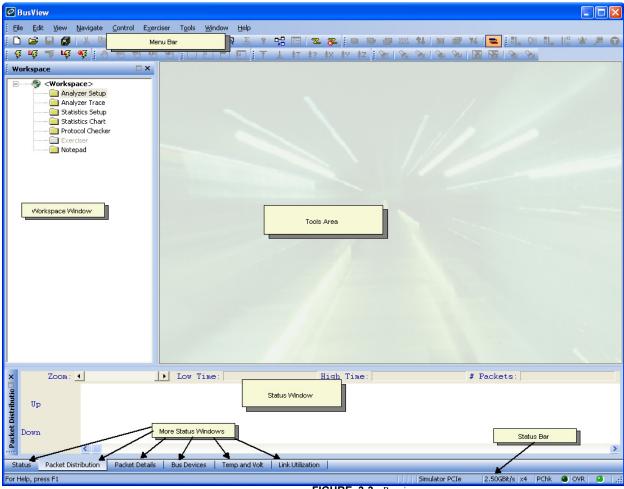

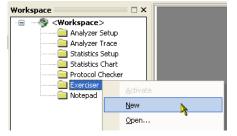

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems.  Using a fixed IP address  Connecting through a Firewall  Device Information dialog.  3.2 Window Elements  Workspace Window                                                                                                                                                                            | 36<br>36<br>37<br>37<br>38<br>40                         |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems.  Using a fixed IP address  Connecting through a Firewall  Device Information dialog  3.2 Window Elements  Workspace Window  Status Window                                                                                                                                                              | 36<br>36<br>37<br>37<br>38<br>40<br>40                   |

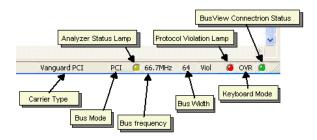

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems  Using a fixed IP address  Connecting through a Firewall  Device Information dialog  3.2 Window Elements  Workspace Window  Status Window  Status bar                                                                                                                                                   | 36<br>36<br>37<br>37<br>38<br>40<br>40<br>42<br>43       |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems.  Using a fixed IP address  Connecting through a Firewall  Device Information dialog.  3.2 Window Elements  Workspace Window  Status Window  Status Window  Status bar  Tools Area                                                                                                                      | 36<br>36<br>37<br>38<br>40<br>40<br>42<br>43<br>44       |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting Connection Problems.  Using a fixed IP address Connecting through a Firewall Device Information dialog.  3.2 Window Elements Workspace Window Status Window Status Window Status bar Tools Area Menus bar                                                                                                                    | 36<br>36<br>37<br>37<br>38<br>40<br>40<br>42<br>43<br>44 |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting Connection Problems. Using a fixed IP address Connecting through a Firewall Device Information dialog 3.2 Window Elements Workspace Window Status Window Status bar Tools Area Menus bar 3.3 Controls                                                                                                                        | 36<br>36<br>37<br>37<br>38<br>40<br>42<br>43<br>44<br>44 |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems.  Using a fixed IP address  Connecting through a Firewall  Device Information dialog  3.2 Window Elements  Workspace Window  Status Window  Status bar  Tools Area  Menus bar  3.3 Controls  Mouse Control                                                                                              | 36 36 37 37 38 40 42 43 44 45                            |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems.  Using a fixed IP address  Connecting through a Firewall  Device Information dialog.  3.2 Window Elements  Workspace Window  Status Window  Status Window  Status bar  Tools Area  Menus bar  3.3 Controls  Mouse Control  Keyboard Control.                                                           | 36 36 37 38 40 40 42 43 44 45 45 45                      |

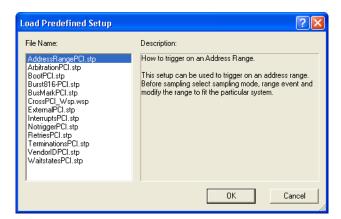

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems.  Using a fixed IP address  Connecting through a Firewall  Device Information dialog  3.2 Window Elements  Workspace Window  Status Window  Status bar  Tools Area  Menus bar  3.3 Controls  Mouse Control  Keyboard Control.  3.4 Predefined Setups                                                    | 36 36 37 37 38 40 42 43 44 45 45 45                      |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems.  Using a fixed IP address  Connecting through a Firewall  Device Information dialog.  3.2 Window Elements  Workspace Window  Status Window  Status Window  Status bar  Tools Area  Menus bar  3.3 Controls  Mouse Control  Keyboard Control.  3.4 Predefined Setups  3.5 Templates                     | 36 36 37 38 40 42 43 44 45 45 45 45 45                   |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems.  Using a fixed IP address  Connecting through a Firewall  Device Information dialog  3.2 Window Elements  Workspace Window  Status Window  Status bar  Tools Area  Menus bar  3.3 Controls  Mouse Control  Keyboard Control.  3.4 Predefined Setups                                                    | 36 36 37 38 40 42 43 44 45 45 45 45 45                   |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting  Connection Problems.  Using a fixed IP address  Connecting through a Firewall  Device Information dialog.  3.2 Window Elements  Workspace Window  Status Window  Status Window  Status bar  Tools Area  Menus bar  3.3 Controls  Mouse Control  Keyboard Control.  3.4 Predefined Setups  3.5 Templates                     | 36 36 37 37 38 40 42 43 44 45 45 45 45 45 45             |

| 3 Getting Started | 3.1 Starting BusView®  Disconnecting / Reconnecting Connection Problems.  Using a fixed IP address Connecting through a Firewall Device Information dialog.  3.2 Window Elements Workspace Window Status Window Status Window Status bar Tools Area Menus bar  3.3 Controls Mouse Control Keyboard Control.  3.4 Predefined Setups  3.5 Templates  3.6 Multiple BusView Sessions | 36 36 37 37 38 40 42 43 44 45 45 45 45 45 45             |

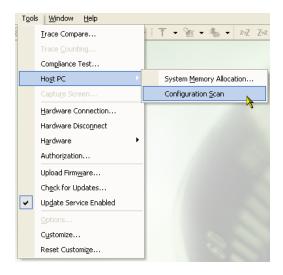

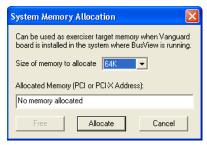

|                | System Memory Allocation                      | 51   |

|----------------|-----------------------------------------------|------|

|                | Configuration Scan                            | 52   |

|                |                                               |      |

| 1 0 1          |                                               |      |

| State Analyzer |                                               | . 53 |

|                | 4.1 Introduction                              | 54   |

|                | Sampling                                      | 55   |

|                | Trigger Conditions                            | 56   |

|                | Trace Display                                 | 57   |

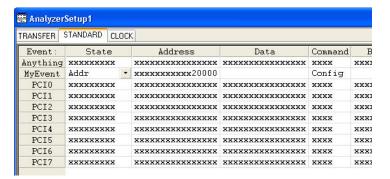

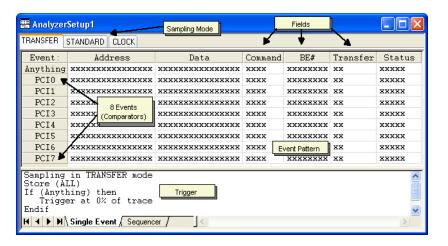

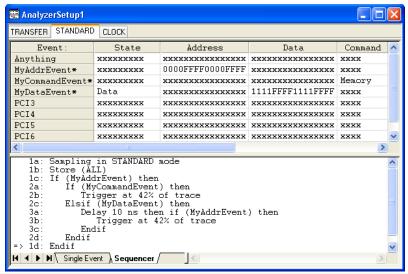

|                | 4.2 Analyzer Setup Window                     | 60   |

|                | Window Layout                                 | 60   |

|                | Analyzer Setup Options                        | 61   |

|                | 4.3 Sampling Modes                            | 66   |

|                | Overview                                      | 66   |

|                | Clock Mode (Multiplexed)                      | 66   |

|                | Standard Mode (Demultiplexed)                 | 66   |

|                | Transfer Mode (Demultiplexed)                 | 67   |

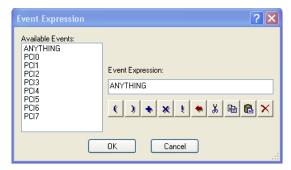

|                | 4.4 Event Patterns                            | 68   |

|                | Single Event Mode                             | 68   |

|                | Events                                        | 68   |

|                | Patterns                                      | 69   |

|                | Editing Event Patterns                        | 69   |

|                | PLP Training Sequence                         |      |

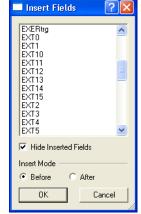

|                | Manipulating Field Columns                    | 70   |

|                | Field Properties                              |      |

|                | Manipulating Events                           | 73   |

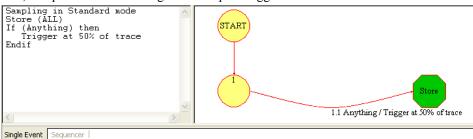

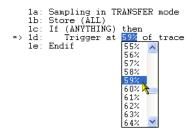

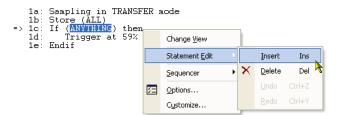

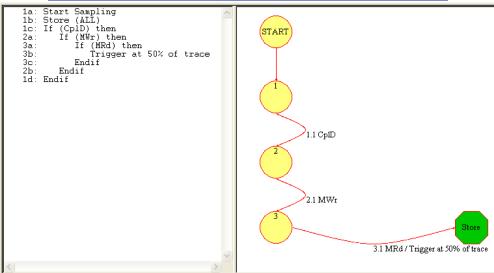

|                | 4.5 The Sequencer                             | 75   |

|                | Notation                                      | 75   |

|                | Syntax                                        |      |

|                | Operators                                     |      |

|                | Using the sequencer                           |      |

|                | Graphical View                                |      |

|                | Sequencer Example                             |      |

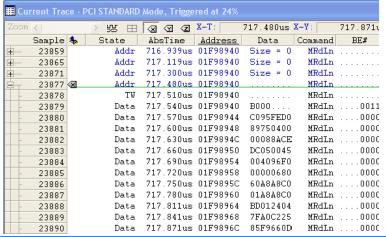

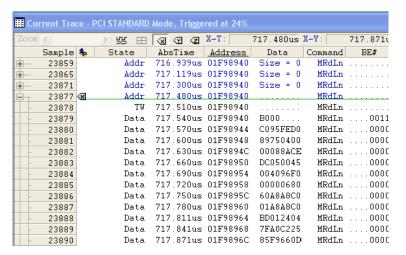

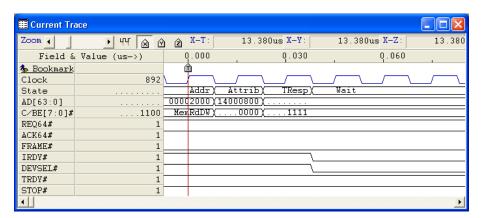

|                | 4.6 Trace Display                             |      |

|                | Editing the Trace window                      |      |

|                | Navigating the Trace Buffer                   |      |

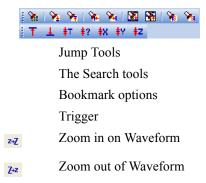

|                | Jump Tools                                    |      |

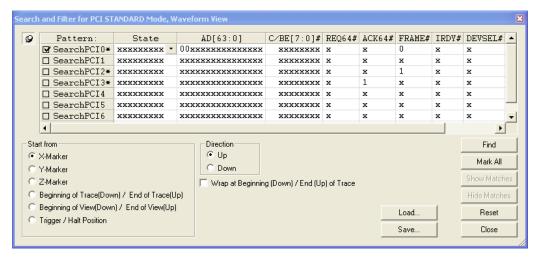

|                | The Search tools                              |      |

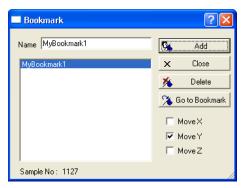

|                | Bookmarks                                     |      |

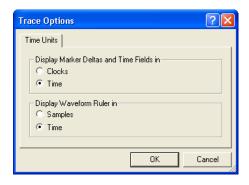

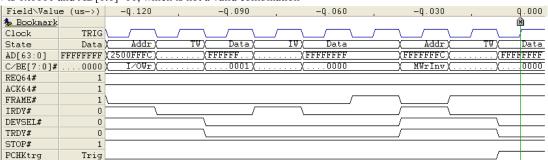

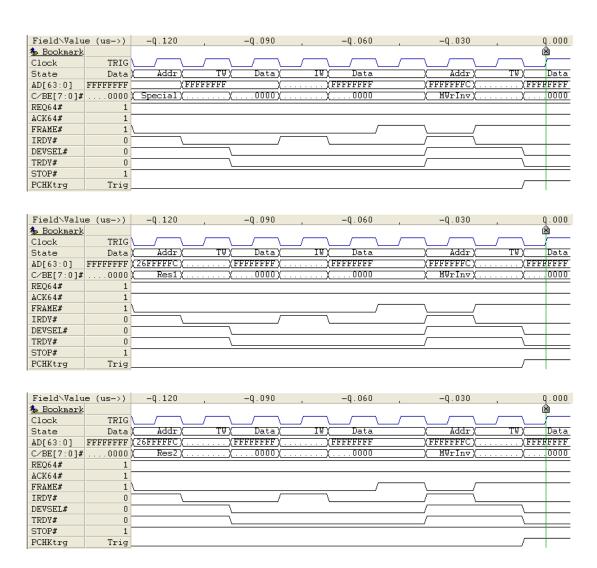

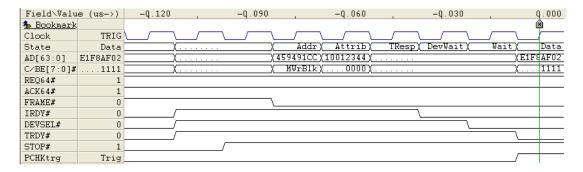

|                | 4.7 Alphanumeric Trace Display                |      |

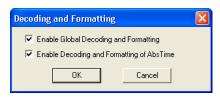

|                | Changing the Alphanumeric Formatting Template |      |

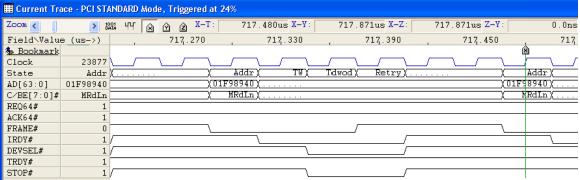

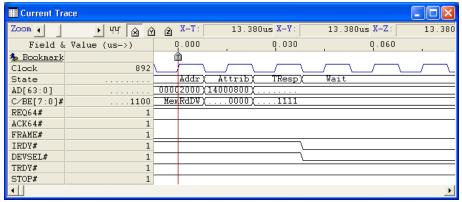

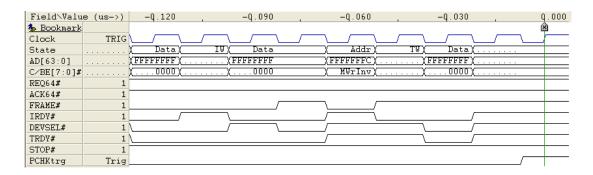

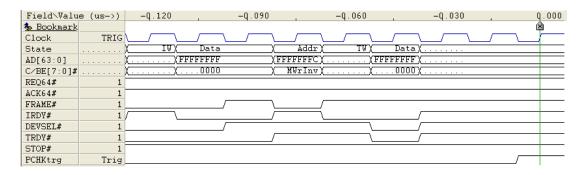

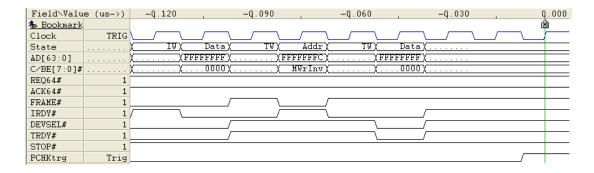

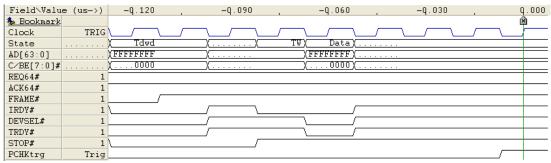

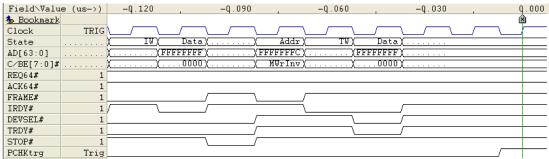

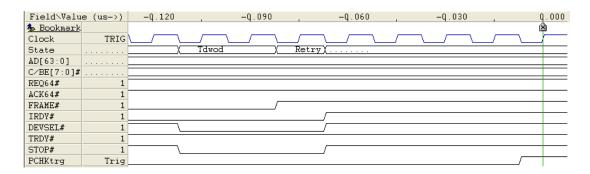

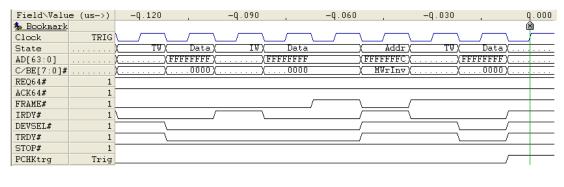

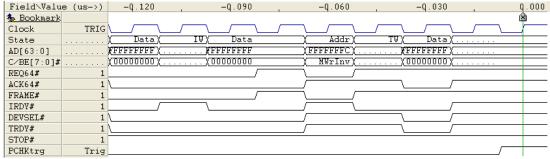

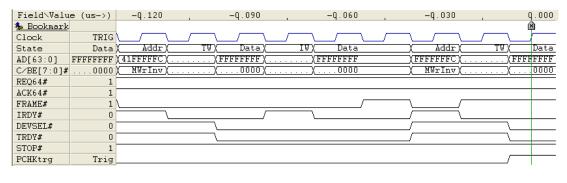

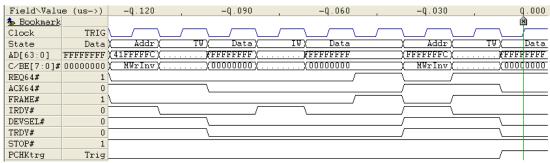

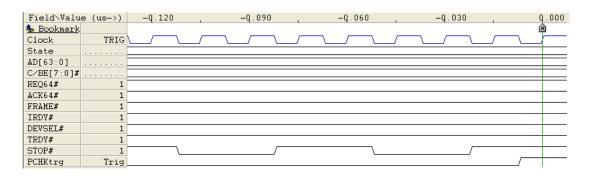

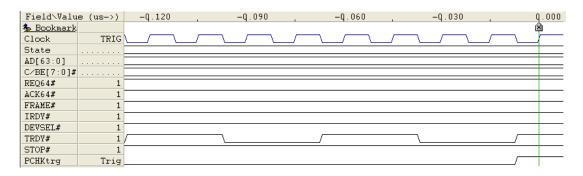

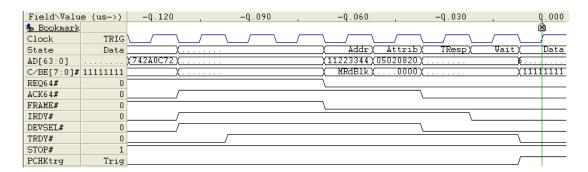

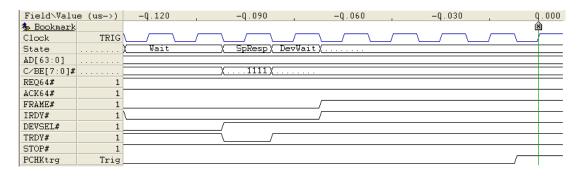

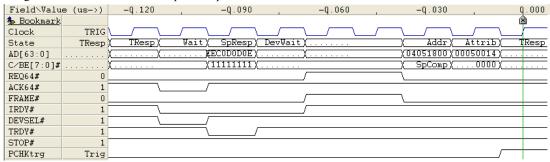

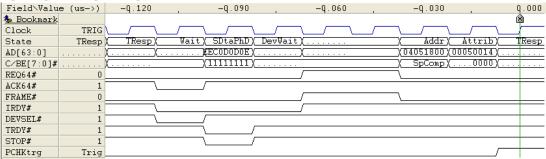

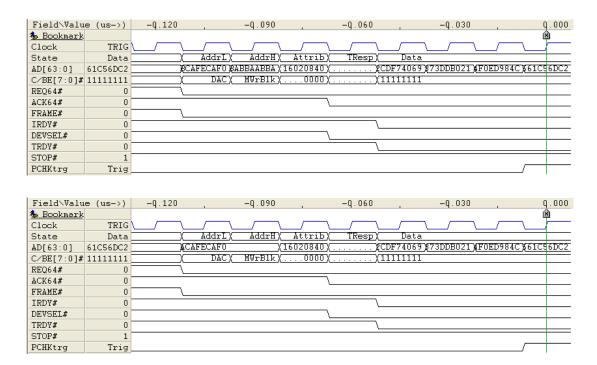

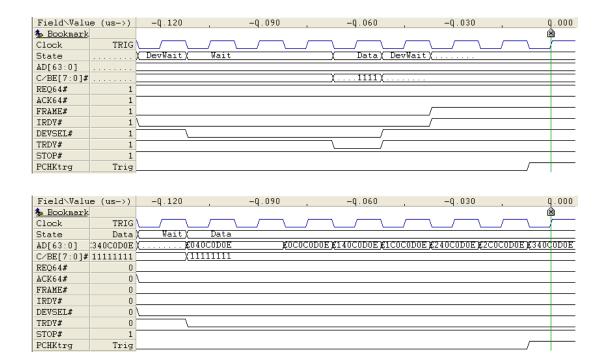

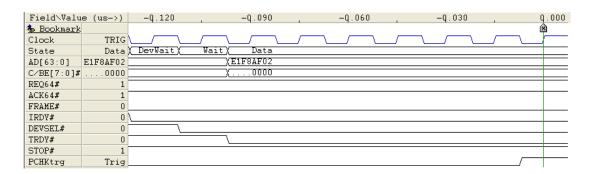

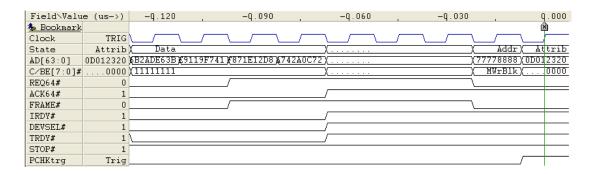

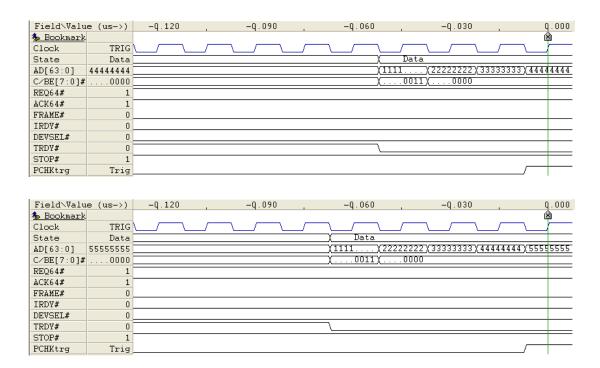

|                | 4.8 Waveform Trace Display                    |      |

|                | Navigating the Trace Buffer in Waveform Mode  |      |

|                | Mouse and keyboard                            |      |

|                | Jump tools                                    |      |

|                | 4.9 Trace Handling                            |      |

|                | Trace Files                                   |      |

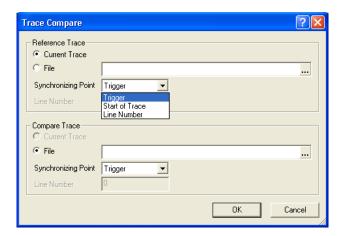

|                | <i>Trace Compare</i>                          | 94   |

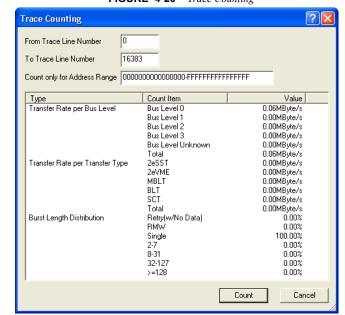

|                | Trace Counting                                  | 97  |

|----------------|-------------------------------------------------|-----|

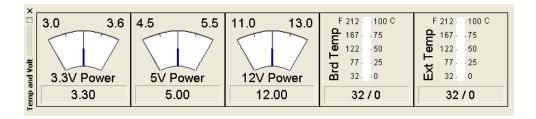

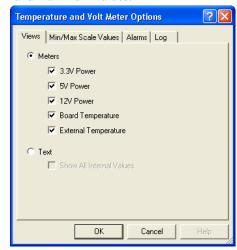

|                | 4.10 Voltage and Temperature Meters             | 98  |

|                | Temperature and Volt Meter Options              |     |

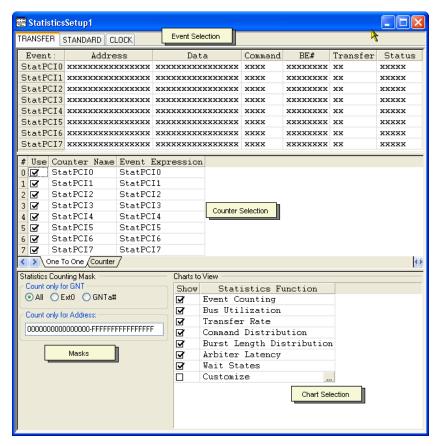

| 5 Statistics F | Functions                                       | 99  |

|                |                                                 |     |

|                | 5.1 Introduction                                |     |

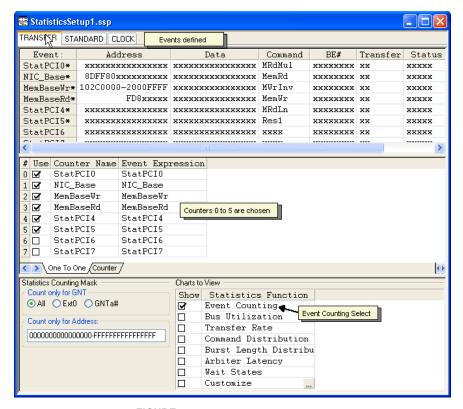

|                | Statistics Setup Window                         |     |

|                | Statistics Setup Options                        |     |

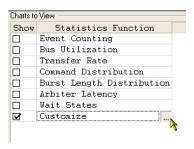

|                | 5.2 Pre-defined Statistics                      |     |

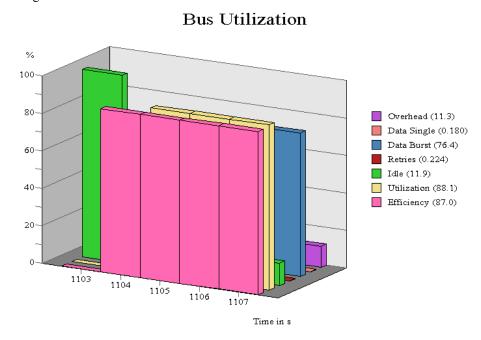

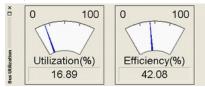

|                | Bus Utilization                                 |     |

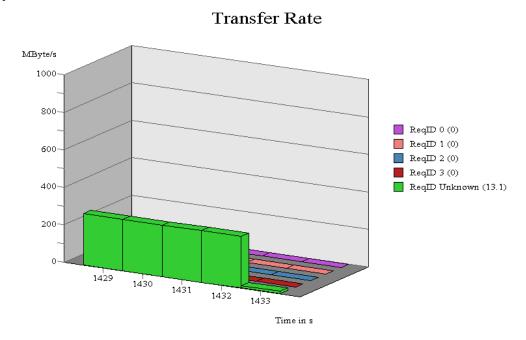

|                | Transfer Rate                                   |     |

|                | Command Distribution.                           |     |

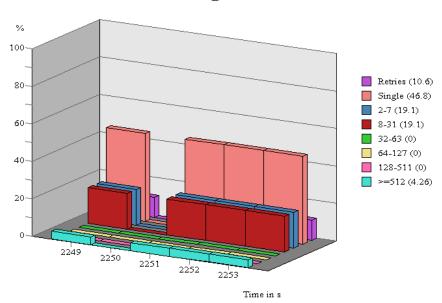

|                | Burst Length Distribution                       |     |

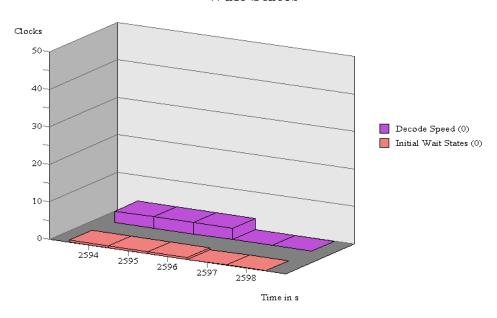

|                | Wait States                                     |     |

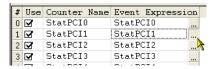

|                | 5.3 User-defined Statistics                     | 112 |

|                | Event Counting                                  |     |

|                | Customized Charts                               |     |

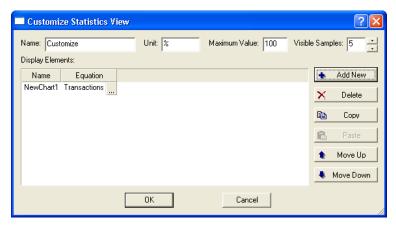

|                | Adding, Deleting and Renaming Customized Charts |     |

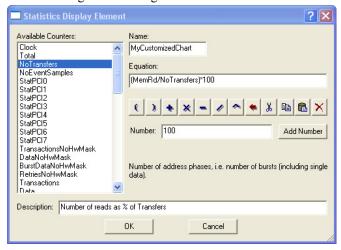

|                | Editing a Customized Chart                      | 116 |

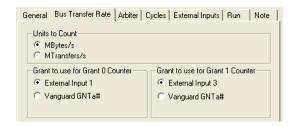

|                | 5.4 Hardware Counters                           |     |

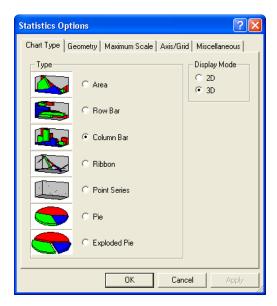

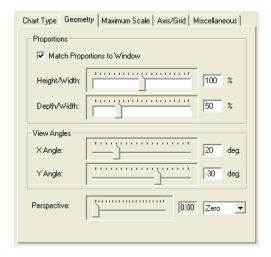

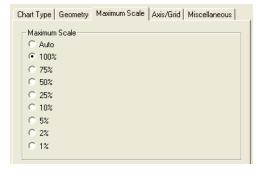

|                | 5.5 Statistics Charts                           | 120 |

|                | 5.6 Statistics Files                            | 123 |

|                | Statistics Setup Files                          |     |

|                | Statistics Setup Options dialog                 |     |

|                | Statistics Chart File                           |     |

| 6 Protocol C   | Checker                                         | 127 |

|                | 6.1 Introduction                                | 128 |

|                | Verification of Detected violations             |     |

|                | 6.2 Features                                    | 120 |

|                |                                                 |     |

|                | 6.3 Operation                                   |     |

|                | Using the Protocol Checker                      |     |

|                | Protocol Checker Output Signal                  |     |

|                | Trigger External Instruments on Violations      |     |

|                | 6.4 PCI Protocol Violations                     |     |

|                | PCI protocol violations                         |     |

|                | 6.5 PCI-X protocol Violations                   |     |

|                | PCL-Y protocol violations                       | 162 |

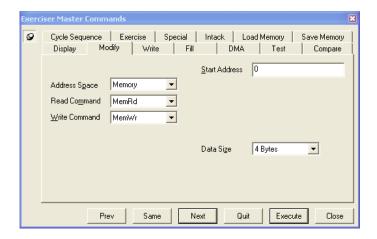

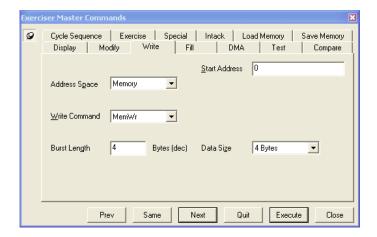

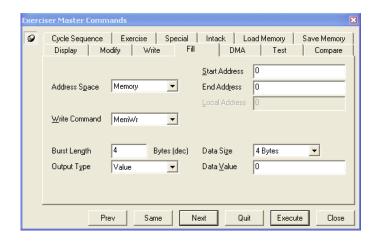

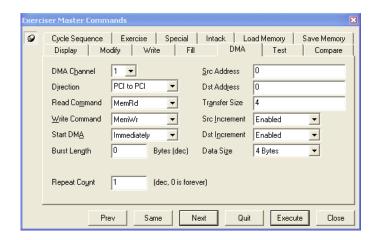

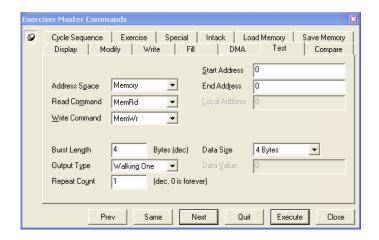

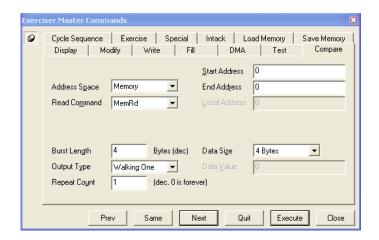

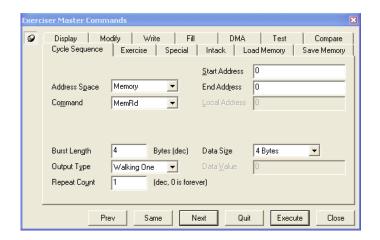

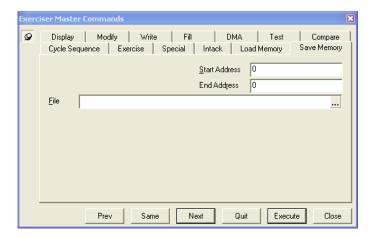

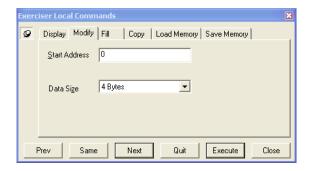

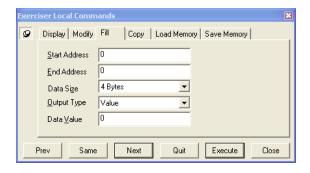

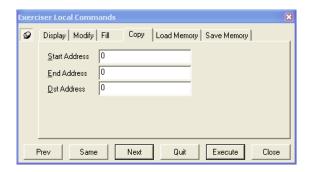

| Exerciser        |                                                                                     | . 217 |

|------------------|-------------------------------------------------------------------------------------|-------|

|                  | 7.1 Overview                                                                        | 218   |

|                  | Features                                                                            |       |

|                  | 7.2 Introduction                                                                    | 220   |

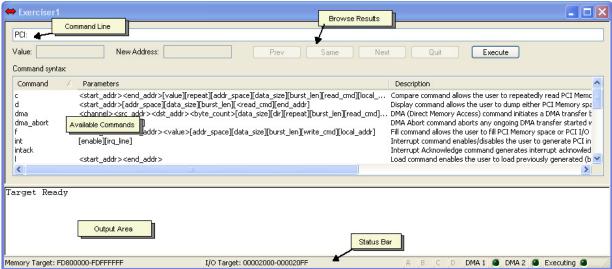

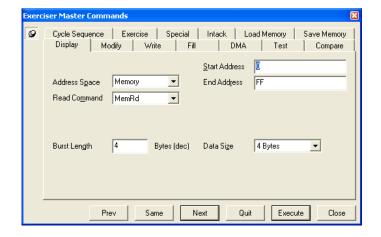

|                  | 7.3 Operation                                                                       | 221   |

|                  | Exerciser Window                                                                    |       |

|                  | The Exerciser toolbar and menu                                                      |       |

|                  | Exerciser Options.                                                                  |       |

|                  | E2 Exerciser Options (Enhanced Exerciser)                                           |       |

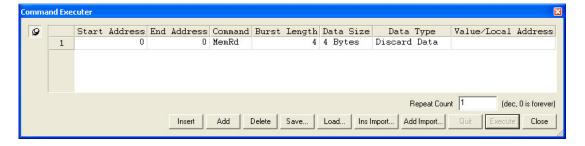

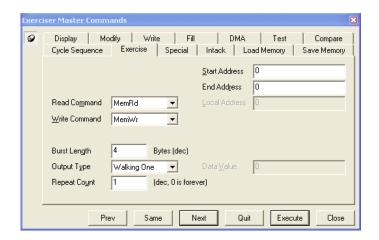

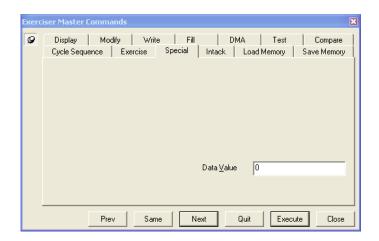

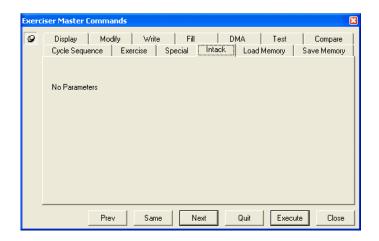

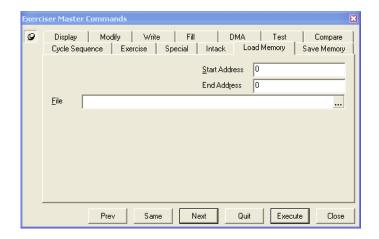

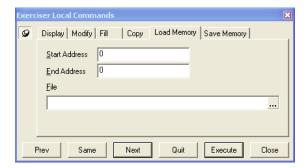

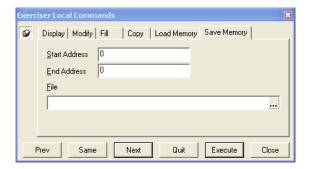

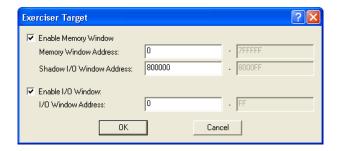

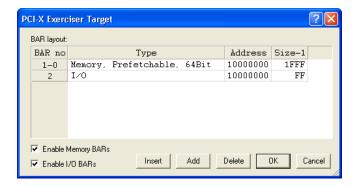

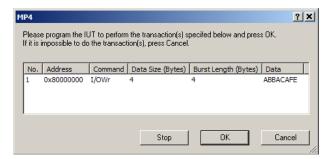

|                  | 7.4 Executing Commands                                                              |       |

|                  | Executing Single commands                                                           |       |

|                  | Executing Multiple Commands                                                         |       |

|                  | 7.5 Summary of Commands                                                             |       |

|                  | 7.6 Configuration Scan                                                              |       |

|                  | 7.7 Using Scripts                                                                   |       |

|                  | Record a Script.                                                                    |       |

|                  | Execute a Script                                                                    | 278   |

|                  | 7.8 Exerciser Script Commands                                                       | 279   |

| The Simulator    | 8.1 Starting the Simulator                                                          | 284   |

|                  | 8.2 Using the Analyzer with the Simulator                                           |       |

|                  | 8.3 Using the Statistics Functions with the Simulator                               |       |

|                  | 8.4 Using the Protocol Checker with the Simulator                                   | 288   |

|                  | 8.5 Using the Exerciser with the Simulator (PCI/PCI-X, VME)                         | 289   |

| 9 Application Pr | rogramming Interface                                                                | . 291 |

|                  | 9.1 Introduction                                                                    | 292   |

|                  | 9.2 API client interfaces                                                           |       |

|                  | Raw ASCII interface                                                                 |       |

|                  | <ul><li><i>XML-RPC interface</i></li><li>9.3 Event notification interface</li></ul> |       |

|                  | Configuration                                                                       |       |

|                  | Message formatting                                                                  |       |

|                  | 9.4 Status codes                                                                    |       |

|                  | 9.5 Command overview                                                                | 301   |

|                  | Miscellaneous Commands                                                              |       |

|                  | Analyzer Commands                                                                   | 301   |

|                  | Protocol Checker Commands                        |       |

|------------------|--------------------------------------------------|-------|

|                  | Exerciser Commands                               |       |

|                  |                                                  |       |

| 10 Compliance    | Checker                                          | . 361 |

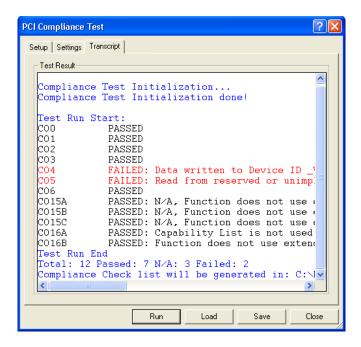

|                  | 10.1 Operation                                   | 36    |

|                  | Getting Started                                  |       |

|                  | Setup                                            |       |

|                  | Settings                                         |       |

|                  | Transcript                                       | 369   |

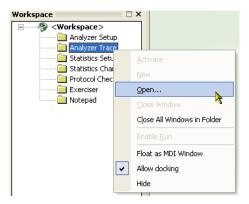

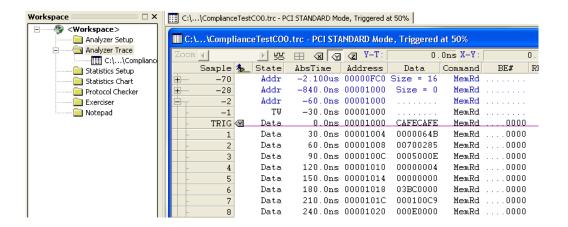

|                  | 10.2 Debugging a failed test                     | 370   |

|                  | Saving and Loading a File                        |       |

|                  | 10.3 Test Requirements                           |       |

|                  | Configuration Tests                              |       |

|                  | Master Tests                                     |       |

|                  | Component Protocol Checklist for a Master Device |       |

|                  | Component Protocol Checklist for a Target Device |       |

|                  | Tests specific to PCI-X                          |       |

|                  | 10.4 Troubleshooting Compliance Checker          | 375   |

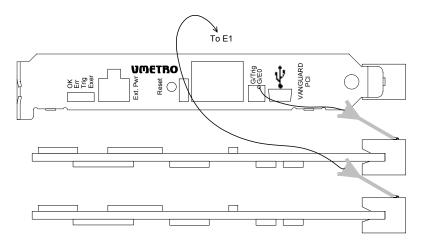

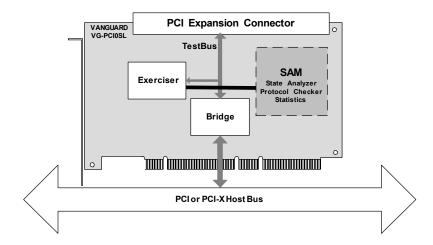

| 11 PCI Zero Slo  | (VG-PCI0SL)                                      | . 377 |

|                  | 11.1 Introduction                                | 378   |

|                  | 11.2 Operating Modes                             | 379   |

|                  | Test Bus Reset button                            |       |

|                  | Hardware Options                                 | 379   |

| ADDENINIVES      |                                                  | . 383 |

| II I ENDIAES     |                                                  | . 505 |

| A Vanguard vs. I | PBT Series                                       | . 385 |

|                  |                                                  |       |

| ☐ Specifications |                                                  | . 387 |

| Signals          |                                                  | 301   |

| Digitals         |                                                  | . 371 |

| D Embedded En    | vironments                                       | . 415 |

# **Figures**

| FIGURE | 1-1 Analyzer acquires bus signals                          | 6  |

|--------|------------------------------------------------------------|----|

| FIGURE | 2-1 Vanguard PCI board layout                              | 10 |

| FIGURE | 2-2 5Volt Adapter Card                                     | 11 |

| FIGURE | 2-3 Front Panel used with the 5V adapter                   | 11 |

| FIGURE | 2-4 Vanguard PMC board layout                              | 13 |

| FIGURE | 2-5 Vanguard PMC Top Spacer                                | 14 |

| FIGURE | 2-6 Vanguard cPCI Board Layout                             | 16 |

|        | 2-7 VG-PCIOSL Board Layout                                 |    |

| FIGURE | 2-8 Connecting external REQ# or GNT# signals               | 21 |

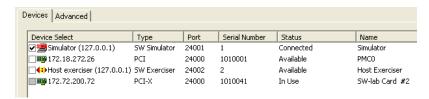

| FIGURE | 3-1 Device Information dialog                              | 38 |

| FIGURE | 3-2 Status Bar                                             | 39 |

| FIGURE | 3-3 Busview.                                               | 40 |

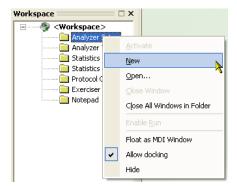

| FIGURE | 3-4 Using the Workspace Window                             | 41 |

| FIGURE | 3-5 Status Bar                                             | 43 |

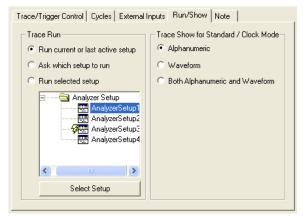

| FIGURE | 3-6 Example Predefined Setups                              | 46 |

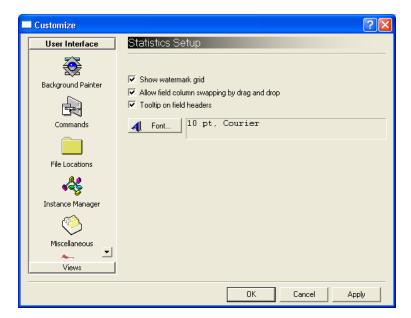

|        | 3-7 Customize Dialog                                       |    |

| FIGURE | 4-1 Block diagram of the State Analyzer                    | 54 |

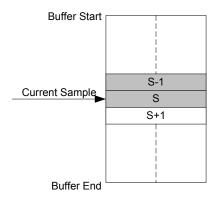

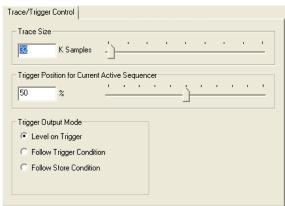

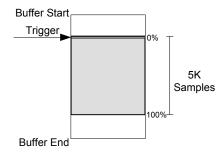

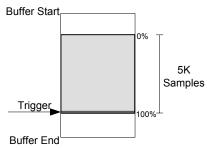

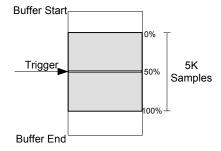

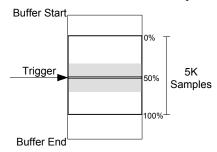

| FIGURE | 4-2 Trace Buffer as circular memory                        | 55 |

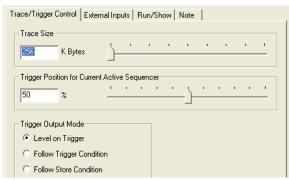

|        | 4-3 Trace buffer settings                                  |    |

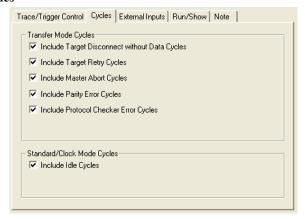

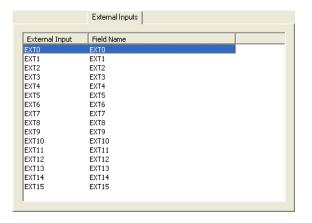

| FIGURE | 4-4 Example of PCI Trigger conditions                      | 56 |

|        | 4-5 The Sequencer                                          |    |

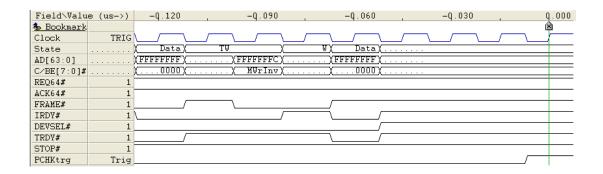

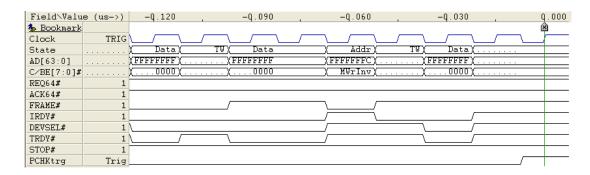

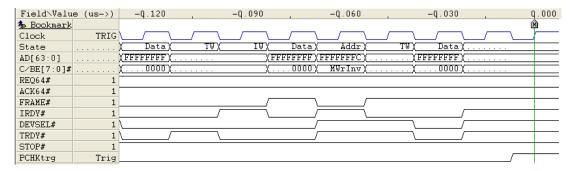

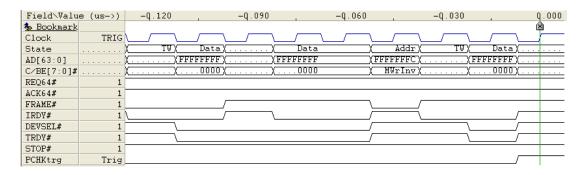

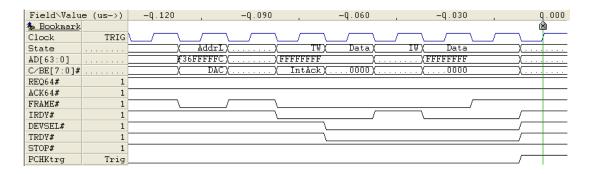

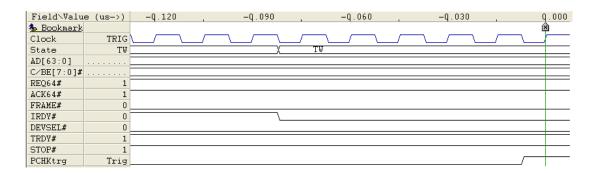

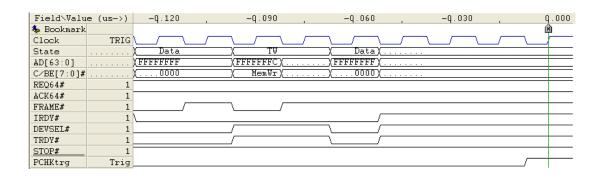

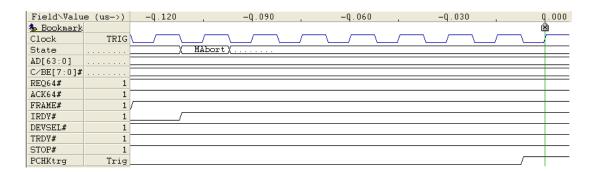

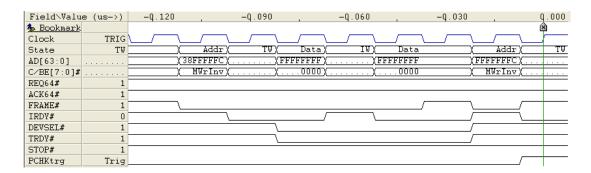

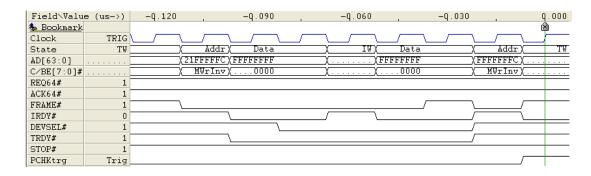

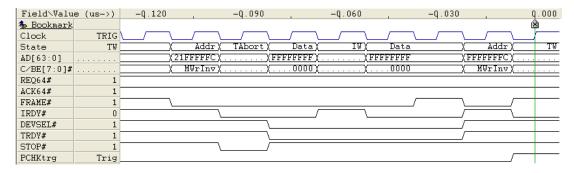

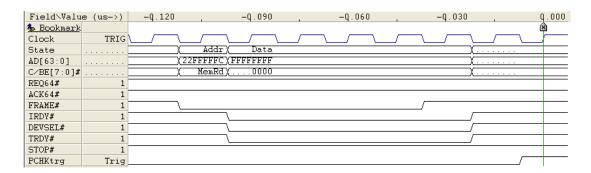

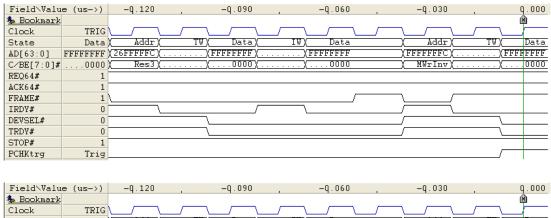

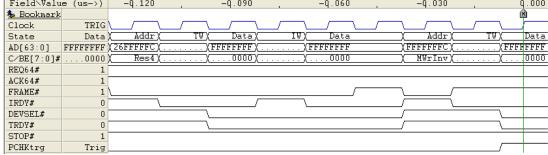

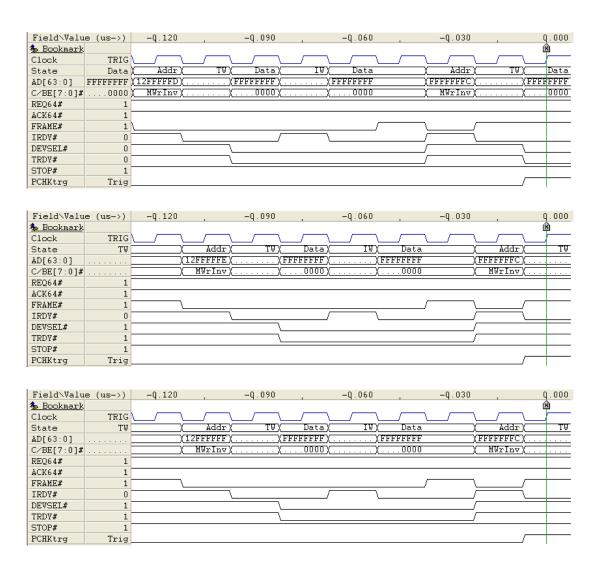

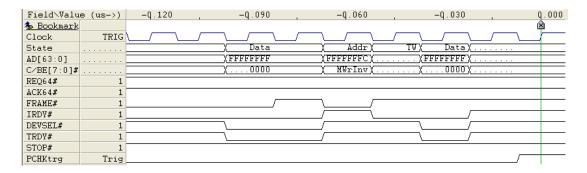

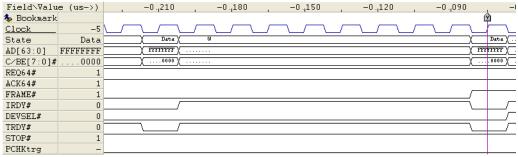

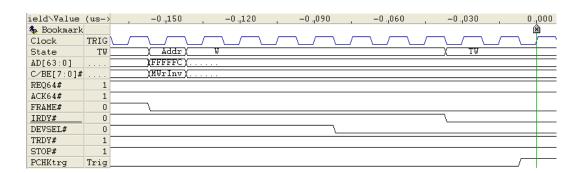

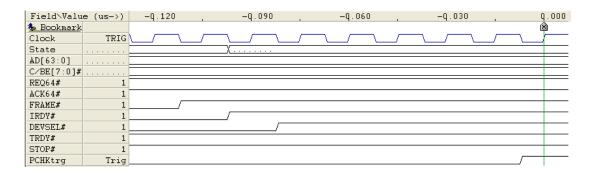

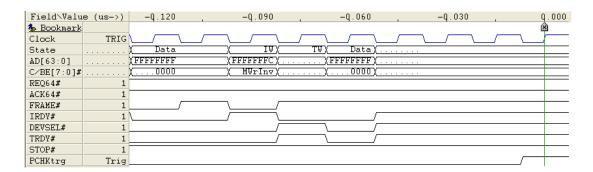

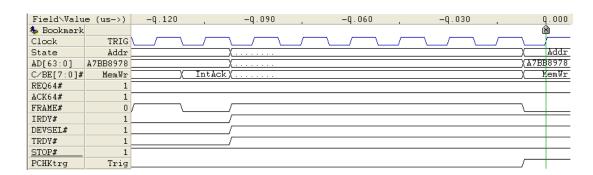

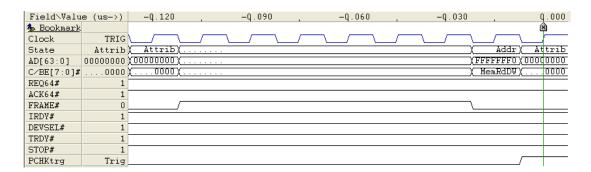

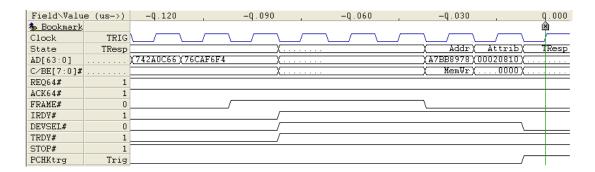

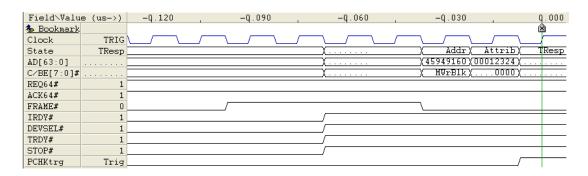

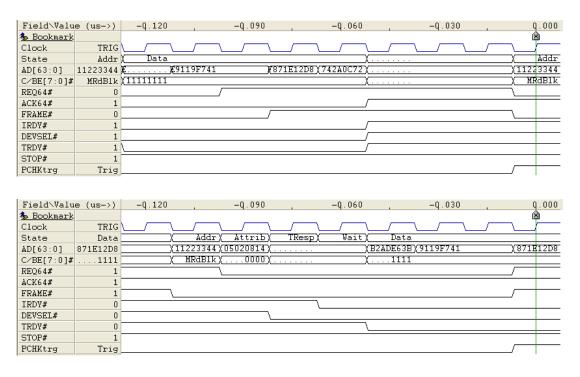

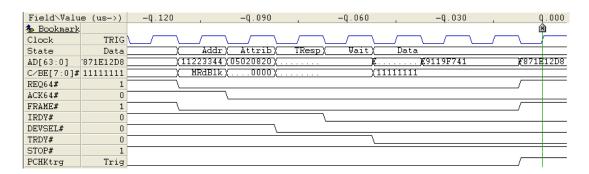

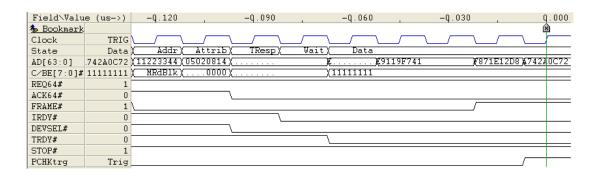

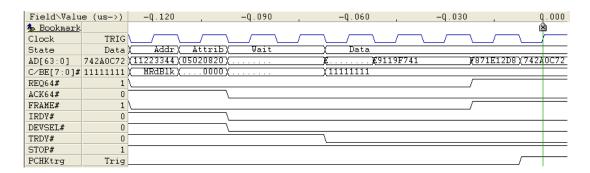

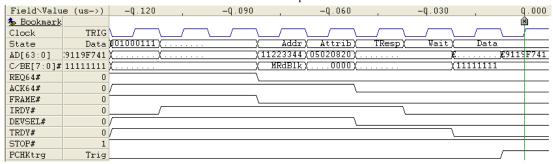

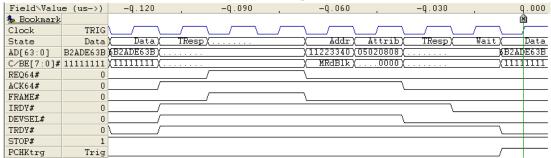

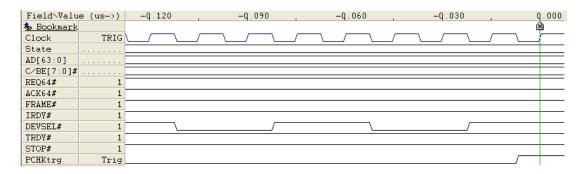

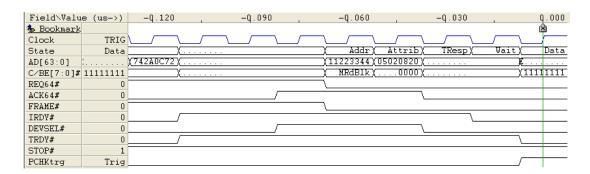

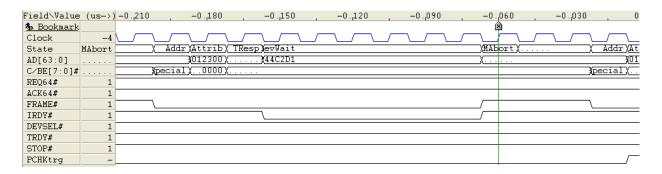

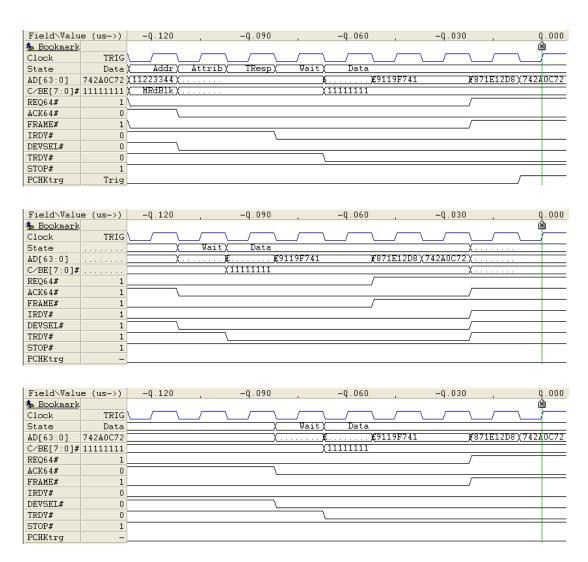

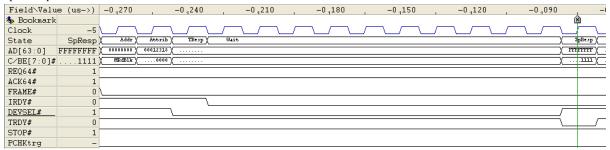

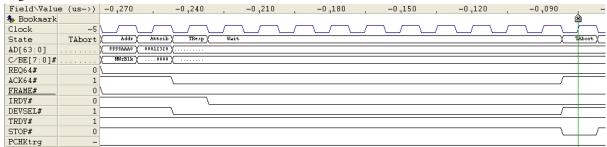

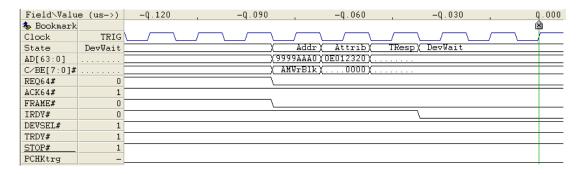

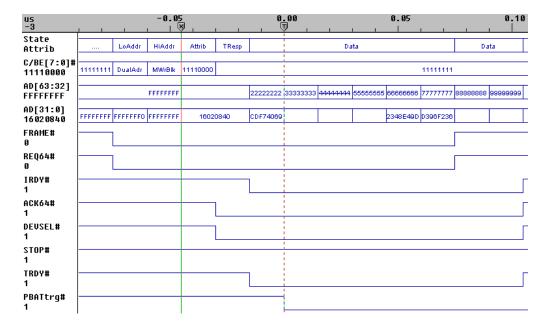

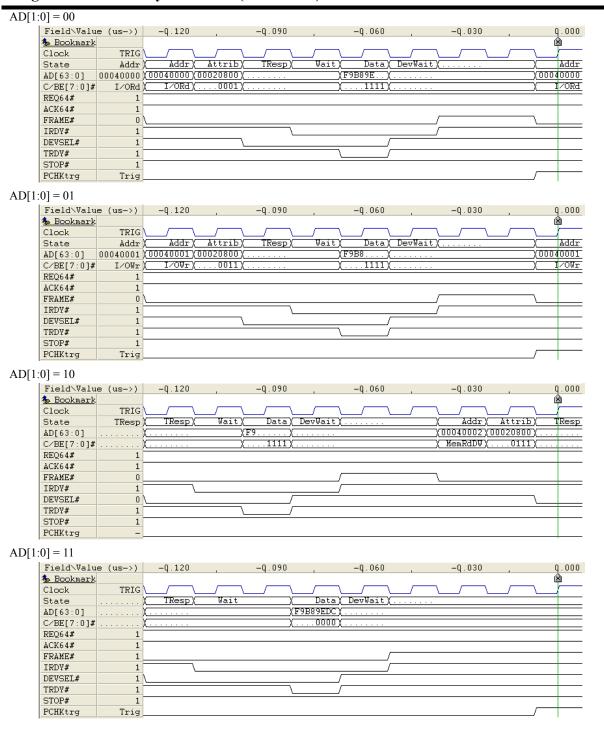

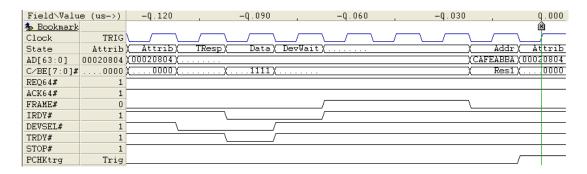

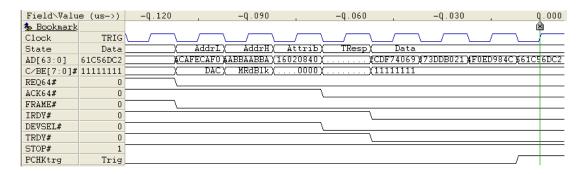

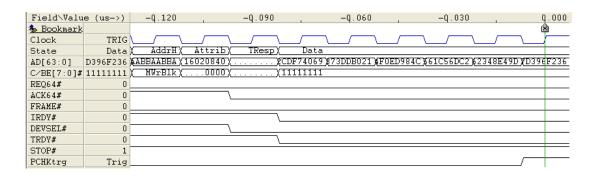

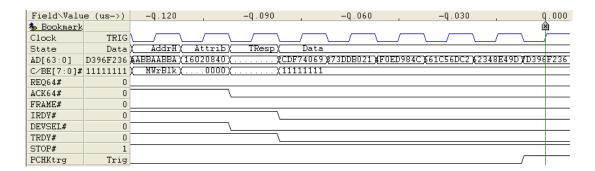

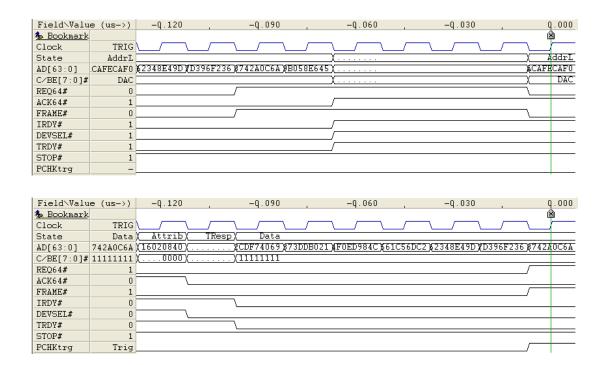

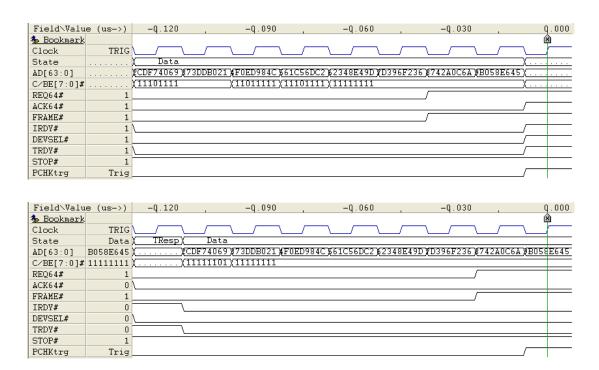

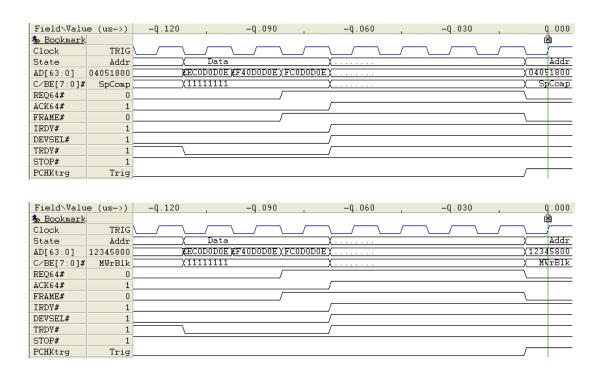

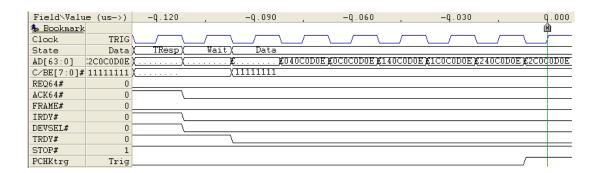

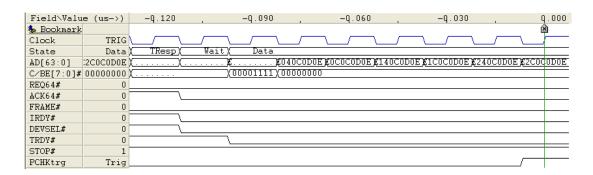

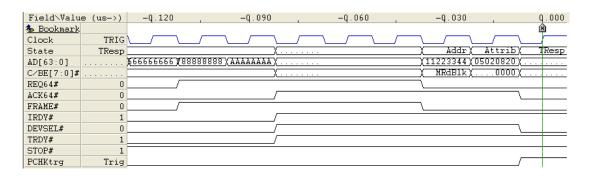

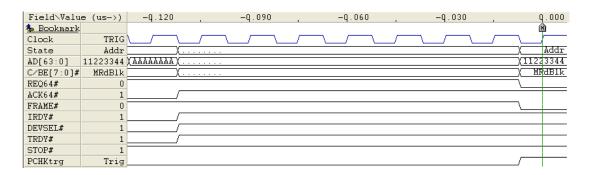

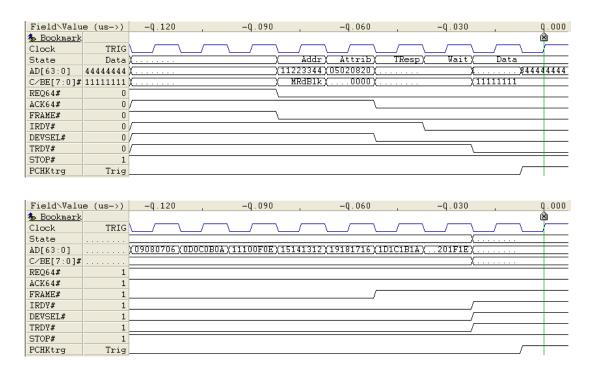

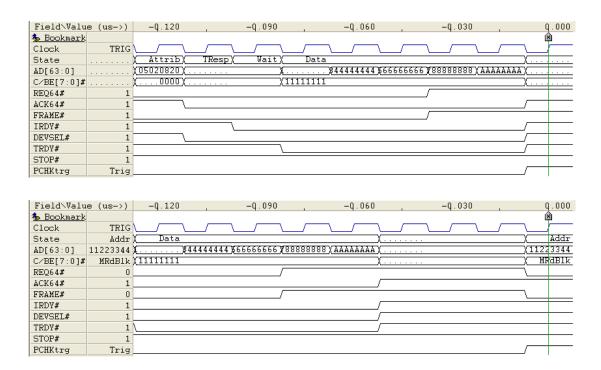

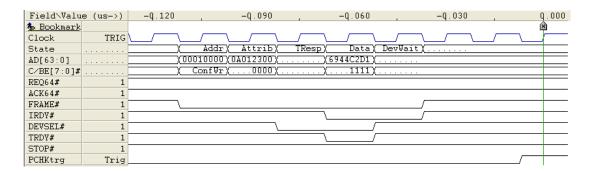

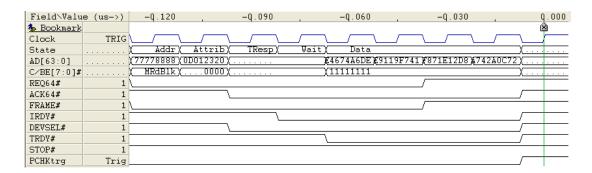

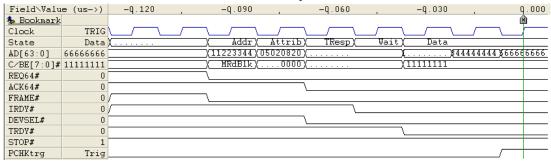

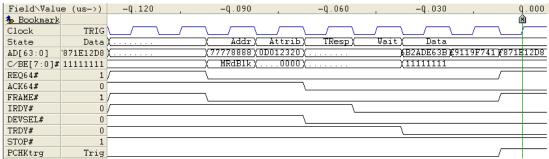

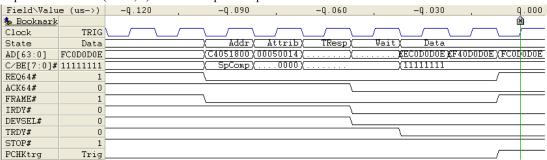

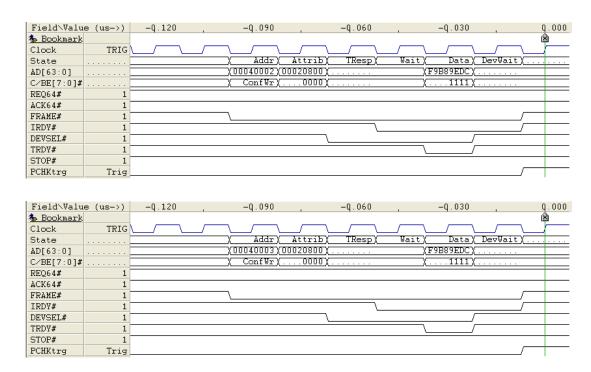

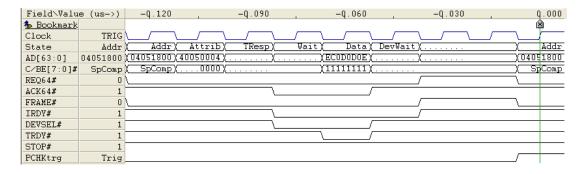

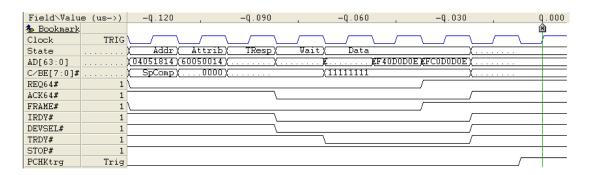

| FIGURE | 4-6 Example PCI trace in alphanumeric and waveform formats | 58 |

| FIGURE | 4-7 Trace ToolTip Information                              | 59 |

| FIGURE | 4-8 Trace Setup Options window                             | 61 |

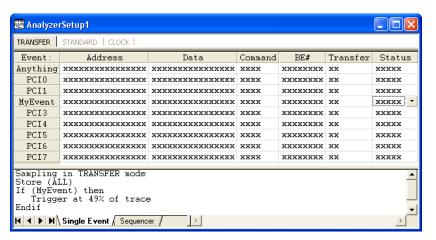

| FIGURE | 4-9 Analyzer Setup Screen                                  | 68 |

| FIGURE | 4-10 Right-click Field menu                                | 72 |

| FIGURE | 4-11 Using Field Properties to set address range.          | 73 |

|        | 4-12 'Don't Care' binary address range                     |    |

| FIGURE | 4-13 Selecting the Sequencer tab.                          | 79 |

| FIGURE | 4-14 Event Expression dialog box                           | 80 |

| FIGURE | 4-15 The Trace Display in Alphanumeric mode                | 83 |

| FIGURE | 4-16 Trace Display menu                                                   | 85  |

|--------|---------------------------------------------------------------------------|-----|

| FIGURE | 4-17 Search and Extract options menu                                      | 88  |

| FIGURE | 4-18 The trace display in waveform mode                                   | 91  |

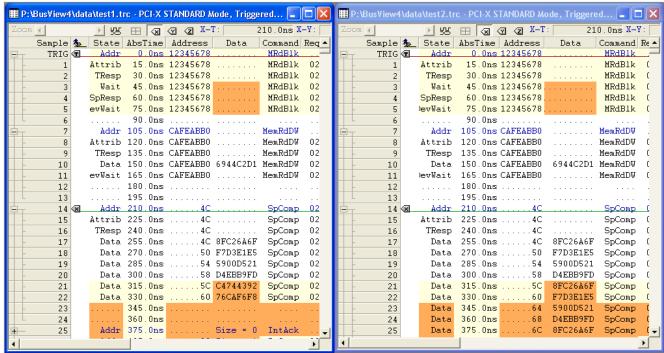

| FIGURE | 4-19 Trace Compare Example                                                | 96  |

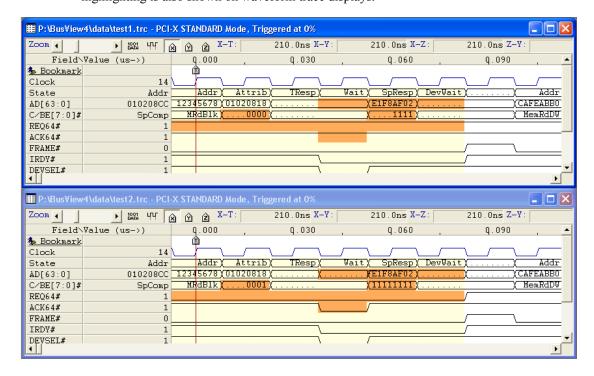

| FIGURE | 4-20 Trace Counting                                                       | 97  |

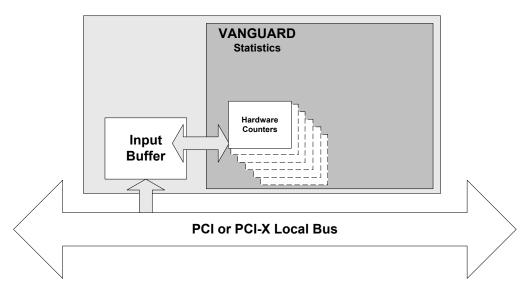

| FIGURE | 5-1 Block diagram of the Statistics module                                | 100 |

| FIGURE | 5-2 Statistics Setup Window                                               | 101 |

|        | 5-3 Statistics Setup Options Window                                       |     |

| FIGURE | 5-4 Event Counting Statistics setup                                       | 113 |

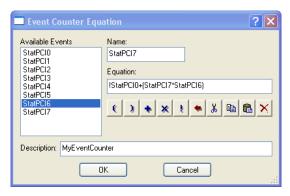

|        | 5-5 Edit an Event Counter Equation                                        |     |

|        | 5-6 Advanced Statistics Counter                                           |     |

| FIGURE | 5-7 Customize Statistics View                                             | 116 |

| FIGURE | 5-8 Statistics Display Element dialog                                     | 116 |

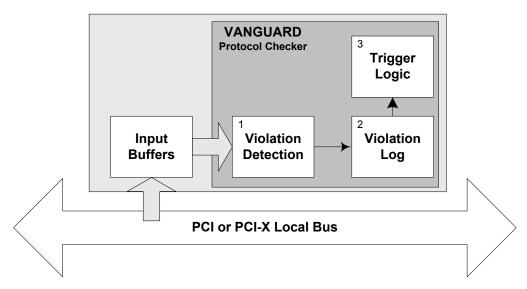

| FIGURE | 6-1 The main blocks of the VANGUARD Protocol Checker.                     | 128 |

| FIGURE | 6-2 The Run Protocol Checker menu item at the menu bar                    | 131 |

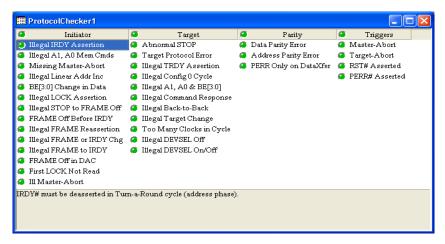

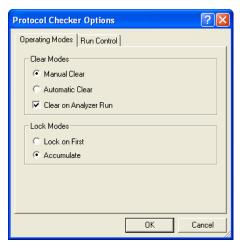

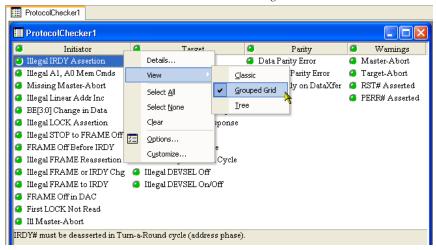

|        | 6-3 Protocol violations in "Grouped Grid" view and "detailed description" |     |

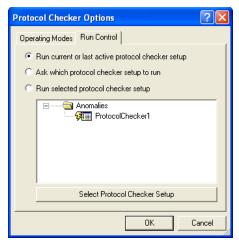

|        | 6-4 Protocol Checker Options                                              |     |

|        | 6-5 Protocol Checker Run Control                                          |     |

|        | 6-6 Protocol Checker right-click menu                                     |     |

|        | 7-1 Exerciser Block Diagram                                               |     |

|        | 7-2 Exerciser Window                                                      |     |

|        | 7-3 Exerciser Performance Options                                         |     |

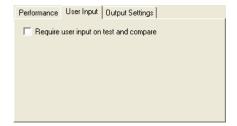

|        | 7-4 Exerciser User Input Options                                          |     |

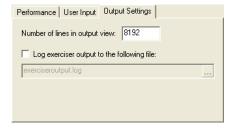

|        | 7-5 Exerciser Output Settings Options                                     |     |

|        | 9-1 Vanguard API firmware integration                                     |     |

|        | 1. Compliance Checker setup                                               |     |

|        | 2. Example Compliance Checker html results page                           |     |

|        | 3. Example cycles request                                                 |     |

|        | 11-1 Block diagram of the VG-PCI0SL                                       |     |

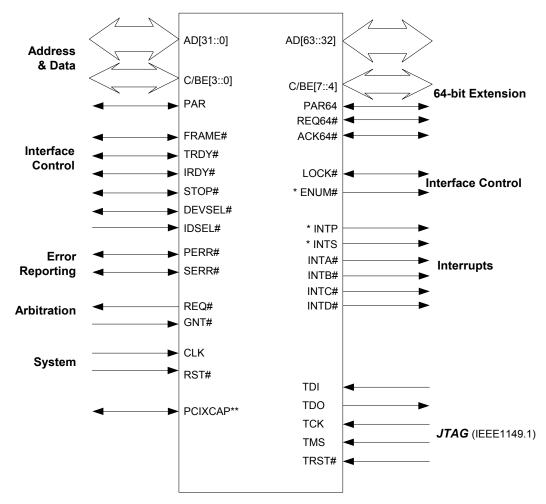

|        | C-1 PCI and PCI-X Signals                                                 |     |

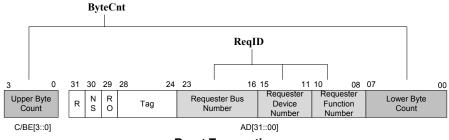

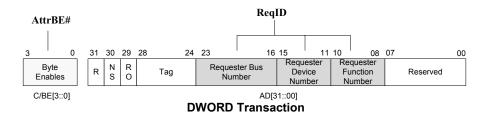

| FIGURE | C-2 Burst and DWORD transaction Attribute Bit Assignments                 | 413 |

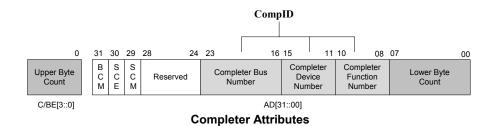

| FIGURE | C-3 Completer Attribute Bit Assignments                                   | 414 |

## **Tables**

| TABLE 2-1.System LEDs                                                  | 19    |

|------------------------------------------------------------------------|-------|

| TABLE 2-2.IO Specification.                                            |       |

| TABLE 2-3.M66EN and PCIXCAP Encoding for Vanguard PCI and Vanguard PMC |       |

| TABLE 2-4.M66EN and PCIXCAP Encoding for Compact PCI version           |       |

| TABLE 3-1.Keys for keyboard control                                    |       |

| TABLE 3-2.Keyboard control from within dialog boxes                    |       |

| TABLE 3-3.Template settings                                            |       |

| TABLE 4-1.Summary of valid characters for Event fields.                |       |

| TABLE 4-2.Sequencer operators.                                         |       |

| TABLE 4-3.Logical Operators                                            |       |

| TABLE 5-1.Command Distribution abbreviations                           |       |

| TABLE 5-2.Burst Length Distribution explanation                        |       |

| TABLE 5-3.Summary of Hardware Counters                                 |       |

| TABLE 6-1.PCHKTrg values                                               |       |

| TABLE 9-1.Raw ASCII message format                                     |       |

| TABLE 9-2.Event notifications.                                         |       |

| TABLE 9-3. Vanguard API status codes                                   |       |

| TABLE 9-4. Vanguard API extended error information                     | . 300 |

| TABLE 9-5.Data type mapping.                                           | . 303 |

| TABLE 9-6.Vanguard API options                                         | . 306 |

| TABLE 9-7.Vanguard device options                                      | . 308 |

| TABLE 9-8. Vanguard reset options                                      | . 309 |

| TABLE 9-9.PCI/PCI-X trace line format                                  | . 316 |

| TABLE 9-10.PCI-X violations                                            | . 319 |

| TABLE 9-11.PCI violations                                              | . 321 |

| TABLE 9-12.Protocol checker options                                    | . 323 |

| TABLE 9-13.PCI/PCI-X options.                                          | . 357 |

| TABLE 9-14.Additional PCI-X E2 options                                 |       |

| TABLE 11-1.M66EN and PCIXCAP Encoding                                  |       |

| TABLE A-1. Vanguard Comparisons with PBT series Analyzers              |       |

| TABLE B-1. Vanguard PCI (Carrier + SAM) 3.3 V                  | 388 |

|----------------------------------------------------------------|-----|

| TABLE C-1.PCI Bus Commands                                     | 395 |

| TABLE C-2.PCI Status Field                                     | 398 |

| TABLE C-3.PCI State Field                                      | 399 |

| TABLE C-4.PCI Transfer Field                                   | 400 |

| TABLE C-5.PCHKTrg Field.                                       | 400 |

| TABLE C-6.EXERtrg Field                                        | 401 |

| TABLE C-7.INTx# Field.                                         | 401 |

| TABLE C-8.PCI Decode field.                                    | 402 |

| TABLE C-9.PCI-X Initialization Pattern.                        | 404 |

| TABLE C-10.M66EN and PCIXCAP Encoding for PCI and PMC versions | 404 |

| TABLE C-11.PCI-X Bus Commands                                  | 406 |

| TABLE C-12.PCI-X Status Field                                  | 408 |

| TABLE C-13.PCI-X State Field                                   |     |

| TABLE C-14.PCI-X Transfer Field                                | 410 |

| TABLE C-15.PCI-X Decode field                                  | 411 |

| TABLE C-16.PCHKTrg Field.                                      |     |

| TABLE C-17.EXERtrg Field                                       |     |

| TABLE C-18 INTx# Field                                         |     |

Product Overview

This section gives a broad overview of the main functions provided by the Vanguard.

- Overview

- Analyzer

- Protocol Checker

- Statistics Functions

- Exerciser (PCI & VME)

- Host Exerciser

#### 1.1 Overview

VMETRO is a company totally committed to building the finest bus analyzers, and is recognized in development laboratories around the world as providing superior tools for developers and manufacturers of bus based computer equipment.

The Vanguard is the result of more than 15 years experience in building bus analyzers. The Vanguard Analyzer has evolved through four generations of VME bus analyzers, five generations of PCI bus analyzer and two generations of PCI-X analyzer.

A bus analyzer is a pre-configured logic analyzer designed as a plug-in card conforming to the logical, electrical and mechanical specification of the target bus. The primary use of a bus analyzer is to monitor the activity on a back plane bus and provide a trace of bus cycles between modules. This information is then presented as alphanumeric trace lists or as waveforms.

The serial protocol analyzer samples the symbols on the serial link and presents the packets formed in a graphical view. This is done without connecting and configuring large numbers of probes to the back plane, a time-consuming and error-prone process necessary with general-purpose logic analyzers.

Statistical analysis of a bus system provides extensive performance monitoring in real time. This analysis can identify latencies, device throughput measurements and efficiency.

For parallel buses (VME, PCI and PCI-X), the Vanguard also includes an Exerciser unit that allows you to generate traffic, emulate a target, and generate interrupts.

The built-in protocol checker detects protocol errors and bus anomalies without the need for detailed knowledge of particular bus specifications and serial protocols.

#### Vanguard

The Vanguard product family provides a suite of tools for use in developing, testing and fault-finding in chipsets, motherboards, add-in boards and software which use PCI, PCI-X, PCIe and VME busses. The tools are controlled through a Windows-based program called *BusView*<sup>®</sup>.

#### The Tools

The tools are categorized as follows.

- Analyzer: Bus sampling and analysis.

- Protocol Checker: Detects bus protocol violations.

- Statistics Functions. Statistical representation of a number of bus performance issues.

- Exerciser: Provides a method of applying traffic (cycles) onto the bus. An enhanced Exerciser is

also available for PCI-X, adding the functionality to inject errors onto the bus as well providing

more flexible control of Master and Target behavior.

- Compliance Verification (PCI and PCI-X). Performs compliance checklist scenarios, including those defined by the PCI SIG (Special Interest Group).

#### The Hardware

The Vanguard Hardware is available in several form factors.

- PCI A PCI carrier card contains the Exerciser. A SAM module is added to provide Analyzer,

Protocol Checker and Statistics functions. Also available is the 0-slot PCI adapter which allows

a PCI card (Device Under Test) to be inserted into the same slot as the PCI Vanguard.

- **Compact PCI** the cPCI carrier board contains the Exerciser. A SAM module is added to provide Analyzer, Protocol Checker and Statistics functions.

- VME A VME carrier board is used in conjunction with a SAM module to provide the Analyzer, Protocol Checker and Statistics functions. An additional Exerciser daughter card can be added. It is also possible to mount the PMC Vanguard for analysis of PCI/PCI-X on the P0 connector.

- PMC The PMC board contains the Analyzer, Protocol Checker, Statistics and Exerciser functions.

- XMC The XMC board contains the Analyzer, Protocol Checker and Statistics functions.

- Vanguard Express A set of carrier cards are available for x1, x4 and x8 link widths. The device under test is mounted on top of the carrier card. An SAE module is added to provide Analyzer, Protocol Checker and Statistics functions.

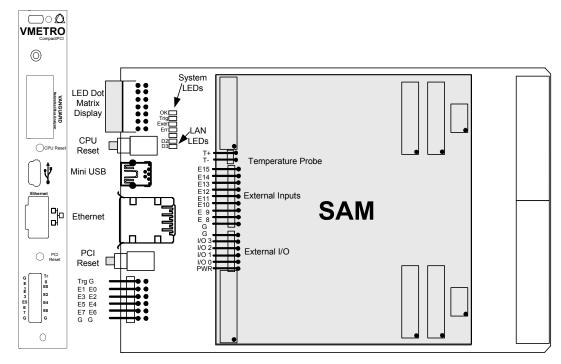

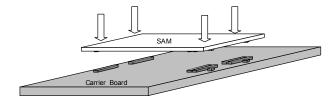

#### **SAM (State Analyzer Module)**

The SAM (State Analyzer Module) is a removable daughter card containing the State Analyzer, Protocol Checker and Statistics functions, and can be used with PCI, VME and Compact PCI carrier cards.

The SAM module can be freely swapped between these carrier cards.

#### **PCI Carrier**

The PCI carrier contains the Exerciser and accommodates the SAM module.

It can be used in any 32 or 64 bit slot in a PCI/PCI-X motherboard.

If it is to be inserted into a 5V slot then the accompanying 5V adapter must be used.

#### **PCI Zero Slot Adapter**

The Vanguard PCI Zero Slot Adapter includes a PCI to PCI bridge and an edge connector to allow for the addition of another PCI card on top of the Vanguard.

#### PMC form factor

The Analyzer, Statistics, Protocol Checker and Exerciser functions are all built into the PMC form factor.

The Vanguard PMC can be combined with a Top Spacer board allowing it to be used in single slot systems.

#### **Compact PCI**

The CompactPCI Vanguard is a 3U Eurocard based form connected via a passive PCI backplane.

#### **VME**

The VME card carries the SAM and the Exerciser modules.

The VME boards can be installed in any VME slot, however, if it is to act as System Controller then the Exerciser module must be present on the board.

There is also a VME P0 version available allowing a Vanguard PMC to be installed to give access to PCI/PCI-X on the P0 connector.

#### PCI Express (PCIe)

PCI Express is a new high performance PCI based bus, utilizing a serial interconnect to provide significant benefits over current parallel interfaces such as PCI/PCI-X, AGP etc.

A connection between two PCI Express devices must minimally support a single-lane in both directions to form a x1 link. Devices may optionally support wider links composed of 2, 4, 8, 12, 16, or 32 lanes creating a parallel interface of independently controlled serial links. Longer physical slots are required where more lanes are in use.

#### XMC form factor (PCI Express)

The Vanguard XMC form factor (Switched Mezzanine Card) provides a backward compatible (PMC) upgrade path to faster interfaces.

XMC supports up to x8 PCI Express. It may also support other serial interconnects instead of PCIe.

#### Serial Analyzer Engine (SAE) Module

The Serial Analyzer Engine (SAE) module is a removable daughter card containing the State Analyzer, Protocol Checker and Statistics functions, and can be used with PCI Express carrier cards.

The SAE module can be freely swapped between these carrier cards.

#### **Vanguard Express Carrier Cards**

The Vanguard Express Carrier Cards are available as x1, x4 and x8 PCIe card edge adapters for the SAE module.

#### **AMC Adapter**

The AMC Adapter card sites between the AMC chassis and the device under test. The Adapter card can be mounted with either the Vanguard Express SAE module or the Vanguard Express XMC board to provide Analyzer, Protocol Checker and Statistics functions.

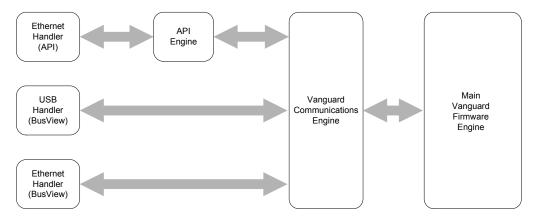

#### The Software - BusView®

BusView is a Windows compatible program from which all of the Vanguard tools are controlled. Once installed onto a compatible workstation, BusView will connect to the hardware. BusView can be installed onto the same system in which the Vanguard is installed, or it can be installed in a different system.

The connection between the Vanguard and BusView is one of two types:

- Direct Connection Connecting directly to the Vanguard via a USB cable, or a crossover Ethernet cable.

- Remote Connection BusView connects to the Vanguard via Ethernet over a network.

#### 1.2 Functional Overview

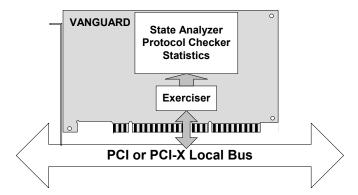

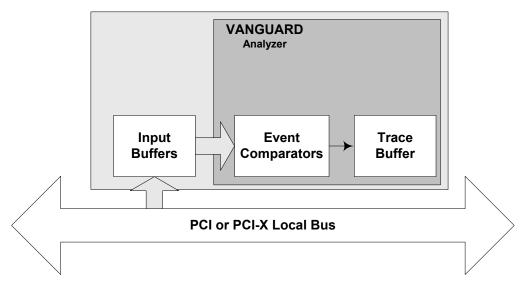

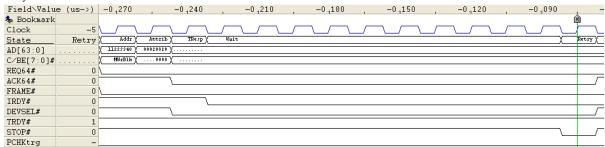

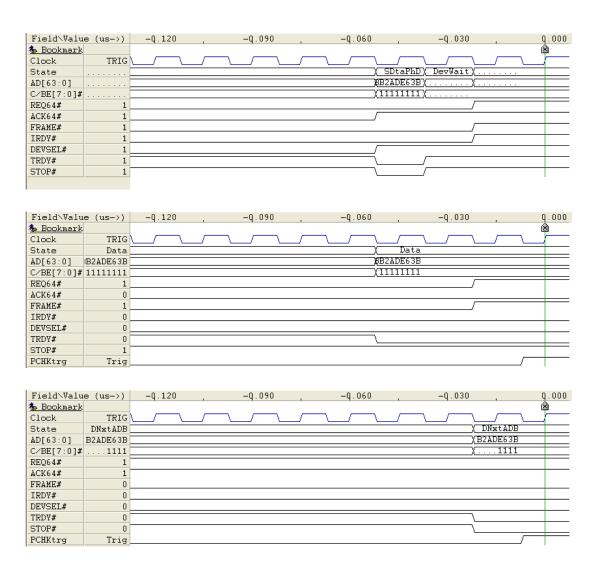

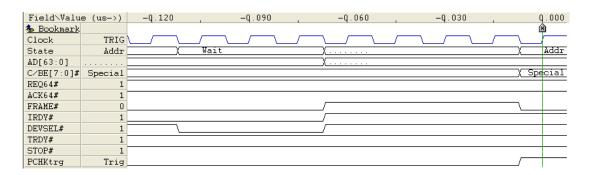

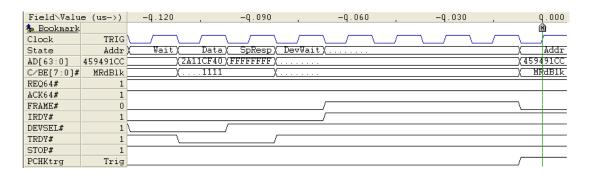

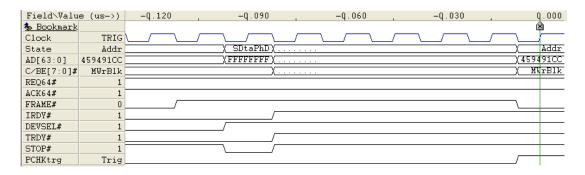

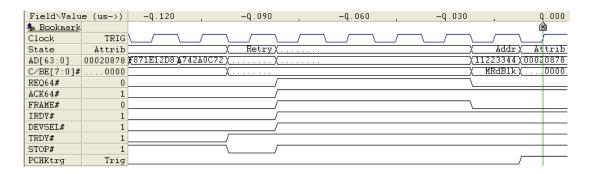

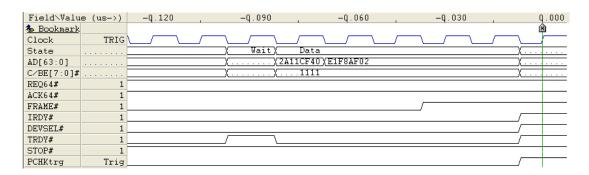

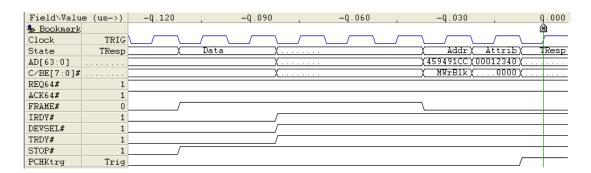

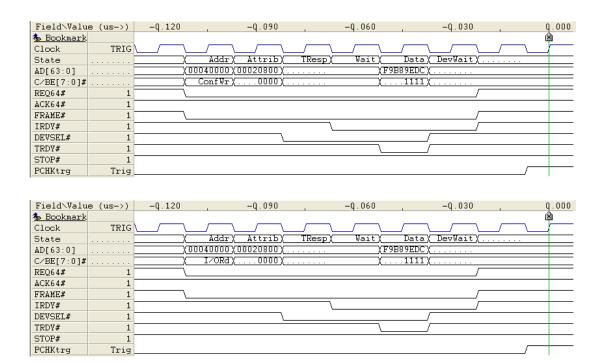

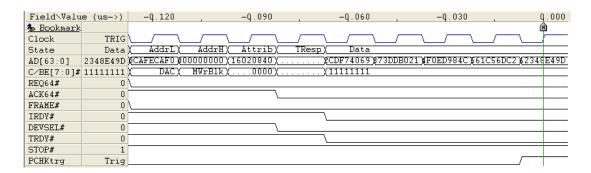

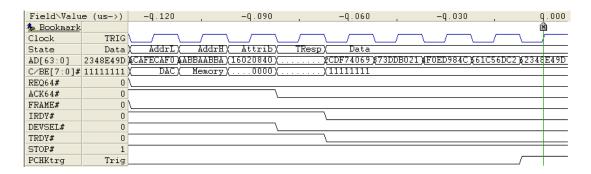

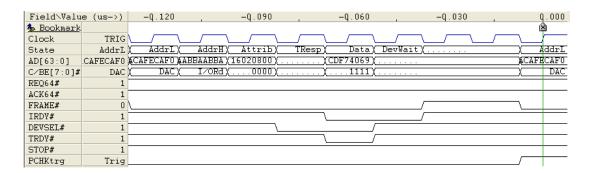

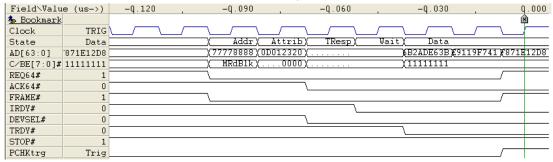

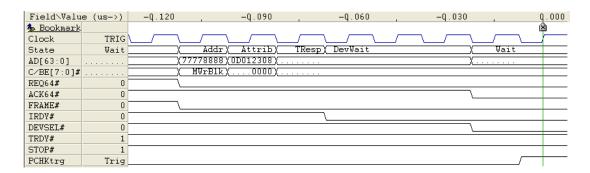

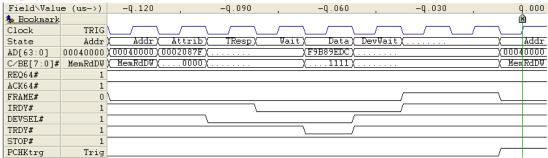

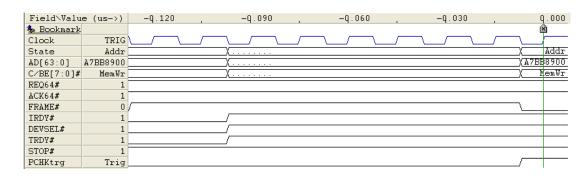

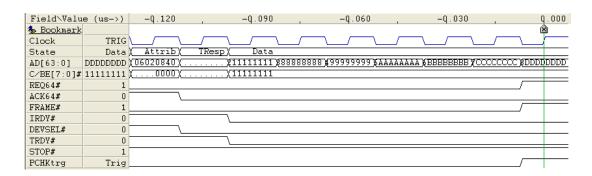

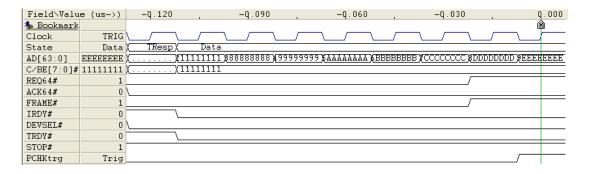

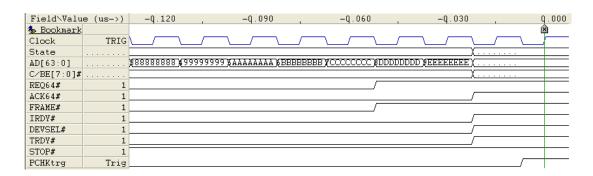

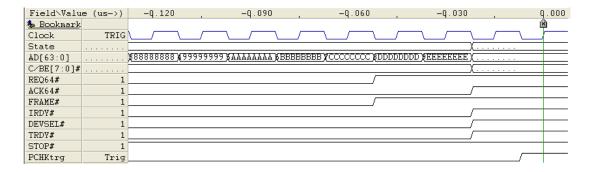

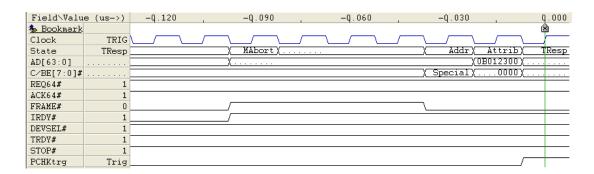

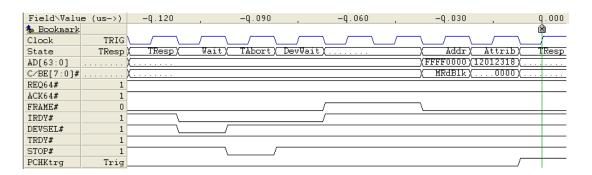

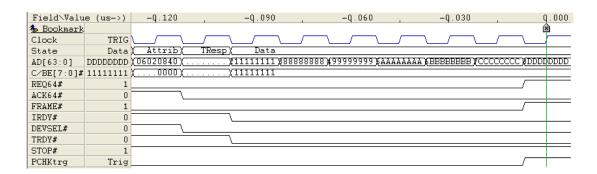

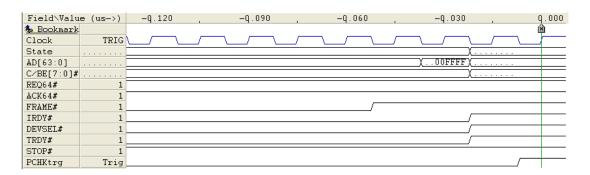

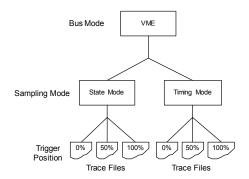

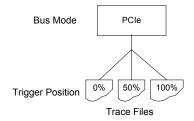

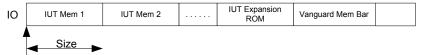

Figure 1-1 illustrates how bus signals are acquired in the Vanguard.

FIGURE 1-1 Analyzer acquires bus signals

#### Analyzer

The Analyzer is responsible for sampling, storing, and displaying bus or link traffic.

The Analyzer will stop sampling according to "trigger conditions" and stores samples of the bus activity according to "trigger and store conditions". A sequencer is also available for building trigger conditions that consist of more than one event or a sequence of events. Once the samples are stored, they are viewed in the "Trace Display" window.

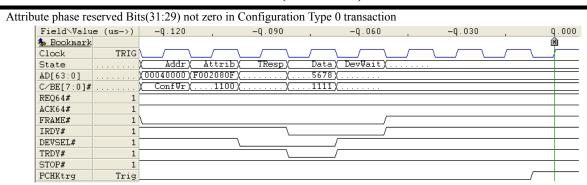

#### **Protocol Checker**

The protocol checker detects protocol violations. This helps uncover design, manufacturing and field-failure-induced flaws in Root Complexes, Switches and Endpoints.

It will also uncover a wide variety of problems originating in other parts of a board that directly or indirectly causes illegal bus activity. This is achieved by monitoring the packet exchange between two devices, that are present in the system configuration. This can help, for example, determine why a board from a particular manufacturer does not function correctly in a system from another manufacturer.

The difficult part of debugging is usually determining which conditions to trigger on. Often, the symptoms of failure give no clue as to their cause. Since all of the Vanguard tools can be used simultaneously, the possibility of triggering the Analyzer as result of a protocol violation significantly enhances the versatility of the Vanguard.

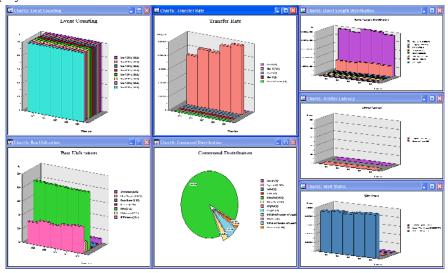

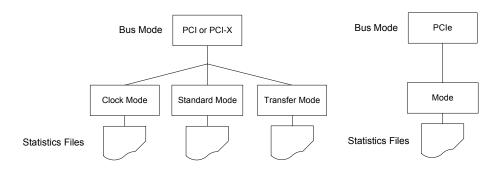

#### **Statistics Functions**

The Statistics Functions offer several pre-defined statistics as well as up to eight 'Event Counters' which can be used together in mathematical formula to count the occurrence of user-selectable events. Used in conjunction with Customized Charts, you can build your own statistical reports for more advanced bus performance analysis.

All statistics can be run simultaneously, in real time. Additionally, a trace counting function is available for generating statistics from a captured trace file offline.

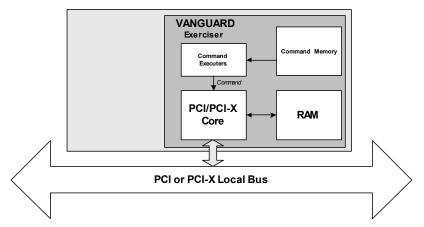

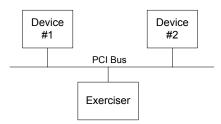

#### **Exerciser (PCI & VME)**

The exerciser acts as a reference unit that generates VME and PCI bus cycles with known characteristics. It is usually used for testing new boards or to assist in the debugging of boards. It can also load the system with heavy bus traffic for performance checks.

The exerciser can also be used to patch data in memory without influencing the operation of other masters on the bus.

Use of the PCI/PCI-X Exerciser requires the "VG-E" or "VG-E2" license. Use of the VME Exerciser requires the "VG-VE" license. See "Ordering Information" on page 427.

#### **Host Exerciser**

The Host Exerciser is software installed on a target machine located. The Host Exerciser is controlled from BusView via a network.

#### **PCI and PCI-X Compliance Verification**

Both master and target tests can be performed to ensure PCI and PCI-X compliance according to the PCI SIG (Special Interest Group) compliance checklist.

Refer to:

"PCI 2.2 Compliance Checklist" and "PCI-X 1.0a Compliance Checklist" documents published by PCI SIG.

# Hardware Description

- Vanguard PCI Assembly PCI Carrier and SAM

- 5V Adapter Card

- Vanguard PMC Assembly

- Top Spacer

- Vanguard cPCI Assembly cPCI Carrier and SAM

- Vanguard Hardware Features

- · External Power

- Miscellaneous Parts

- · Hardware Menu

- Moving the SAM

ESD – Static electricity can permanently damage your Vanguard. Prevent electrostatic damage by following the static electricity precautions listed in the Installation Guide.

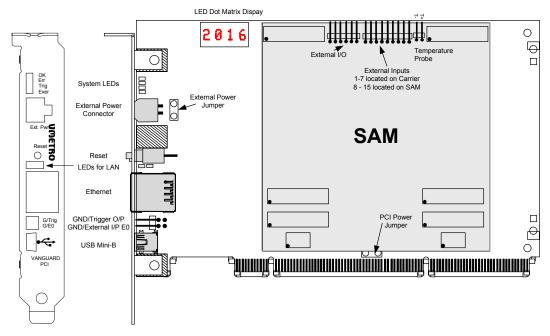

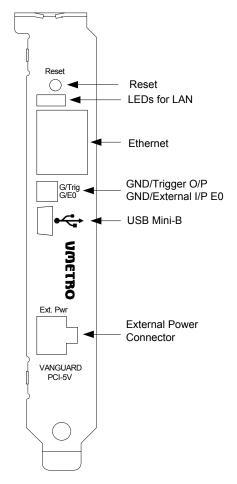

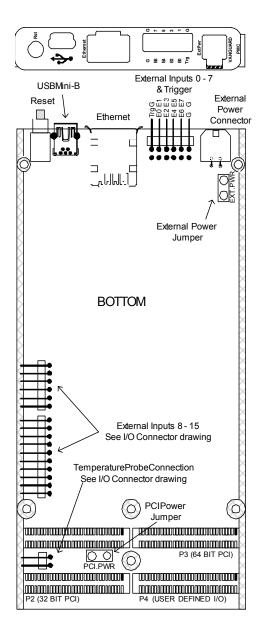

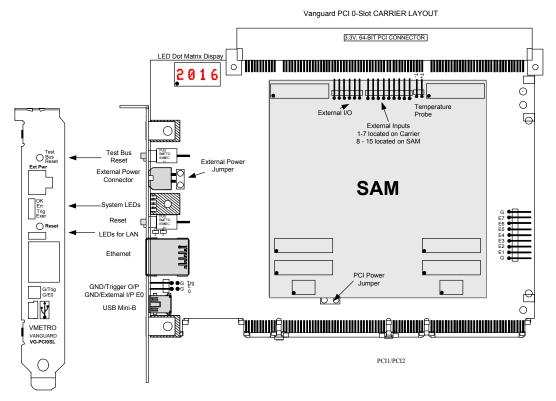

#### 2.1 Vanguard PCI Assembly - PCI Carrier and SAM

FIGURE 2-1 Vanguard PCI board layout

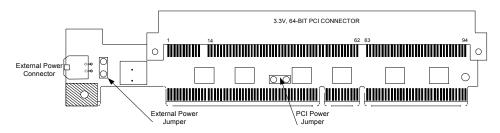

#### **5V Adapter Card**

Since the Vanguard uses 3.3V signalling as standard, this adapter card is necessary for systems using 5V signalling. The 5V Adapter can only be used for a 5V 33MHz PCI system. See the Installation Guide for instructions on assembling the adapter card to the Vanguard.

**Note** – If an external power source is used, the external Power connector on the Vanguard main board will be blocked by the adapter card front panel. Use the external power connector located on the adapter card instead.

FIGURE 2-2 5Volt Adapter Card

FIGURE 2-3 Front Panel used with the 5V adapter

The blue jumper located on the Vanguard main board must be in the PCI.PWR position when this 5V adapter card is used.

#### 2.2 Vanguard PMC Assembly

#### Vanguard PMC board

##

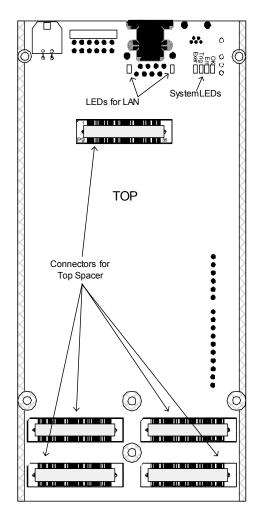

FIGURE 2-4 Vanguard PMC board layout

#### **Top Spacer**

If all of the PMC slots on the carrier board are occupied, the Top Spacer can be used to place the Vanguard PMC in between the carrier board and the PMC module under test.

The Top Spacer extends the PMC slot and enables the PMC module to be mounted on top of the Top Spacer. The spacer has male connectors on top and female connectors on the bottom that match the connectors found on the top of the Vanguard.

The spacer is designed so that the front panel of the PMC module under test is resting on top of the Top Spacer ensuring that the stacked module remains parallel with the carrier board.

Note – The Top Spacer regenerates the PCI CLK signal using a PLL. The PLL frequency range is from 10MHz to 133.33MHz. It is this PCI CLK signal that is supplied to a PMC board mounted on top of the Top Spacer.

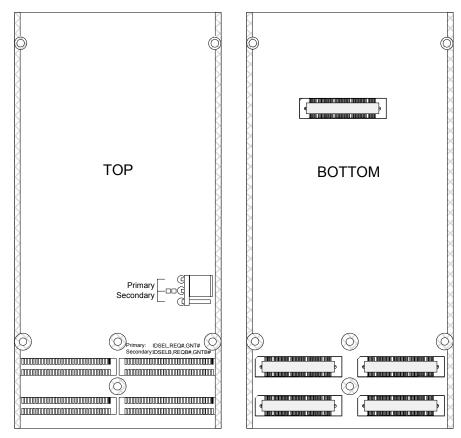

FIGURE 2-5 Vanguard PMC Top Spacer

#### **Jumper Positions**

**Primary Position** When in the Primary position, the jumper controls a quick switch that muxes REQ#/GNT#/IDSEL from the carrier board to REQ#/GNT#/IDSEL on the Top Spacer PMC connector.

**Secondary Position**When in the Secondary position, the jumper controls a quick switch that muxes REQB#/GNTB#/IDSELB from the carrier board to REQ#/GNT#/IDSEL.

**Note** – REQB#/GNTB#/IDSELB from the carrier board is always connected to REQB#/GNTB#/IDSELB Top Spacer PMC connector regardless of jumper position.

Below are the four possible configurations of Carrier/PMC cards with the VG-PMC/Top Spacer in conjunction with the Primary/Secondary jumper setting. The limiting factor to consider is that the carrier board has either one or two sets of REQ#/GNT#/IDSEL signals. Consequently it can only support a maximum of two PCI devices. The Vanguard Exerciser counts as one device.

#### Configuration 1: PMC Carrier and PMC card on top of VG-PMC

- Primary Position: VG-PMC Exerciser is disabled, and the PMC card uses REQ# / GNT# / IDSEL from PMC Carrier.

- Secondary Position: VG-PMC Exerciser is enabled, and the PMC card is not supported. REQ# / GNT# / IDSEL to PMC card are pulled to inactive levels.

#### Configuration 2: PMC Carrier and PrPMC card on top of VG-PMC

- Primary Position: VG-PMC Exerciser is disabled, and the PrPMC card uses REQ# / GNT# / IDSEL from PMC Carrier. REQB# / GNTB# / IDSELB is not supported from PMC Carrier (REQB# / GNTB# / IDSELB to PrPMC card are pulled to inactive levels).

- Secondary Position: VG-PMC Exerciser is enabled, and PrPMC card is not supported, AND MUST NOT BE MOUNTED. Alternatively do not mount the Top Spacer/PrPMC card assembly to enable the VG-PMC Exerciser.

#### Configuration 3: PrPMC Carrier and PMC card on top of VG-PMC

- Primary Position: VG-PMC Exerciser is disabled, and the PMC card uses REQ# / GNT# / IDSEL from PrPMC Carrier.

- Secondary Position: VG-PMC Exerciser is enabled, and the PMC card uses REQB# / GNTB# / IDSELB from PrPMC Carrier.

#### Configuration 4: PrPMC Carrier and PrPMC card on top of VG-PMC

- Primary Position: VG-PMC Exerciser is disabled, and the PrPMC card uses REQ# / GNT# / IDSEL, and REQB# / GNTB# / IDSELB from PrPMC Carrier.

- Secondary Position: VG-PMC Exerciser is enabled, and PrPMC card is not supported, AND MUST NOT BE MOUNTED. Alternatively do not mount the Top Spacer/PrPMC card assembly to enable the VG-PMC Exerciser.

#### **Voltage Keying**

**Warning!** The Voltage Keying Post must be mounted in the correct position. Failure to do so will cause permanent damage to the board and is a potential fire hazard.

Please see the Installation Guide for instructions.

#### 2.3 Vanguard cPCI Assembly - cPCI Carrier and SAM

FIGURE 2-6 Vanguard cPCI Board Layout

#### **System Slot functions**

The cPCI back plane is passive, which means that one of the inserted boards has to control some system functions like clock generation, mode detection, arbiter functions and the like. This board is called a system controller, and it is inserted into a dedicated system slot. The other boards are peripheral boards, and they are inserted into one of the peripheral slots. The back plane controls the slot setup by the SYSEN# signal.

The cPCI Vanguard supports system slot functions, but not high level functions like system configuration.

Busview shows "SysSlot" in the status line if the board is inserted into a system slot.

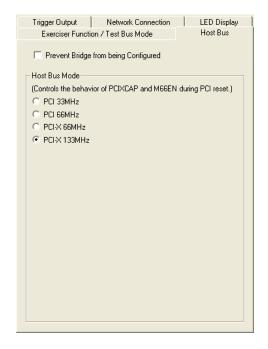

For Mode Detection information, See "Bus Mode" on page 27.

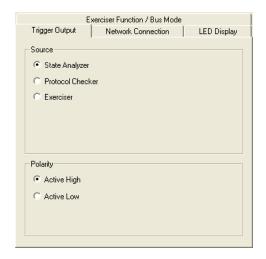

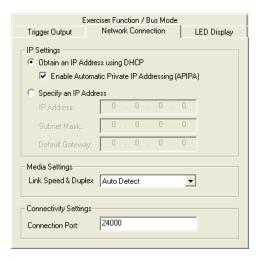

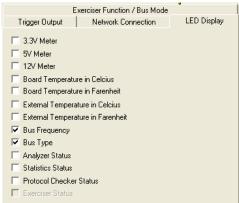

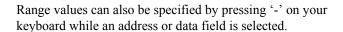

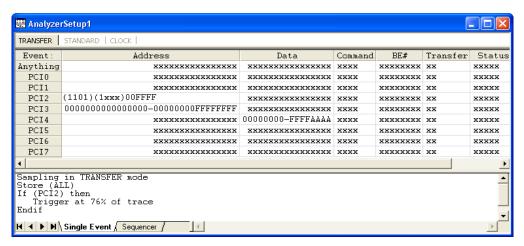

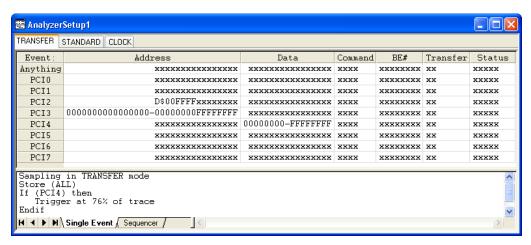

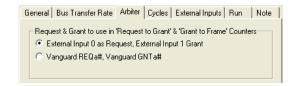

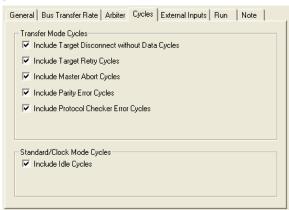

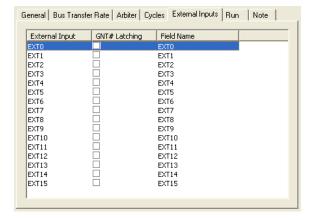

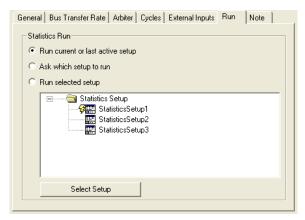

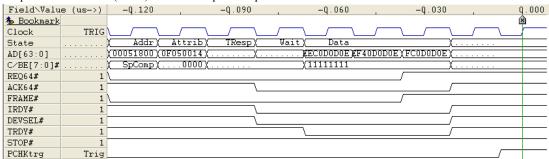

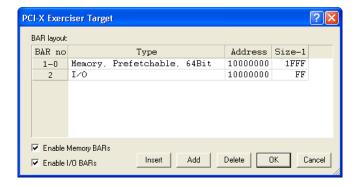

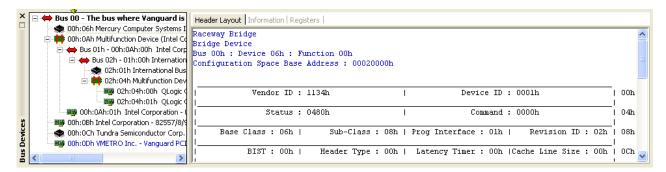

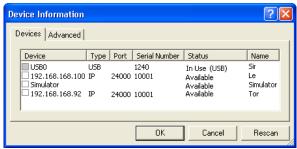

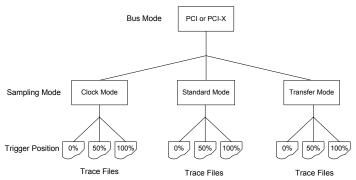

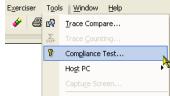

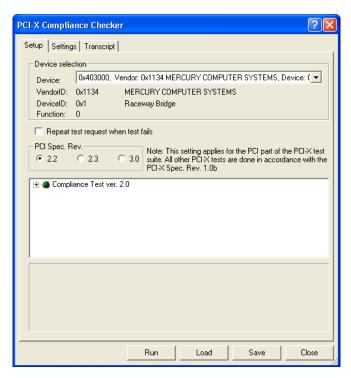

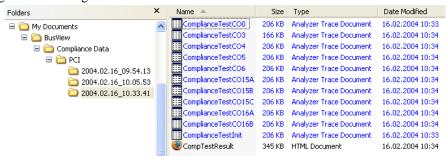

#### Arbiter