## Systran FHE6-FM6MWB04-00 SL240X CMC FPDP Card, 850 nm Laser

In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/72138-31

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

TECHNOLOGY CROUP

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# SL100X/SL240X Hardware Reference for Carrier and Rehostable CMC FPDP Cards

Document No. F-T-MR-S3FPDP##-A-0-A8

## **FOREWORD**

The information in this document has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. Curtiss-Wright Controls, Inc reserves the right to make changes without notice.

Curtiss-Wright Controls, Inc. makes no warranty of any kind with regard to this printed material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

©Copyright 2004, Curtiss-Wright Controls, Inc. All Rights Reserved. SL100/SL240 Dual-Port Memory FIFO U.S. Patent #6,259,648

Systran® is a registered trademark of Curtiss-Wright Controls, Inc. Systran Division.

\*\* is a registered trademark of Curtiss-Wright Controls, Inc.

FibreXtreme® is a registered trademark of Curtiss-Wright Controls, Inc.

LinkXchange® is a registered trademark of Curtiss-Wright Controls, Inc.

Any reference made within this document to equipment from other vendors does not constitute an endorsement of their product(s).

Revised: November 29, 2004

**Curtiss-Wright Controls Embedded Computing**

Data Communications 4126 Linden Avenue Dayton, OH 45432-3068 USA (800) 252-5601(U.S. only) (937) 252-5601

#### **FCC**

This product is intended for use in industrial, laboratory or military environments. This product uses and emits electromagnetic radiation, which may interfere with other radio and communication devices. The user may be in violation of FCC regulations if this device is used in other than the intended market environments.

#### CE

As a component part of another system, this product has no intrinsic function and is therefore not subject to the European Union CE EMC directive 89/336/EEC.

## **TABLE OF CONTENTS**

| 1. INTRO | ODUCTION                                                     | 1-1                |

|----------|--------------------------------------------------------------|--------------------|

|          | 1.1 How to Use This Manual                                   | 1-1                |

|          | 1.1.1 Purpose                                                |                    |

|          | 1.1.2 Scope                                                  |                    |

|          | 1.1.3 Style Conventions                                      |                    |

|          | 1.2 Related Information                                      |                    |

|          | 1.3 Quality Assurance                                        |                    |

|          | 1.4 Technical Support                                        |                    |

|          | 1.5 Ordering Process                                         | 1-4                |

| 2 PROD   | UCT OVERVIEW                                                 | 2-1                |

| 2.1100   | 2.1 Overview                                                 |                    |

|          | 2.2 SL240X Features                                          |                    |

|          | 2.2.1 Media Options                                          |                    |

|          | 2.3 SL240X Cards                                             |                    |

|          | 2.3.1 FPDP Card Features                                     |                    |

|          | 2.4 Applications                                             |                    |

|          | 2.4.1 LinkXchange LX2500 Crossbar Switch (LX2500)            |                    |

|          | 2.4.2 Typical Digital Signal Processing (DSP) Imaging System | 2-7<br>2-8         |

|          | 2.4.3 Extending FPDP                                         | 2-0<br>2-9         |

|          | 2.5 Topologies                                               |                    |

|          | 2.5.1 Typical Topologies                                     | 2-9<br>2-0         |

|          | 2.5.2 Point-to-point                                         | ر- <u>2</u><br>2 0 |

|          | 2.5.3 Chained.                                               |                    |

|          | 2.5.4 Single Master Ring                                     |                    |

|          | 2.5.5 Multiple Master Ring                                   |                    |

|          | 2.6 Status LEDs.                                             |                    |

|          | 2.6.1 "LINK UP" LED                                          |                    |

|          | 2.6.2 "MICRO," "RX OK," and "TX OK" LEDs                     |                    |

|          |                                                              |                    |

| 3. INSTA | ALLATION                                                     | 3-1                |

|          | 3.1 Installation Procedures                                  |                    |

|          | 3.2 Unpack the Card                                          | 3-1                |

|          | 3.3 Inspect the Card                                         |                    |

|          | 3.4 Install the Card                                         | 3-2                |

|          | 3.4.1 VME Card Installation                                  | 3-2                |

|          | 3.4.2 PCI FibreXtreme Carrier Card Installation              |                    |

|          | 3.4.3 Rehostable CMC Card Installation                       |                    |

|          | 3.5 Configure the Cards                                      |                    |

|          | 3.6 Connect the Cables                                       |                    |

|          | 3.6.1 FPDP Cables                                            |                    |

|          | 3.6.2 Fiber-optic Cables                                     |                    |

|          | 3.6.3 Copper Cables                                          | 3-5                |

|          | 3.7 Troubleshooting                                          | 3-6                |

| 4. OPER  | ATION                                                        | 4-1                |

| .,       | 4.1 Overview                                                 |                    |

|          | 4.2 Theory of operation                                      |                    |

|          | 4.2.1 Receive Operation                                      |                    |

|          | 4.2.2 Transmit Operation                                     |                    |

|          | 4.2.3 Loop Operation                                         |                    |

|          | 4.3 Data Synchronization                                     |                    |

|          | 4.4 Configuration Options                                    |                    |

|          | 4.4.1 Flow Control                                           | Δ-A                |

|          | 4.4.2 Loop Enable.                                           |                    |

|          | 4.4.3 Receiver/Transmitter Enable                            |                    |

|          | 4.4.4 CRC Generation/Checking                                |                    |

|          | 4.4.5 Stop on Link Error or /SYNC                            | Δ-A                |

|          | 4.4.6 Receive FIFO Threshold Interrupt.                      | 4-5                |

|          | 10 12001. The control interrupt                              | 1 3                |

## **APPENDICES**

| APPENDIX A – SPECIFICATIONS                                                                                                                                                                                                                           | A-1                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| APPENDIX B – REGISTER SET                                                                                                                                                                                                                             | B-1                      |

| APPENDIX C – CARRIER/CMC CONFIGURATION                                                                                                                                                                                                                | C-1                      |

| APPENDIX D – SL100X/SL240X PROTOCOL                                                                                                                                                                                                                   | D-1                      |

| APPENDIX E – ORDERING INFORMATION                                                                                                                                                                                                                     | E-1                      |

| APPENDIX F – FPDP PRIMER                                                                                                                                                                                                                              |                          |

| APPENDIX G – REHOSTABLE CMC FPDP INTERFACE                                                                                                                                                                                                            | G-1                      |

| GLOSSARY                                                                                                                                                                                                                                              | GLOSSARY-1               |

| INDEX                                                                                                                                                                                                                                                 | INDEX-1                  |

| FIGURES                                                                                                                                                                                                                                               |                          |

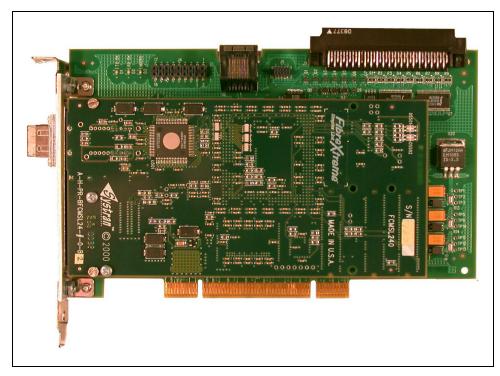

| Figure 2-1 SL240X Rehostable CMC Card                                                                                                                                                                                                                 |                          |

| Figure 2-2 NGSL VMER Card                                                                                                                                                                                                                             | 2-3                      |

| Figure 2-3 FXSL VMER Card                                                                                                                                                                                                                             |                          |

| Figure 2-4 DUAL VMER Card                                                                                                                                                                                                                             |                          |

| Figure 2-5 PCI FibreXtreme Carrier Card                                                                                                                                                                                                               |                          |

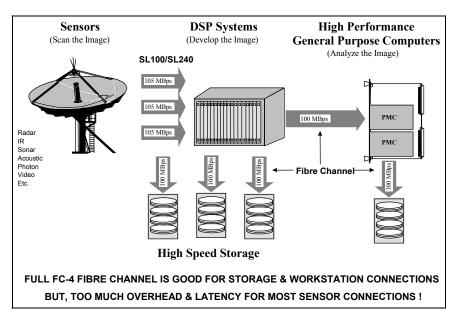

| Figure 2-6 Typical Applications of FibreXtreme SL240X in Advanced DSP Systems                                                                                                                                                                         | 2-8                      |

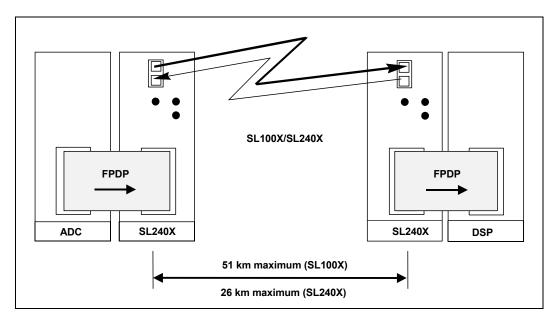

| Figure 2-7 FibreXtreme SL240X Extending FPDP                                                                                                                                                                                                          |                          |

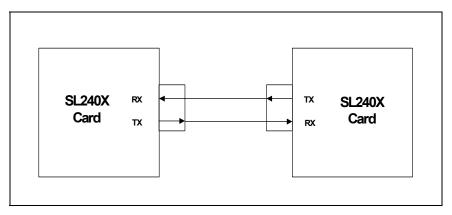

| Figure 2-8 Point-to-Point Topology                                                                                                                                                                                                                    |                          |

| Figure 2-9 Chained Topology                                                                                                                                                                                                                           |                          |

| Figure 2-10 Single Master Ring                                                                                                                                                                                                                        |                          |

| Figure 2-12 Status LEDs on SL240X VME and Rehostable CMC Cards                                                                                                                                                                                        |                          |

| Figure 2-13 Status LEDs on FXSL VMER and Rehostable CMC Card                                                                                                                                                                                          |                          |

| Figure 2-14 Status LEDs on Dual VMER and Rehostable CMC Cards                                                                                                                                                                                         |                          |

| Figure 2-15 Status LEDs on PCI FibreXtreme Carrier Card                                                                                                                                                                                               |                          |

| Figure 3-1 SL240 PCI Card Installation                                                                                                                                                                                                                |                          |

| Figure 3-2 FPDP Connectors                                                                                                                                                                                                                            |                          |

| Figure 3-3 Fiber-optic Simplex LC Connector                                                                                                                                                                                                           |                          |

| Figure 3-4 Fiber-optic Duplex LC Connector                                                                                                                                                                                                            |                          |

| Figure 3-5 HSSDC2 Copper Connector                                                                                                                                                                                                                    |                          |

| Figure 3-6 HSSDC2 Receptacle Contact Pin Locations                                                                                                                                                                                                    | 3-5                      |

| Table 2-1 NGSL VMER FPDP Transmitter Bus Speeds Table 2-2 FXSL VMER FPDP Transmitter Bus Speeds Table 2-3 Dual VMER FPDP Transmitter Bus Speeds Table 2-4 PCI FibreXtreme Carrier FPDP Transmitter Bus Speeds Table 2-5 Summary of FPDP Card Features | 2-5<br>2-6<br>2-6<br>2-7 |

| Table 3-1 HSSDC2 Receptacle Pin Assignments                                                                                                                                                                                                           | 3-5                      |

#### 1.1 How to Use This Manual

#### 1.1.1 Purpose

This manual describes the FibreXtreme SL100X/SL240X CMC FPDP card, and guides you through the process of unpacking, setting up, and using the card.

**NOTE:** Both the FibreXtreme SL100X and SL240X hardware are referred to throughout this manual as SL240X. The software that supports both the SL100X and SL240X hardware are also referred to as SL240X, including the driver and API. Anything that is exclusive to the SL100X or the SL240X is described as such.

#### 1.1.2 **Scope**

This manual contains the following information:

- An introduction to the FibreXtreme SL240X family of products.

- Applications and topologies for SL240X cards.

- Instructions for installing and configuring the cards.

- An operational overview of the product.

- General card specifications.

- Register set information.

- Configuration information.

- Summary of the protocol used by the SL240X cards.

- Ordering information for all products mentioned in this manual.

- A brief introduction to the Front Panel Data Port (FPDP) interface.

- Specifications for integrating the rehostable CMC FPDP card into an application.

- Definitions of words, phrases, and terms used in this manual.

- List of key words referenced in this manual.

The information in this manual is intended for information systems personnel, system coordinators, or highly skilled network users with at least a systems-level understanding of general computer processing, memory, and hardware operation.

## 1.1.3 Style Conventions

- Called functions are italicized. For example, *OpenConnect()*.

- Data types are italicized. For example, *int*.

- Function parameters are bolded. For example, **Action**.

- Path names are italicized. For example, *utility/sw/cfg*.

- File names are bolded. For example, **config.c**.

- Path file names are italicized and bolded. For example, *utility/sw/cfg/config.c*.

- Hexadecimal values are written with a "0x" prefix. For example, 0x7e.

- For signals on hardware products, an 'Active Low' is represented by prefixing the signal name with a slash (/). For example, /SYNC.

• Code and monitor screen displays of input and output are boxed and indented on a separate line. Text that represents user input is bolded. Text that the computer displays on the screen is not bolded. For example:

c:\>ls file1 file2 file3

• Large samples of code are Courier font, at least one size less than context, and are usually on a separate page or in an appendix.

#### 1.2 Related Information

- ANSI Z136.2-1988 American National Standard for the Safe Use of Optical Fiber Communication Systems Using Laser Diode and LED Sources.

- Draft Standard for a Common Mezzanine Card Family: CMC; IEEE P1386, Draft 2.0, April 4, 1995.

- Fibre Channel Association Product Information Bulletin Revision, December 9, 1994.

- Fibre Channel Physical and Signaling Interface (FC-PH), Revision 4.3, June 1, 1994; Produced by the ANSI X3T9.3 standards group.

- Fibre Channel Physical and Signaling Interface-2 (FC-PH-2), Revision 7.3, January 5, 1996; Produced by the ANSI X3T11 standards group.

- Fibre Channel Physical and Signaling Interface-3 (FC-PH-3), Revision 8.6, April, 1996; Produced by the ANSI X3T11 standards group.

- Front Panel Data Port Specifications, ANSI/VITA 17-1998, Revision 1.0; February 11, 1999. Produced by the VITA Standards Organization.

- Serial Front Panel Data Port (FPDP) ANSI/VITA 17.1–2003 Specifications. Produced by the VITA Standards Organization.

- *IEC 825-1984 Radiation Safety of Laser Products, Equipment Classification, Requirements, and User's Guide, 2 parts,* 1993.

- FibreXtreme SL100/SL240 Hardware Reference Manual for PCI, PMC, and CPCI Cards, (Doc. No. F-T-MR-S2PCIPMC), Curtiss-Wright Controls, Inc.

- LinkXchange LX1500e Crossbar Switch Hardware Reference Manual, (Doc. No. F-T-MR-LX1500E), Curtiss-Wright Controls, Inc.

- LinkXchange LX2500 Crossbar Switch Hardware Reference Manual, (Doc. No. F-T-MR-LX2500), Curtiss-Wright Controls, Inc.

- VITA http://www.vita.com/

- Curtiss-Wright Controls, Inc. http://cwcembedded.com/

## 1.3 Quality Assurance

Curtiss-Wright Controls policy is to provide our customers with the highest quality products and services. In addition to the physical product, the company provides documentation, sales and marketing support, hardware and software technical support, and timely product delivery. Our quality commitment begins with product concept, and continues after receipt of the purchased product.

Curtiss-Wright Controls' Quality System conforms to the ISO 9001 international standard for quality systems. ISO 9001 is the model for quality assurance in design, development, production, installation, and servicing. The ISO 9001 standard addresses all 20 clauses of the ISO quality system, and is the most comprehensive of the conformance standards.

Our Quality System addresses the following basic objectives:

- Achieve, maintain, and continually improve the quality of our products through established design, test, and production procedures.

- Improve the quality of our operations to meet the needs of our customers, suppliers, and other stakeholders.

- Provide our employees with the tools and overall work environment to fulfill, maintain, and improve product and service quality.

- Ensure our customer and other stakeholders that only the highest quality product or service will be delivered.

The British Standards Institution (BSI), the world's largest and most respected standardization authority, assessed Curtiss-Wright Controls' Quality System. BSI's Quality Assurance division certified we meet or exceed all applicable international standards, and issued Certificate of Registration, number FM 31468, on May 16, 1995. The scope of Curtiss-Wright Controls' registration is: "Design, manufacture and service of high technology hardware and software computer communications products." The registration is maintained under BSI QA's bi-annual quality audit program.

Customer feedback is integral to our quality and reliability program. We encourage customers to contact us with questions, suggestions, or comments regarding any of our products or services. We guarantee professional and quick responses to your questions, comments, or problems.

## 1.4 Technical Support

Technical documentation is provided with all of our products. This documentation describes the technology, its performance characteristics, and includes some typical applications. It also includes comprehensive support information, designed to answer any technical questions that might arise concerning the use of this product. We also publish and distribute technical briefs and application notes that cover a wide assortment of topics. Although we try to tailor the applications to real scenarios, not all possible circumstances are covered.

Although we have attempted to make this document comprehensive, you may have specific problems or issues this document does not satisfactorily cover. Our goal is to offer a combination of products and services that provide complete, easy-to-use solutions for your application.

If you have any technical or non-technical questions or comments, contact us. Hours of operation are from 8:00 a.m. to 5:00 p.m. Eastern Standard/Daylight Time.

• Phone: (937) 252-5601 or (800) 252-5601

• E-mail: support@systran.com

• Fax: (937) 252-1465

• World Wide Web address: <u>www.cwcembedded.com</u>

## 1.5 Ordering Process

To learn more about Curtiss-Wright Controls' products or to place an order, please use the following contact information. Hours of operation are from 8:00 a.m. to 5:00 p.m. Eastern Standard/Daylight Time.

• Phone: (937) 252-5601 or (800) 252-5601

• E-mail: info@systran.com

• World Wide Web address: www.cwcembedded.com

## 2. PRODUCT OVERVIEW

#### 2.1 Overview

The FibreXtreme SL240X cards provide fast, low latency point-to-point or broadcast connections between sensors and processing devices. The FPDP versions include a 6U VME or PCI-based solution with standard FPDP connectors, and a rehostable Common Mezzanine Card (CMC).

The CMC card provides this interface through a simple unidirectional parallel port. This port can be connected to existing FPDP equipment or can be integrated into new products (CMC). All of these variations interoperate completely on the link interface, providing seamless integration between diverse platforms.

#### 2.2 SL240X Features

SL240X provides reliable point-to-point or broadcast interconnects between systems, with minimal overhead and very low latency. The protocol involved for this transport is based on Fibre Channel, though it is not Fibre-Channel compliant. The major SL240X features are listed below:

- Uses proven 8B/10B encoding for data transmission.

- End-to-end throughput of 247 MBps with or without frame checksums (SL240X).

- End-to-end throughput of 105 MBps with or without frame checksums (SL100X).

- Minimizes implementation cost and enhances throughput by using a simple protocol.

- Provides built-in data synchronization with very little reduction in throughput.

- Integrated interrupt controller to report link failure, transaction completion, or buffer space request.

- Status LED that reports link stability.

- Loop operation with out-of-band arbitration or point-to-point operation.

- Provides a register set designed for easy programming and status retrieval.

- Four media options available—long-reach wavelength laser, long wavelength laser, short wavelength laser, and HSSDC2 copper.

- Watchdog timer for failover operation.

- 1 MB Receive FIFO.

- 2 KB Transmit FIFO.

- Rugged versions of some cards are available.

## 2.2.1 Media Options

There are four basic media options—a long wavelength laser (1300 nm), short wavelength laser (850 nm), and HSSDC2 copper. The long-reach wavelength laser is required for very long distances (10 km to 50 km). Long wavelength laser interconnections are recommended for intermediate distances (300 m to 10 km). The short wavelength version is useful for intrasystem connections, such as connecting between cards on the same backplane. It is also suited for short reach intersystem

connections (< 300 m). HSSDC interconnections are recommended for very short distances of 30 meters or less.

All cards use a Duplex LC style connector or HSSDC2 receptacle, available from most major cable manufacturers. For details concerning this connector, contact Curtiss-Wright Controls, Inc. Technical Support.

### 2.3 SL240X Cards

This section contains photographs of the SL240X CMC and VME FPDP cards.

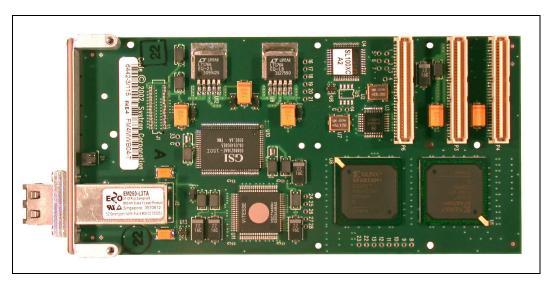

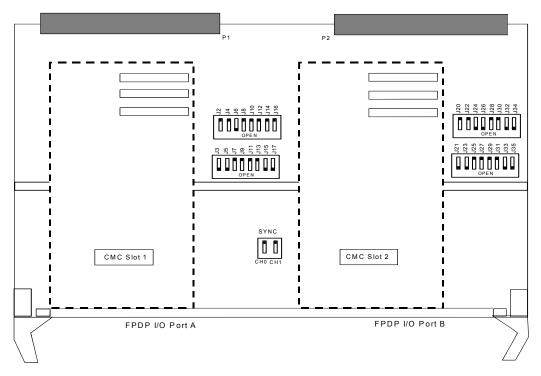

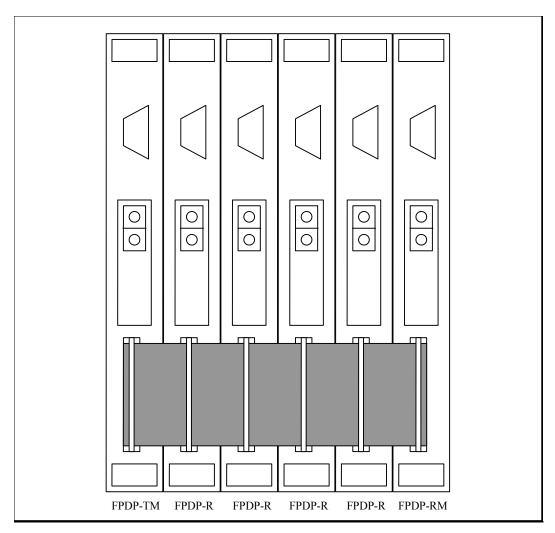

Figure 2-1 SL240X Rehostable CMC Card

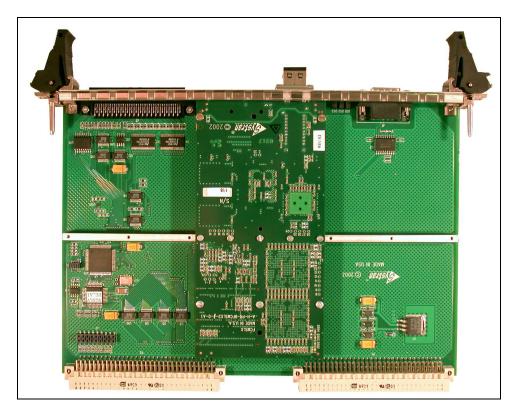

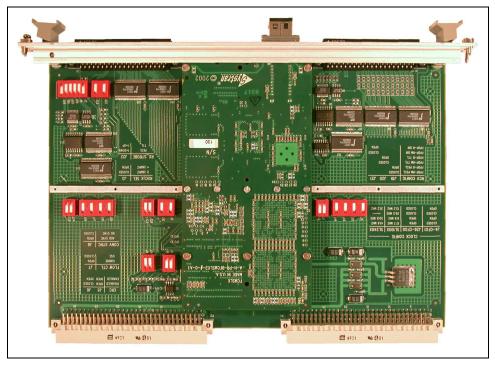

Figure 2-2 NGSL VMER Card

Figure 2-3 FXSL VMER Card

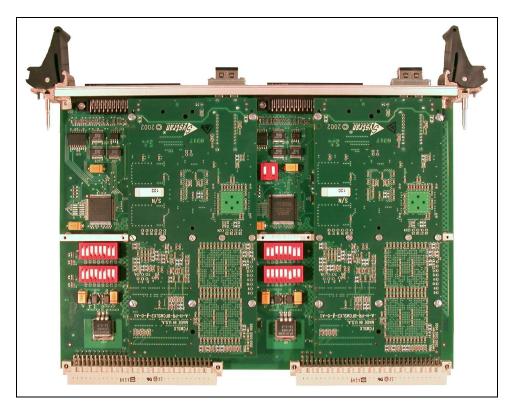

Figure 2-4 DUAL VMER Card

Figure 2-5 PCI FibreXtreme Carrier Card

#### 2.3.1 FPDP Card Features

The major features of the various FPDP cards are listed below. See Table 2-1 for a summary of all FPDP card features.

**NOTE:** The FPDP bus speeds are derived from the reference clock (53.125 MHz or 125 MHz) divided by 2, 3, 4, or 6.

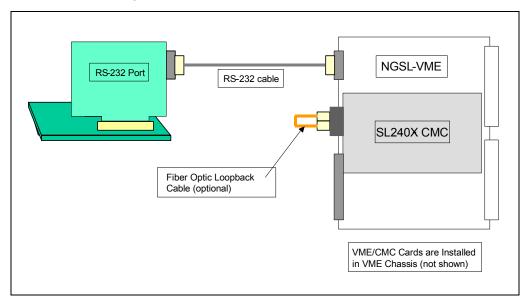

#### **NGSL VMER FPDP CARDS**

Sample Application: Useful for applications where it is desired to change the FPDP port data direction via software control and a 6U VME form factor is required.

#### Features:

- 6U VME form factor

- One FPDP port configurable for input or output

- Accepts one SL100X/SL240X CMC card

- Configurable using a microcontroller interface via an RS-232 port

- Offers access to SL100X/SL240X CMC card's register set

- Supports the following FPDP transmitter bus speeds

Table 2-1 NGSL VMER FPDP Transmitter Bus Speeds

| Reference Clock<br>Division Factor | SL100X<br>(53.125 MHz) | SL240X<br>(125 MHz) |  |

|------------------------------------|------------------------|---------------------|--|

| 2                                  | 26.5625 MHz            | 62.5000 MHz         |  |

| 3                                  | 17.7083 MHz            | 41.6667 MHz         |  |

| 4                                  | 13.2813 MHz            | 31.2500 MHz         |  |

| 6                                  | 8.8542 MHz             | 20.8333 MHz         |  |

#### **FXSL VMER FPDP CARD**

Sample Application: Useful for applications requiring bi-directional data flow on the link interface and two channels of FPDP data.

#### Features:

- 6U VME form factor

- Two FPDP ports (one input and one output)

- Accepts one SL100X/SL240X CMC card

- Does not offer access to SL100X/SL240X CMC card's register set

- Configurable using switches

- Supports the following FPDP transmitter bus speeds

Table 2-2 FXSL VMER FPDP Transmitter Bus Speeds

| Reference Clock<br>Division Factor | SL100X<br>(53.125 MHz) | SL240X<br>(125 MHz) |  |

|------------------------------------|------------------------|---------------------|--|

| 2                                  | 26.5625 MHz            | 62.5000 MHz         |  |

| 3                                  | 17.7083 MHz            | 41.6667 MHz         |  |

| 4                                  | 13.2813 MHz            | 31.2500 MHz         |  |

| 6                                  | 8.8542 MHz             | 20.8333 MHz         |  |

#### **DUAL VMER FPDP CARDS**

Sample Application: Useful for applications requiring two channels of FPDP data but having a limited number of available VME slots.

#### Features:

- 6U VME form factor

- Two independent FPDP ports configurable for input or output (one FPDP port per CMC card)

- Accepts one or two SL100X/SL240X CMC cards

- Does not offer access to SL100X/SL240X CMC card's register set

- Configurable using switches

- Supports the following FPDP transmitter bus speeds

Table 2-3 Dual VMER FPDP Transmitter Bus Speeds

| Reference Clock<br>Division Factor | SL100X<br>(53.125 MHz) | SL240X<br>(125 MHz) |  |

|------------------------------------|------------------------|---------------------|--|

| 2                                  | 26.5625 MHz            | 62.5000 MHz         |  |

| 3                                  | 17.7083 MHz            | 41.6667 MHz         |  |

| 4                                  | 13.2813 MHz            | 31.2500 MHz         |  |

| 6                                  | 8.8542 MHz             | 20.8333 MHz         |  |

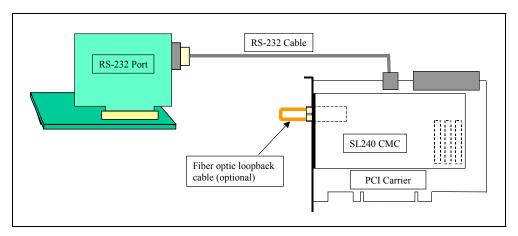

#### PCI FIBREXTREME CARRIER CARD

Sample Application: Useful for applications where it is desired to change the FPDP port data direction via software control and a PCI form factor is required.

#### Features:

- PCI form factor

- One FPDP port configurable for input or output

- Accepts one SL100X/SL240X CMC card

- Configurable using a microcontroller interface via an RS-232 port

- Offers access to SL100X/SL240X CMC card's register set

- Supports the following FPDP transmitter bus speeds

Table 2-4 PCI FibreXtreme Carrier FPDP Transmitter Bus Speeds

| Reference Clock<br>Division Factor | SL100X<br>(53.125 MHz) | SL240X<br>(125 MHz) |  |

|------------------------------------|------------------------|---------------------|--|

| 2                                  | 26.5625 MHz            | 62.5000 MHz         |  |

| 3                                  | 17.7083 MHz            | 41.6667 MHz         |  |

| 4                                  | 13.2813 MHz            | 31.2500 MHz         |  |

| 6                                  | 8.8542 MHz             | 20.8333 MHz         |  |

Table 2-5 Summary of FPDP Card Features

| Features                              | Carrier Card    |                  |                  |                 |

|---------------------------------------|-----------------|------------------|------------------|-----------------|

| reatures                              | NGSL VMER       | <b>FXSL VMER</b> | <b>Dual VMER</b> | PCI             |

| Number of FPDP Ports                  | 1               | 2                | 2                | 1               |

| Number of CMC Cards                   | 1               | 1                | 2                | 1               |

| Configuration Method                  | Microcontroller | Switches         | Switches         | Microcontroller |

| Form Factor                           | 6UVME           | 6UVME            | 6UVME            | PCI             |

| CMC Cards Supported                   |                 |                  |                  |                 |

| SL100X                                | Yes             | Yes              | Yes              | Yes             |

| SL240X                                | Yes             | No               | Yes              | Yes             |

| Register Set Access                   |                 |                  |                  |                 |

| Carrier Card                          | Yes             | No               | No               | Yes             |

| CMC Card                              | Yes             | No               | No               | Yes             |

| FPDP Transmitter Bus Speeds Supported |                 |                  |                  |                 |

| SL100X                                |                 |                  |                  |                 |

| 26.5625 MHz                           | Yes             | Yes              | Yes              | Yes             |

| 17.7083 MHz                           | Yes             | Yes              | Yes              | Yes             |

| 13.2813 MHz                           | Yes             | Yes              | Yes              | Yes             |

| 8.8542 MHz                            | Yes             | Yes              | Yes              | Yes             |

| SL240X                                |                 |                  |                  |                 |

| 62.5000 MHz                           | Yes             | Yes              | Yes              | Yes             |

| 41.6667 MHz                           | Yes             | Yes              | Yes              | Yes             |

| 31.2500 MHz                           | Yes             | Yes              | Yes              | Yes             |

| 20.8333 MHz                           | Yes             | Yes              | Yes              | Yes             |

## 2.4 Applications

SL240X cards can be used in a variety of topologies for a variety of applications. The following sections detail typical topologies used and some applications. Many other applications are possible in these configurations.

## 2.4.1 LinkXchange LX2500 Crossbar Switch (LX2500)

Curtiss-Wright Controls' LX2500 Crossbar Switch provides the following features:

- Up to 32 non-blocking media-specific I/O ports.

- Up to 2.5 Gbps/port baud rate (port card dependent).

- Support for multiple point-to-point, loop, and broadcast communication links simultaneously.

- Automatic I/O Port fault isolation.

- Multiple media options.

- Out-of-band control through an RS-232 port.

- Can be connected to a modem and controlled from a remote location.

For more detailed information regarding LX2500 features and operation, contact Curtiss-Wright Controls and request a copy of the *LinkXchange LX2500 Crossbar Switch Hardware Reference Manual* or visit our web site.

### 2.4.2 Typical Digital Signal Processing (DSP) Imaging System

With the support for 1.0625 Gbps or 2.5 Gbps link transmission rates between interconnected subsystems, SL240X is ideal for use in many of today's high-throughput data transfer applications. One example is shown in Figure 2-6. This figure shows the SL100X's usable data throughput rate. However, the figure is also applicable to SL240X by changing the data throughput rate to 247 MBps.

Figure 2-6 Typical Applications of FibreXtreme SL240X in Advanced DSP Systems

#### 2.4.3 Extending FPDP

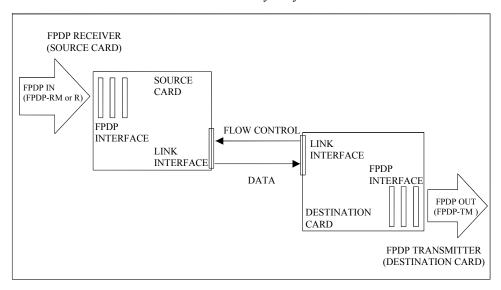

The maximum allowable length for FPDP cables ranges from 1 m to 5 m depending upon its configuration. The FibreXtreme SL240X system provides a communication link that extends the reach of FPDP while retaining simplicity, high bandwidth, and reliability. This concept is shown in Figure 2-7. The type of transceiver used determines the distance the FPDP cards can be separated. See section 2.2.1, Media Options, for details on transceivers. Using fiber optics provides electrical isolation.

Figure 2-7 FibreXtreme SL240X Extending FPDP

## 2.5 Topologies

## 2.5.1 Typical Topologies

There are four typical topologies for the SL240X card. These topologies should cover most customer applications, though if another topology is desired contact Curtiss-Wright Controls Technical Support to see if it is possible. The topologies are:

- Point-to-point

- Chained

- Single Master Loop

- Multiple Master Loop

#### 2.5.2 Point-to-point

The point-to-point topology is the native mode for the SL240X card. One user option available in this mode is if flow control is used. If flow control is used, the transmitter on each end will not transmit when the remote receiver is telling it to back off or the receive fiber is missing. In this mode, the maximum amount of data that can be transferred is 247 MBps per direction (in this case, both cards are receiving and transmitting 247 MBps at the same time). The maximum distance between the nodes is 26 km.

There are many applications for the point-to-point topology—as long as it involves only two nodes, this topology covers it. One advantage that point-to-point has over the other topologies is the ability to do simultaneous bi-directional traffic.

Figure 2-8 Point-to-Point Topology

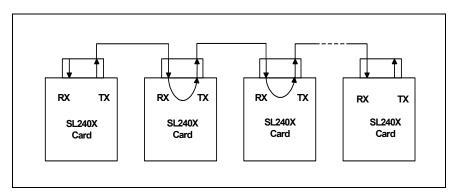

#### 2.5.3 Chained

This topology is a single transmitter on the end of a long string of receivers. No flow control is available in this topology, and the distance between the nodes is limited only by the transceivers used (10 km typical, 26 km maximum).

This topology is good for broadcasting data to multiple destinations where late data is of no use, such as video transmission applications.

Figure 2-9 Chained Topology

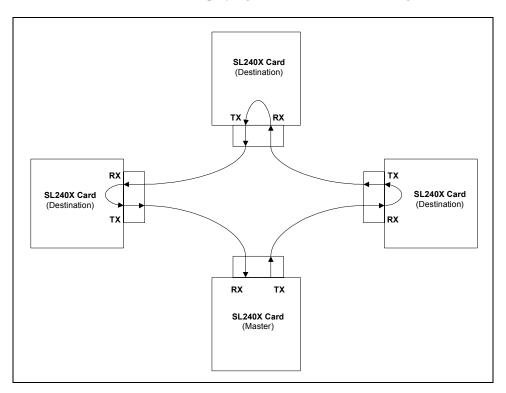

#### 2.5.4 Single Master Ring

This is one of the most useful topologies for the SL240X card. This topology allows a single transmitter to send data to a group of destinations with flow control from all of the destinations. Note that this flow control is a single flag to the master—either it can send or it cannot send data. This means that if one destination has a failure and stops removing data from its Receive FIFO, it should be switched out to avoid bringing down the loop. A Crossbar Switch suitable for this purpose, the LinkXchange LX2500 Crossbar Switch, is available from Curtiss-Wright Controls, Inc. Software controls mastership switching of the ring. There are rules associated with master switching listed in the "Programming Interface" section. The flow control used in this case is similar to a multi-drop FPDP bus, where any receiver can back the transmitter off.

This is the typical configuration for record-playback systems, where you have multiple signal processors and data storage elements present on the network and there is only one node (the data source or the recorder playing the data back) transmitting at a time.

Figure 2-10 Single Master Ring

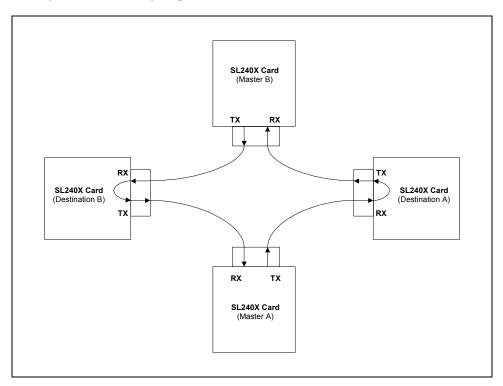

#### 2.5.5 Multiple Master Ring

This is another form of ring topology, where there are multiple masters on the ring, and these masters have to receive data as well as transmit data to the next master. In the most complex case, each node is a master, which means that it receives data from the previous master and sends data to the next master. No flow control is allowed in this topology for rings above two nodes, and the data cannot be passed through masters unless control guarantees that there is at least one source-only node on the ring, and that no two masters will transmit at the same time. Single master rings should temporarily become multiple master rings when switching loop masters.

Figure 2-11 Multiple Master Ring

## 2.6 Status LEDs

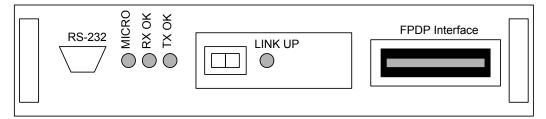

#### 2.6.1 "LINK UP" LED

All of the SL240X cards are equipped with a link status indicator LED. This LED is labeled "LINK UP" and is visible through the card's faceplate. When this LED is lit, it indicates a signal is present on the receiver. This LED gives no indication of the validity of the signal, only that a signal is present.

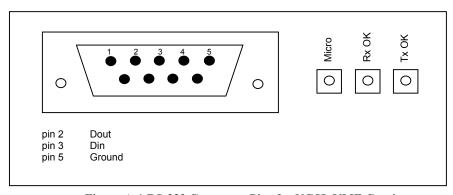

#### 2.6.2 "MICRO," "RX OK," and "TX OK" LEDs

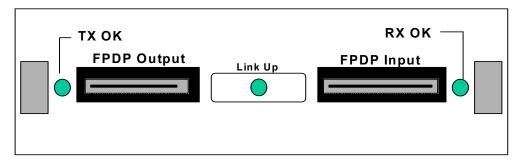

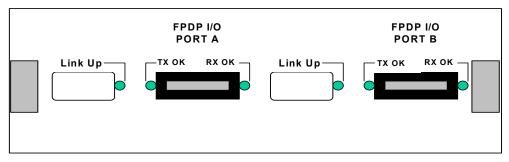

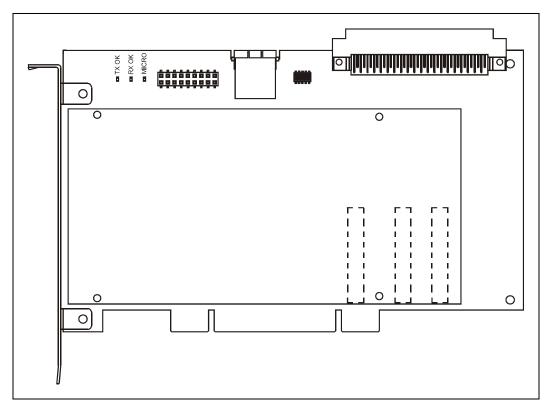

The NGSL VMER card has three status LEDs. The FXSL VMER card has two status LEDs. The Dual VMER card has four status LEDs. These LEDs viewed from the front end of the card are shown in Figures 2-11, 2-12 and 2-13. The PCI FibreXtreme Carrier card has three LEDs. These LEDs viewed from the component side of the card are shown in Figure 2-14.

The LED labeled "MICRO" is currently not used and will remain unlit.

When the LED labeled "RX OK" is lit, it indicates no errors have occurred on the FPDP receive interface or the link transmit interface. When this LED is not lit, the link interface is down and flow control is not ignored.

When the LED labeled "TX OK" is lit, it indicates no errors have occurred on the FPDP transmit interface or the link receive interface. When this LED is not lit, any one of the following errors have occurred:

- Receive FIFO overflow.

- The link interface is down.

- CRC error.

- 8B/10B decoding error.

Figure 2-12 Status LEDs on SL240X VME and Rehostable CMC Cards

Figure 2-13 Status LEDs on FXSL VMER and Rehostable CMC Card

Figure 2-14 Status LEDs on Dual VMER and Rehostable CMC Cards

Figure 2-15 Status LEDs on PCI FibreXtreme Carrier Card

## 3. INSTALLATION

## 3.1 Installation Procedures

Each FibreXtreme VME FPDP card requires only one slot on the VME host backplane The PCI FibreXtreme Carrier card requires one PCI slot. A FibreXtreme SL240X rehostable CMC FPDP card requires only one slot on your custom-designed carrier.

To install the SL240X card, follow the steps below:

- 1. Unpack the card.

- 2. Inspect the card.

- 3. Install the card.

- 4. Configure the card.

- 5. Connect the cables.

## 3.2 Unpack the Card

**CAUTION:** Exercise care regarding the static environment. Use an anti-static mat connected to a wristband when handling or installing the SL240X card. Failure to do this may cause permanent damage to the components on the card.

Follow the steps below to unpack the card:

- 1. Put on a wristband attached to an anti-static mat.

- 2. Remove the card and anti-static bag from the carton.

- 3. Place the bag on the anti-static mat.

- 4. Open the anti-static bag and remove the card.

- 5. In the unlikely event you need to return your SL240X card, please keep the original shipping materials for this purpose.

Any optional equipment is shipped in separate cartons.

## 3.3 Inspect the Card

Each FibreXtreme FPDP card consists of a single card with a built-in link interface and FPDP interface. A FibreXtreme SL240X rehostable CMC FPDP card consists of a single card with a built-in link interface. If the card was damaged in shipping, notify Curtiss-Wright Controls or your supplier immediately.

## 3.4 Install the Card

**WARNING**: Before installing any peripheral component into a computer, ensure the system is powered off.

#### 3.4.1 VME Card Installation

To install the VME card:

- 1. Insert the card into the VME backplane until it is firmly seated.

- 2. Install the screws to fasten the card in place.

#### 3.4.2 PCI FibreXtreme Carrier Card Installation

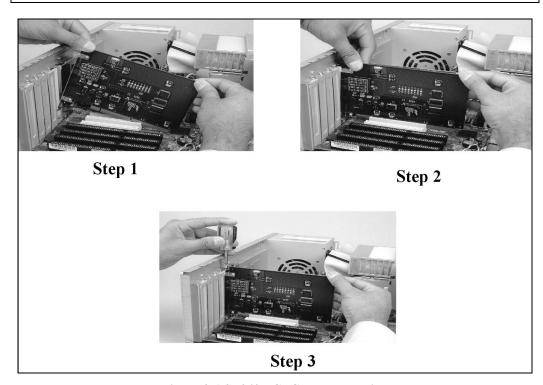

To install the PCI FibreXtreme Carrier card, push the card into the mother card, as shown in Figure 3-1, steps 1 and 2, until it is firmly seated. Install the mounting screw as shown in step 3.

**NOTE:** The PCI FibreXtreme Carrier card only uses +5 volt power and ground from the PCI bus. As a result, it can be plugged into any PCI/PCI-X slot (3.3 or 5 volt) and will also have no impact on PCI/PCI-X bus throughput.

Figure 3-1 SL240 PCI Card Installation

#### 3.4.3 Rehostable CMC Card Installation

Since the SL240X CMC FPDP card was designed to be rehostable, the installation procedures depend upon the user's design.

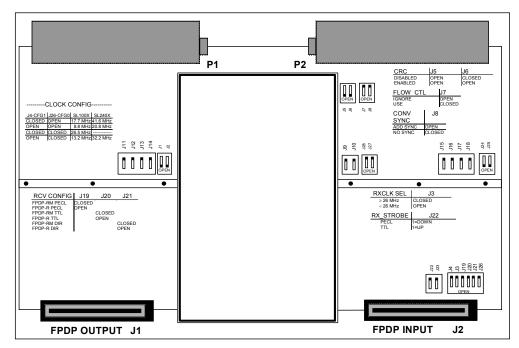

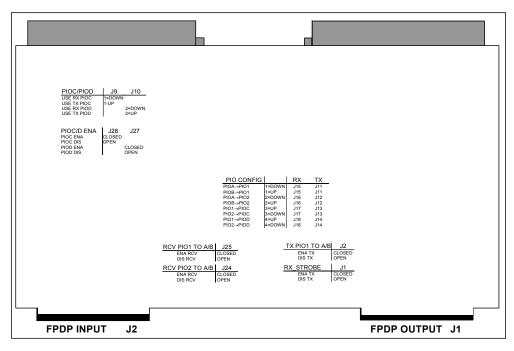

## 3.5 Configure the Cards

See Appendix C, CARRIER/CMC Configuration, for configuration instructions.

#### 3.6 Connect the Cables

#### 3.6.1 FPDP Cables

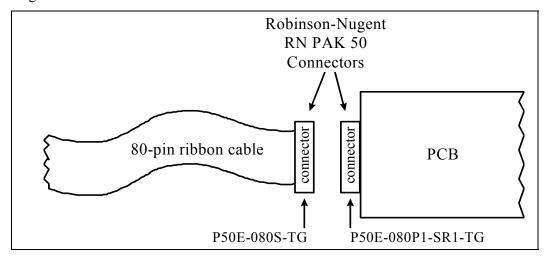

The FPDP cables are ribbon cables with 80-pin Robinson-Nugent RN PAK-50 latching, high-density socket connectors at each end. Robinson-Nugent's part number for the ribbon cable connector is: P50E-080S-TG. Curtiss-Wright Controls uses the Robinson-Nugent P50E-080P1-SR1-TG connector on the SL240X VME FPDP card.

Figure 3-2 FPDP Connectors

**NOTE:** Curtiss-Wright Controls, Inc. does not provide the FPDP cables. Please use the Robinson-Nugent connector (part number: P50E-080S-TG) to make your own cable set or contact the appropriate cable vendor to acquire the cable set you desire.

## 3.6.2 Fiber-optic Cables

The two factors to consider when connecting the cables are the topology and the transmission media used. There are several different topologies the cards can be connected in, depending on your application. See section 2.5 for more detailed examples of topologies.

#### **Fiber-optic Cable Precautions**

**CAUTION:** Fiber-optic cables are made of glass and may break if crushed or bent in a loop with less than a 2-inch radius.

Look at the cable ends closely before inserting them into the connector. If debris is inserted into the transmitter/receiver connector, it may not be possible to clean the connector out and could result in damage to the transmitter or receiver lens. Hair, dirt, and dust can interfere with the light signal transmission.

Use an alcohol-base wipe to clean the cable ends.

For short wavelength laser modules, either a 50  $\mu$ m or 62.5  $\mu$ m core diameter cable should be used. A 62.5  $\mu$ m cable can be used for distances up to 300 m. 50  $\mu$ m cable allows distances up to 500 m. For distances greater than 500 m (up to 10 km), long wavelength laser modules with 9  $\mu$ m core cable should be used.

The optional fiber-optic cables may be shipped in a separate carton. Remove the rubber boots on the fiber-optic transmitters and receivers as well as the ones on the fiber-optic cables. These rubber boots should be replaced when cables are not in use or in the event the node must be returned to the factory. Attach the fiber-optic cables to the connectors on the SL240X card.

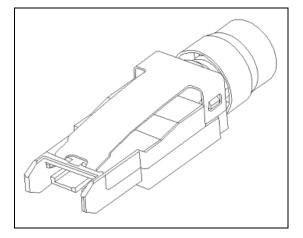

Figure 3-3 and Figure 3-4 depict the types of fiber-optic connectors needed for the SL240X card.

Figure 3-3 Fiber-optic Simplex LC Connector

Figure 3-4 Fiber-optic Duplex LC Connector

#### 3.6.3 Copper Cables

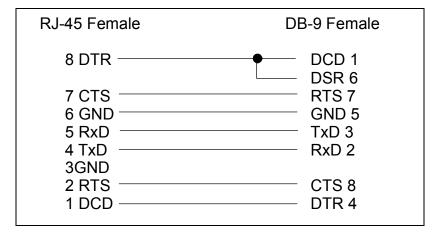

The copper media interface on the SL100X/SL240X cards support shielded cable, terminated with HSSDC2 style connectors, shown in Figure 3-5. Figure 3-6 displays the HSSDC2 SFP receptacle used on the SL100X/SL240X cards. This figure indicates the HSSDC2 contact pin locations and Table 3-1 contains the pin assignments.

PIN #7

Figure 3-5 HSSDC2 Copper Connector

Figure 3-6 HSSDC2 Receptacle Contact Pin Locations

Table 3-1 HSSDC2 Receptacle Pin Assignments for SL100

| Pin Number | Pin Description |  |  |

|------------|-----------------|--|--|

| 1          | Ground          |  |  |

| 2          | Receive -       |  |  |

| 3          | Receive +       |  |  |

| 4          | Ground          |  |  |

| Pin Number | Pin Description |  |  |

|------------|-----------------|--|--|

| 5          | Transmit +      |  |  |

| 6          | Transmit -      |  |  |

| 7          | Ground          |  |  |

Table 3-2 HSSDC2 Receptacle Pin Assignments for SL240

| Pin Number | Pin Description |

|------------|-----------------|

| 1          | Ground          |

| 2          | Receive +       |

| 3          | Receive -       |

| 4          | Ground          |

| 5          | Transmit -      |

| 6          | Transmit +      |

| 7          | Ground          |

To insure data integrity, take care when selecting the appropriate HSSDC2 cable assembly for the SL100X/SL240X application. Application data rate and the presence of equalization circuits determine length boundaries for HSSDC2 cable assemblies. Application operating at 2.5 Gbps must use equalized 100 Ohm HSSDC2 cables for cable lengths greater than 5 meters. However, applications operating at 1.0625 Gbps must use equalized 150 Ohm HSSDC2 cables when cable lengths exceed 15 meters.

**NOTE:** The HSSDC2 cables are not interchangeable due to different keying.

## 3.7 Troubleshooting

If the system does not boot correctly, power down the machine, reseat the card, double-check cable connections, and turn the system back on. If problems persist, contact Curtiss-Wright Controls Technical Support at (800) 252-5601 or support@systran.com for assistance.

Please be prepared to supply the following information:

| Machine:            |          |  |  |

|---------------------|----------|--|--|

| OS Name:            |          |  |  |

| OS Version:         |          |  |  |

| Card Type:          |          |  |  |

| Card Serial #:      |          |  |  |

| Software Part #:    |          |  |  |

| Software S/N:       |          |  |  |

| Problem Reproduc    | ibility: |  |  |

| Problem Description | on:      |  |  |

#### 4.1 Overview

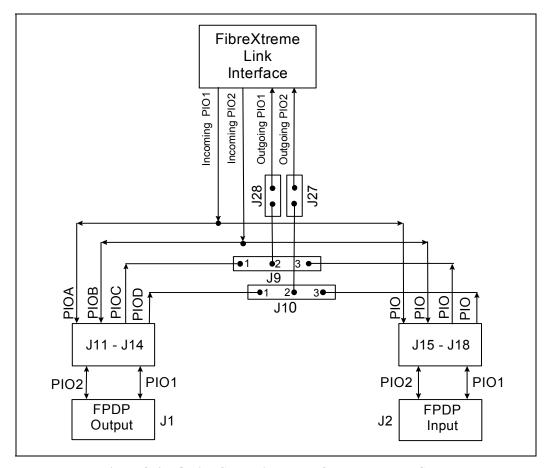

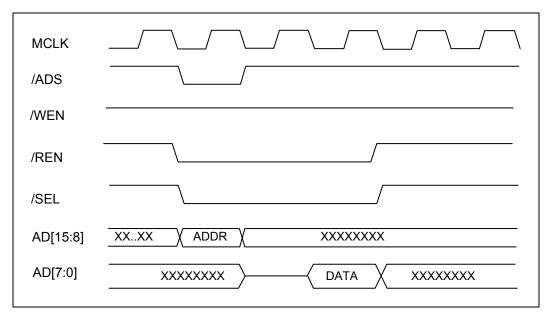

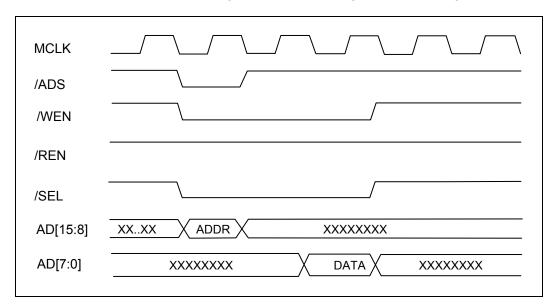

SL100X/SL240X cards move data with very low latency between a host interface and a 1.0625 Gbps or a 2.5 Gbps link, respectively. The host interfaces available is an FPDP-like proprietary interface. The advantage of the FPDP-like interface is that it requires very simplistic hardware to interface.

**CAUTION**: Do **not** break the link between two SL100X/SL100X cards. The unpredictable results may affect your system. While the FPGA can recover from link break scenarios, the corresponding link and data errors caused by disruption of the link must be adequately addressed by the host interface.

**NOTE:** It is not possible for the SL100X and SL240X cards to communicate/operate with each other on the link because the link speeds are not compatible.

## 4.2 Theory of operation

The operation of SL240X cards is simple—take data from the host bus interface and transmit it across a link, or take data from the link and pass it to the host bus interface. The link protocol involved is kept minimal to reduce the latency and improve throughput, while still providing a set of useful features for users to customize their applications. The hardware is designed to offer many different features for advanced applications, while maintaining a simple interface to the most commonly used features.

**NOTE:** For further explanation of terms used in the following sections, consult the FPDP Primer located in Appendix F.

#### 4.2.1 Receive Operation

The SL240X card has several options for receiving data. The most basic option is no loop operation with data receive enabled. In this case, data is:

- 1. Received from the link.

- 2. Decoded by the card.

- 3. Placed in the Receive FIFO.

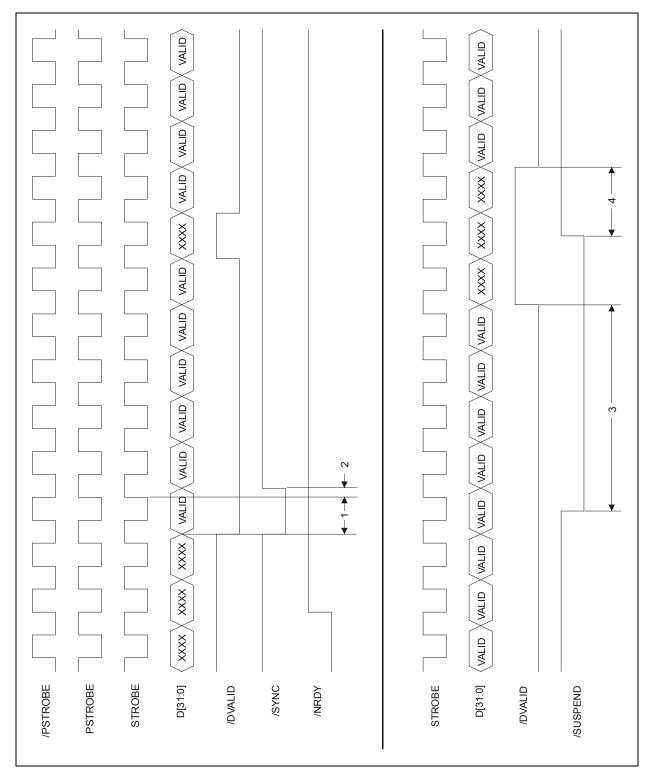

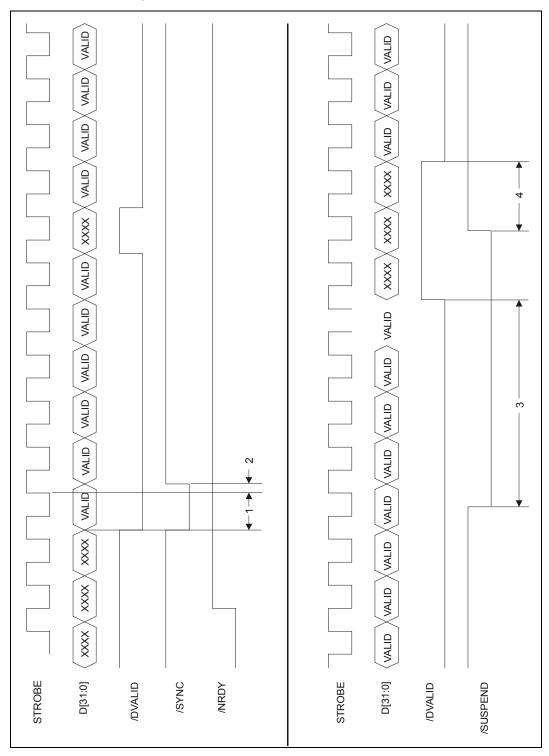

At this point, the operation depends on the host interface. If it is an FPDP based card, and /SUSPEND is not asserted, the card asserts /DVALID and proceeds to transmit the data on the FPDP interface. If /SUSPEND or /NRDY is asserted, then the data waits in the Receive FIFO until these signals go away.

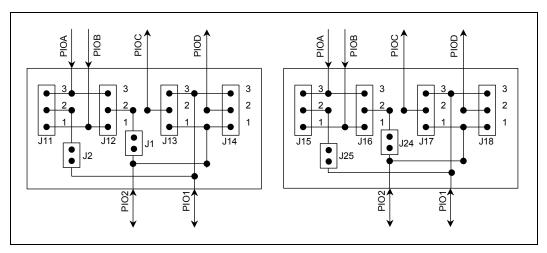

FPDP signals are embedded into the control words of a frame. The FPDP signals transported across are: /NRDY, /DIR, /SYNC, PIO1 and PIO2. A /SUSPEND signal is synthesized by the transmit state machine in response to how full the Receive FIFO is – this is not the /SUSPEND from an FPDP port.

All FPDP signals, with the exclusion of /SYNC, are passed around the Receive FIFO and are not synchronized with the data stream.

#### 4.2.2 Transmit Operation

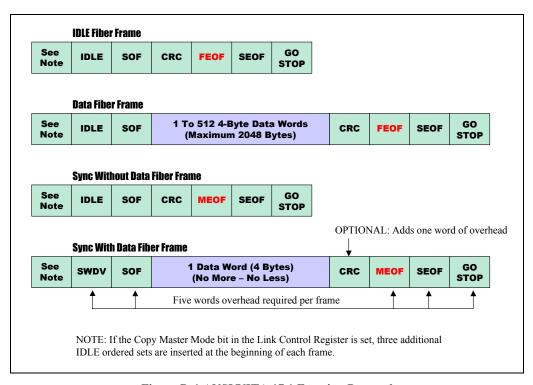

The transmit operation first has to collect data in the Transmit FIFO for transmission. FPDP cards collect any data words accompanied by /DVALID on the FPDP interface. Once a data word is in the FIFO, transmission can begin. The framing state machine first checks that there is no data in the Retransmit FIFO and that the remote node is not telling this node to back off. If it is clear to send, after it transmits the next SOF it begins filling the data frame as full as possible (up to 2048 bytes). The data is then encoded and sent out across the link. If there is data in the Retransmit FIFO or the card is being backed off from the destination, then the card waits until both conditions are clear before it starts transmission. Note that SYNC and SWDV can also be transmitted by the link logic and these two types of synchronization primitives are handled by the Transmit FIFO and transmit control logic in a similar method as standard data. Specifically, they are written to the link logic through the same interface, passed through the same internal link logic path, and are used in the assembly of link frames in a similar fashion, although the maximum frame size does differ for these types of associated Serial FPDP frames.

All FPDP signals, with the exclusion of /SYNC, are passed around the Transmit FIFO and are not synchronized with the data stream. For PCI variations of this card, the FPDP signals can be written to a register and then transmitted across the link.

#### 4.2.3 Loop Operation

In the Loop Operation discussion below, SL100X/SL240X is used generically to refer to any Curtiss-Wright Controls SL100X/SL240X card. Anything that applies to only a specific SL100X/SL240X product will be noted as such.

Loop operation with the SL100X/SL240X acts like a virtual FPDP bus where one source (the loop master) can transmit to any number of receive nodes. The link protocol is the same for this operation, except any node in the loop may assert a suspend request embedded in this data stream. This implies if one node on the loop is not ready to receive data, the source is backed off for all nodes. This is the same way that multi-drop FPDP busses function.

The fundamental difference between a loop master and a receiving node is the loop master does not have its loop retransmission enabled. So, to the loop master, it appears as if it is still in a point-to-point connection with a single node. Receiving nodes, on the other hand, have knowledge that they are in a loop configuration and must be configured as such. Note that the loop master receives all the data it transmits, so data can either be checked for errors or ignored when it is received. This checking (beyond verification of CRC and 8B/10B decoding validity) is not done in the SL100X/SL240X and must be implemented by the system designer.

The receivers on the loop can choose to collect the data or ignore it off the loop. If the Receive FIFO is enabled (the node is collecting data), a suspend request may be asserted by this node as the data passes through. If it is not configured to receive the data, it simply passes the data through the Retransmit FIFO without modifying the suspend request.

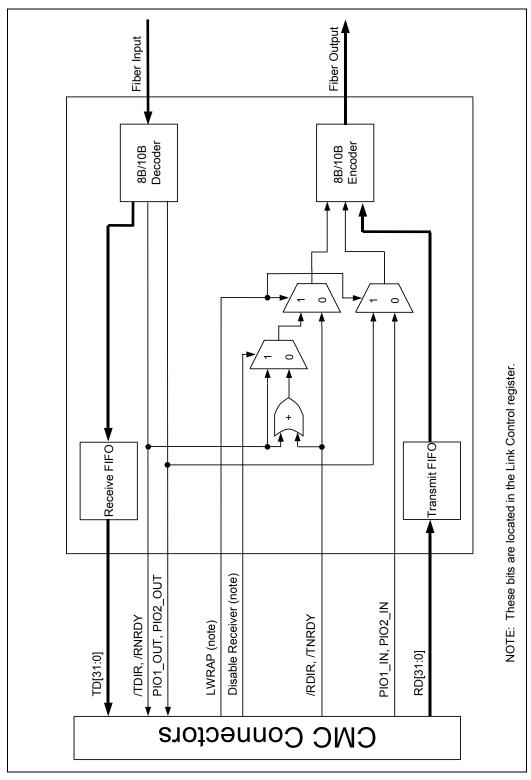

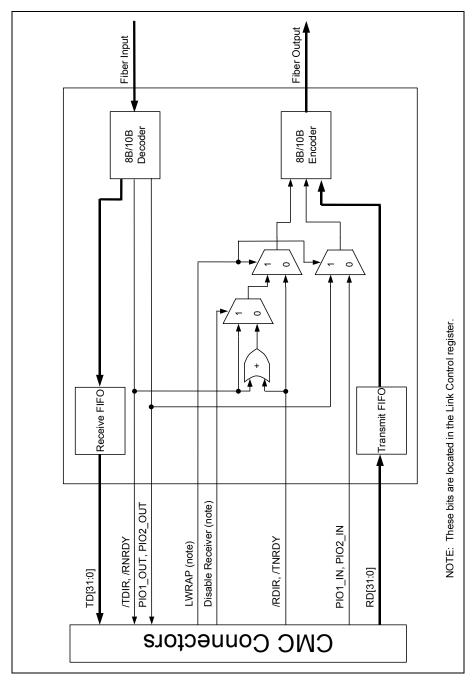

Serial FPDP supports the DIR, NRDY, PIO1, and PIO2 FPDP signals. These signals do not propagate through the Transmit FIFO or the Receive FIFO and thus cannot be directly associated with the corresponding data. To guarantee a pulse on these signals is

propagated to the remote Serial FPDP receiver, the pulse width from the host-bus interface must be equal to or greater than the maximum Serial FPDP frame length (512 words of data with an overhead of nine ordered sets). The use of these signals is host-specific and will now be explained for each SL100X/SL240X product.

For SL100X/SL240X CMC cards, the values of PIO1 and PIO2 are retransmitted according to their received link values and the values of DIR and NRDY are used as follows: if the receive interface is enabled, the values transmitted are the received link values logically ORed with the FPDP host-interface values; otherwise, the values are retransmitted according to their received link values. NRDY received from the link translates to /NRDY output from the FPDP receiver (FPDP-RM or FPDP-R) port. Thus, reception of NRDY from the link interface may be used to back off the FPDP transmitter, depending of the usage of /NRDY used by the respective FPDP transmit master.

Curtiss-Wright Controls' SL100X/SL240X CMC cards, when functioning as a FPDP transmit master, will stop the transmission of FPDP data when /NRDY is asserted by the FPDP receiver. The receipt of a suspend request will indirectly back off the FPDP transmitter, as the link logic no longer transmits link data, the link Transmit FIFO will back up, which will eventually back off the FPDP transmitter via the assertion of the /SUSPEND signal. The values of these four signals (PIO1, PIO2, DIR, and NRDY) sent to and received from the link are placed on the FPDP bus and also in the register set, if applicable. If placed in the register set, they can be accessed by a microcontroller via the optional microcontroller interface on the CMC carrier. The use of DIR and NRDY is consistent with the use of flow control (retransmission of a STOP request) for loop operation. See the ANSI/VITA 17.1 Serial FPDP specification for additional details.

Note that NRDY as a Serial FPDP signal has no direct impact on the operation of the link logic. Rather, NRDY is simply passed through the link logic and its function is dependent on the respective host interface. The Serial FPDP flow control (implemented via suspend requests which are also known as STOP ordered sets) is used by the link logic and does not directly affect the interface between the link logic and host interface.

**NOTE:** One node on the loop MUST be in non-loop operation in order for loop operation to work correctly. One node needs to remove the data from the loop. When switching masters on the loop, both the previous master and the next master should be in non-loop operation before the previous master switches into loop mode.

## 4.3 Data Synchronization

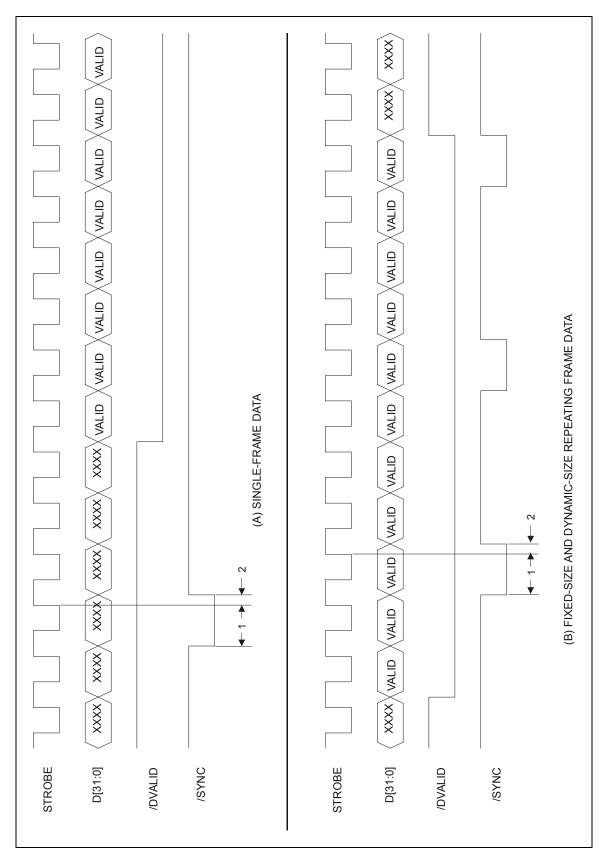

There is a data synchronization primitive, called SYNC, which is sent across the link under user control. This primitive is used to synchronize with the data stream. On the FPDP card, this signal is the /SYNC line on the FPDP interface.

Unless a non-intelligent device is used, such as a sensor, which cannot insert a periodic SYNC, SYNC should always be used to segment data transfers. It has little impact on system performance and will provide a mechanism to synchronize the send and receive operations via the link. This synchronization process is especially useful at application start-up, after error conditions, and is also useful to verify the error-free flow of data during normal operation.

## **4.4 Configuration Options**

There are many different configuration options available which affect the operation of the SL240X card. Most of these options are configured in the Link Control register (described in Appendix B).

#### 4.4.1 Flow Control

Flow control allows a Serial FPDP receiver to throttle the data stream from a Serial FPDP transmitter. If this option is turned off, the card continues to send data even when the receiver signals for it to stop or when the link is down.

In almost every application, flow control should be enabled. Even if the application must sustain maximum link throughput, it is better to drop the data at the sending source should the system experience a temporary overload condition. Some exotic conditions could apply where flow control is not desirable, but they require very careful system planning and should be confirmed with Curtiss-Wright Controls prior to architectural finalization. One possible exception is for applications that cannot use a duplex fiber-optic link, which means status information (link up and state of flow control) is not available from the remote node. In this circumstance, disable flow control to allow the transmitter to function without the receiver connected normally.

#### 4.4.2 Loop Enable

The loop enable option allows the SL240X card to transmit the Serial FPDP received data stream again. Turning on the loop enable implies that this node is designated as a receiver in the current configuration.

#### 4.4.3 Receiver/Transmitter Enable

The transmitter and receiver enable bits in the Link Control register turn off the transmit and receive Serial FPDP data streams, respectively. Neither affects the loop operation, so data is still retransmitted if the loop operation is enabled. This makes these options useful for record/playback systems where you wish to merely retransmit the data received without processing it. The receive enable is useful for disabling the Receive FIFO for the master in loop operation so that the data sent is not received.

## 4.4.4 CRC Generation/Checking

The CRC Generation/Checking option allows the SL240X card to detect data transmission errors. The card is not capable of correcting the errors—error correction is left to application level design.

A single bit controls both generation and checking. CRC should be used in almost all applications. It offers excellent coverage of data errors and has very little impact on link throughput for maximum frame sizes. The option of disabling CRC is only retained for compatibility with older third-part devices. Both nodes on the link (or all nodes in a loop configuration) should be set to a common CRC mode or the resulting mismatch will cause data errors and/or link errors.

## 4.4.5 Stop on Link Error or /SYNC

There are two DMA stop conditions available to the user—stop on link error and stop on /SYNC. The stop on link error stops the DMA engine from removing data from the Receive FIFO when there is a link error, such as the link going down. The stop on /SYNC

option allows you to stop data from being received from the Receive FIFO when a /SYNC without /DVALID is received on the output.

### 4.4.6 Receive FIFO Threshold Interrupt

SL240X cards can be configured to interrupt the host when the FIFO passes a certain threshold, allowing for efficient PIO transactions out of the Receive FIFO. This is particularly important on data storage systems, where you do not want to remove data from the FIFO until you have a full block of data to transmit. One of four different thresholds (not empty, ½ full, ½ full, ¾ full) can be selected through the control registers.

This page intentionally left blank

4-6

### **APPENDIX A**

### **SPECIFICATIONS**

### **TABLE OF CONTENTS**

| A.1 Overview                                             | A-1          |

|----------------------------------------------------------|--------------|

| A.2 NGSL VMER FPDP Card Specifications                   | A-1          |

| A.3 FXSL VMER FPDP Card Specifications                   | A-1          |

| A.4 Dual VMER FPDP Card Specifications                   | A-2          |

| A.5 Rehostable CMC FPDP Card Specifications              | A-2          |

| A.6 PCI FibreXtreme Carrier Card Specifications          | A-3          |

| A.7 Ruggedized CMC Environmental Specifications          | A-4          |

| A.1.7 Rugged Level 1                                     | A-4          |

| A.2.7 Rugged Level 2                                     | A-5          |

| A.8 FPDP Connector Pin Assignments                       | A-6          |

| A.9 RS-232 Pin-out for NGSL VME Carrier                  | A-6          |

| A.10 RS-232 Pin-out on PCI FibreXtreme Carrier           | A-7          |

| A.11 Media Interface Specifications                      | A-8          |

| A.1.11 SL100X Fiber-Optic Media Interface Specifications | A-8          |

| A.2.11 SL240X Fiber-Optic Media Interface Specifications |              |

| A.3.11 SL100X HSSDC2 Copper Media Interface              | A <b>-</b> 9 |

| A 4.11 SL.240X HSSDC2 Copper Media Interface             | A-9          |

#### A.1 Overview

This section shows the general card specifications of the FibreXtreme SL100X/SL240X VME and rehostable CMC FPDP cards and FPDP connector pin assignments.

**NOTE:** "Peak" current requirements represent a measured maximum for a typical card. Measurements were taken while the card was transmitting and receiving large buffers of data. "Average" current requirements represent a measured maximum for a card that is powered on but is not transmitting or receiving any data.

### A.2 NGSL VMER FPDP Card Specifications

| Hardware Compatibility:              | ANSI/IEEE Std. 1014-1987                |

|--------------------------------------|-----------------------------------------|

| Physical Dimensions:                 | 6.30 x 9.17 inches (160 x 233 mm)       |

| Weight:                              | ≈ 0.5 lb.                               |

| Electrical Requirements:             |                                         |

| SL100X                               | +5 VDC, 1.8 Amps Peak, 1.6 Amps Average |

| SL240X                               | +5 VDC, 2.2 Amps Peak, 2.0 Amps Average |

| Operating Temperature Range:         | 0° to +50°C                             |

| Mean Time Between Failure (MTBF)*:   |                                         |

| SL100X, Short wavelength laser:      | 199,174 hours (22.7 years)              |

| SL100X, Long wavelength laser:       | 199,015 hours (22.7 years)              |

| SL100X, Long-reach wavelength laser: | 158,709 hours (18.1 years)              |

| SL240X, Short wavelength laser:      | 199,174 hours (22.7 years)              |

| SL240X, Long wavelength laser:       | 199,015 hours (22.7 years)              |

| SL240X, Long-reach wavelength laser: | 156,844 hours (17.9 years)              |

| VME Carrier without CMC card:        | 402,589 hours (46.0 years)              |

| Storage Temperature Range:           | 40° to +85°C                            |

| Maximum FPDP Node Separation:        | 1 to 5 m (application dependent)        |

|                                      |                                         |

### A.3 FXSL VMER FPDP Card Specifications

| Physical Dimensions: 6.30 x 9.17 inches (160 x 233 mm)  Weight: $\approx$ 0.5 lb.  Electrical Requirements: +5 VDC, 1.7 Amps Peak, 1.5 Amps Average |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical Requirements:                                                                                                                            |

| *                                                                                                                                                   |

| SL100X +5 VDC, 1.7 Amps Peak, 1.5 Amps Average                                                                                                      |

| r                                                                                                                                                   |

| SL240X+5 VDC, 2.1 Amps Peak, 1.8 Amps Average                                                                                                       |

| Operating Temperature Range:                                                                                                                        |

| Mean Time Between Failure (MTBF)*:                                                                                                                  |

| SL100X, Short wavelength laser:                                                                                                                     |

| SL100X, Long wavelength laser:                                                                                                                      |

| SL100X, Long-reach wavelength laser: 145,389 hours (16.6 years)                                                                                     |

| SL240X, Short wavelength laser: 178,635 hours (20.4 years)                                                                                          |

| SL240X, Long wavelength laser:                                                                                                                      |

| SL240X, Long-reach wavelength laser: 143,822 hours (16.4 years)                                                                                     |

| VME Carrier without CMC card:326,669 hours (37.3 years)                                                                                             |

Storage Temperature Range: .....-40° to +85°C Maximum FPDP Node Separation: ...... 1 to 5 m (application dependent)

### A.4 Dual VMER FPDP Card Specifications

Hardware Compatibility: ANSI/IEEE Std. 1014-1987 Physical Dimensions: 6.30 x 9.17 inches (160 x 233 mm) Weight:  $\approx 0.5 \text{ lb}.$ **Electrical Requirements:** SL100X ......+5 VDC, 3.1 Amps Peak, 2.9 Amps Average Mean Time Between Failure (MTBF)\*: SL100X, Short wavelength laser: ...... 111,943 hours (12.8 years) SL100X, Long-reach wavelength laser: ......... 87,007 hours (9.9 years) SL240X, Short wavelength laser: ...... 111,943 hours (12.8 years) SL240X, Long-reach wavelength laser: ....... 85,887 hours (9.8 years) Storage Temperature Range: -40° to +85°C Maximum FPDP Node Separation: ............................... 1 to 5 m (application dependent)

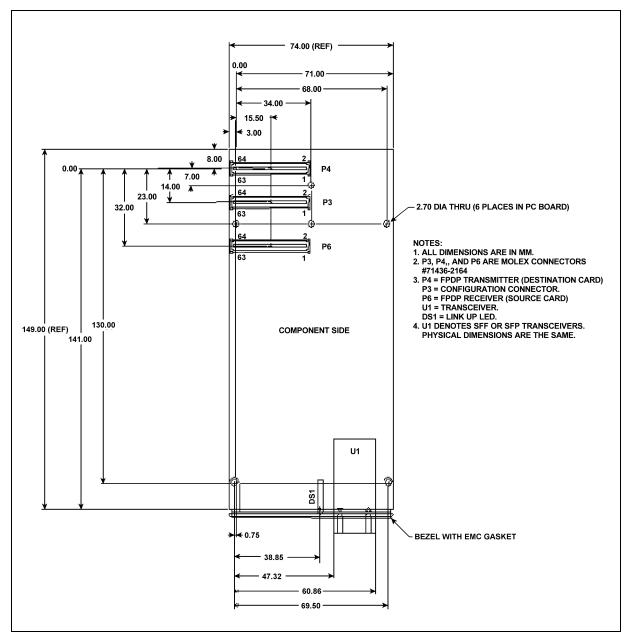

### A.5 Rehostable CMC FPDP Card Specifications

Weight:  $\approx 0.25 \text{ lb}.$ Component Density: 90% (max) Power Dissipation: Electrical Requirements: Operating Temperature Range: ...... 0° to +50° C Mean Time Between Failure (MTBF)\*: SL100X, Long-reach wavelength laser: ....... 261,992 hours (29.9 years) SL240X, Long-reach wavelength laser: ....... 256,949 hours (29.3 years) Storage Temperature Range: -40° to +85° C

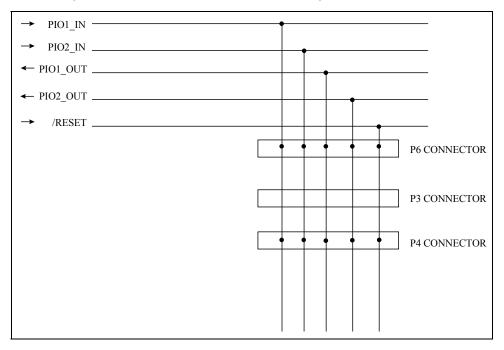

<sup>\*</sup>SL100X/SL240X CMC cards do not require 5 VDC. However, Curtiss-Wright Controls recommends supplying 5 VDC to P4 and P6 connectors.

### **A.6 PCI FibreXtreme Carrier Card Specifications**

| Physical Dimensions:                 | 174.6 x 106.7 mm                 |

|--------------------------------------|----------------------------------|

| Weight:                              | ≈ 0.40 lbs                       |

| Operating Voltage:                   | 4.75 V to 5.25 V                 |

| Electrical Requirements:             |                                  |

| SL100X                               | +5 VDC, TBD Amps Peak, TBD Amps  |

|                                      | Average                          |

| SL240X                               | +5 VDC, TBD Amps Peak, TBD Amps  |

|                                      | Average                          |

| Operating Temperature Range:         | $+0^{\circ}$ to $+50^{\circ}$ C  |

| Mean Time Between Failure (MTBF)*:   |                                  |

| SL100X, Short wavelength laser:      | 197,309 hours (22.5 years)       |

| SL100X, Long wavelength laser:       | 197,153 hours (22.5 years)       |

| SL100X, Long-reach wavelength laser: | 157,523 hours (18.0 years)       |

| SL240X, Short wavelength laser:      | 197,309 hours (22.5 years)       |

| SL240X, Long wavelength laser:       | 197,153 hours (22.5 years)       |

| SL240X, Long-reach wavelength laser: | 155,685 hours (17.8 years)       |

| PCI FibreXtreme Carrier              |                                  |

| without CMC card:                    | 395,042 hours (45.1 years)       |

| Storage Temperature Range:           | 40° to +85°C                     |

| Maximum FPDP Node Separation:        | 1 to 5 m (application dependent) |

<sup>\*</sup>The MTBF numbers are based on calculations using MIL-HDBK-217F, Appendix A; and Bellcore 332, Issue 6, for a ground-benign environment.

### A.7 Ruggedized CMC Environmental Specifications

The SL100X/SL240X products are offered at three different ruggedization levels. These levels are Standard, Rugged Level 1, and Rugged Level 2. Standard level operation specifications are defined in Sections A.1 of Appendix A. The specifications for Rugged Level 1 and Rugged Level 2 are defined in the following sections.

Current SL100X/SL240X standard and ruggedized products are listed in Appendix E.

#### A.7.1 Rugged Level 1

| Temperature Range: |                                                                            |

|--------------------|----------------------------------------------------------------------------|

| Operating          | -10° to +70° C                                                             |

| Storage            | -40° to +85°C                                                              |

| Humidity Range:    |                                                                            |

| Operating          | 0% to 95% (noncondensing)                                                  |

| Storage            | 0% to 95% (noncondensing)                                                  |

| Altitude:          |                                                                            |

| Operating          | 25,000 ft steady; rapid decompression to 40,000 ft                         |

| Storage            | 25,000 ft                                                                  |

| Vibration:         |                                                                            |

| Sine               | 10 g peak<br>10 Hz to 2 kHz                                                |

| Random             | .04 g <sup>2</sup> /Hz<br>10 Hz to 2 kHz<br>-6 dB/octave<br>1 kHz to 2 kHz |

| Shock              | 20 g peak ½ sine wave 11 ms duration                                       |

| Airflow            | 300 LFM                                                                    |

| Conformal Coating  | Acrylic HumiSeal 1B31*                                                     |

\* Ruggedized cards are coated with HumiSeal 1B31 acrylic conformal coating. This coating is qualified to MIL-I-46058C, Type AR. More detailed information on the coating can be found at the HumiSeal website <a href="http://www.humiseal.com/">http://www.humiseal.com/</a>.

#### A.7.2 Rugged Level 2

Temperature Range:

Operating  $-40^{\circ}$  to  $+85^{\circ}$  C Storage  $-40^{\circ}$  to  $+85^{\circ}$  C

**Humidity Range:**

Altitude:

to 40,000 ft

Vibration:

10 Hz to 2 kHz

Random .....  $1 g^2/Hz$

10 Hz to 2 kHz -6 dB/octave 1 kHz to 2 kHz

Shock 30 g peak

½ sine wave 11 ms duration

Conformal Coating...... Acrylic HumiSeal 1B31\*

FPDP Ribbon Cable ...... The 80-pin FPDP ribbon cable must **not** exceed 12 inches for Rugged Level 2 environments

\*\* For SL240X Longwave: 600 LFM

<sup>\*</sup> Ruggedized cards are coated with HumiSeal 1B31 acrylic conformal coating. This coating is qualified to MIL-I-46058C, Type AR. More detailed information on the coating can be found at the HumiSeal website <a href="http://www.humiseal.com/">http://www.humiseal.com/</a>.

### A.8 FPDP Connector Pin Assignments

The FPDP connector pin assignments are shown in Table A-1. These assignments are the normal (non-inverted) connector pin assignment for the FPDP interface described in Table 2 of the *Front Panel Data Port Specifications*, ANSI/VITA 17-1998. Cable conductor numbers are shown in parenthesis. Pin 1 is adjacent to the connector index mark.

| Pin | Row A    |      | Row E  | 3    | Row C    |      | Rov | w D  |

|-----|----------|------|--------|------|----------|------|-----|------|

| 1   | GND      | (1)  | STROBE | (2)  | GND      | (3)  | GND | (4)  |

| 2   | GND      | (5)  | GND    | (6)  | /NRDY    | (7)  | GND | (8)  |

| 3   | /DIR     | (9)  | GND    | (10) | RESERVED | (11) | GND | (12) |