#### Systran SCRAMNet SC150 **VME6U Module**

In Stock

Used and in Excellent Condition

**Open Web Page**

https://www.artisantg.com/67433-24

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

Your definitive source for quality pre-owned equipment.

**Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# SCRAMNet + Network

# SC150 VME6U Hardware Reference

Document No. D-T-MR-VME6U###-A-0-A9

# **FOREWORD**

The information in this document has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. Systran reserves the right to make changes without notice.

Systran makes no warranty of any kind with regard to this printed material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

©Copyright 2003 Systran Corporation. All Rights Reserved.

SCRAMNet® is a registered trademark of Systran Corporation. U.S. Patent # 4,928,289.  $VAX^{TM}$  and  $VMS^{TM}$  are trademarks of DIGITAL Equipment Corporation.

UNIX® is a registered trademark of UNIX System Laboratories, Inc., a wholly owned subsidiary of Novell, Inc.

ST<sup>®</sup> is a registered trademark of AT&T.

Revised: November 3, 2003

**Systran Corporation** 4126 Linden Avenue Dayton, OH 45432-3068 USA (800) 252-5601 (U.S. only) (937) 252-5601

#### **FCC**

This product is intended for use in industrial, laboratory or military environments. This product uses and emits electromagnetic radiation, which may interfere with other radio and communication devices. The user may be in violation of FCC regulations if this device is used in other than the intended market environments.

### CE

As a component part of another system, this product has no intrinsic function and is therefore not subject to the European Union CE EMC directive 89/336/EEC.

# **TABLE OF CONTENTS**

| 1. INTR | ODUCTION                                 | 1-1 |

|---------|------------------------------------------|-----|

|         | 1.1 How To Use This Manual               | 1-1 |

|         | 1.1.1 Purpose                            |     |

|         | 1.1.2 Scope                              | 1-1 |

|         | 1.1.3 Style Conventions                  |     |

|         | 1.2 Related Information.                 | 1-1 |

|         | 1.3 Quality Assurance                    | 1-2 |

|         | 1.4 Technical Support                    |     |

|         | 1.5 Ordering Process                     | 1-3 |

| 2. SCRA | AMNET NETWORK                            | 2-1 |

|         | 2.1 Overview                             | 2-1 |

|         | 2.2 Shared Memory                        |     |

|         | 2.2.1 Dual Port Memory Controller        |     |

|         | 2.2.2 Control/Status Registers (CSRs)    |     |

|         | 2.2.3 Virtual Paging                     | 2-3 |

|         | 2.3 FIFO Buffers.                        | 2-3 |

|         | 2.3.1 Transmit FIFO                      | 2-3 |

|         | 2.3.2 Transceiver FIFO                   | 2-3 |

|         | 2.3.3 Interrupt FIFO                     | 2-3 |

|         | 2.3.4 Receiver FIFO                      |     |

|         | 2.4 Network Ring.                        |     |

|         | 2.4.1 Protocol                           | 2-4 |

|         | 2.5 Auxiliary Control RAM (ACR)          |     |

|         | 2.6 Interrupts                           |     |

|         | 2.6.1 Network Interrupt WRITEs           |     |

|         | 2.6.2 Selected Interrupt                 |     |

|         | 2.6.3 Forced Interrupt.                  | 2-8 |

|         | 2.7 External Triggers.                   |     |

|         | 2.8 General Purpose Counter/Global Timer | 2-8 |

|         | 2.9 LED Status Indicators.               | 2-8 |

|         | 2.10 Modes of Operation                  |     |

|         | 2.10.1 Data Filter Mode                  | 2-9 |

|         | 2.10.2 High Performance (HIPRO) Mode     | 2-9 |

|         | 2.10.3 VME Holdoff Mode                  |     |

|         | 2.10.4 Loopback Modes                    |     |

|         | 2.10.5 Write-Me-Last Mode                |     |

| 3. PROI | DUCT OVERVIEW                            |     |

|         | 3.1 Overview                             |     |

|         | 3.1.1 Network Features                   |     |

|         | 3.1.2 Options                            |     |

|         | 3.1.3 VME6U Board Features               |     |

|         | 3.2 VMEbus Specification Level           | 3-2 |

|         | 3.3 Addressing Compatibility             |     |

|         | 3.3.1 Memory                             |     |

|         | 3.3.2 Control/Status Registers           |     |

|         | 3.4 Data Transfer Capability             | 3-3 |

|         | 3.4.1 Memory                             |     |

|         | 3.4.2 I/O                                |     |

|         | 3.5 Interrupt Capability                 |     |

|         | 3.6 P1 and P2 Connectors.                |     |

|         | 3.7 Utility Software                     |     |

|         | 3.7.1 SCRAMNet Diagnostics               |     |

|         | 3.7.2 EEPROM Initialization (EPI)        |     |

|         | 3.7.3 SCRAMNet Monitor                   |     |

|         | 3.8 Options                              | 3-4 |

|               | 3.8.1 Electronic Bypass Switch              |              |

|---------------|---------------------------------------------|--------------|

|               | 3.8.2 Quad Switch.                          |              |

|               | 3.8.3 Cabinet Kit                           | 3-5          |

| A INSTALLATIO | ON                                          | 1 1          |

|               |                                             |              |

|               | allation Procedures                         |              |

| 4.2 Unp       | back the Board                              | 4-2          |

| 4.3 Visi      | ually Inspect the Board                     |              |

|               | 4.3.1 SIMM Connections                      |              |

|               | 4.3.2 Check Media Card Connection (J302)    | 4-2          |

|               | 4.3.3 J8/P2 Connection.                     | 4-4          |

| 4.4 Exte      | ernally Configure the Board                 |              |

|               | 4.4.1 EEPROM                                |              |

|               | 4.4.2 CSR Address Switches                  |              |

|               | 4.4.3 Resolution Bus Switch (S8)            |              |

|               | 4.4.4 Software Compatibility (SW_CMPT) (J2) | 4-6          |

|               | 4.4.5 Memory Configuration (J3)             |              |

|               | 4.4.6 Variable Length Enable (VL_EN) (J4)   |              |

|               | 4.4.7 Ground Jumper (J6)                    |              |

|               | 4.4.8 External Trigger Connections.         | 4-8          |

| 45 Inst       | all the Board                               |              |

|               | ect Cabling Options                         |              |

| 7.0 3010      | 4.6.1 Cabinet Kit Connection                |              |

|               | 4.6.2 Fiber-Optic Configuration.            | 7-1<br>1.10  |

|               | 4.6.3 Coaxial Cable Configuration.          |              |

|               | 4.6.4 Fiber-optic Cables                    | 4-10<br>4 10 |

|               | 4.6.5 Fiber-optic Connection                |              |

| 4.7 Inst      |                                             |              |

| 4. / IIISU    | all Fiber Optic Bypass Switch (Optional)    |              |

| 4 O I         | 4.7.1 Auxiliary Connection.                 |              |

| 4.8 Inte      | rnally Configure the Board                  |              |

|               | 4.8.1 Node Identification                   |              |

|               | 4.8.2 Network Time-out                      |              |

| 400           | 4.8.3 Memory                                | 4-14         |

| 4.9 Byte      | e Swapping                                  | 4-14         |

| 4.10 Tr       | oubleshooting                               |              |

|               | 4.10.1 Other H/W Considerations             |              |

|               | 4.10.2 Customer Support                     | 4-15         |

| 5 OPERATION   |                                             | 5-1          |

|               |                                             |              |

|               | erview                                      |              |

| 5.2 Sha       | red Memory                                  |              |

|               | 5.2.1 Virtual Paging                        |              |

|               | 5.2.2 Memory Considerations                 | 5-3          |

|               | 5.2.3 Control/Status Registers.             |              |

|               | alization                                   |              |

|               | ic Send/Receive Configuration               |              |

| 5.5 Net       | work Ring                                   |              |

|               | 5.5.1 Message Contents                      |              |

|               | 5.5.2 Protocol                              |              |

|               | 5.5.3 Performance                           |              |

|               | 5.5.4 Throughput                            |              |

|               | tiliary Control RAM                         |              |

| 5.7 Inte      | rrupt Controls                              |              |

|               | 5.7.1 Interrupt Options                     | 5-9          |

| 5.8 Inte      | rrupt Conditions                            |              |

|               | 5.8.1 Network Data WRITE                    |              |

|               | 5.8.2 Network Error                         | 5-14         |

|               | 5.8.3 Interrupt Handling                    |              |

| 5.9 Exte      | ernal Triggers                              |              |

|               | eneral Purpose Counter/Timer                |              |

|               | 5.10.1 Available Modes.                     |              |

|               | 5.10.2 Rollover/Reset                       |              |

|               | 5.10.3 Presetting Values                    |              |

|               | odes of Operation                           |              |

| 5.11.1 Data Filter        | 5-17 |

|---------------------------|------|

| 5.11.2 HIPRO Mode         | 5-19 |

| 5.11.3 Loopback Modes     | 5-20 |

| 5.11.4 Node Insert Mode   |      |

| 5.11.5 VME Holdoff Mode   | 5-26 |

| 5.11.6 Write-Me-Last Mode |      |

| 5 12 Quad Switch          | 5-28 |

# **APPENDICES**

| APPENDIX A. SPECIFICATIONS     | A-1        |

|--------------------------------|------------|

| APPENDIX B. CSR DEFINITIONS    | B-1        |

| APPENDIX C. CSR SUMMARY        |            |

| APPENDIX D. HOST ACCESS TIMING | D-1        |

| APPENDIX E. CABINET KIT        | E-1        |

| APPENDIX F. CONFIGURATION AIDS | F-1        |

| GLOSSARY                       | GLOSSARY-1 |

| INDEX                          | INDEX-1    |

# **FIGURES**

| Figure 2-1 Functional Diagram                   | 2-2  |

|-------------------------------------------------|------|

| Figure 2-2 ACR/Memory Access                    | 2-5  |

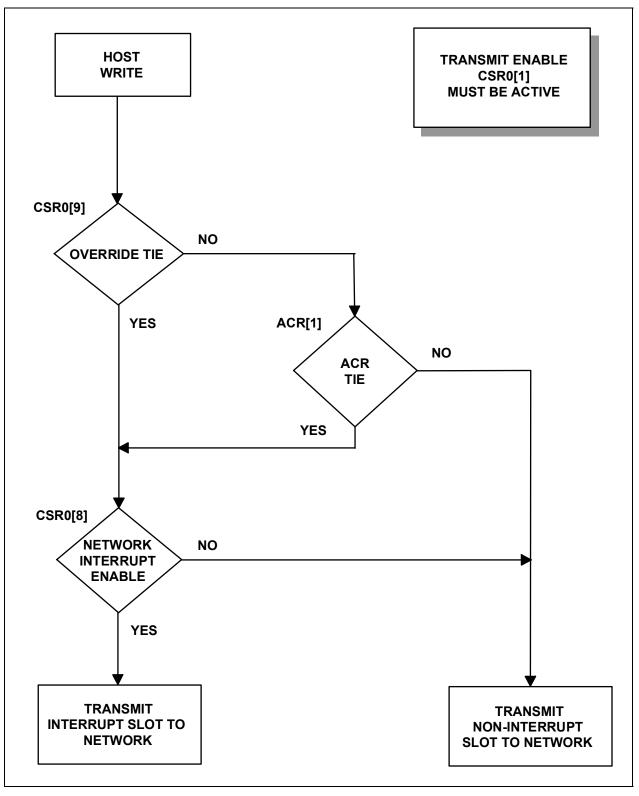

| Figure 2-3 Outgoing Interrupt                   | 2-7  |

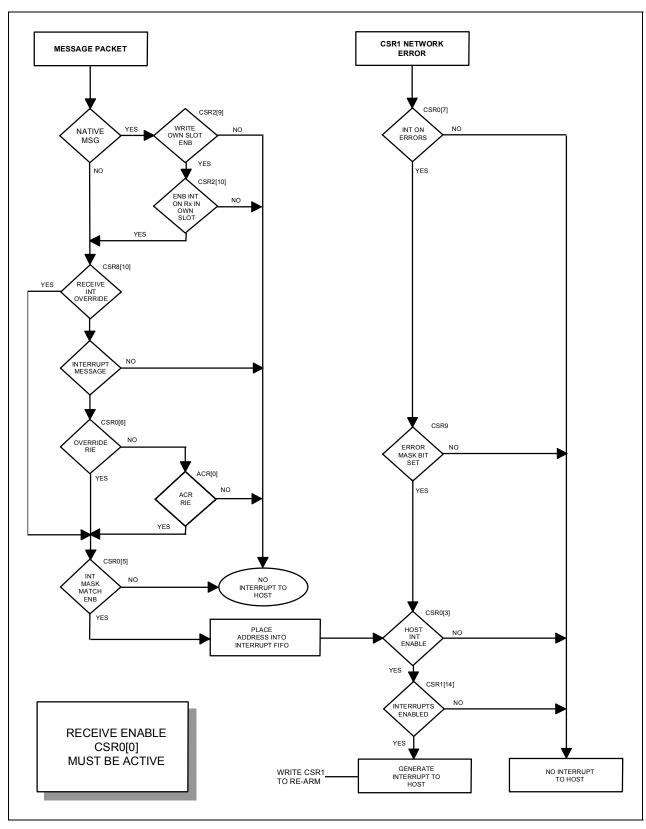

| Figure 2-4 Incoming Interrupt                   | 2-7  |

| Figure 3-5 VME6U Board, Version B1              |      |

| Figure 3-6 Node Inclusion and Isolation         | 3-5  |

| Figure 4-1 Fiber-optic Media Card (Bottom view) | 4-2  |

| Figure 4-2 VME6U Layout                         |      |

| Figure 4-3 EEPROM WRITE (J303)                  | 4-4  |

| Figure 4-4 EEPROM READ (J304)                   | 4-4  |

| Figure 4-5 Software Compatibility (J2)          | 4-6  |

| Figure 4-6 Memory Configuration (J3)            | 4-6  |

| Figure 4-7 Install SIMMS                        |      |

| Figure 4-8 Variable Length Messages (J4)        | 4-7  |

| Figure 4-9 Ground (J6)                          | 4-8  |

| Figure 4-10 External Trigger Connections (J7)   | 4-8  |

| Figure 4-11 Fiber-optic ST Connector            | 4-10 |

| Figure 4-12 Fiber-optic Connections             | 4-11 |

| Figure 4-13 Inserted State (Power On)           | 4-11 |

| Figure 4-14 Bypass State (Power Off)            | 4-12 |

| Figure 4-15 Auxiliary Connection                | 4-12 |

| Figure 5-1 Memory Sharing With Virtual Paging   | 5-2  |

| Figure 5-2 Transmit Interrupt Logic             | 5-11 |

| Figure 5-3 Receive Interrupt Logic              | 5-13 |

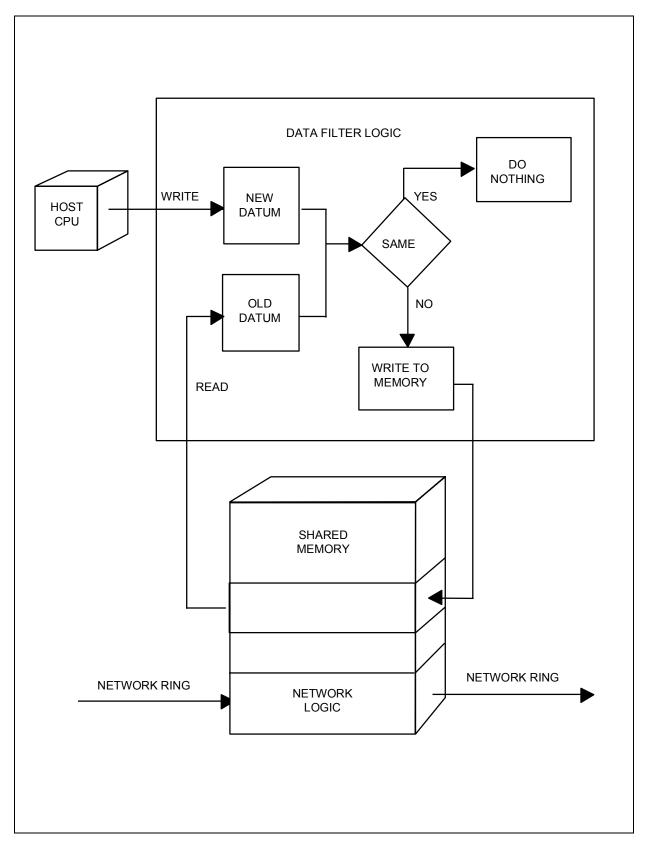

| Figure 5-4 Data Filter Logic                    |      |

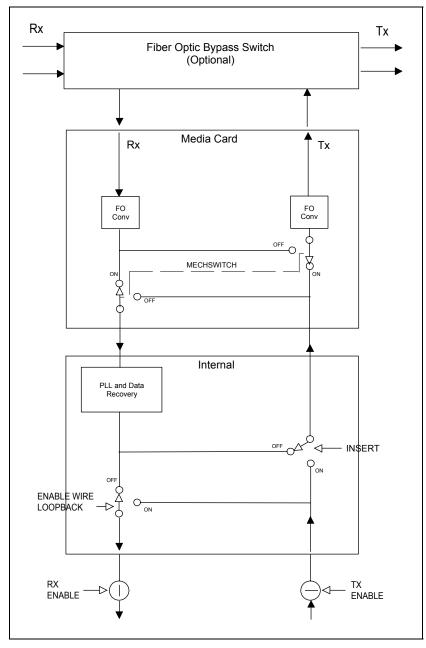

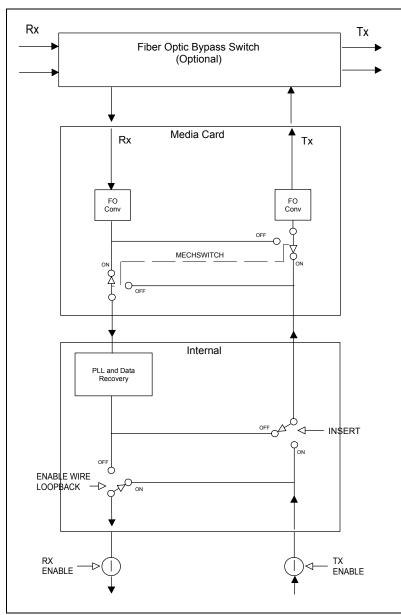

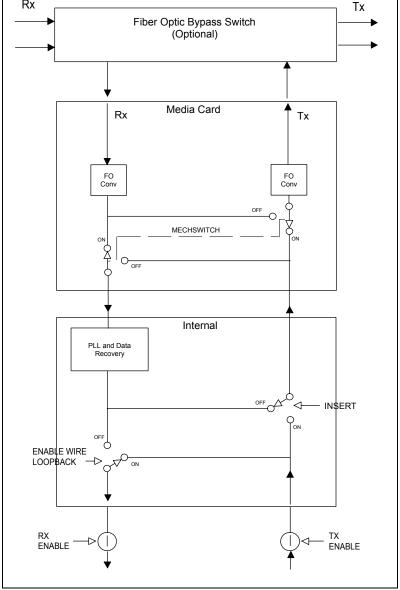

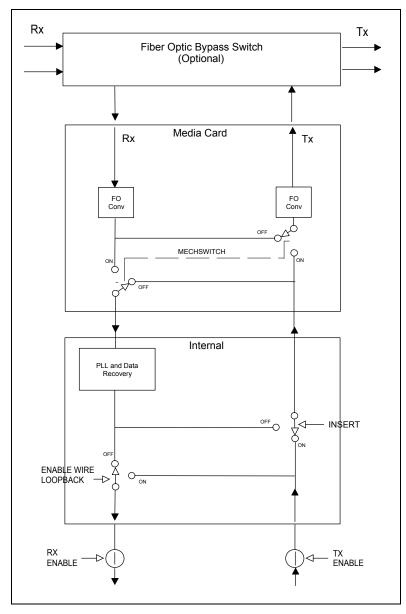

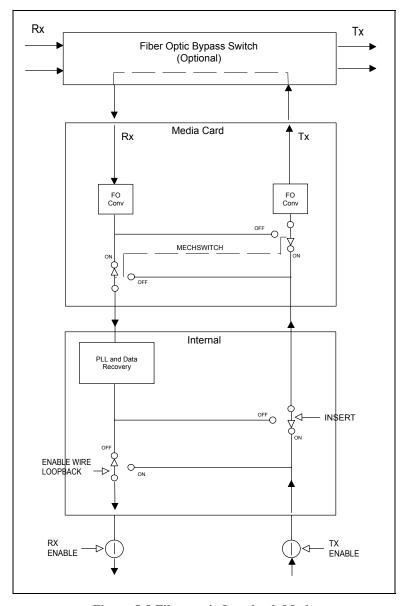

| Figure 5-5 Monitor and Bypass Mode              | 5-21 |

| Figure 5-6 Wire Loopback Mode                   | 5-22 |

| Figure 5-7 Mechanical Switch Loopback Mode      | 5-23 |

| Figure 5-8 Fiber-optic Loopback Mode            |      |

| Figure 5-9 Insert Mode                          |      |

| Figure 5-10 Quad Switch                         |      |

| Figure 5-11 Interrupt Service Routine           | 5-29 |

# **TABLES**

| Table 4-1 Setting the CSR Physical Address       | 4-5  |

|--------------------------------------------------|------|

| Table 4-2 Example of a CSR Address               | 4-5  |

| Table 4-3 Setting the Resolution Switch          | 4-6  |

| Table 4-4 Trigger Pin Connections (J7)           | 4-8  |

| Table 4-5 External Trigger Actions.              | 4-8  |

| Table 4-6 Auxiliary Connection Pinout            | 4-12 |

| Table 4-7 EEPROM Table                           | 4-13 |

| Table 4-8 EEPROM Initialization                  | 4-13 |

| Table 4-9 Big Endian - Little Endian Comparisons | 4-14 |

| Table 5-1 SCRAMNet+ Message Contents             | 5-4  |

| Table 5-2 ACR Functions                          | 5-8  |

| Table 5-3 Interrupt Controls                     | 5-9  |

| Table 5-4 Interrupt Error/Status Conditions.     | 5-14 |

| Table 5-5 General Purpose Counter/Timer Modes    |      |

| Table 5-6 Data Filter Options                    | 5-17 |

| Table 5-7 Monitor and Bypass Mode States         |      |

| Table 5-8 Wire Loopback Mode States              | 5-22 |

| Table 5-9 Mechanical Switch Loopback Mode States | 5-23 |

| Table 5-10 Fiber-optic Loopback Mode States      |      |

| Table 5-11 Node Insert Mode                      |      |

This page intentionally left blank

# 1. INTRODUCTION

## 1.1 How To Use This Manual

## 1.1.1 Purpose

This document is a reference manual for the SCRAMNet+ SC150 VME6U host interface board. It provides a physical and functional description of the SCRAMNet+ SC150 VME6U board. The manual describes how to unpack, set up, install and operate the hardware

### 1.1.2 Scope

This information is intended for systems designers, engineers and network installation personnel. You need at least a systems level understanding of general computer processing, of memory and hardware operation, and of the specific host processor to effectively use this manual.

### 1.1.3 Style Conventions

- Hexadecimal values are written with "0x" preceding the value, For example, 0x03FF.

- Switch, signal and jumper abbreviations are in capital letters, for example, RSW1, J5, etc.

- Register bits and bit ranges are specified by the register identification followed by the bit or range of bits in brackets [], For example, CSR6[4], CSR3[15:0], ACR[1,2]

- Bit values are shown in single-quotes, for example, set bit 15 to '1'.

- Code and monitor screen displays of input and output are boxed and indented on a separate line. Text that represents user input is bolded. Text that the computer displays on the screen is not bolded. For example:

| C:\>ls |       |       |

|--------|-------|-------|

| file1  | file2 | file3 |

• Large samples of code are Courier font, at least one size less than context, and are usually on a separate page or in an appendix.

## 1.2 Related Information

*SCRAMNet Network Cabinet Kit Hardware Reference* (Doc. Nr. D-T-MR-CABKIT) – A physical and functional description of SCRAMNet+ cabinet kits, including installation.

SCRAMNet Network Programmer's Reference Guide (Doc. Nr. D-T-MR-PROGREF) – A collection of routines to assist SCRAMNet users with application development.

SCRAMNet Network Utilities User Manual (Doc. Nr. C-T-MU-UTIL) – A user's manual for the SCRAMNet Classic, SCRAMNet+, and SCRAMNet+ hardware diagnostic software, SCRAMNet+ EEPROM initialization software, and the SCRAMNet Network Monitor.

# 1.3 Quality Assurance

Systran Corporate policy is to provide our customers with the highest quality products and services. In addition to the physical product, the company provides documentation, sales and marketing support, hardware and software technical support, and timely product delivery. Our quality commitment begins with product concept, and continues after receipt of the purchased product.

Systran's Quality System conforms to the ISO 9001 international standard for quality systems. ISO 9001 is the model for quality assurance in design, development, production, installation and servicing. The ISO 9001 standard addresses all 20 clauses of the ISO quality system, and is the most comprehensive of the conformance standards.

Our Quality System addresses the following basic objectives:

- Achieve, maintain and continually improve the quality of our products through established design, test, and production procedures.

- Improve the quality of our operations to meet the needs of our customers, suppliers, and other stakeholders.

- Provide our employees with the tools and overall work environment to fulfill, maintain, and improve product and service quality.

- Ensure our customer and other stakeholders that only the highest quality product or service will be delivered.

The British Standards Institution (BSI), the world's largest and most respected standardization authority, assessed Systran's Quality System. BSI's Quality Assurance division certified we meet or exceed all applicable international standards, and issued Certificate of Registration, number FM 31468, on May 16, 1995. The scope of Systran's registration is: "Design, manufacture and service of high technology hardware and software computer communications products." The registration is maintained under BSI QA's bi-annual quality audit program.

Customer feedback is integral to our quality and reliability program. We encourage customers to contact us with questions, suggestions, or comments regarding any of our products or services. We guarantee professional and quick responses to your questions, comments, or problems.

## 1.4 Technical Support

Technical documentation is provided with all of our products. This documentation describes the technology, its performance characteristics, and includes some typical applications. It also includes comprehensive support information, designed to answer any technical questions that might arise concerning the use of this product. We also publish and distribute technical briefs and application notes that cover a wide assortment of topics. Although we try to tailor the applications to real scenarios, not all possible circumstances are covered.

Although we have attempted to make this document comprehensive, you may have specific problems or issues this document does not satisfactorily cover. Our goal is to offer a combination of products and services that provide complete, easy-to-use solutions for your application.

If you have any technical or non-technical questions or comments, contact us. Hours of operation are from 8:00 a.m. to 5:00 p.m. Eastern Standard/Daylight Time.

• Phone: (937) 252-5601 or (800) 252-5601

• E-mail: support@systran.com

• Fax: (937) 252-1349

• World Wide Web address: www.systran.com

# 1.5 Ordering Process

To learn more about Systran products or to place an order, please use the following contact information. Hours of operation are from 8:00 a.m. to 5:00 p.m. Eastern Standard/Daylight Time.

• Phone: (937) 252-5601 or (800) 252-5601

• E-mail: info@systran.com

• World Wide Web address: www.systran.com

This page intentionally left blank

# 2. SCRAMNET NETWORK

### 2.1 Overview

The SCRAMNet+ Network is a real-time communications network, based on a replicated, shared-memory concept. Each host processor on the network has access to its own local copy of shared memory that is updated over a high-speed, serial-ring network. The network is optimized for the high-speed transfer of data among multiple, real-time computers that are all solving portions of the same real-time problem. The SCRAMNet+ node board can automatically filter out redundant data.

# 2.2 Shared Memory

In its simplest form, the SCRAMNet+ Network system is designed to appear as general-purpose memory. The use of this memory depends only on the conventions and limitations imposed by the specific host computer system and operating system. On most processors, this means that the application program can use this memory in basically the same way as any other data storage area of memory. The memory cannot be used as instruction space.

The major difference between SCRAMNet+ memory and system memory is that any data written into SCRAMNet+ memory is automatically sent to the same shared-memory location in all nodes on the network. This is why it is also referred to as replicated shared memory. A good analogy is the COMMON AREA used by the FORTRAN programming language. Where the COMMON AREA makes variables available to subroutines of a program, SCRAMNet+ makes variables available to processors of a network.

The SCRAMNet+ memory size can range from either 4 KB or 128 KB on-board memory to 8 MB of expansion memory. Available options include: 512 KB, 1 MB, 2 MB, 4 MB and 8 MB. A software driver is usually not required except for interrupt handling. When a host computer WRITEs to the shared memory, the proper handshaking logic is supplied by the SCRAMNet+ node host adapter. The shared memory behaves somewhat like resident or local memory.

## 2.2.1 Dual Port Memory Controller

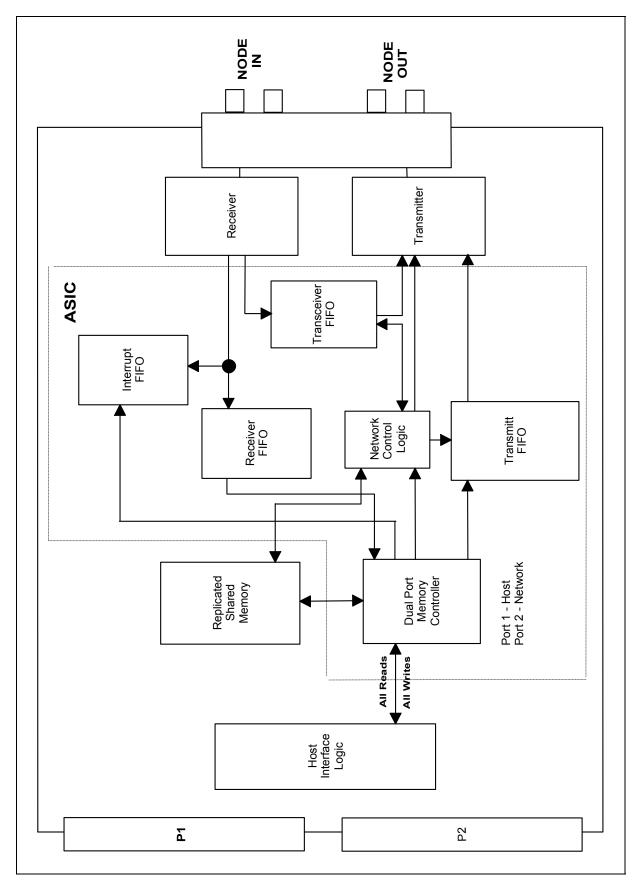

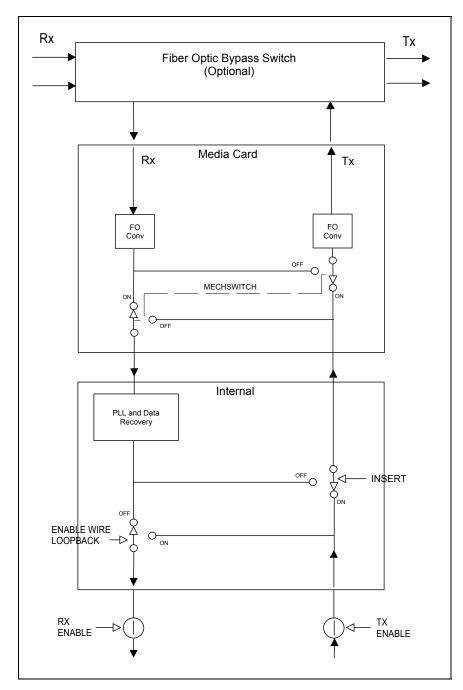

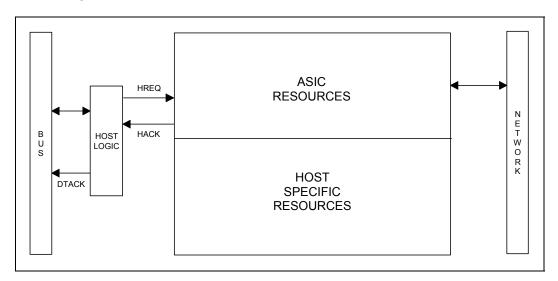

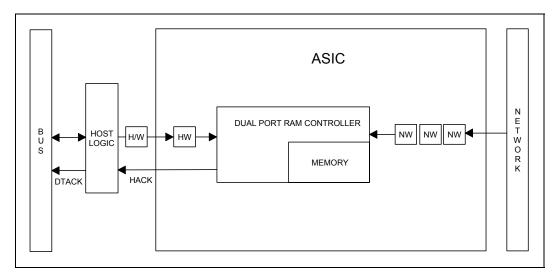

The Dual Port Memory Controller (see Figure 2-1) allows the host to READ from or WRITE to shared memory with a simultaneous network WRITE to shared memory. Unless an interrupt has been authorized for that memory address, the host is not aware the network is writing to shared memory. This is why caching must be disabled for SCRAMNet memory. If an interrupt has been authorized, the interrupt will then be sent to the host processor.

## 2.2.2 Control/Status Registers (CSRs)

The operation of the SCRAMNet+ board is controlled by Input/Output (I/O) CSRs. The location of the CSRs in the computer's address space is switch-selectable. In most

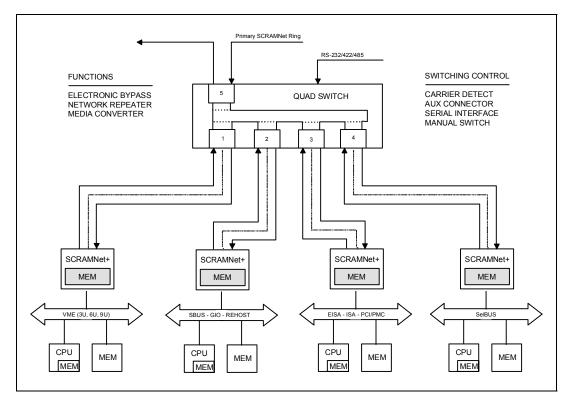

Figure 2-1 Functional Diagram

cases, the mode of operation is set during initialization and remains unchanged during run time. The CSRs are described in detail in Section 5.

## 2.2.3 Virtual Paging

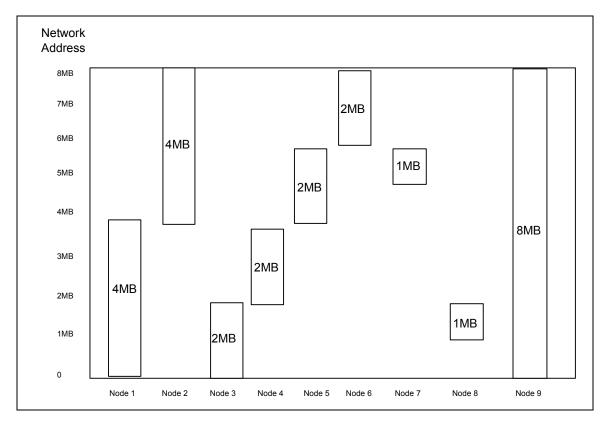

All SCRAMNet+ nodes use the same 8 MB shared memory map. This feature permits different SCRAMNet+ boards with 4 MB of shared memory or less to be paged into different sections of the 8 MB memory map. A board with a 4 MB or smaller memory may be located on any shared memory address boundary that is an even multiple of itself (e.g., 2 MB can page to 0, 2, 4 or 6 MB address).

## 2.3 FIFO Buffers

The SCRAMNet+ board contains various FIFO buffers used for temporarily storing information during normal send and receive operation of the node. Refer to Figure 2-1.

### 2.3.1 Transmit FIFO

The Transmit FIFO is a message holding area for native messages waiting to be transmitted. Each host write to SCRAMNet+ memory may constitute a WRITE to the Transmit FIFO. (Data Filtering and HIPRO features may interfere with this.) Each WRITE to the Transmit FIFO contains 21 bits of address (A22-A2), 32 bits of data, and one bit of interrupt information. The Transmit FIFO can hold up to 1024 writes before becoming full.

When the Transmit FIFO reaches a FULL condition (CSR1[0] ON), one more host WRITE could cause a message to be lost. To prevent this, the CSR-controllable, built-in SCRAMNet+ feature called VME Holdoff extends the computer WRITE cycle until the Transmit FIFO is able to empty at least one message.

#### 2.3.2 Transceiver FIFO

This buffer is used to receive foreign messages from the network, and send them on, or to hold received foreign messages while inserting a native message from the host onto the network.

Each node is responsible for receiving foreign messages, writing them to its copy of shared memory, and re-transmitting the message to the next node.

## 2.3.3 Interrupt FIFO

The Interrupt FIFO contains a 21-bit address (A22 - A2) and a retry status bit for each shared-memory-based interrupt received. The Interrupt FIFO can hold 1024 interrupt addresses. This FIFO can be read using CSR4 and CSR5.

#### 2.3.4 Receiver FIFO

The Receiver FIFO is designed as a temporary holding place for incoming foreign messages while the shared memory is busy servicing a host request. This FIFO is three messages deep, and is designed so it can never be overrun. Each item in the Receiver FIFO contains 21 bits of address (A22 - A2), 32 bits of data, and one incoming interrupt bit. When the messages are 1024 bytes, the initial header information data stays in the FIFO, the subsequent 4 bytes of data are loaded in, and the address is incremented by four.

## 2.4 Network Ring

The SCRAMNet+ Network is a ring topology network. Data is transmitted at a rate of 150 Mbits/s over dual fiber-optic cables. The two lines together produce the incoming data clock. Due to the network speed and message slot size, the network can accommodate over 1,800,000 message slots passing by each node every second. There is an approximate 247 ns (minimum) delay at each node as the message slot works its way around the ring. The maximum delay depends on the selection of fixed or variable-length message packets. A fixed-length message packet has a maximum delay of 800 ns, a 256-byte variable-length message packet is 16.2 µs, and a 1024-byte variable-length message packet is 62 µs. Delay can be imposed when a node must complete the transmission of a native message packet before retransmitting a foreign message packet. A SCRAMNet+Network can accommodate up to 256 nodes per network ring.

#### 2.4.1 Protocol

The protocol is a register-insertion methodology and is <u>NOT</u> a token ring. Depending on the protocol selected, all message packets are the same size or are variable (as in the PLUS modes), and multiple nodes can transmit data simultaneously. There is no master node, and all nodes have equal priority for network bandwidth. The message protocol is designed specifically for real-time applications where data must be passed very rapidly. When the node operates in BURST or BURST PLUS mode, the node will never retransmit its own messages for error correction. When operating in PLATINUM or PLATINUM PLUS mode, error detection is enabled, and re-transmission can occur.

#### **BURST MODE**

BURST mode is an open loop, non-error-corrected communication mode. This mode allows multiple 82-bit messages (46-bit header plus 32-bite data and four parity bits) per node on the ring at a time. The limited packet length enhances the data latency characteristics of the network by providing the shortest possible media access delay. The messages are transmitted as fast as the system will allow.

#### PLATINUM MODE

PLATINUM mode is BURST mode with error correction enabled. The messages are transmitted as fast as the system will allow, but error checking is used to detect and retransmit corrupted packets.

#### **PLUS MODES**

The PLUS mode protocol enhancement can increase the maximum network throughput from 6.5 MB/sec to approximately 15.2 to 16.7 MB/sec by the use of variable-length message packets. Each SCRAMNet+ message packet has a 46-bit header plus the data. The user-selectable maximum packet size increases the data size from the normal 32 bits to either 256 or 1024 bytes of data. Data must be written to sequential longword addresses.

# 2.5 Auxiliary Control RAM (ACR)

The Auxiliary Control RAM (ACR) provides a method of external triggering and interrupt control by offering a choice of four actions to occur when a particular SCRAMNet+ shared-memory address is written into. Each shared-memory location has its own action or set of actions associated with it.

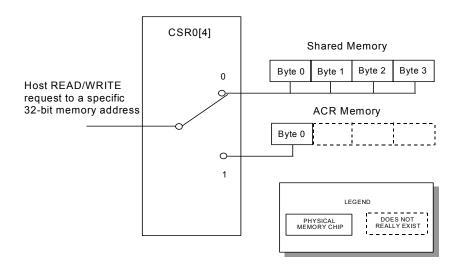

Figure 2-2 ACR/Memory Access

In Figure 2-2, host CPU READ/WRITE operations are channeled to either SCRAMNet+ memory or to the ACR. The ACR is a physically separate memory from the shared memory. Channeling is based on a user-controlled switch setting and may be toggled to the desired position by writing to a bit in the SCRAMNet+ CSR. When access to the ACR is enabled, shared memory is not accessible by the host and the ACR byte is viewed as the least significant byte (LSB) of every shared-memory four-byte address. The ACR bits define what external trigger and/or interrupt action(s) are to be taken whenever writing to any byte of the SCRAMNet+ shared memory 4-byte word.

Only five bits of the ACR are associated with every four-byte word of shared memory (on even four-byte boundaries). The other 27 bits of the ACR are phantom bits and do not physically exist.

## 2.6 Interrupts

SCRAMNet+ allows a node processor to receive interrupts from and transmit interrupts to any node on the network, including the originating node, provided the receiving node is set up to receive an interrupt message. Interrupts can be generated under two different conditions:

- SCRAMNet+ Network data WRITEs to shared memory; and

- SCRAMNet+ network errors detected on the local node.

SCRAMNet+ interrupts usually require a device driver to interface with the node processor. There must also be a host-dependent interrupt vector placed in CSR6 and CSR7 identifying the Interrupt Service Routine (ISR). The driver is required primarily to permit the host processor to handle interrupts from the SCRAMNet device.

### 2.6.1 Network Interrupt WRITEs

#### **FOREIGN MESSAGE**

The node can receive a message from another node with the interrupt bit set. If Receive Interrupt Enable ACR[0] and Interrupt Mask Match Enable CSR0[5] are enabled, the data is written to shared memory and the address is placed on the Interrupt FIFO.

#### NATIVE MESSAGE

If the message received was originated by the node, and Write Own Slot Enable CSR2[9] and Enable Interrupt on Own Slot CSR2[10] are enabled, the host has authorized a Self-Interrupt. The data is written to shared memory and the address is placed on the Interrupt FIFO.

Network Interrupt WRITEs can be accomplished by two methods:

- **Selected**. Data WRITEs to selected shared memory locations from the network.

- **Forced**. Any data WRITEs to any shared memory from the network.

In either case, the node can be configured to WRITE to itself. This condition is called "Self Interrupt."

## 2.6.2 Selected Interrupt

The selected-interrupt method requires choosing SCRAMNet+ shared-memory locations on each node to receive and/or to transmit interrupts. These shared-memory locations may also be used to generate signals to external triggers. The procedure for selecting shared-memory locations for interrupts and/or external triggers is explained in the paragraph on the Auxiliary Control RAM, paragraph 2.5.

#### **OUTGOING INTERRUPT**

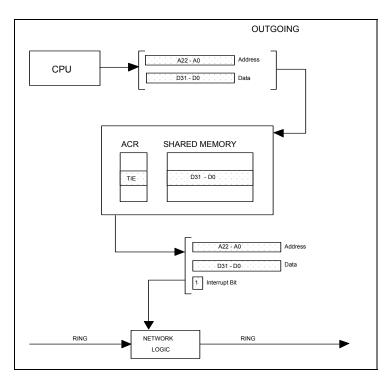

The Outgoing Interrupt is described in Figure 2-3. If both Transmit Interrupt Enable ACR[1] and Network Interrupt Enable CSR0[8] are set, and a data item is transmitted to any of the selected-interrupt memory locations, then an interrupt message is sent out on the network. This message will generate interrupts to any processors on the network that have that same shared-memory location selected to receive interrupts.

#### INCOMING INTERRUPT

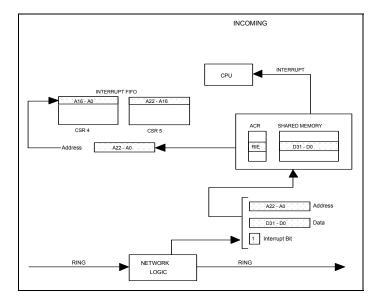

Figure 2-4 demonstrates the process of receiving a message with the interrupt bit set. The data is written to shared memory and the address is placed in CSR5 and CSR4 to await being sent to the host. If the Receive Interrupt Enable ACR[0], Host Interrupt Enable CSR0[3], and the Interrupt Memory Mask Match Enable CSR0[5] are set, and network interrupt data is received for any one of the selected-interrupt memory locations the following occurs:

- The data is stored in that location

- The SCRAMNet+ address of the memory location is placed on the Interrupt FIFO queue, and

- An interrupt is sent to the processor.

**Figure 2-3 Outgoing Interrupt**

**Figure 2-4 Incoming Interrupt**

#### **NETWORK ERRORS**

The Interrupt on (Network) Errors mode is enabled by setting CSR0[7] ON. Network errors are defined in CSR1 according to an interrupt mask set in CSR9. When an incoming foreign message generates an interrupt, there is no way to mask the interrupt according to the content of the message. However, specific error conditions may be identified.

Error conditions are listed in CSR1 and may be masked by setting the corresponding bit in CSR9. If the Mask bits in CSR9 are all set to '1,' any error will generate an interrupt. Otherwise, only errors with a '1' in the appropriate Mask bit will generate an interrupt.

A Network Interrupt vector may be placed in CSR7 to identify a Network Error Interrupt Service Routine.

## 2.6.3 Forced Interrupt

The forced-interrupt method works the same as for selected except for the choice of interrupt locations. All shared-memory locations are automatically set up to receive and/or transmit interrupts depending upon the ACR override conditions set in CSR0[6] and/or CSR0[9].

When Override Receive Interrupt Enable CSR0[6] is set an interrupt will be sent to the host by any network interrupt data message, regardless of the status of the ACR Receive Interrupt bit.

When Override Transmit Interrupt Enable CSR0[9] is set an interrupt will be sent out on the network regardless of the status of the ACR Transmit Interrupt bit.

A third condition, Receive Interrupt Override CSR8[10], is used to designate all incoming network traffic as interrupt messages. The network message interrupt bit does not need to be set.

# 2.7 External Triggers

Two external triggers are supported by SCRAMNet+ VME6U. The external triggers will occur <u>only</u> if the ACR has been configured to enable them. Triggers 1 and 2 are generated by SCRAMNet+ shared-memory access. Both triggers generate a 26.64 ns TTL level compatible, non-terminated, output.

- Trigger 1 Host Read/Write ACR[2] enables)

- Trigger 2 Network Write ACR[3] enables)

## 2.8 General Purpose Counter/Global Timer

The General Purpose Counter/Timer has six modes of operation controlled by CSR8 and CSR9, the output from the General Purpose Counter/Timer is stored in CSR13. Counter modes can count errors, external trigger events, or network messages. A high-resolution timer mode can run free or measure the ring time with a 26.66 ns resolution.

The global timer mode clocks with a resolution of  $1.706~\mu s$  and resets on an external trigger event. (See 2.7: External Triggers). A specific shared-memory location may be identified with External Trigger 2 (ACR[3]) so that a memory WRITE from a single node on the network can simultaneously reset all the global timers in the ring.

If the Trigger 2 event is the frame counter, the timers in the ring effectively become synchronized sub-frame timers, which can then be used to tag time-critical data or to measure and compare the completion time of various tasks within a distributed real-time system.

## 2.9 LED Status Indicators

#### **INSERT**

The green Insert LED is ON when the node is inserted into the SCRAMNet+ Network ring. This is the result of setting CSR 0[15].

#### **MESSAGE WAITING**

The green Message Waiting LED lights when a message is placed in the Transmit FIFO.

#### **CARRIER DETECT**

The green carrier detect LED is ON when there is a valid pair of transmit lights from the previous SCRAMNet+ node into this node's receiver pair. If the fiber-optic cables are connected and the carrier detect LED is OFF, then the ring integrity is NOT valid. This condition indicates improper fiber-optic cabling or problems with the down-line node's transmitter(s).

**NOTE**: On a freshly powered system, a message from any node on the ring may be necessary to establish carrier.

#### **ERROR**

The yellow error LED is active whenever any error conditions set in CSR1 are detected.

#### **NATIVE MESSAGE**

The green Native Message LED lights when the message received was originated by the node.

#### **FOREIGN MESSAGE**

The green Foreign Message LED becomes active when the message received is from another node.

## 2.10 Modes of Operation

#### 2.10.1 Data Filter Mode

When SCRAMNet+ Data Filtering is enabled, only those WRITEs to SCRAMNet+ memory that produce a data change are transmitted to the network.

#### **EXAMPLE:**

If location 1000 in SCRAMNet+ memory contains the value '20' and the host processor WRITEs the value '20' to location 1000, then no network traffic will be generated. However, if any other value is written to location 1000, then the new value will be passed around the network to update the other SCRAMNet+ node memories.

When a WRITE is received from the host, a comparison is made to the old data at that address to see if there was a change before writing to shared memory. If the data has changed, then it is written to shared memory, and is also transmitted onto the network. This entire process is completed within the host memory standard bus WRITE cycle.

Data filtering is a powerful communications compression technique for cyclical applications. This technique has been shown to significantly reduce the network traffic and therefore increase the effective throughput on the network.

## 2.10.2 High Performance (HIPRO) Mode

HIPRO provides an efficient means to transmit 8-bit and 16-bit data transactions as one 32-bit network WRITE. It also provides a means of keeping 32-bit data from becoming fractured.

#### **EXAMPLE #1:**

A floating-point length numeric sent in 8-bit or 16-bit pieces may not be accurately reassembled at the destination.

#### **EXAMPLE #2:**

The receiving node may otherwise try to use part or half of such a value before the entire 32 bits is received.

#### HIPRO WRITE

The SCRAMNet+ network message is based on 32-bit longword data. This means if any 8-bit field of the 32-bit buffer is changed, the entire 32-bit message is transmitted. If a host is limited to only 8-bit or 16-bit databus transactions the network throughput is quartered or halved, respectively.

HIPRO mode permits a 32-bit location to be set up in shared memory such that any initial WRITE smaller than 32 bits to that location will not automatically go onto the network. The 32-bit WRITE to the network will only occur when all four bytes within the 32-bit location have been written through subsequent WRITEs by the host CPU. This can be accomplished by four consecutive 8-bit or two consecutive 16-bit WRITEs to the SCRAMNet memory.

**NOTE**: HIPRO WRITE will not work if Disable Host to Memory Write CSR2[8] is set, or when writing two separate shortwords while using interrupts.

#### **HIPRO READ**

The HIPRO READ is controlled by CSR16. This register is CSR enabled and ACR location selectable.

To conserve host cycles and increase host throughput, HIPRO READ mode allows the host to get part of the information (1 shortword or 2 bytes) during the first READ on that longword boundary. On the next READ operation (not the same location or within the same longword boundary) the remaining data is provided.

#### 2.10.3 VME Holdoff Mode

It is possible that the Transmit FIFO can become full when the host is writing to the SCRAMNet+ interface faster than the network can absorb the data.

In VME Holdoff mode, the host WRITE cycle is automatically extended until the SCRAMNet+ Transmit FIFO buffer transmits at least one message. This prevents the loss of data and is transparent to the user.

In some system designs, and on some computer buses, it is not desirable or effective to have the WRITE cycle lengthened to match network throughput—even at the expense of possible data loss across the network. In this case this option may be disabled by setting CSR8[1] ON. Transmit FIFO 7/8 Full CSR1[2] can then be used to control the data flow via software control.

## 2.10.4 Loopback Modes

Loopback mode is used for testing, and for routing data, which would normally be transmitted onto the network back into the node. This mode is used to check performance internally (Wire Loopback) at the Media Card (Mechanical Switch Loopback) and Transmit/ Receive (Fiber-optic Loopback).

#### **WIRE LOOPBACK MODE**

The Wire Loopback mode needs no manual external modifications to work. Wire Loopback is enabled by setting CSR2[7] ON. This mode checks the on-board circuitry for continuity.

**NOTE**: If a node is inserted into the network while in wire loopback mode, it will create a break in the network ring, making all nodes down-line unreachable.

#### MECHANICAL SWITCH (MEDIA CARD) LOOPBACK MODE

Mechanical Switch (Media Card) Loopback mode is enabled by setting Mechanical Switch Override CSR8[11] to OFF. This test is used to check the circuitry up to and including a major portion of the Media Card but excludes the fiber-optic circuitry. In this test the signal does not leave the Media Card.

#### FIBER-OPTIC LOOPBACK MODE

The Fiber-optic Loopback mode must have the optional Fiber Optic Bypass Switch connected, Disable Fiber-optics Loopback CSR2[6] set to OFF (power up default), and Insert Node CSR0[15] enabled to be valid. When the Fiber-optic Loopback mode is in effect, the output of the transmitter is connected by fiber optics directly to the input of the receiver, and the receiver is disconnected from the network.

The optional Fiber Optic Bypass Switch must be installed for this loopback to work. However, in the absence of the Fiber Optic Bypass Switch, fiber-optic cables could be run from the node's transmitter output connectors to the receiver input connectors. This configuration, with Insert Node enabled, would constitute a Fiber-optic Loopback mode for stand-alone testing. Set CSR2[6] ON to disable the Fiber-optic Loopback mode when the node is in use as a part of the network. This configuration is not a substitute for the Fiber Optic Bypass Switch for network operation.

#### 2.10.5 Write-Me-Last Mode

The Write-Me-Last mode of operation allows the originating node to be the last node in the ring to have the data deposited to its memory. This can be useful for synchronization. This means that when the host performs a WRITE to the SCRAMNet+ shared memory, this data is not immediately written to the host node's memory, but is first sent to the other nodes on the network. When the message returns to the originating node it is written to shared memory, and is then removed from the network ring.

Therefore, host-originated data written to shared memory travels the ring updating the SCRAMNet+ node memories on the ring and, upon returning to the originating node, that node WRITEs the data to its own shared memory as the last node on the ring. This guarantees that the data is available on all other nodes.

This page intentionally left blank

# 3. PRODUCT OVERVIEW

## 3.1 Overview

SCRAMNet+ (Shared Common Random Access Memory Network) is a communications network geared toward real-time applications, and based on a replicated, shared-memory concept.

The SCRAMNet+ VME6U host interface node board is backwards compatible with the original SCRAMNet Classic product. The SCRAMNet Classic Gold Ring communication protocol is compatible with the SCRAMNet+ Platinum protocol, but not with BURST PLUS or PLATINUM PLUS. The programmable byte swapper is no longer available on VMEbus-based products.

The SCRAMNet+ VME6U board requires a single slot in the VMEbus chassis.

The SCRAMNet+ VME6U board base address for Control/Status Registers (CSRs) is switch selectable. The 4 KB or the optional 128 KB on-board shared memory can be upgraded to 512 KB, 1 MB, 2 MB, 4 MB or 8 MB random access memory (RAM). Installing any memory upgrade overrides the on-board 128 KB memory.

#### 3.1.1 Network Features

- A ring topology with 150 Mbit/s line transmission rate.

- A Data Filter that allows only data stored in shared memory that has changed to be communicated to the other network nodes.

- Field Upgrade Memory Options up to 8 MB of replicated, shared memory for each node processor.

- BURST Mode protocol (Error Correction Disabled) with fixed-length message packets of 82 bits.

- BURST PLUS Mode communication based on variable-length message packet to a maximum of either 256 bytes or 1024 bytes.

- PLATINUM Mode protocol (Error Correction enabled) with fixed-length message packets of 82 bits.

- PLATINUM PLUS Mode communication based on variable-length message packet to a maximum of either 256 bytes or 1024 bytes.

- 256 node capacity on each ring.

- No operating or system software required to support network protocol.

- No network-dependent application software required.

## 3.1.2 Options

- Optional paired-fiber-optic or coaxial transmission media

- Fiber Optic Bypass Switch for ring continuity when node power is off.

- Quad Switch—A switching-control device that controls up to four nodes or subrings, eliminates the need for a separate Fiber Optic Bypass Switch, and functions as a repeater.

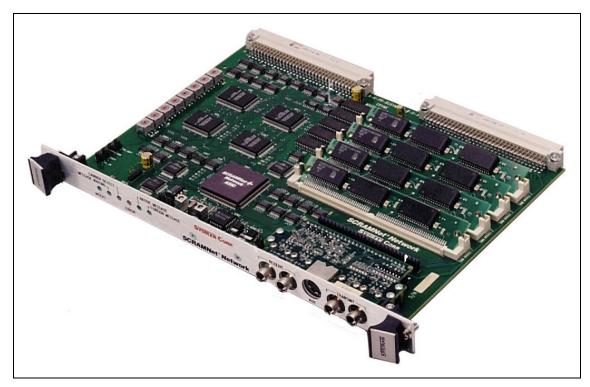

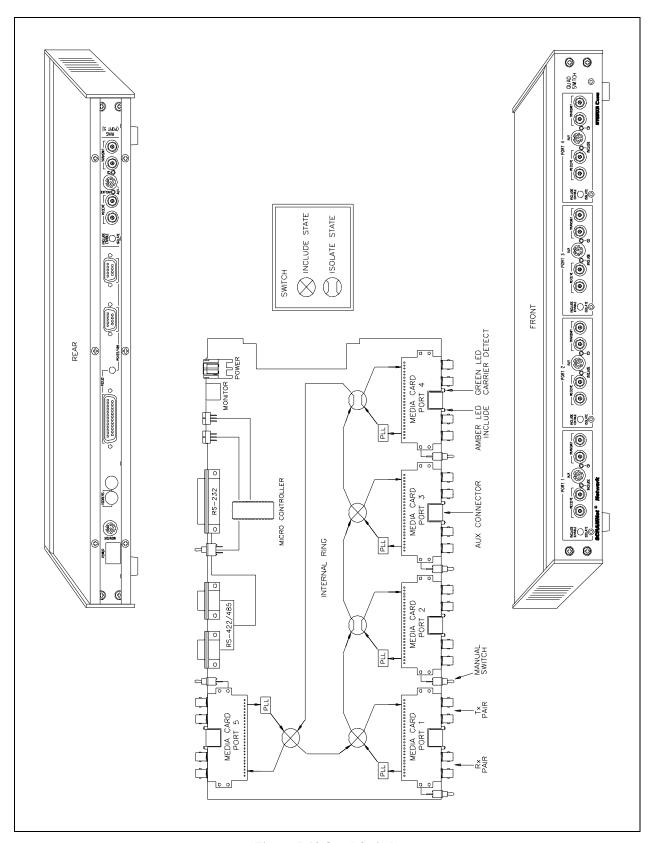

Figure 3-5 VME6U Board, Version B1

#### 3.1.3 VME6U Board Features

- SIMM memory upgrade option

- General purpose counter

- Error-interrupt mask

- Dynamic shared-memory addressing

- Switch-selectable CSR address selector

- Virtual paging for shared memory (CSR selectable)

- Variable-length message packet capability

- Dual-port memory

- Dual-vector memory/error interrupt (single level interrupt)

- Single-slot solution

- EEPROM initialization

# 3.2 VMEbus Specification Level

The SCRAMNet+ VME6U host board was designed in accordance with the VMEbus specification Revision C.3, ANSI/IEEE Std 1014-1987.

- Slave device

- SADO32 (No UAT, no BLT; A32, A24 memory; A32, A24, A16 CSR)

- SRMW32 (D32, D16, D08 (EO))

- 8-bit vector ROAK

- 6U double-height card size

## 3.3 Addressing Compatibility

## **3.3.1 Memory**

The shared memory resident on the SCRAMNet+ VME6U host interface board must be located on either the A24 standard bus or the A32 extended bus. The address is CSR selectable. The memory address selected must be an address boundary that is a multiple of the shared-memory size, and must be loaded and enabled through the CSRs.

## 3.3.2 Control/Status Registers

I/O Control in the form of CSRs can be located on the A16 I/O bus, the A24 standard bus, or the A32 extended bus. The address is set manually using the rotary switches on the board. This is independent of the shared-memory address. The CSRs require 64 contiguous bytes of address space.

# 3.4 Data Transfer Capability

## **3.4.1 Memory**

Data transfers to the shared memory on the SCRAMNet+ VME6U host interface can be 8, 16 or 32 bits wide and may be of the READ-MODIFY-WRITE type. Three-byte unaligned transfers are not permitted.

#### 3.4.2 I/O

Data transfers to the I/O control area of the SCRAMNet+ VME6U host interface can be 8, 16 or 32 bits wide and may be of the READ-MODIFY-WRITE type. Three-byte unaligned transfers are not permitted.

## 3.5 Interrupt Capability

The SCRAMNet+ VME6U host interface is an interrupter of the type D08. Interrupt level 1 through 7 may be selected by setting a value in CSR15. The IRQ is mapped using a bit-wise format; bit 1 is IRQ 1, bit 2 is IRQ 2, etc. (Bit 0 is not used.) The vector generated by the node is 8 bits wide. Being an ROAK (Release On interrupt AcKnowledge) type of interrupter means that the device releases the interrupt request during the interrupt-acknowledge cycle. The 8-bit vector address is loaded at CSR6 - Memory, and CSR7 – Error. If Interrupt-on-Error is not used, CSR7 must contain the same vector as CSR6.

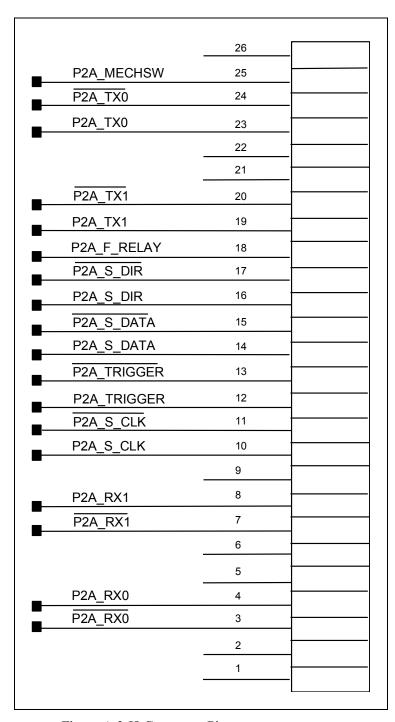

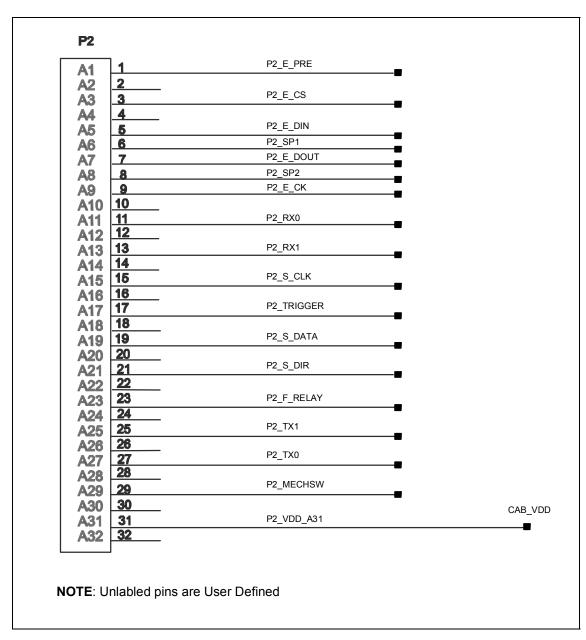

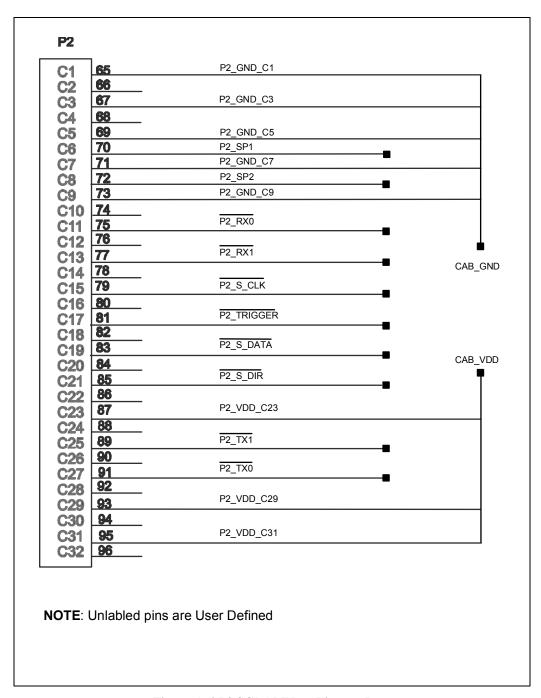

## 3.6 P1 and P2 Connectors

The SCRAMNet+ VME6U card's P1 and P2 backplane connectors are in accordance with the VMEbus specifications.

P2 pin connections are defined for SCRAMNet+ in Appendix A.

## 3.7 Utility Software

## 3.7.1 SCRAMNet Diagnostics

The SCRAMNet Network Hardware Diagnostics are designed to test the functionality of the hardware. This suite of tests will detect whether it is testing a Classic board or a SCRAMNet-LX/SCRAMNet+ board and adjust the test menus accordingly.

### 3.7.2 EEPROM Initialization (EPI)

The EEPROM Initialization program is a SCRAMNet+ utility used to simplify configuration of the network node. The EPI program will store a start-up configuration in the serial EEPROM that can initialize the node on power up. This initialization program can be run when the board is installed to set the desired power-up state of the SCRAMNet+ node. EPI is completely menu driven and contains a context-sensitive help feature.

#### 3.7.3 SCRAMNet Monitor

The SCRAMNet Monitor allows viewing and editing of memory and CSR locations on the SCRAMNet node. This utility is useful during software development to verify that the correct values are being written to SCRAMNet memory and CSRs.

# 3.8 Options

## 3.8.1 Electronic Bypass Switch

The Electronic Bypass Switch exists on some Media Cards. This switch allows for fast bypass on power-fail conditions. The electronic switch operates in the low nanosecond range compared to a 20 millisecond time for a typical mechanical switch.

In case of node power failure, the electronic switch restores the network so quickly that only one or two messages will have to be retransmitted, whereas a mechanical switch could cost an excessive amount of transmission time re-sending perhaps thousands of messages.

#### 3.8.2 Quad Switch

The SCRAMNet Quad Switch is designed to provide configuration control over the network topology and computing resources. The Quad Switch allows local clusters of up to four SCRAMNet nodes to be switched in or out of a primary SCRAMNet ring, independently and dynamically (Figure 3-6). It also allows sharing of a critical real-time resource between multiple systems.

The Quad Switch performs other useful functions such as optical bypassing, fiber-optic repeating to gain transmission length beyond the SCRAMNet node's transmission power limit, and to act as a media converter.

The electronic bypass switching action is very fast, introducing a total network disruption of about one microsecond. This is over 10,000 times faster than mechanical optical bypass switches, and permits ring re-configuration to be performed in real-time with minimal impact on the system.

As a repeater, each Quad Switch port converts optical signals to electrical signals. These signals are re-synchronized and re-transmitted. This allows each connection to the Quad Switch to be the maximum length for the type of media selected.

The Quad Switch can also perform media conversion. Since each port has a Media Card just like a SCRAMNet node, each port can be configured to handle coax, standard link or long-link fiber. This allows a signal to arrive on one media type, and go out on another.

Figure 3-6 Node Inclusion and Isolation

Visually, LED's signify the state of node inclusion in the ring and if carrier is detected. If carrier is not detected, the port is put into Isolate state and the port is bypassed thereby retaining ring integrity. The auxiliary connector and the associated control cable links the port to the node to allow the application running the node to switch the Quad Switch in and out of Include or Isolate state. A manual Include/Isolate switch is used to guarantee that a node is isolated or that it can be included. A serial-port interface is used to send message packets to the Quad Switch to perform control function or to obtain switch status remotely via the RS-232 or RS-422/485 connection. Two mechanical rotary switches set the serial interface address

#### 3.8.3 Cabinet Kit

The Cabinet Kit for the SCRAMNet+ Network permits adapting the node to the host cabinet while still maintaining the shielding of the chassis. Access to the node's connections, and cable integrity is exterior to the cabinet. This eliminates the need to remove the node board, once proper installation has been accomplished.

Cabinet kits are available for a variety of vendor chassis, and include the Compact and the Extended models. The Compact Cabinet Kit is described in Appendix D, and in detail in the SCRAMNet Network Cabinet Kit Hardware Reference.

This page intentionally left blank

# 4. INSTALLATION

## 4.1 Installation Procedures

Installation of the VME6U board includes the following:

- Unpack the board

- Visually inspect the board

- Check SIMM connection(s), if any

- Check Media Card connection

- Externally configure the board

- Set/verify EEPROM WRITE jumper (J303)

- Set/verify EEPROM READ jumper (J304)

- Set CSR Address switches (S1-S7)

- Set bus resolution switch (S8)

- Set/verify Software Compatibility jumper (J2)

- Set/verify Memory Configuration jumper (J3)

- Set/verify Variable Length jumper (J4)

- Set/verify Ground jumper (J6)

- Set/verify External Trigger connections (J7)

- Install the board

- Select cabling options

- Install Fiber Optic Bypass Switch (optional)

- Internal Configuration

- Set Node Identification (CSR3, BITS [15:8])

- Set Network Time-out (CSR5)

- Set Memory Base Address (CSR10, bits [15:12] and CSR11, bits [15:0])

- Enable/disable Shared Memory (CSR10, bit 0)

- Set Variable Length message packet size (CSR2, bit 11)

## 4.2 Unpack the Board

1. The board is wrapped in an anti-static bag and encased in anti-static foam.

**CAUTION**: Use an anti-static mat connected to a wristband when handling or installing the SCRAMNet+ board.

2. Remove the board and anti-static bag from the carton. Open the anti-static bag and remove the board while wearing an anti-static wristband.

Save the shipping material in the event that the SCRAMNet+ board needs to be returned.

The optional fiber-optic cables, the optional Fiber Optic Bypass Switch, and the optional redundant transceivers are shipped in separate cartons.

# 4.3 Visually Inspect the Board

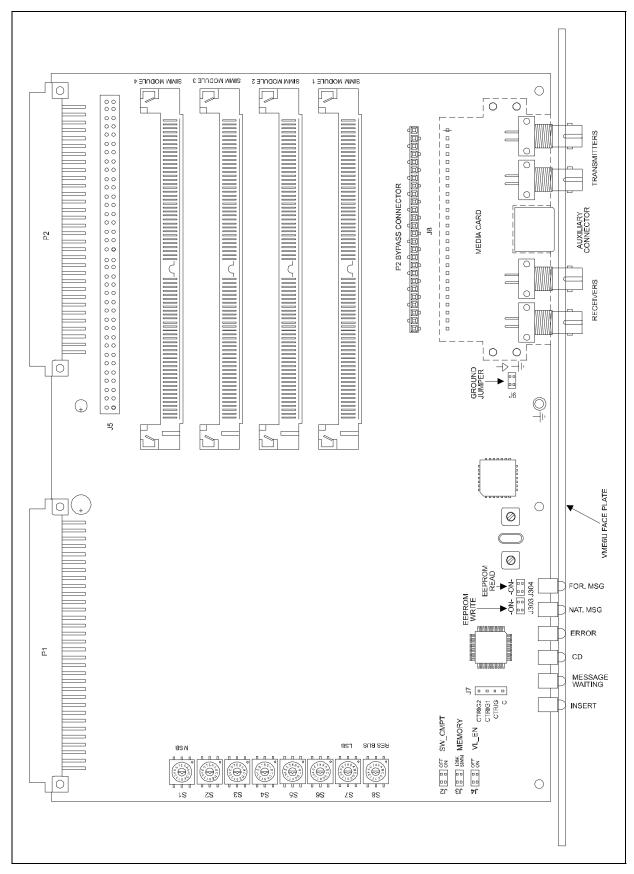

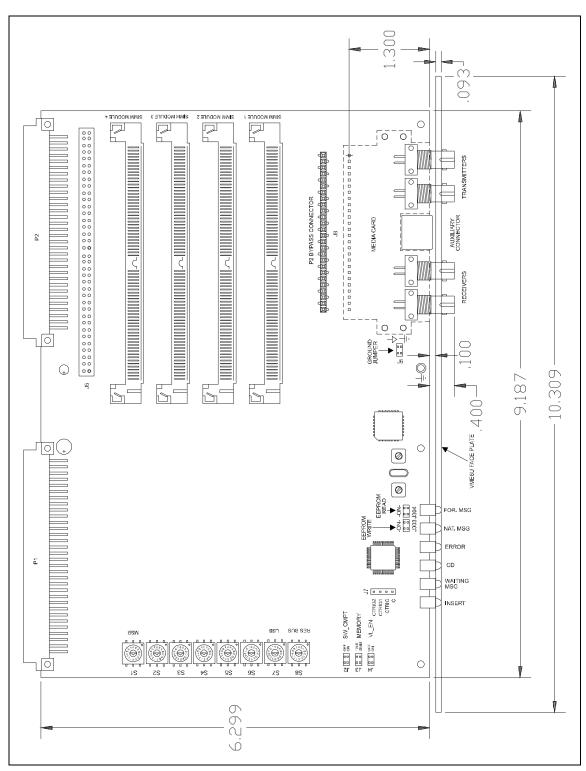

The SCRAMNet+ Network node consists of a single board as shown in Figure 4-2. If the optional memory upgrade was ordered, it will come already installed. In the event that any shipping damage has occurred, notify SYSTRAN Corporation or your supplier immediately.

#### 4.3.1 SIMM Connections

If SIMMs are installed, press gently downward on each SIMM and make sure the clips are engaged to hold the SIMM in place.

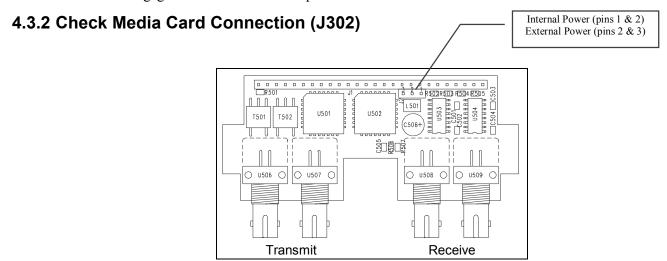

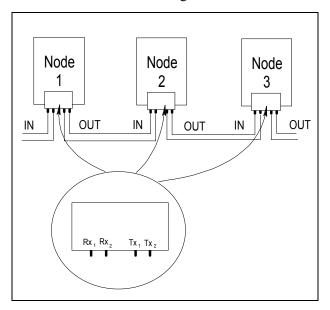

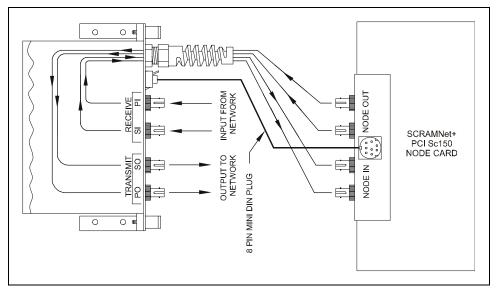

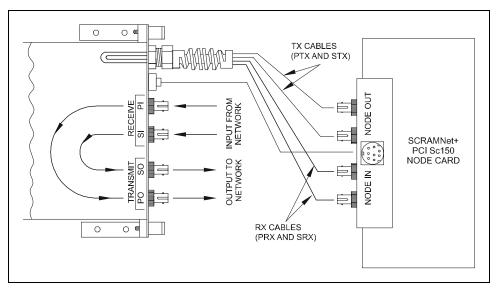

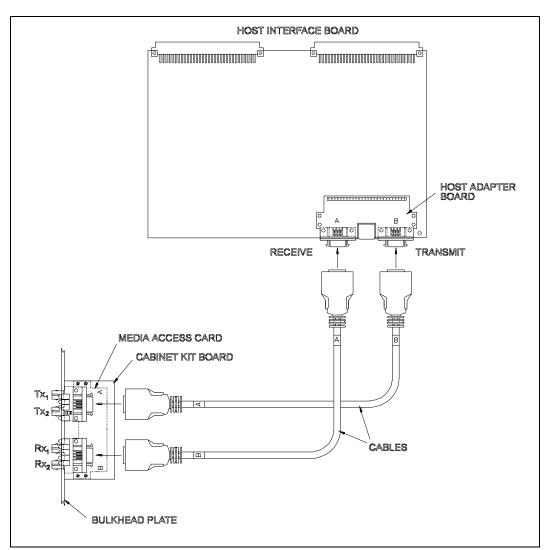

Figure 4-1 Fiber-optic Media Card (Bottom view)

The Media Card can have either coaxial or fiber-optic connectors. Figure 4-1 shows the fiber-optic media card. The SCRAMNet+ VME6U board will support either option. The type of Media Card installed will be dictated by the network configuration. There are two receive connections ( $Rx_1$  and  $Rx_2$ ) and two transmit connections ( $Tx_1$  and  $Tx_2$ ).

Figure 4-2 VME6U Layout

This fiber-optic card has two power options; host power and standby or battery power. Jumper J2 in Figure 4-1 controls the power options. Pins 1 and 2 are for normal host power, and pins 2 and 3 are for standby power. The standby or battery power requires external connection via the auxiliary connection on the cabinet kit board or the host interface board if no cabinet kit is installed.

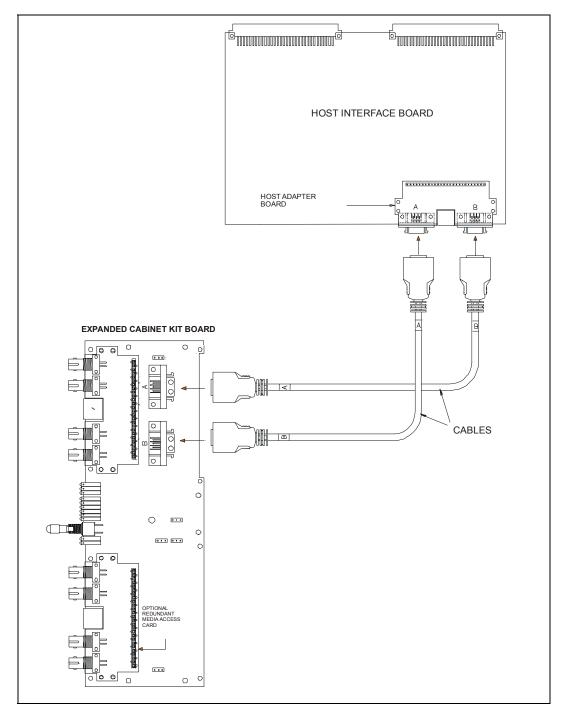

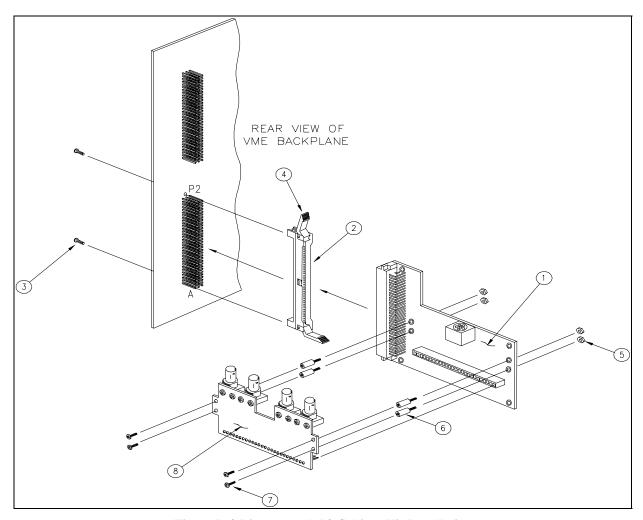

#### 4.3.3 J8/P2 Connection

If a cabinet kit is used in lieu of the Media Card, an adapter card is installed on J302 and J8. This forces the Media Card signals to J5. When four 9-pin headers are installed on J5, the Media Card Signals pass through to P2, row A. See Appendix C for the pinout description. Connection J8[26:1] corresponds to connection P2[26:1]. Refer to the SCRAMNet *Network Cabinet Kit Hardware Reference* for more details.

# 4.4 Externally Configure the Board

#### **4.4.1 EEPROM**

### **EEPROM WRITE JUMPER (J303)**

To enable the EEPROM WRITE place a 2-pin header on the top row as viewed from the face-plate edge of the board. To disable EEPROM WRITE place a 2-pin header on the bottom row. (Figure 4-3). Factory default setting: ENABLED

Figure 4-3 EEPROM WRITE (J303)

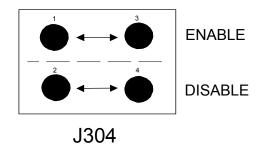

### **EEPROM READ JUMPER (J304)**

To enable the EEPROM READ place a 2-pin header on the top row as viewed from the faceplate edge of the board. To disable EEPROM READ place a 2-pin header on the bottom row. (Figure 4-4). Factory default setting: ENABLED

Figure 4-4 EEPROM READ (J304)

#### 4.4.2 CSR Address Switches

The CSR addressing for the VME6U bus can be short (16-bit), standard (24-bit) or extended (32-bit). The SCRAMNet+ CSRs must be configured on a contiguous 64-byte boundary.

Set the base address for the Control/Status Registers using S1 through S7 as indicated in Table 4-1 and Figure 4-2. Switch S1 contains the Most Significant Bits, and S7 contains the Least Significant Bits.

Factory Default settings: CSR ADDRESS: S1-S7 = 00000000

**Table 4-1 Setting the CSR Physical Address**

| Switch | Physical Address |     |          |          |

|--------|------------------|-----|----------|----------|

| S1     | A31              | A30 | A29      | A28      |

| S2     | A27              | A26 | A25      | A24      |

| S3     | A23              | A22 | A21      | A20      |

| S4     | A19              | A18 | A17      | A16      |

| S5     | A15              | A14 | A13      | A12      |

| S6     | A11              | A10 | A09      | A08      |

| S7     | A07              | A06 | Not used | Not used |

Table 4-2 Example of a CSR Address

| <b>S</b> 1      | S2              | S3              | S4              |

|-----------------|-----------------|-----------------|-----------------|

| A31 A30 A29 A28 | A27 A26 A25 A24 | A23 A22 A21 A20 | A19 A18 A17 A16 |

| 1               | Α               | В               | С               |

| S5              | S6              | <b>S7</b> | - |

|-----------------|-----------------|-----------|---|

| A15 A14 A13 A12 | A11 A10 A09 A08 | A07 A06   |   |

| 3               | 0               | 0         | 0 |

Table 4-2 contains an example of CSR address 0x1abc3000.

**NOTE:** The least significant hex digit is always zero, and no rotary switch is provided for bits. A[3:0]. Bite A15 and A4 are also always zero on switch S7. Switch S7 can only have the values 0, 4, 8 or C.

EXAMPLE of the 16-bit address 0x6000 = : S5 S6 S

S5 S6 S7 6 0 0

### 4.4.3 Resolution Bus Switch (S8)

Switch S8 is the Resolution Bus switch. Set switch S8 to the desired value as indicated in Table 4-3 and Figure 4-2.

Resolution bus switch factory default setting: 0x6-CSR A16 MEMORY A24

**CSR** Memory Value F A32 A32 A24 Ε A32 A24 A32 В A24 A24 Α A16 A32 7 A16 A24 6

**Table 4-3 Setting the Resolution Switch**

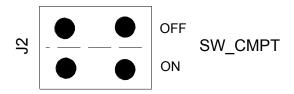

### 4.4.4 Software Compatibility (SW\_CMPT) (J2)

If the SCRAMNet+ board must be software compatible with SCRAMNet Classic interrupt addressing, set place a 2-pin header on the bottom row as viewed from the face-plate edge of the board (Figure 4-5).

Factory default setting: OFF

Figure 4-5 Software Compatibility (J2)

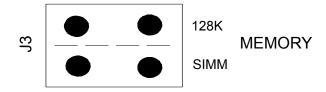

# 4.4.5 Memory Configuration (J3)

Figure 4-6 Memory Configuration (J3)

If no SIMMs are installed, two options are available

- 4 KB memory—install a 2-pin header on the bottom row.

- 128 KB memory—install a 2-pin header on the top row.

If SIMMs are installed, install a 2-pin header on the bottom row.

The SIMMs used with this board are proprietary, and must be ordered from Systran.

#### **OPTIONS**

```

Low density, 512 KB SIMMs 1 = 512 KB (SIMM 1)

2 = 1 MB (SIMM 1 and 2)

4 = 2 MB (SIMMs 1 through 4)

High density, 2 MB SIMMs 1 = 2 MB (SIMM 1)

2 = 4 MB (SIMM 1 and 2)

4 = 8 MB (SIMMs 1 through 4)

```

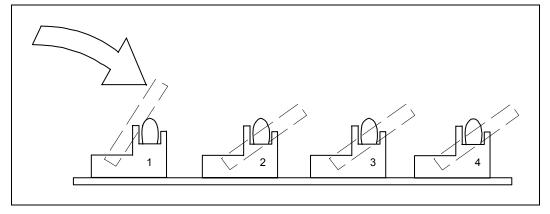

Figure 4-7 Install SIMMS

SIMMs must all be either low density or high density; they can not be mixed.

To install SIMMs, set the SIMM in the slot and gently press back and down until the clips snap into place (Figure 3-6).

To remove the SIMMs, push the clips gently to the outside with each thumb while gently pulling the SIMM toward you with your index fingers.

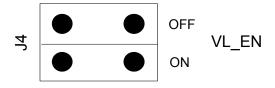

# 4.4.6 Variable Length Enable (VL\_EN) (J4)

If the network will be using variable-length message packets, set jumper J5 to ON (Figure 3-7).

Factory default setting: ON.

Figure 4-8 Variable Length Messages (J4)

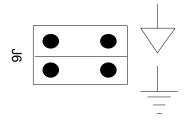

## 4.4.7 Ground Jumper (J6)

The Chassis/Signal Ground is a user option (Figure 3-8).

Factory default setting: CHASSIS GROUND  $(\frac{\bot}{=})$ .

Figure 4-9 Ground (J6)

### 4.4.8 External Trigger Connections

The SCRAMNet+ board generates two external triggers. Activating the triggers for any shared-memory location will cause an external trigger to be generated when the shared-memory location is accessed (Figure 3-9, Tables 3-5, 3-6).

Figure 4-10 External Trigger Connections (J7)

**Table 4-4 Trigger Pin Connections (J7)**

| Pins | Output         |

|------|----------------|

| 1    | TRIG2          |

| 2    | TRIG1          |

| 3    | TRIG1 or TRIG2 |

| 4    | GROUND         |

**Table 4-5 External Trigger Actions**

| Trigger | ACR   | Action             |

|---------|-------|--------------------|

| 1       | bit 2 | Host READ/WRITE    |

| 2       | bit 3 | Network READ/WRITE |

### 4.5 Install the Board

Once all the switch settings have been made, the board is ready to be installed so the CSRs may be accessed to continue configuration.

**CAUTION**: Make certain that the power to the host computer is OFF.

The SCRAMNet+ Network node requires one board slot in the backplane. Place the top and bottom edges of the board into the slide-guides of the card cage slots with the component side of the boards facing the same direction as the other existing boards. Slide the board in until it butts against the backplane. Using the levers on the lower end of the faceplate, seat the board in place on the backplane.

The machine is now ready to have power turned ON. Watch the Operator's Console for any booting problems that may occur due to improper settings which correspond to illegal address space or improper seating of the node.

# 4.6 Select Cabling Options

### 4.6.1 Cabinet Kit Connection

The SCRAMNet+ board that is configured to work with the cabinet kit has no Media Card of its own. The cabinet kit configuration is discussed in Appendix B.

#### FIBER-OPTIC CABLE PRECAUTIONS

Fiber-optic cables are made of glass and may break if crushed or bent in a loop with less than a 2-inch radius.

Perform a visual check of the cable ends before inserting into the Media Card connector. If debris is inserted into the transmitter/receiver connector, it may not be possible to clean it out and it could result in damage to the transmitter or receiver lens. Hair, dirt, and dust can interfere with the light signal transmission.

Use an alcohol-base wipe to clean the cable ends.

### 4.6.2 Fiber-Optic Configuration

The basic SCRAMNet+ Network communication architecture consists of SCRAMNet+ boards tied together by paired sets of fiber-optic cable in a ring configuration. The maximum recommended distance between each node of the network using this configuration is approximately 300 meters. Maximum node separation using long-link fiber is 3,500 meters. The recommended fiber-optic cable is 62.5/125 micron core multimode fiber cable with ST connectors.

**NOTE:** On a freshly powered system, a message from any node on the ring may be necessary to establish the carrier signal.

### 4.6.3 Coaxial Cable Configuration

SCRAMNet+ coaxial cable is composed of paired, shielded conductors terminated with SMA connectors. Maximum node separation using coax is 30 meters. The recommended coaxial cable is RG-58.

### 4.6.4 Fiber-optic Cables

The optional paired fiber-optic cables are shipped in a separate carton. The fiber-optic cables are to be attached to the connectors on the SCRAMNet+ board or the Cabinet Kit, as appropriate. Remove the rubber boots on the fiber-optic transmitters and receivers as well as the ones on the fiber-optic cables. These rubber boots should be replaced when cables are not in use or in the event the node must be returned to the factory.

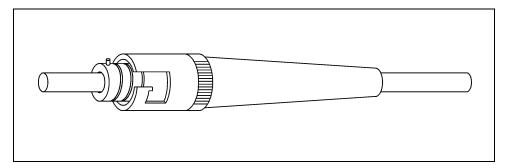

Figure 4-11 Fiber-optic ST Connector

It is important that the ends of the fiber-optic cable be kept clean. If there is an exceptional amount of light-power loss experienced, the cable ends should be inspected for cleanliness. Alcohol-based fiber-optic cleaning pads are available to remove minor contaminants such as dust and dirt.

Figure 4-11 is a representation of a fiber-optic connector.

## 4.6.5 Fiber-optic Connection

The fiber-optic cable transmitter pairs of the up-stream node are connected to the receiver pair of the down-stream node. Data flows from the transmitter pair of one node to the receiver pair of the next node as described in Figure 4-12.

**Figure 4-12 Fiber-optic Connections**

**NOTE**: It does not matter if  $Tx_1$  or  $Tx_2$  is connected to the next node's  $Rx_1$  or  $Rx_2$  as long as both Tx cables are connected to both of the next node's Rx connectors

# 4.7 Install Fiber Optic Bypass Switch (Optional)

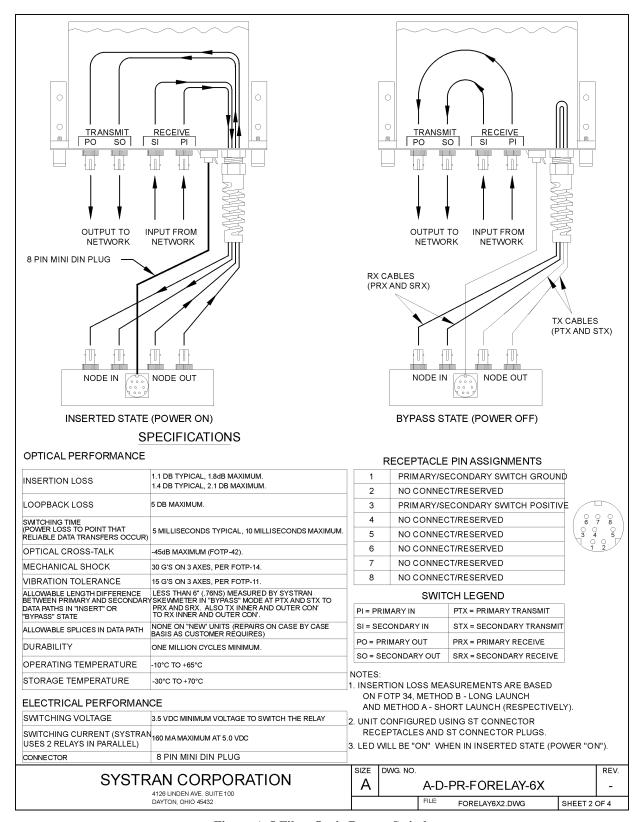

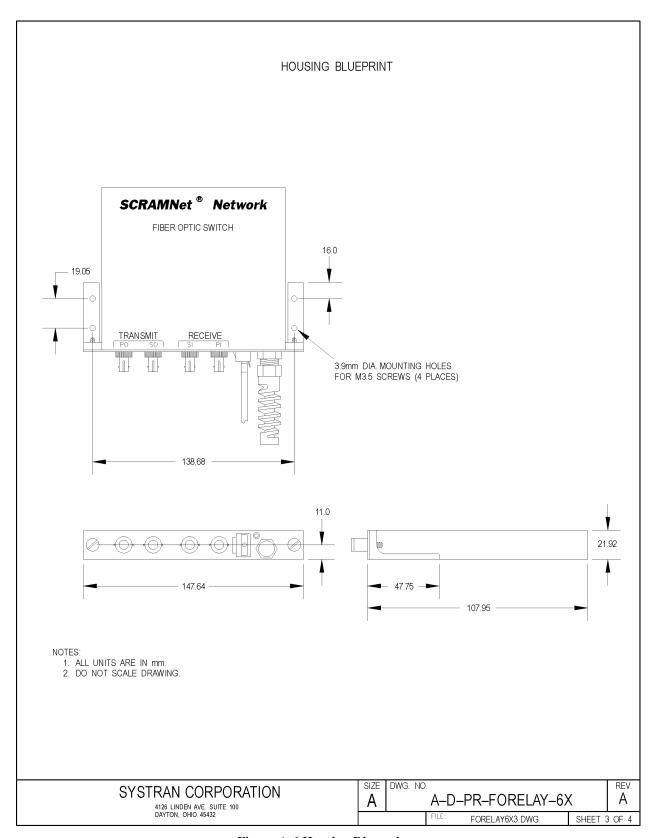

Make Fiber Optic Bypass Switch connections as shown in Figure 4-13 and Figure 4-14.

Figure 4-13 Inserted State (Power On)

Figure 4-14 Bypass State (Power Off)

## 4.7.1 Auxiliary Connection

The optional Fiber Optic Bypass switch is used to provide an uninterrupted fiber-optic path when the node is not powered up.

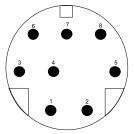

The Auxiliary Connection at the Media Card is used for communication with the Fiber Optic Bypass Switch. The 8-pin modular in-line plug male-pin connection (Figure 4-15) is defined in Table 4-6. (The view in Figure 4-15 is looking into the connector.)

**Table 4-6 Auxiliary Connection Pinout**

| Pins | Name    | Definition                            |  |

|------|---------|---------------------------------------|--|

| 1    | GND     | Logic Ground                          |  |

| 2    | S_CLK   | Serial Clock                          |  |

| 3    | F_RELAY | Fiber-optic Relay Drive and Sense     |  |

| 4    | S_DATA  | Serial Data                           |  |

| 5    | EXT_PWR | +5 Source to External Ground          |  |

| 6    | S_DIR   | Serial Data Direction                 |  |

| 7    | TRIGGER | Trigger Output (TRIG1)                |  |

| 8    | BAK_PWR | Backup +5 Source from External Device |  |

Figure 4-15 Auxiliary Connection

**NOTE:** Specifications for the Fiber Optic Bypass Switch are contained in Appendix A.

# 4.8 Internally Configure the Board

Specific items which must be configured through the CSRs include: Node ID, network time-out, memory addressing, shared memory on/off, BURST PLUS protocol on/off, interrupt options, and virtual paging.

#### INITIALIZATION

The EEPROM is used to store the initial power-up register values. The EEPROM can be programmed either over the host backplane or by most PROM programmers. An EEPROM initialization program is included in the Core Software Package offered by SYSTRAN Corp.

The initialization of the SCRAMNet+ node from a cold boot is determined by the settings of the EEPROM as indicated in Table 4-7.

0 2 Α С Ε 4 6 8 00 0000 0000 C040 XX00 XX00 0010 0000 0000 0FF0 0000 0000 0020 10 0800 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 XXXX YYYY YYYY 5555 70 ZZZZ 5555 5555 5555

**Table 4-7 EEPROM Table**

NOTE: XXXX: 00A1=ASIC1, 00B1=ASIC2; YYYY ignore; ZZZZ = Serial Number

The board comes with power-up default values in each of the registers and default switch settings so the board can be used without making any changes. Defaults are shown in Table 4-8

| SCRAMNet+ Registers                                |                                                                     |  |  |  |

|----------------------------------------------------|---------------------------------------------------------------------|--|--|--|

| CSR0 - 0                                           | CSR1 - READ Only (Errors)                                           |  |  |  |

| CSR2 - 0xC040 (BURST Mode)                         | CSR3 - Node ID (0 - 255)                                            |  |  |  |

| CSR4 - 0 (READ Only)                               | CSR5 - 0x0010 READ Only (WRITE Network Time-out to shadow register) |  |  |  |

| CSR6 - 0 (Data Vector)                             | CSR7 - 0 (Error Vector)                                             |  |  |  |

| CSR8 - 0x0800 (Mech Switch Override) <sup>\$</sup> | CSR9 - 0x0FF0 (Error Mask)#                                         |  |  |  |

| CSR10 - 0 (SM Address LSW)                         | CSR11 - 0 (SM Address MSW)                                          |  |  |  |

| CSR12 - 0 (Virtual Page)                           | CSR13 - 0 (GP Counter)                                              |  |  |  |

| VME Registers                                      |                                                                     |  |  |  |

| CSR14 - 0 (Reserved)                               | CSR15 - 0x20 (Interrupt Level 5)                                    |  |  |  |

| CSR16 - 0 (HIPRO READ)                             |                                                                     |  |  |  |

**Table 4-8 EEPROM Initialization**

These values are assigned to the Control/Status Registers on power-up. The values may be changed at any time using the appropriate software to access the CSRs. When the system is powered down and powered up again, the CSRs will be reinitialized to these EEPROM values.

<sup>\$</sup> VME HOLDOFF is enabled

<sup>#</sup> Normal Error Masking enabled

#### 4.8.1 Node Identification

All nodes in the ring must have a unique Node ID. To set the Node ID, WRITE a unique value 8-bit number between 0 and 255 to CSR3[15:8].

#### 4.8.2 Network Time-out

The recommended value for the Network Time-out is:

#### # NODES IN RING + (TOTAL LENGTH OF CABLE IN METERS+50) + 1

To set the network time-out value, WRITE the result as a 16-bit hexadecimal number to CSR5. This register has a "shadow register" which holds the network time-out value. Each increment in the "shadow register" is worth approximately 240 ns. The time-out will be 240 ns multiplied by the value written.

The time-out register is WRITE ONLY. If a READ is performed, it will result in a READ to the Interrupt FIFO.

**CAUTION**: Ensure a non-zero value is written to CSR5. A value of '0' will keep host-generated data from leaving the Transmit FIFO

### **4.8.3 Memory**

#### **MEMORY ADDRESSING**

The memory base address is software configurable anywhere through the A24 and A32 address space. If the shared-memory and CSR addresses should overlap, the CSR s will be decoded making the overlapped memory inaccessible.

The Least Significant Word (LSW) of shared-memory address is in CSR10[15:12]. The Most Significant Word (MSW) of shared-memory address is contained in CSR11[15:0].

#### SHARED MEMORY

SMA\_ENABLE CSR10[0] must be set ON to enable the shared-memory address decoder.

# 4.9 Byte Swapping

Some computer systems use different methods of byte ordering. Some have the high bits arranged from right to left (Little Endian) and other have the high bits going from left to right (Big Endian). Motorola is an example of a Big-Endian system. Intel is an example of a Little-Endian system.

Table 4-9 is a simplified summary for 8-bit, 16-bit, and 32-bit byte ordering for big endian and little endian.

Size

Big Endian

Little Endian

byte (8-bit)

12 34 56 78

78 56 34 12

shortword (16- bit)

1234 5678

5678 1234

longword (32-bit)

12345678

12345678

Table 4-9 Big Endian - Little Endian Comparisons

The SCRAMNet-LX and SCRAMNet+ product line has adopted the big-endian ordering philosophy as the default for data passing. SCRAMNet-LX and SCRAMNet+ do not have a built-in byte-ordering conversion function.

# 4.10 Troubleshooting

On UNIX-like systems, the driver will output a message on boot up similar to the following:

```

SCRAMNet+ installed and on line

```

If this message does not appear then one or more of the following is <u>not</u> correct:

- Physical address for the CSRs switch selection on the board.

- VME address bus for the CSRs (16- or 24-bit)

- The address for the CSRs in the system files is not correct.

- The driver was not installed into the new kernel properly.

#### 4.10.1 Other H/W Considerations

- The SCRAMNet+ Network is not installed into a standard VME slot. Some vendors mix VME and their own private bus in what appears to be the same backplane. This check should be performed before installing the SCRAMNet+ Network card into any slots.

- The Bus Resolution switch (S8) is set incorrectly. See Table 4-3 on page 4-6.

- The memory bus address and/or bus size is set incorrectly.

- The CSR bus address and/or bus size is set incorrectly.

- The interrupt request level is set too high (7).

- The memory is installed at an improper boundary for the size of memory. For example, a 2 MB board can not be installed at hex address 10500000. However, 10400000 or 10600000 are on 2 MB boundaries.

# 4.10.2 Customer Support

If the system does not boot correctly, reseat the board and double-check cable connections. If problems persist, call Systran Customer Support at (937) 252-5601 for assistance.

|                  | <br>• |  |

|------------------|-------|--|

| Host machine:    |       |  |

| Operating System |       |  |

| Name:            |       |  |

| Version:         |       |  |

| Rus Interface:   |       |  |

Please be prepared to supply the following information:

This page intentionally left blank

# 5. OPERATION

### 5.1 Overview

The SCRAMNet+ Network is a shared-memory system. Every computer on the network has a constantly updated local copy of all global data that is passed to all the network computers. The network protocol is implemented in the SCRAMNet+ hardware and therefore no software overhead is required to retrieve this information from the network.

The protocol is transparent to the computer. This frees computer processor time for application algorithm execution and other real-time tasks. Since any computer on the network has access to data in the shared memory, any computer can read or modify the shared data and thereby communicate with the other computers on the network.

Very little special software is required for normal operation because of the SCRAMNet+ shared-memory configuration. Typically, SCRAMNet+ memory is installed and linked to a host global common block through the host operating system. Once the link is complete, any program can reference SCRAMNet+ memory as a standard common-block variable reference.

For interrupt driven applications, an interrupt service routine (ISR) is required to handle the interrupts triggered by the SCRAMNet+ node. An example of a generic ISR is included at the end of this section, Figure 5-11, page 5-29.

# **5.2 Shared Memory**

Global variables are mapped directly onto the replicated shared memory. The application program typically contains a list of variables or arrays which are stored in a contiguous space and which are to be shared across processors. The analogy of a FORTRAN COMMON BLOCK is most fitting. For the purpose of identification, these variables are referred to as SCRAMNet+ variables.

The application program usually requires a short section of instructions to initialize the SCRAMNet+ hardware and to link the SCRAMNet+ memory to the SCRAMNet+ variable list. The shared memory cannot be used as instruction space.

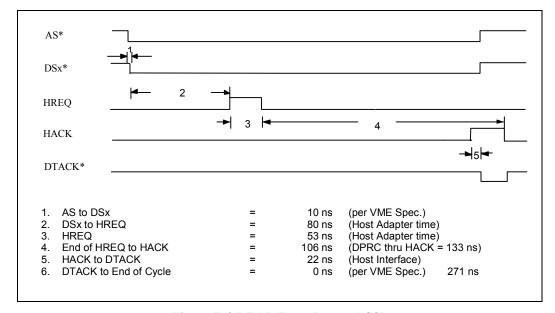

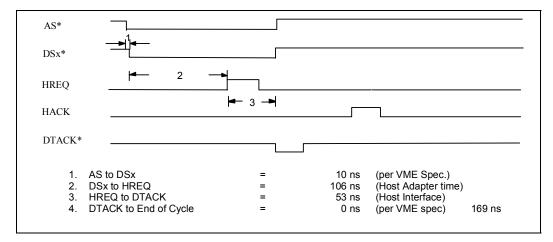

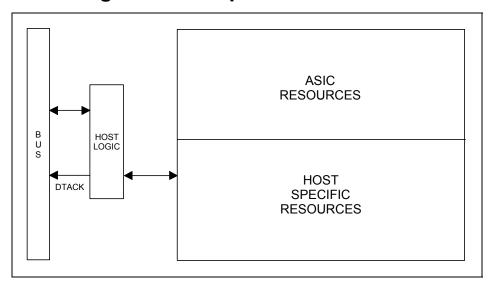

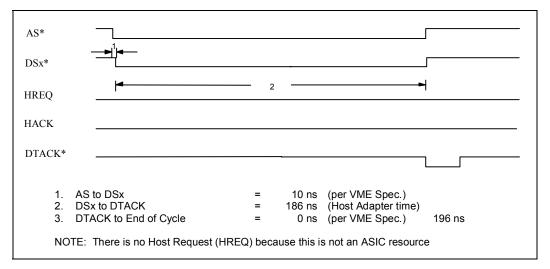

# 5.2.1 Virtual Paging