#### High Performance Digital Signal Processing (DSP)

In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/61739-1

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

Your definitive source for quality pre-owned equipment.

**Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

The future of high-integrity, embedded technology

# Manual for the IXA4 Quad PowerPC Board

Version 2.8 September 2002

Address: Dy 4 Systems, Inc.

741-G Miller Drive, SE Leesburg, VA 20175

Telephone: (703) 779-7800 FAX: (703) 779-7805 Internet: www.dy4.com

Information furnished by Dy 4 Systems, Inc. is believed to be accurate and reliable. However, Dy 4 Systems, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Dy 4 Systems, Inc.

Dy 4 Systems, Inc. reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Dy 4 Systems, Inc. to notify any person or persons of such revision or changes.

No part of this document may be reproduced or copied in any tangible medium, or stored in a retrieval system, or transmitted in any form, or by any means, radio, electronic, mechanical, photocopying, recording, or facsimile, or otherwise, without prior written permission from Dy 4 Systems, Inc.

Trademarks used herein are the property of their respective companies.

PICMG® and CompactPCI® are registered trademarks of the PCI Industrial Computers Manufacturers Group

*PowerPC*<sup>TM</sup> is a trademark of International Business Machines Corporation.

VxWorks™, Tornado™, and WindSh™ are trademarks of Wind River Systems, Inc.

$\ensuremath{\mathbb{C}}$  2000-2002 Dy 4 Systems, Inc.

ALL RIGHTS RESERVED

PRINTED IN THE USA

# **Customer Support**

## Technical Support Hotline

If you have any questions about the IXA4, please contact Dy 4 Systems, Inc.

**Telephone:** (703) 779-7800

**FAX:** (703) 779-7805

email: support@dy4.com

**Address:** Dy 4 Systems, Inc.

741-G Miller Drive, SE Leesburg, VA 20175

#### Sales Hotline

If you desire product pricing and availability, please contact Dy 4 Systems, Inc.

**Telephone:** (703) 779-7800

**FAX:** (703) 779-7805

email: sales@dy4.com

**Address:** Dy 4 Systems, Inc.

741-G Miller Drive, SE Leesburg, VA 20175

# **Table of Contents**

| Chapter 1: Getting Started                   | 1-1  |

|----------------------------------------------|------|

| 1.1 Introduction                             | 1-1  |

| 1.2 Assumptions                              |      |

| 1.3 Conventions                              |      |

| 1.4 Product Overview                         |      |

| 1.5 Related Documentation                    |      |

| Chapter 2: Installation                      |      |

| _                                            |      |

| 2.1 Some Cautions                            |      |

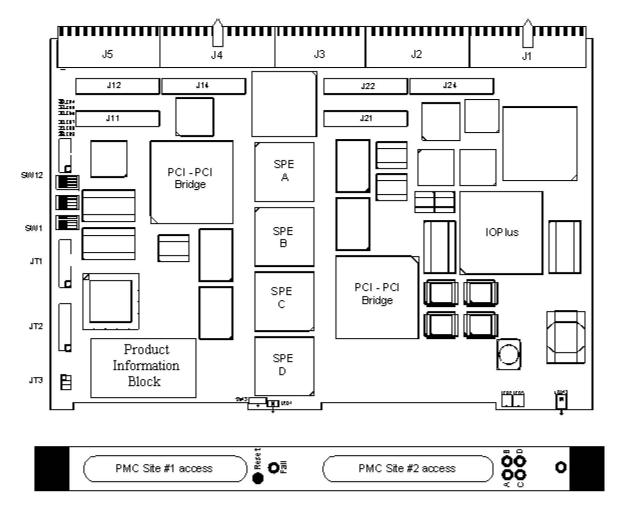

| 2.2 Board Layout                             |      |

| 2.3 Configuring the Board's DIP Switches     |      |

| 2.4 CompactPCI Interface                     |      |

| 2.5 Installing PMCs                          |      |

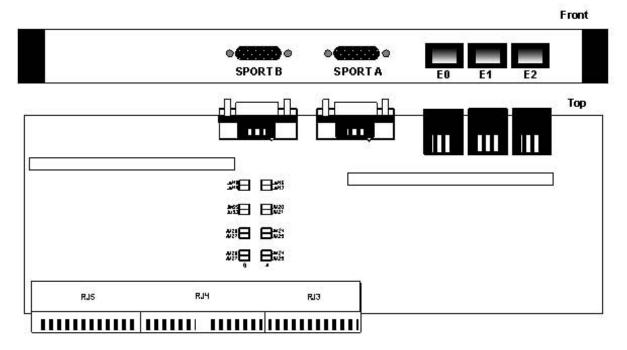

| 2.6 Installing the Rear Panel Module         |      |

| 2.7 Verifying cPCI Backplane Power           |      |

| 2.8 Board Boot Operation                     |      |

| 2.9 Power-up Diagnostics                     |      |

| 2.10 FLASH Recovery Procedure                |      |

| 2.11 JTAG/COP Connections                    |      |

| 2.12 Configuring an Emulator for an IXA4     |      |

| 2.13 Configuring the VxWorks Boot Parameters |      |

| 2.14 Installing IXAtools                     | 2-19 |

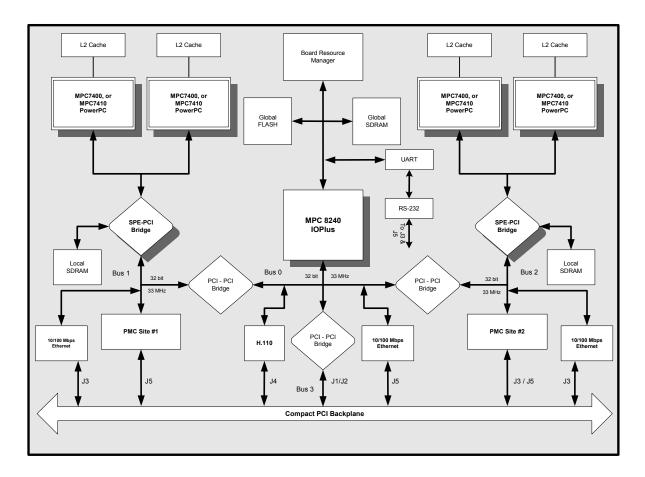

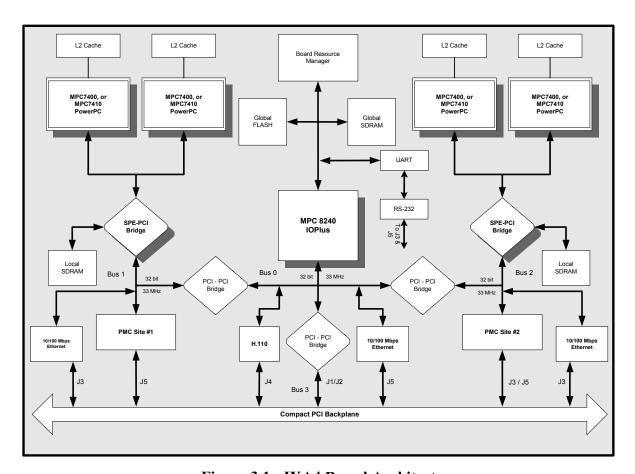

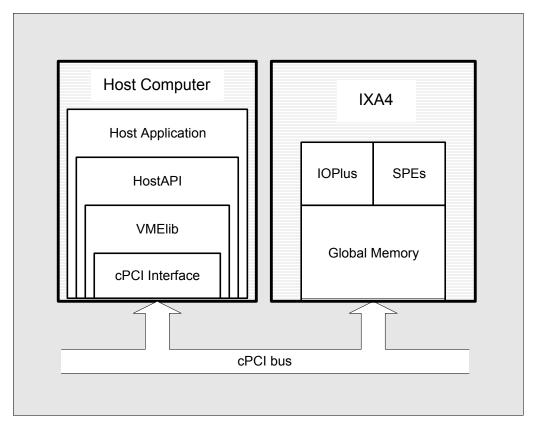

| Chapter 3: Hardware Architecture             | 3-1  |

| 3.1 Introduction                             | 3-1  |

| 3.2 IOPlus                                   |      |

| 3.3 SPEs                                     |      |

| 3.4 SPE-PCI Bridge                           |      |

| 3.5 PCI Local Bus.                           |      |

| 3.6 Board Resource Manager                   |      |

| 3.7 Board Semaphores                         |      |

| 3.8 Global Memory                            |      |

| 3.9 SPE Local Memory                         |      |

| 3.10 FLASH Memory                            |      |

| 3.11 PMC Sites                               |      |

| 3.12 cPCI bus Interface                      |      |

| Chapter 4: Memory Maps                       |      |

| 4.1 Introduction                             |      |

|                                              |      |

| 4.2 IOPlus Memory Map                        |      |

| 4.3 SPE Memory                               |      |

| 4.4 Global Memory                            |      |

| 4.5 cPCI Memory                              |      |

| 4.6 Board Resource Manager Register Map      |      |

| Chapter 5: Using the IOPlus                  | 5-1  |

| 5.1 Introduction                             |      |

| 5.2 Command / Response Packet Format         |      |

| 5.3 Packet Routing and Processor IDs         | 5-2  |

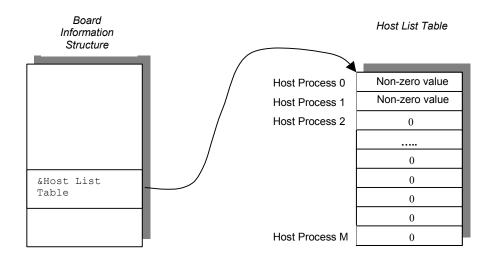

| 5.4 Assignment of IDs to Host Processes      | 5-4  |

| 5.5 Board Information Structure                                             |      |

|-----------------------------------------------------------------------------|------|

| 5.6 Linked Command List Overview                                            |      |

| 5.7 Linked List Management Protocol                                         |      |

| 5.8 Command Option and Status Register Definition                           |      |

| 5.9 Interrupt Protocol                                                      |      |

| 5.10 Semaphore Protocol                                                     |      |

| 5.11 FLASH Memory Management Protocol                                       |      |

| 5.12 IOPlus Command List                                                    |      |

| CMD_GENERATE_INT                                                            |      |

| CMD_LOOPBACK                                                                |      |

| CMD_MOVE_DATA                                                               |      |

| CMD_READ_DATA                                                               |      |

| CMD_RESET                                                                   |      |

| CMD_SUPPORT_QUERY                                                           | 5-29 |

| CMD TOGGLE LED                                                              | 5-30 |

| CMD USER                                                                    | 5-31 |

| CMD WAIT INT                                                                | 5-32 |

| CMD WRITE DATA                                                              | 5-34 |

|                                                                             | ( 1  |

| Chapter 6: Programming the IOPlus                                           | 6-1  |

| 6.1 Introduction                                                            | 6-1  |

| 6.2 VxWorks and the IOPlus                                                  |      |

| 6.3 The IOPlus Application Programming Interface                            |      |

| ioplus calloc                                                               |      |

| ioplus check pci dma done                                                   |      |

| ioplus free                                                                 |      |

| ioplus generate interrupt                                                   |      |

| ioplus malloc                                                               |      |

| ioplus move data                                                            |      |

| ioplus pci find device                                                      |      |

| ioplus read data                                                            |      |

| ioplus realloc                                                              |      |

| ioplus reset                                                                |      |

| ioplus_resetioplus_toggle_led                                               |      |

| ioplus write data                                                           |      |

| • – –                                                                       |      |

| Chapter 7: Programming the SPEs                                             | 7-1  |

| 7.1 SPE Software Development                                                | 7_1  |

| 7.2 The Common Boot Code                                                    |      |

| 7.3 Performance Monitoring Capabilities                                     |      |

| 7.4 VxWorks and the SPEs.                                                   |      |

| 7.5 Commanding the IOPlus from a SPE                                        |      |

| 7.6 Function Reference                                                      |      |

| getchar                                                                     |      |

| ixa cache enable                                                            |      |

| ixa cache disable                                                           |      |

| ixa_cache_flush                                                             |      |

|                                                                             |      |

| ixa_cache_invalidate                                                        |      |

| ixa_cache_inv_all                                                           |      |

| ixa_cache_sync                                                              |      |

| ixa_cache_throttle_read                                                     |      |

| ixa_cache_throttle_write                                                    |      |

| ixa_cmd_close                                                               |      |

| ixa_cmd_error                                                               |      |

| ixa_cmd_open                                                                |      |

| ixa_cmd_set_next, ixa_cmd_set_opcode, ixa_cmd_set_option, ixa_cmd_set_param | /-35 |

| ixa cmd start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 7-37          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| ixa cmd status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 7-38          |

| ixa cmd stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 7-39          |

| ixa cmd VME error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 7-40          |

| ixa_cmd_VME_read, ixa_cmd_VME_write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 7-41          |

| ixa cmd VME status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

| ixa CPCI close                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

| ixa CPCI open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

| ixa CPCI read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

| ixa CPCI to local, ixa local to CPCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |

| ixa CPCI write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

| ixa delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |

| ixa delay msec, ixa delay sec, ixa delay usec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

| ixa dma init                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |

| ixa dma start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

| ixa evt disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| ixa_evt_enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

| ixa evt get                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |

| ixa evt set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |

| ixa_evt_restore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| ixa_flash_delete, ixa_flash_read, ixa_flash_write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |

| ixa get cluster id                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

| ixa get proc id                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| ixa get proc info                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |

| ixa_get_proc_titjoixa_get_proc_rev                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

| ixa_get_proc_revixa_get_proc_type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |

| ixa_get_proc_typeixa_get_sysproc_id                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |

| ixa_gei_sysproc_iaixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa_initixa |                 |

| ixa_int_ack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| ixa_int_disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| ixa_int_enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

| ixa_int_getvect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| ixa_int_lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |

| ixa_int_setpri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

| ixa_int_setvect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| ixa_int_unlock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

| ixa_ipi_ack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |

| ixa_ipi_disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

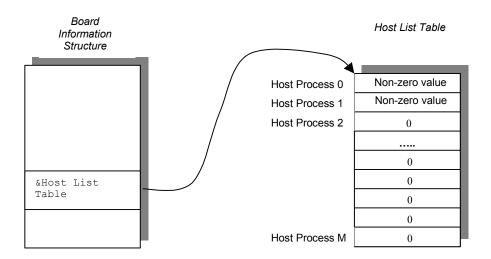

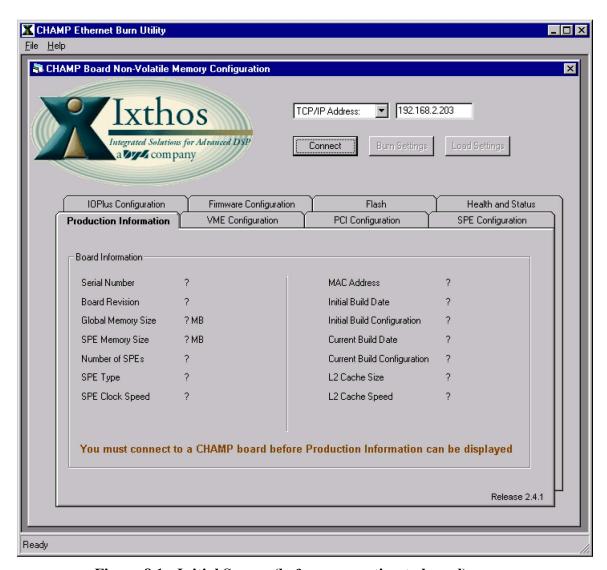

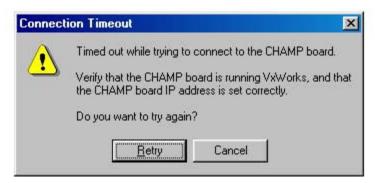

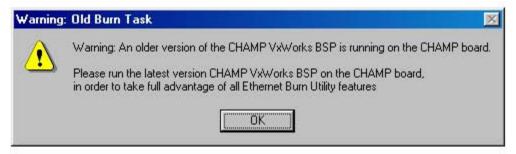

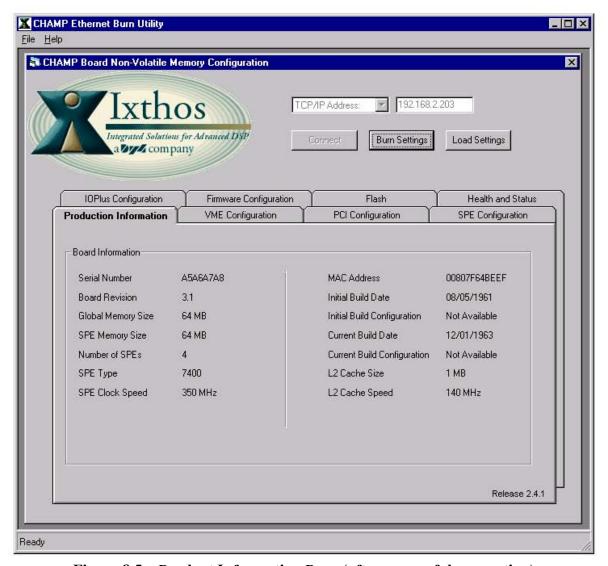

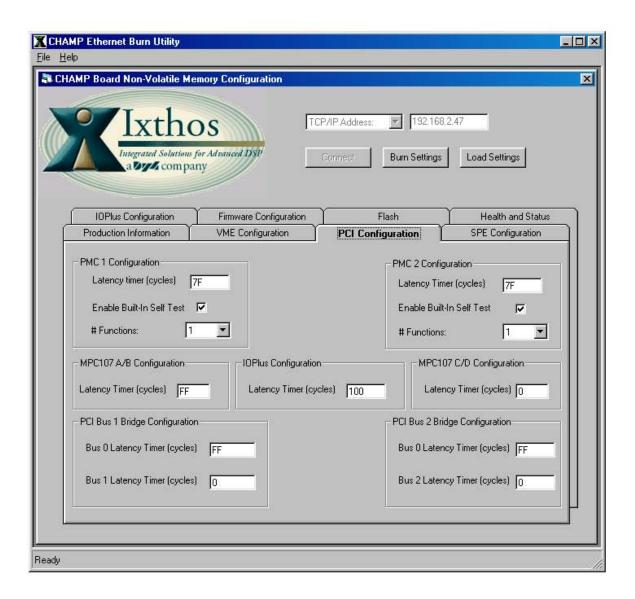

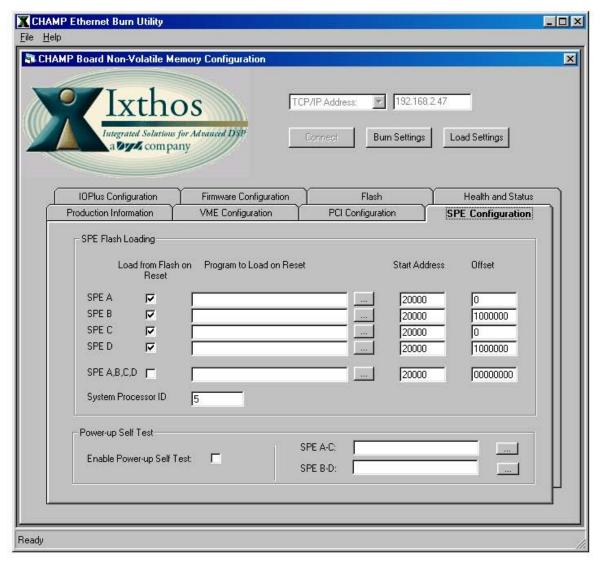

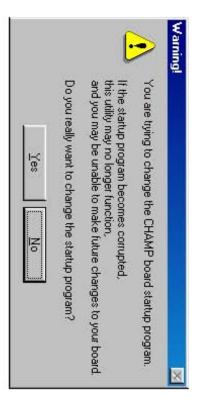

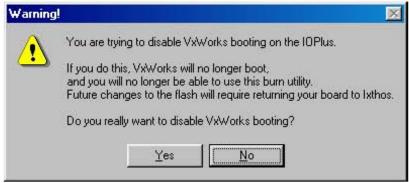

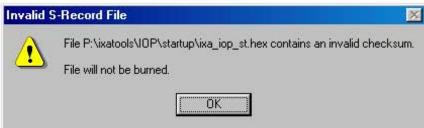

| ixa_ipi_enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |