# Motorola MVME130 Single Board Computer

In Stock

**Used and in Excellent Condition**

**Open Web Page**

6 Artean Technology Group

https://www.artisantg.com/71423-1

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

TECHNOLOGY GROUP

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# VMEmodule 32-Bit Monoboard Microcomputer

The VMEmodule 32-bit Monoboard Microcomputer (MVME130) is designed to function in those applications requiring maximum performance while maintaining the versatility inherent in VMEmodule systems. Highest performance is attained when the MVME130 is used in conjunction with one or more MVME204 Dual Ported RAM Cards operating as a main memory. The MVME130 is the first VMEmodule product to offer the following:

- MC68020 Microprocessor with 32-bit Address and Data VMEbus Interface

- Provision for MC68881 Floating Point Coprocessor (customer-supplied option)

- Provision for Demand Paged Virtual Memory Management Board (MMB) Implemented with Gate Array Technology.

- Two 28-pin JEDEC Sockets for up to 16Kb Onboard Static RAM

- VSB\* Interface Provides High-speed Data Path to/from Memory

- VMEbus Interface Allows User Configuration of Microcomputer System to Fit the Application

- VMEbus Interrupter, Interrupt Handler, and Arbiter Onboard

- Programmable Timer Module

- Dual Multiprotocol Serial I/O Ports

- Accepts MVME130bug Debug Monitor Firmware (optionally available)

- Two ROM Sockets Configured for Industry Standard 28-Pin ROM/EPROM devices. Four ROM Sockets Available when no Sockets are Devoted to RAM

- Broadcast Interrupt Capability for Multi-processor Synchronizing Applications

#### CPU

The MVME130 uses an MC68020 Microprocessor operating at a fixed speed of 12.5 MHz. This CPU will eventually operate at 16.67 MHz on the MVME130. The MC68020 is the first product within the popular MC68000 family to offer external 32-bit address and data paths. With its higher clock rate, advanced architecture, enhanced addressing modes, and on-chip instruction cache, this product offers state-of-the-art performance while maintaining software compatibility with its widely accepted predecessors.

### **DEBUG MONITOR FIRMWARE**

The MVME130bug Debug Monitor firmware package is optionally available for use with the MVME130 module. This firmware offers 32 debug, up/downline load, one line assembler/disassembler and disk bootstrap load commands.

### COPROCESSOR

The MVME130 module is equipped with a socket to accept the MC68881 Floating Point Coprocessor, a customer supplied option. When available and installed, the MC68881 Floating Point Coprocessor will improve computing speed of the MVME130 when the system is utilized in applications requiring arithmetic operations.

The MVME130 utilizes the MC68020 Coprocessor Interface to provide a logical extension to the MC68020 architecture and instruction set.

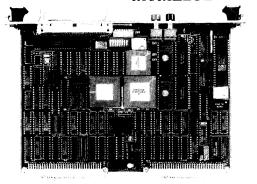

Figure 1 is a block diagram of the MVME130 module.

### FIGURE 1 — MVME130 32-Bit Microcomputer Module

### **MEMORY MANAGEMENT**

The MVME130 is designed to eventually utilize the MC68851 Demand Paged Virtual Memory Management Unit. However, one initial version of the MVME130 (MVME131) utilizes a Memory Management Board (MMB) which conforms to a subset of the MC68851. This subset is implemented via gate array technology together with other semi-conductor devices mounted on a secondary PC board. The socket assigned for future use with the MC68851 is utilized to mount the secondary PC board in a mezzanine fashion on the introductory version of the MVME130. The MMB offers the following features:

- Logical address consisting of:

- 32-bit Address

- 3-bit Function Code

- · Physical address output of 32 bits.

- · Logical to physical address translation;

- Table walking algorithm

- Single logical bus master

- Single page size (1Kb)

- Used, modified, and write protect bits.

- Supports MC68020 and external data cache.

- 512 entry set associative cache.

The eventual use of the MC68851 will add multiple Protection/Privilege capabilities.

The principal operating function of the MMB on the MVME130 is to provide the hardware logical to physical address translation and access protection necessary for operating system support. The MMB logical to physical translation mapping function utilizes a table-walking algorithmic search through memory-resident translation tables. The MMB utilizes a cache architecture to eliminate table-walking for most CPU bus cycles.

The MMB utilizes the MC68020 clock circuitry, but does not use the coprocessor interface. This requires the internal

registers to be in the CPU address space, whereas the MC68851 internal registers will be accessed via the coprocessor interface. This will require a change in driver routines when the MC68851 is used with the MVME130.

#### ONBOARD STATIC RAM

The MVME130 Static Memory is implemented with two 28-pin industry-standard JEDEC sockets. The MVME130 will provide 16Kb of single-ported memory for the MC68020 local processor. However, if the user does not require the onboard memory, the two static RAM sockets can be reconfigured to accept EPROMS up to 512K in size.

### **VSB INTERFACE**

The VSB Interface occupies 64 P2 I/O pins and is designed to serve as the system's high-speed memory access channel. The signals utilize multiplexing of address and data in order to accommodate full 32-bit functionality, along with appropriate control signals, into the 64-pin allotment.

The VSB Interface on the MVME130 is limited to one master. The interface can be turned off via a control bit to force all accesses to go to the VMEbus, and speed up VMEbus accesses. The MVME130, with one or more MVME204's, creates a memory system with performance similar to that of a VMEmodule with onboard memory, but with virtually unlimited memory size constraints.

### **MEMORY MAP**

The address map, (refer to Table 1) indicates the 32-bit address map for different devices addressed by the MVME130. The 24-bit address map is determined by eliminating the two most significant hex digits from the 32-bit addresses. A control bit on the control register allows the user to switch between 16- and 32-bit data paths, and between 32-/24-bit address modifier codes.

### TABLE 1 -- Address Map

| Device           | Physical Address  | Comments                                                               |

|------------------|-------------------|------------------------------------------------------------------------|

| VMEbus/VSB       | 00000000-FFEFFFF  | 32/16-bit port size; R/W.                                              |

| ROM              | FFF00000-FFF8FFFF | 16-bit port size; read only.                                           |

| Local Static RAM | FFF20000-FFF2FFFF | 16-bit port size; R/W.                                                 |

| Spare            | FFF40000-FFF6FFFF | 32-bit port size; R/W provided for cache expansion ability.            |

| Timer            | FFFBxx00-FFFBxx2F | 8-bit port size; R/W.                                                  |

| Status & Control | FFFBxx30-FFFBxx3F | 32-bit port size; Status is read only; Control is R/W.                 |

| Serial I/O Port  | FFFBxx40-FFFBxx5F | 8-bit port size; most are R/W.                                         |

| Reserved         | FFFBxx60-FFFBxx6F | Unimplemented.                                                         |

| Spare            | FFFBxx70-FFFEFFFF | Unimplemented; Access will cause LBTO (BERR source) cycle termination. |

| VMEbus Short I/O | FFFF0000-FFFFFFF  | 16-bit; R/W; VMEbus Short I/O Address Modifier will be generated.      |

### PROGRAMMABLE TIMER MODULE

The MVME130 Programmer Timer Module provides the following:

- Three Cascadable, Independent 16-bit Counters

- Interrupt Capability

#### SERIAL I/O

The MVME130 is equipped with two multiprotocol serial I/O ports with connection via a 50-pin flat ribbon cable connector at the top of the board. Signal levels at this connector correspond to TTL specifications. A transition board/cable/connector (MVME707) is made available to transform the TTL levels to RS-232C and provide a standard DB-25 interface. The ports have the following features:

- Programmable Baud Rates

- Full and Half Duplex Compatibility

- 5- to 8-bits Per Character Plus Parity

- Synchronous or Asynchronous Operation, Including

- Byte-oriented protocols (BISYNCH)

- Bit-oriented protocols (SDLC)

Data Rate Capability to 800 Kilobits/Second

### STATUS/CONTROL REGISTERS

The MVME130 Status and Control Registers provide local and system wide status information to the on-board MPU. By reading the Status and Control register bits, the MPU can determine VMEbus information, interrupt status, the source of a particular BERR, and which self-test to perform. The MVME130 Status/Control Register bits control the module's hardware by providing configuration and control information to the VMEbus Interrupter, the Interrupt Handler, the VMEbus Arbiter and VSB. For example, the Multi-Processor Interrupt Request (MPIRQ\*) is an input from the VMEbus IRQ1\* signal. MPIRQ\* enables the user to interrupt several MVME130 modules in a multi-processor system with a single VMEbus interrupt.

The Control Register bits are software alterable. The Status/Control registers are privileged resources and in special cases can be made accessible by the user. The Status Register format is shown in Table 2 and the Control Registers are described in Table 3.

# TABLE 2 — Status Register Format

| <stat0></stat0>        |               | .,,_                                                                                                                                            |                                       | g                 | <b></b>       |                                |              |

|------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|---------------|--------------------------------|--------------|

| 31                     |               |                                                                                                                                                 | Front Panel Sw                        | ritch Selectable  |               |                                | 24           |

| MODE                   | AMSEL         | SC*                                                                                                                                             | GPC                                   | GPB               | GPA           | GP9                            | GP8          |

|                        |               |                                                                                                                                                 |                                       |                   |               |                                |              |

| <stat1><br/>23</stat1> |               |                                                                                                                                                 | Front Panel Sw                        | itch Selectable   |               |                                | 16           |

| GP7                    | GP6           | GP5                                                                                                                                             | GP4                                   | GP3               | GP2           | GP1                            | GP0          |

| <b>4</b>               |               |                                                                                                                                                 | ME130 Networking<br>as general purpos | •                 |               |                                |              |

| <stat2><br/>15</stat2> |               |                                                                                                                                                 | Power Up Rese                         | et Condition: "1" | ,             |                                | 0            |

| **                     | **            | ABORT                                                                                                                                           | SYSFAIL*                              | VBERR*            | VXBERR*       | MMUBERR*                       | LBTO*        |

|                        |               |                                                                                                                                                 | <b>4</b>                              | BERR S            | Source Status | Register                       |              |

| (**denotes: un         | implemented — | - always read a                                                                                                                                 | as "1").                              | •                 |               |                                |              |

| ODE, AMSEL             |               | /MEbus Mode:                                                                                                                                    |                                       | VBEF              |               | VMEbus BERR F                  |              |

| C*<br>PC-GP0           | ,             | rstem Controlle<br>rpose User Sta                                                                                                               |                                       | VXBE<br>MMU       |               | VSB BERR Flag<br>MMU BERR Flag |              |

| BORT<br>YSFAIL*        |               | <general bits="" purpose="" status="" user=""> <abort pushbutton="" status=""> <vmebus failure="" flag="" system=""></vmebus></abort></general> |                                       | LBTC              | O* <          | Local Bus Timeor               | ut BERR Flag |

## **TABLE 3** — Control Register Format

| <cnt0></cnt0>                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    |                                                                            |                                                                               |                                                                                                                               |                                                                          |                        |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------|

| 31                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    | Power Up Rese                                                              | t Condition: "1"                                                              |                                                                                                                               |                                                                          | 24                     |

| VBV7                                                                           | VBV6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VBV5                                                                                                               | VBV4                                                                       | VBV3                                                                          | VBV2                                                                                                                          | VBV1                                                                     | VBV0                   |

| <b></b>                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    | - VMEbus IRQ                                                               | Vector -                                                                      |                                                                                                                               |                                                                          |                        |

| <b></b>                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    | - Port A on the                                                            | Z8036 Timer -                                                                 |                                                                                                                               |                                                                          |                        |

| <cnt1></cnt1>                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    | Power Up Rese                                                              | t Canditian: "4"                                                              |                                                                                                                               |                                                                          |                        |

| MPIRQ*                                                                         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | T                                                                                                                  | <del>,                                      </del>                         | Reserved                                                                      | Reserved                                                                                                                      | Reserved                                                                 | Reserved 24            |

| WIFIRQ                                                                         | neserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reserved                                                                                                           | Reserved                                                                   | Z8036 Timer –                                                                 |                                                                                                                               | Reserved                                                                 | Heserved               |

|                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    | - Port B on the                                                            | 26036 Timer =                                                                 |                                                                                                                               |                                                                          | ·                      |

| <cnt2></cnt2>                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    |                                                                            |                                                                               |                                                                                                                               |                                                                          |                        |

| 31                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ·                                                                                                                  | Power Up Rese                                                              | t Condition: "1"                                                              |                                                                                                                               |                                                                          | 24                     |

| VBIMSK7                                                                        | VBIMSK6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VBIMSK5                                                                                                            | VBIMSK4                                                                    | VBIMSK3                                                                       | VBIMSK2                                                                                                                       | VBIMSK1                                                                  | VBISMSK                |

| <b>4</b>                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - which VMEb                                                                                                       | ous IRQ's this In                                                          | terrupt Handler                                                               | responds to                                                                                                                   |                                                                          | 1                      |

| .01.70                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    |                                                                            |                                                                               |                                                                                                                               |                                                                          |                        |

| <cnt3></cnt3>                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    | Daniel Ha Danie                                                            | t Condition: "0"                                                              |                                                                                                                               |                                                                          | 16                     |

| 23                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    |                                                                            |                                                                               |                                                                                                                               |                                                                          |                        |

| 23<br>Reserved                                                                 | ALLIEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T                                                                                                                  | <del></del>                                                                |                                                                               |                                                                                                                               | 11.0                                                                     | Reserved               |

| Reserved                                                                       | ALLIEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SYSFIEN                                                                                                            | Reserved                                                                   | IL2                                                                           | IL1                                                                                                                           | IL0                                                                      | Reserved               |

|                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | T                                                                                                                  | <del></del>                                                                | IL2                                                                           | IL1                                                                                                                           | IL0<br>est Level, Statu                                                  |                        |

|                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SYSFIEN                                                                                                            | <del></del>                                                                | IL2                                                                           | IL1                                                                                                                           |                                                                          |                        |

| Reserved                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SYSFIEN<br>pt Enables                                                                                              | <del></del>                                                                | IL2                                                                           | IL1<br>VME IRQ Requ                                                                                                           |                                                                          |                        |

| Reserved <                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SYSFIEN<br>pt Enables                                                                                              | Reserved                                                                   | IL2                                                                           | IL1<br>VME IRQ Requ                                                                                                           |                                                                          | s                      |

| Reserved  <                                                                    | — — Interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SYSFIEN<br>pt Enables                                                                                              | Reserved                                                                   | IL2<br>▼ \ It Condition; "1"                                                  | IL1<br>VME IRQ Requ                                                                                                           | est Level, Statu                                                         | s                      |

| Reserved <cnt4> 15 Reserved</cnt4>                                             | — — Interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SYSFIEN<br>pt Enables                                                                                              | Reserved                                                                   | IL2<br>▼ \ It Condition; "1"                                                  | IL1<br>VME IRQ Requ                                                                                                           | est Level, Statu                                                         | s                      |

| Reserved <cnt4> 15  Reserved  <cnt5></cnt5></cnt4>                             | — — Interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SYSFIEN pt Enables                                                                                                 | Power Up Rese                                                              | IL2  It Condition; "1"  Reserved                                              | IL1<br>VME IRQ Requ                                                                                                           | est Level, Statu                                                         | 08<br>Reserved         |

| Reserved <cnt4> 15  Reserved  <cnt5> 07</cnt5></cnt4>                          | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SYSFIEN pt Enables                                                                                                 | Power Up Rese                                                              | IL2  t Condition; "1"  Reserved  t Condition: "1"                             | IL1<br>VME IRQ Requ<br>Reserved                                                                                               | est Level, Statu<br>Reserved                                             | 08 Reserved            |

| Reserved <cnt4> 15  Reserved  <cnt5></cnt5></cnt4>                             | — — Interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SYSFIEN pt Enables                                                                                                 | Power Up Rese                                                              | IL2  It Condition; "1"  Reserved                                              | IL1<br>VME IRQ Requ                                                                                                           | est Level, Statu                                                         | 08<br>Reserved         |

| Reserved <cnt4> 15 Reserved  <cnt5> 07 PMEN</cnt5></cnt4>                      | Reserved  VXDIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SYSFIEN pt Enables Reserved                                                                                        | Power Up Rese 32/24*  Power Up Rese VXDEN                                  | IL2  t Condition; "1"  Reserved  t Condition: "1"  UXIRQ                      | IL1 /ME IRQ Requ Reserved                                                                                                     | Reserved 32/16*                                                          | 08 Reserved            |

| Reserved <cnt4> 15 Reserved  <cnt5> 07 PMEN</cnt5></cnt4>                      | Reserved  VXDIS <vmebus irc<="" td=""><td>SYSFIEN pt Enables  Reserved  VXRR*</td><td>Power Up Rese 32/24*  Power Up Rese VXDEN  Prese VXDEN</td><td>it Condition; "1" Reserved  t Condition: "1" UXIRQ VXDIS</td><td>IL1 /ME IRQ Requ  Reserved  32/24*  <vsb d<="" td=""><td>Reserved  32/16*</td><td>08 Reserved 00 BDFAIL</td></vsb></td></vmebus>                                                                                                                                                                                                                                                                                | SYSFIEN pt Enables  Reserved  VXRR*                                                                                | Power Up Rese 32/24*  Power Up Rese VXDEN  Prese VXDEN                     | it Condition; "1" Reserved  t Condition: "1" UXIRQ VXDIS                      | IL1 /ME IRQ Requ  Reserved  32/24* <vsb d<="" td=""><td>Reserved  32/16*</td><td>08 Reserved 00 BDFAIL</td></vsb>             | Reserved  32/16*                                                         | 08 Reserved 00 BDFAIL  |

| Reserved <cnt4> 15 Reserved  <cnt5> 07 PMEN</cnt5></cnt4>                      | Reserved  VXDIS <vmebus <multi-proces<="" irc="" td=""><td>SYSFIEN pt Enables Reserved</td><td>Power Up Rese 32/24*  Power Up Rese VXDEN  Prese VXDEN</td><td>IL2  t Condition; "1"  Reserved  t Condition: "1"  UXIRQ</td><td>IL1 /ME IRQ Requ  Reserved  32/24*  <vsb <vsb="" c="" f<="" td=""><td>Reserved 32/16*</td><td>08 Reserved 00 BDFAIL</td></vsb></td></vmebus>                                                                                                                                                                                                                                                           | SYSFIEN pt Enables Reserved                                                                                        | Power Up Rese 32/24*  Power Up Rese VXDEN  Prese VXDEN                     | IL2  t Condition; "1"  Reserved  t Condition: "1"  UXIRQ                      | IL1 /ME IRQ Requ  Reserved  32/24* <vsb <vsb="" c="" f<="" td=""><td>Reserved 32/16*</td><td>08 Reserved 00 BDFAIL</td></vsb> | Reserved 32/16*                                                          | 08 Reserved 00 BDFAIL  |

| Reserved <cnt4> 15 Reserved  <cnt5> 07 PMEN  /BV7-VBV0  MPIRQ*</cnt5></cnt4>   | Reserved  VXDIS <vmebus <multi-proces="" <vmebus="" interproces<="" irc="" td=""><td>SYSFIEN pt Enables – –  Reserved  VXRR*  2 Vector Numbusor Interrupt Re</td><td>Power Up Rese  32/24*  Power Up Rese  VXDEN  er Register&gt; equest&gt;</td><td>t Condition; "1" Reserved  t Condition: "1" UXIRQ  VXDIS VXRR*</td><td>IL1 /ME IRQ Requ  Reserved  32/24*   VSB E  VSB E  VSB D</td><td>Reserved  32/16*  Disable&gt; lead Only Mode</td><td>08 Reserved 00 BDFAIL</td></vmebus>                                                                                                                                                 | SYSFIEN pt Enables – –  Reserved  VXRR*  2 Vector Numbusor Interrupt Re                                            | Power Up Rese  32/24*  Power Up Rese  VXDEN  er Register> equest>          | t Condition; "1" Reserved  t Condition: "1" UXIRQ  VXDIS VXRR*                | IL1 /ME IRQ Requ  Reserved  32/24*   VSB E  VSB E  VSB D                                                                      | Reserved  32/16*  Disable> lead Only Mode                                | 08 Reserved 00 BDFAIL  |

| Reserved  CNT4> 15 Reserved  CNT5> 07 PMEN  /BV7-VBV0 /BIMSK7-1 /BISMSK kLLIEN | Reserved  VXDIS <vmebus <all="" <multi-proces="" <vmebus="" enal<="" inte="" irc="" irq="" td=""><td>SYSFIEN pt Enables – —  Reserved  VXRR*  VXRR*  Voctor Numbusor Interrupt Referrupt Masks &gt; errupt Status IR ble &gt;</td><td>Power Up Rese  32/24*  Power Up Rese  VXDEN  er Register&gt; equest&gt;</td><td>IL2  It Condition; "1"  Reserved  It Condition: "1"  UXIRQ  VXDIS VXRR* VXDEN</td><td>IL1 /ME IRQ Requ  Reserved  32/24*   VSB D  VSB D  VSB IF  VSB IF  VSB IF</td><td>Reserved  32/16*  bisable&gt; lead Only Modelecode Enable&gt;</td><td>08 Reserved  00 BDFAIL</td></vmebus>                              | SYSFIEN pt Enables – —  Reserved  VXRR*  VXRR*  Voctor Numbusor Interrupt Referrupt Masks > errupt Status IR ble > | Power Up Rese  32/24*  Power Up Rese  VXDEN  er Register> equest>          | IL2  It Condition; "1"  Reserved  It Condition: "1"  UXIRQ  VXDIS VXRR* VXDEN | IL1 /ME IRQ Requ  Reserved  32/24*   VSB D  VSB D  VSB IF  VSB IF  VSB IF                                                     | Reserved  32/16*  bisable> lead Only Modelecode Enable>                  | 08 Reserved  00 BDFAIL |

| Reserved  CNT4> 15 Reserved  CNT5> 07 PMEN  /BV7-VBV0 /PIRQ* /BIMSK7-1 /BISMSK | Reserved  VXDIS <vmebus <multi-proces="" <sysfail="" <vmebus="" <vmirq="" ent="" int="" ir<="" irc="" td=""><td>SYSFIEN pt Enables – —  Reserved  VXRR*  VXRR*  Voctor Numbusor Interrupt Referrupt Masks &gt; errupt Status IR ble &gt;</td><td>Power Up Rese  32/24*  Power Up Rese  VXDEN  er Register&gt; equest&gt;  Q Mask&gt;</td><td>t Condition; "1"  Reserved  t Condition: "1"  UXIRQ  VXDIS VXRR* VXDEN VXIRQ</td><td>IL1 /ME IRQ Requ  Reserved  32/24*   VSB E  VSB I  VME IRQ Requ</td><td>Reserved  32/16*  bisable&gt; lead Only Modelecode Enable&gt; atterrupt Reques</td><td>08 Reserved  00 BDFAIL</td></vmebus> | SYSFIEN pt Enables – —  Reserved  VXRR*  VXRR*  Voctor Numbusor Interrupt Referrupt Masks > errupt Status IR ble > | Power Up Rese  32/24*  Power Up Rese  VXDEN  er Register> equest>  Q Mask> | t Condition; "1"  Reserved  t Condition: "1"  UXIRQ  VXDIS VXRR* VXDEN VXIRQ  | IL1 /ME IRQ Requ  Reserved  32/24*   VSB E  VSB I  VME IRQ Requ                                                               | Reserved  32/16*  bisable> lead Only Modelecode Enable> atterrupt Reques | 08 Reserved  00 BDFAIL |

### VMEbus INTERFACE

The VMEbus interface provides for VMEbus arbitration; for buffering of data, address, and control signals; for word data manipulation to accommodate MC68020 and VMEbus data handling differences and for Interrupt handling.

The VMEbus arbiter arbitrates up to four levels of bus mastership on a priority basis, utilizes a Pal chip, and incorporates the Release on Request (ROR) option described in the VMEbus specification (HB212).

### **INTERRUPT HANDLER**

The MVME130 allows interrupts to the onboard CPU from up to 20 sources. The interrupt handler preprocesses interrupt sources into three groups of seven interrupts corresponding to the seven possible MC68020 interrupt levels. The groups are labeled Group 1, Group 2, and Group 3. The interrupt service priority is determined by the interrupt level and the group number. Interrupts with different interrupt levels are processed according to the standard interrupt processing discipline. Interrupts within an interrupt level are processed according to the group number.

Group 1 is reserved for VMEbus interrupts. The interrupt handler processes Group 2 and 3 interrupts differently from Group 1 interrupts. If the interrupt being acknowledged is a Group 2 or 3 interrupt, the interrupt handler fetches the appropriate exception vector number from PROM and sends it to the CPU via the local bus. If the interrupt being acknowledged is a Group 1 interrupt, the exception vector number is fetched from the VMEbus where it was placed by the interrupting device.

The Interrupt assignments are described in Table 4.

#### VMEbus INTERRUPTER

The VMEbus interrupter can generate any level of VMEbus interrupt under software control. When the VMEbus interrupt is acknowledged, the Interrupter places the appropriate vector from a hardware register on the VMEbus.

TABLE 4 — Interrupt Handler Priority Assignments

| 1     | Priority Within a | Particular IRQ Level Determines | he Service Order |  |

|-------|-------------------|---------------------------------|------------------|--|

| IRQ   | (Highest)         | (Middle)                        | (Lowest)         |  |

| Level | Group 3           | Group 2                         | Group 1          |  |

| 7     | ABORT*            | ACFAIL Interrupt<br>ACFIRQ*     | IRQ7* (VMEbus)   |  |

| 6     | TMRIRQ*           | SYSFIRQ*                        | IRQ6* (VMEbus)   |  |

| 5     | SIOIRQ*           | VBISIRQ*                        | IRQ5* (VMEbus)   |  |

| 4     | Unassigned        | VXIRQ*                          | IRQ4* (VMEbus)   |  |

| 3     | Unassigned        | Unassigned                      | IRQ3* (VMEbus)   |  |

| 2     | Unassigned        | Unassigned                      | IRQ2* (VMEbus)   |  |

| 1     | N/A               | Unassigned                      | IRQ1* (VMEbus)   |  |

Within a Group x, interrupt priority decreases from top to bottom in the table. Within a particular IRQ level, interrupt priority decreases from left to right.

**Group 3 Interrupts**

ABORT\* TMRIRQ\* <Timer IRQ>

SIOIRQ\* <Dual Channel Serial Port IRQ>

<Abort Pushbutton IRQ>

ACFIRQ\* SYSFIRQ\*

**Group 2 Interrupts**

< VMEbus AC Power Fail Interrupt>

<VMEbus System Fail Interrupt> VBISIRQ\* <VMEbus IRQ Request Acknowledge Interrupt>

VXIRQ\*

<VSB Interrupt>

**Group 1 Interrupts**

IRQ7-1\*

<VMEbus Interrupts>

## **Mechanical and Environmental Specifications**

| Characteristics                            | Specifications                                                                                                 |  |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| Power Requirements<br>MVME130<br>MVME131   | +5 Vdc, 5 A (typ), 6 A (max)<br>+5 Vdc, 6 A (typ), 7 A (max)<br>+12 Vdc, 250 mA (max)<br>-12 Vdc, 250 mA (max) |  |  |

| Clock Signal                               | 12.5 MHz clock frequency                                                                                       |  |  |

| Addressing Total system size ROM/EPROM/RAM | 4 Gigabytes (32-bit addressing) Four 28-pin sockets for 16/32/64Kb devices using +5 Vdc only.                  |  |  |

| Operating Temperature                      | 0° to 50°C                                                                                                     |  |  |

| Storage Temperature                        | -40° to 85°C                                                                                                   |  |  |

| Relative Humidity                          | 5% to 95% (non-condensing)                                                                                     |  |  |

| Physical Dimensions<br>Height<br>Width     | 6.3 in (16.0 cm)<br>9.19 in (23.34 cm)                                                                         |  |  |

| Thickness (MVME130)<br>(MVME131)           | .71 in (1.8 cm)<br>1.51 in (3.84 cm)                                                                           |  |  |

# **Ordering Information**

| Part Number | Description                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------------------|

| MVME130     | VMEmodule 32-bit Monoboard Microcomputer with MC68020 CPU. Includes User's Manual.                                |

| MVME131     | VMEmodule 32-bit Monoboard Microcomputer with MC68020 CPU and Hardware Memory Management. Includes User's Manual. |

| MVME130/D   | VMEmodule 32-bit Monoboard Microcomputer User's Manual.                                                           |

### **Related Product**

| Part Number | Description                                                                                             |  |  |

|-------------|---------------------------------------------------------------------------------------------------------|--|--|

| MVME130bug  | MVME130bug Debugging Package for VMEmodule 32-bit Monoboard<br>Microcomputer. Includes User's Manual.   |  |  |

| MVME204     | VMEmodule 1024Kb Dynamic RAM Module with VSB. Includes User's Manual.                                   |  |  |

| MVME214     | VMEmodule Static RAM/ROM Module with VSB. Includes User's Manual.                                       |  |  |

| MVME707     | MVME130 RS-232C Distribution Board with Dual RS-232C Serial I/O Cable Assembly. Includes User's Manual. |  |  |

# MVME130bug

# Advance Information

# 130bug Debug/ Diagnostic Monitor

### 130bug RESIDENT PACKAGE

- Debug and Diagnostic Monitor in EPROM for the MC68020-based MVME130 and MVME131 Monoboard Microcomputers

- Full Speed Execution of System and User Programs in a MVME130/MVME131 Monoboard Microcomputer System

- More than 20 Debug and Program Development Commands

- 18 Diagnostic and Hardware Debug Commands

- Provides Access to all I/O, Control and Memory Facilities of a MVME130/MVME131-based System Plus the Full 4 Gigabyte Direct Address Range of the VMEbus

- Support for the MC68881 Floating Point Coprocessor (FPC)

- Supports the MVME320 Disk Controller

- Virtual Terminal Capability for Up/Down Load to/from any Host via Motorola S-Records

- One Line Assembler/Disassembler for Convenient Program Monitoring/Modification

- 21 I/O, Data Conversion and Timing Routines Callable from User-written Programs

- Complete MVME130/MVME131 Hardware Diagnostics with Loop Continuous and Loop-on-error Modes

- Self Test verifies System Integrity on Power Up

### 130bug SOURCE MODULE PACKAGE

- 130bug Source Modules Supplied on VME/10 Microcomputer System or EXORmacs Development System Diskette

- Source Modules Allow Modification of 130bug as Required

## 130bug DEBUG/DIAGNOSTIC MONITOR

The Debug/Diagnostic Monitor, 130bug, is supplied as two separate products:

- For Resident Use

- The object code is supplied in two 32Kb EPROMs which plug into sockets provided on the MVME130 and MVME131 Monoboard Microcomputers

- For Customization

- The source code is supplied on VME/10 Microcomputer System-compatible 5-1/4" diskettes or on EXORmacs Development System-compatible 8" diskettes

Any MVME130 or MVME131 system having a VMEbus backplane such as that provided by the chassis for one of Motorola's new "Open System" Microcomputer Families, the 9-slot MVME943 VMEmodule Chassis and the 20-slot MVME944 VMEmodule Chassis can use 130bug.

The 130bug firmware monitor is a versatile, effective tool. It offers many powerful commands for application program development and modification and for MVME130 or MVME131 system hardware diagnosis and debugging in a VMEbus or standalone environment. It permits, under complete operator control, full-speed execution of system and application programs including code utilizing the MC68881 Floating Point Coprocessor.

Memory space required by 130bug includes 8Kb of RAM storage for exception vectors and stack/work space and 8Kb for user space. The monitor normally reserves the 16Kb of static RAM on board MVME130 and MVME131 but can optionally search system memory space for off-board RAM. To operate the 130bug/monoboard combination in the standalone mode requires that the onboard memory be used.

With a user-supplied module translating the TTL levels of the two MVME130 or MVME131 serial ports to RS-232-C to create standard DB-25 interfaces (one such board is the Motorola MVME707 RS-232 Serial Port Distribution Module), a standard RS-232-C, asynchronous, ASCII terminal can be connected to one serial port so that the 130bug/monoboard system can be operated in a standalone mode. This mode allows full use of the 130bug program development and hardware diagnostic capabilities and is also commonly used for the final debugging of the application system. Figure 1 depicts operating in the standalone mode.

Figure 1. Standalone Operation

The translation board also allows a direct or dial-up RS-232-C link from a host computer to be interfaced to the second serial port so that programs in Motorola S-Record format may be up/down loaded. For this purpose, 130bug provides commands used to place the monoboard in the transparent mode and to configure the

# MVME130bug

ports for the desired communication protocol. For example, both host and target must be set to the same baud rate. Viewed from the host, while in the transparent mode, the monoboard appears to be an asynchronous ASCII terminal (virtual terminal). Figures 2 and 3 show operation in the transparent mode for communication with a host computer.

Support provided within 130bug for the MVME320 Disk Controller includes a command which can be used to load into a system any VERSAdos-bootable operating system.

Figure 2. Transparent Mode — Direct Serial Connection With Host Computer

### **DEBUG/DIAGNOSTIC FACILITIES**

The 130bug monitor is a command driven program which has facilities for accepting a command entered at the system console and for operating in the debug or in the diagnostic mode. To indicate the current operating mode, 130bug displays an individual prompt: 130Bug> or 130Diag>. Debugging activities are supported by a large set of versatile commands many of which can be used for diagnosis or self test of the MVME130 and MVME131 monoboards.

On power-up and reset, 130bug follows certain default condition procedures according to the value of a switch-settable flag on the monoboard. These include the allocation of onboard or of system memory.

#### PROGRAM DEBUGGING

Debugging support includes commands for examining and modifying registers and memory, commands which allow blocks of memory to be filled, moved or searched for the occurrence of specified data, breakpoint commands which allow program segments to be run, trace commands for examining the execution of instructions or small program portions, commands for beginning execution at a specified address, commands which facilitate host/target communication, printer attach/detach commands and utility commands which provide the capabilities of switching to the other operating mode, formatting the monoboard's serial ports, displaying or modifying the offset registers, converting the number base of data and displaying the name and a brief description of the entire command set. Table 1 lists all debugging commands.

Several commands are included for performing disk

I/O using the MVME320 Disk Controller Module. The parameters of several commonly-used disk configurations are already known to the monitor and a command, I/O Teach, is included which allows a user to "teach" the monitor the specifics of another configuration. Particular sectors can be read from or written to using the I/O Physical To Disk command. Another command, Boot Operating System And Halt, is useful for debugging bootable code.

In a typical debug session after loading the program under development, appropriate commands from the debug set are invoked so that operation of a particular program portion can be checked and, if necessary, the code modified. Often, using the powerful Register Display/Modify, Memory Display/Modify and Block Memory Move commands, trial conditions for a program portion are established and the code executed. Results can be determined by examining the processor registers or memory values. A user may also examine the registers of the MC68881 FPC and display or change the contents of memory in any one of the various floating point formats.

An alternative method is to set a breakpoint in place of an appropriate instruction to halt execution and obtain automatic display of processor register values. A more detailed examination of program validity is offered by the Trace commands which allow execution of one instruction at a time, with accompanying processor register display following each execution. If required, program code is easily modified with the aid of the one line assembly/ disassembly function provided by the Memory Modify command. The Data Conversion command which converts values from decimal to hexadecimal or hexadecimal to decimal is also a useful modification tool.

Debugging of modular code is done using the commands for displaying and modifying the offset registers which 130bug provides to make this task easier.

When the program is fully debugged, it is saved to disk or the Dump S-Records command is used to format and upload the code to the host for storage.

Figure 3. Transparent Mode — Dial-Up Serial Link With Host Computer

## MVME130bug

Table 1. 130bug Debugging Commands

|                                                | • • • •                                                                                   |

|------------------------------------------------|-------------------------------------------------------------------------------------------|

| MEMORY COMMANDS                                | SYNTAX                                                                                    |

| Memory Display                                 | MD[S] <addr>[:<count>   <addr>][;[B   W   L   D]]</addr></count></addr>                   |

| Memory Modify/Disassembly/Assembly             | MM <addr> [;[ [N] [B   W   L   A] DI ]</addr>                                             |

| Memory Set                                     | MS <addr> {Hexadecimal number} {'string'}</addr>                                          |

| REGISTER COMMANDS*                             | SYNTAX                                                                                    |

| Register Display                               | RD<br>RM (DEC)                                                                            |

| Register Modify                                | RM <reg></reg>                                                                            |

| BLOCK OF MEMORY COMMANDS                       | SYNTAX                                                                                    |

| Block of Memory Fill                           | BF <range><del><data>[;B   W   L]</data></del></range>                                    |

| Block of Memory Move                           | BM <range><del><addr>[;B   W   L]</addr></del></range>                                    |

| Block of Memory Search                         | BS <range><del><text>   <data>[<mask>] [;B   W   L /N]</mask></data></text></del></range> |

| DISK SUPPORT COMMANDS                          | SYNTAX                                                                                    |

| Boot Operating System                          | во                                                                                        |

| Boot Operating System and Halt                 | BH                                                                                        |

| I/O Physical To Disk                           | IOP                                                                                       |

| I/O "Teach"                                    | IOT                                                                                       |

| HOST COMMUNICATION COMMANDS                    | SYNTAX                                                                                    |

| Dump S-Records                                 | DU[n] <range><del>[<text>] [<addr>] [;B   W   L]</addr></text></del></range>              |

| Load S-Records                                 | LO $[]$ [;[-C/X]= <text>]</text>                                                          |

| Transparent Mode<br>Verify S-Records           | TM <escape> VE [<addr>] [;[-C/X]=<text>]</text></addr></escape>                           |

| GO COMMANDS                                    | SYNTAX                                                                                    |

|                                                |                                                                                           |

| Go Direct (Ignore Breakpoints)                 | GD [ <addr>]</addr>                                                                       |

| Go Execute User Program Go To Next Instruction | GO [ <addr>]<br/>GN</addr>                                                                |

| Go To Temporary Breakpoint                     | GT <addr></addr>                                                                          |

| TRACE COMMANDS                                 | SYNTAX                                                                                    |

| Trace                                          | T [ <count>]</count>                                                                      |

| Trace on Change of Control Flow                | TC [ <count>]</count>                                                                     |

| Trace To Temporary Breakpoint                  | TT <addr></addr>                                                                          |

| BREAKPOINT COMMANDS                            | SYNTAX                                                                                    |

| Breakpoint Insert                              | BR { <addr>[:<count>]}</count></addr>                                                     |

| Breakpoint Delete                              | NOBR { <addr>}</addr>                                                                     |

| PRINTER COMMANDS                               | SYNTAX                                                                                    |

| Printer Attach                                 | PA                                                                                        |

| Printer Detach                                 | NOPA                                                                                      |

| MISCELLANEOUS UTILITY COMMANDS                 | SYNTAX                                                                                    |

| Data Conversion                                | DC <expression></expression>                                                              |

| Help                                           | HE [ <command/> ]                                                                         |

| Offset Registers Display/Modify                | OF [ Rn[;A] ]                                                                             |

| Port Format                                    | PF[n]                                                                                     |

| Switch Directories                             | SD                                                                                        |

### HARDWARE DIAGNOSTICS

Test and diagnostic capabilities offered by 130bug are provided by commands which include:

- Set-up Utilities for Selecting an Operating Mode such as Stop-on-error

- Tests of MVME130/131 Hardware Including Tests of the Onboard Memory, MC68020 Cache, Counter/Timer, Serial I/O, VMEbus/VSB, Tests of the Memory Management Board and Final Assembly Tests

- Commands for Hardware Debugging which Provide a Self-test Sequence and Continuous Write and Read Loops

When the 130bug diagnostic mode is entered, the monitor displays the prompt: "130Diag>" indicating that any of the commands in the diagnostic directory may be used. The 130bug Diagnostic Commands are listed in Table 2.

### **CALLABLE 130bug ROUTINES**

A TRAP #15 handler is included in 130bug which allows calls from user-written programs to input, output and other useful routines within 130bug. Such a system call is made by including in the source program a TRAP #15 instruction line followed by a DC.W instruction line containing the code of the desired function. The callable 130bug functions and their codes are listed in Table 3.

**Table 2. 130bug Diagnostic Commands**

| Туре                              | Command<br>Mnemonic                          | Description                                                                                                                                         |

|-----------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Diagnostic<br>Set-Up<br>Utilities | LE<br>SE<br>LC<br>NV<br>DP<br>ZP<br>DE<br>ZE | Loop-on-Error Mode Stop-on-Error Mode Loop Continuous Mode Non-Verbose Mode Display Pass Count Clear Pass Count Display Errors Clear Error Counters |

| Hardware<br>Debugging<br>Tools    | ST<br>WL<br>RL                               | Run Self-Test Sequence<br>Continuous Write Loop<br>Continuous Read Loop                                                                             |