In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/97359-15

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

Your definitive source for quality pre-owned equipment.

**Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

MVME143S

MPU VMEmodule<sup>TM</sup>

User's Manual

(MVME143S/D1)

## APPENDIX A EIA-232-D INTERCONNECTIONS

The EIA-232-D standard is the most widely used interface between terminals and computers or modems, and yet it is not fully understood. This is because all the lines are not clearly defined, and many users do not see the need to conform for their applications. A system should easily connect to any other. Many times designers think only of their own equipment, but the state-of-the-art is computer-to-computer or computer-to-modem operation.

The EIA-232-D standard was originally developed by the Bell System to connect terminals via modems. Therefore, several handshaking lines were included. In many applications these are not needed, but since they permit diagnosis of problems, they are included in many applications.

The standard EIA-232-D interconnections are listed in Table A-1. To interpret this information correctly it is necessary to know that EIA-232-D is intended to connect a terminal to a modem. When computers are connected to computers without modems, one of them must be configured as a terminal and the other as a modem. Because computers are normally configured to work with terminals, they are said to be configured as a modem. Also, the signal levels must be between +3 and +15 volts for a high level, and between -3 and -15 volts for a low level. Any attempt to connect units in parallel may result in out of range voltages and is not allowed by the EIA-232-D specification.

Table A-1. EIA-232-D Interconnections

| Pin<br>Number | Signal<br>Mnemonic | Signal Name and Description                                                                               |

|---------------|--------------------|-----------------------------------------------------------------------------------------------------------|

| 1             |                    | Not used.                                                                                                 |

| 2             | TxD                | TRANSMIT DATA — data to be transmitted is furnished on this line to the modem from the terminal.          |

| 3             | RxD                | RECEIVE DATA — data which is demodulated from the receive line is presented to the terminal by the modem. |

Table A-1. EIA-232-D Interconnections (cont'd)

| Pin<br>Number | Signal<br>Mnemonic | Signal Name and Description                                                                                                                                                                                                            |

|---------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4             | RTS                | REQUEST TO SEND — RTS is supplied by the terminal to the modem when required to transmit a message. With RTS off, the modem carrier remains off. When RTS is turned on, the modem immediately turns on the carrier.                    |

| 5             | CTS                | CLEAR TO SEND — CTS is a function supplied to the terminal by the modem which indicates that it is permissible to begin transmission of a message. When using a modem, CTS follows the off-to-on transition of RTS after a time delay. |

| 6             | DSR                | DATA SET READY — data set ready is a function supplied by the modem to the terminal to indicate that the modem is ready to transmit data.                                                                                              |

| 7             | SIG-GND            | SIGNAL GROUND — common return line for all signals at the modem interface.                                                                                                                                                             |

| 8             | DCD                | DATA CARRIER DETECT — sent by the modem to the terminal to indicate that a valid carrier is being received.                                                                                                                            |

| 09-14         |                    | Not used.                                                                                                                                                                                                                              |

| 15            | TxC                | TRANSMIT CLOCK — this line clocks output data to the modem from the terminal.                                                                                                                                                          |

| 16            |                    | Not used.                                                                                                                                                                                                                              |

| 17            | RxC                | RECEIVE CLOCK — this line clocks input data from a terminal to a modem.                                                                                                                                                                |

| 18,19         |                    | Not used.                                                                                                                                                                                                                              |

| 20            | DTR                | DATA TERMINAL READY — a signal from the terminal to the modem indicating that the terminal is ready to send or receive data.                                                                                                           |

| Pin<br>Number | Signal<br>Mnemonic | Signal Name and Description                                                                                                                                                                                                |  |  |  |  |

|---------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 21            |                    | Not used.                                                                                                                                                                                                                  |  |  |  |  |

| 22            | RI                 | RING INDICATOR — RI is sent by the modem to the terminal. This line indicates to the terminal that an incoming call is present. The terminal causes the modem to answer the phone by carrying DTR true while RI is active. |  |  |  |  |

| 23            |                    | Not used.                                                                                                                                                                                                                  |  |  |  |  |

| 24            | TxC                | TRANSMIT CLOCK — same as TxC on pin 15.                                                                                                                                                                                    |  |  |  |  |

| 25            | BSY                | BUSY — a positive EIA signal applied to this pin<br>causes the modem to go off-hook and make the<br>associated phone busy.                                                                                                 |  |  |  |  |

Table A-1. EIA-232-D Interconnections (cont'd)

**NOTES:** 1. High level = +3 to +15 volts. Low level = -3 to -15 volts.

EIA-232-D is intended to connect a terminal to a modem. When computers are connected to computers without modems, one of the computers must be configured as a modem and the other as a terminal.

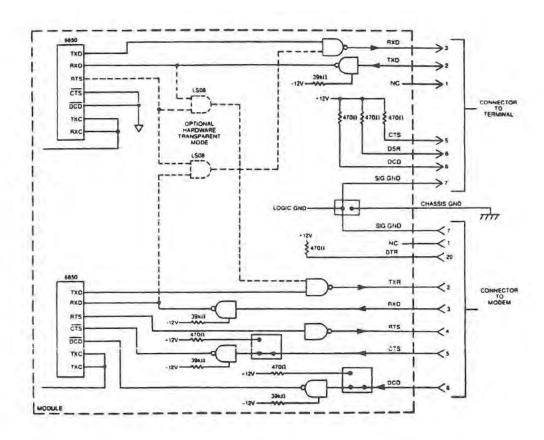

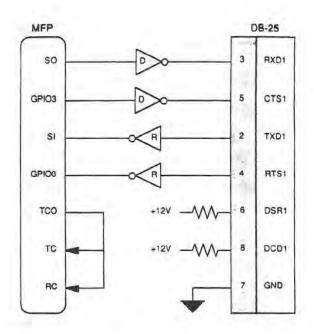

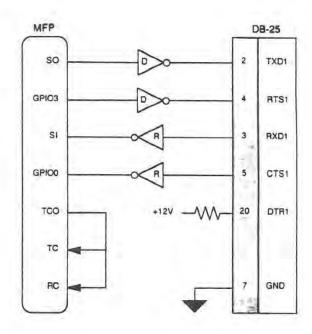

There are several levels of conformance that are appropriate for typical EIA-232-D interconnections. The bare minimum requirement is the two data lines and a ground. The full version of EIA-232-D requires 12 lines and accommodates automatic dialing, automatic answering, and synchronous transmission. A middle-of-the-road approach is illustrated in Figure A-1.

One set of handshaking signals frequently implemented are RTS and CTS. CTS is used in many systems to inhibit transmission until the signal is high. In the modem application, RTS is turned around and returned as CTS after 150 microseconds. RTS is programmable in some systems to work with the older type 202 modem (half duplex). CTS is used in some systems to provide flow control to avoid buffer overflow. This is not possible if modems are used. It is usually necessary to make CTS high by connecting it to RTS or to some source of +12 volts such as the resistors shown in Figure A-2. It is also frequently jumpered to an MC1488 gate which has its inputs grounded (the gate is provided for this purpose). Another signal used in many systems is DCD. The original purpose of this signal was to tell the system that the carrier tone from the distant modem

was being received. This signal is frequently used by the software to display a message like CARRIER NOT PRESENT to help the user to diagnose failure to communicate. Obviously, if the system is designed properly to use this signal, and it is not connected to a modem, the signal must be provided by a pullup resistor or gate as described before (see Figure A-1). Many modems expect a DTR high signal and issue a DSR. These signals are used by software to help prompt the operator about possible causes of trouble. The DTR signal is used sometimes to disconnect the phone circuit in preparation for another automatic call. It is necessary to provide these signals in order to talk to all possible modems (see Figure A-2). Figure A-1 is a good minimum configuration that almost always works. If the CTS and DCD signals are not received from the modem, the jumpers can be moved to artificially provide the needed signal. A way that an EIA-232-D connector can be wired to enable a computer to connect to a basic terminal with only three wires is shown in Figure A-2. This is because most terminals have a DTR signal that is ON, and that can be used to pullup the CTS, DCD, and DSR signals. Two of these connectors wired back-to-back can be used. It must be realized that all the handshaking has been bypassed and possible diagnostic messages do not occur. Also the Tx and Rx lines may have to be crossed since Tx from a terminal is outgoing but the Tx line on a modem is an incoming signal.

Another subject that needs to be considered is the use of ground pins. There are two pins labeled GND. Pin 7 is the SIGNAL GROUND and must be connected to the distant device to complete the circuit. Pin 1 is the CHASSIS GROUND, but it must be used with care. The chassis is connected to the power ground through the green wire in the power cord and must be connected to the chassis to be in compliance with the electrical code. The problem is that when units are connected to different electrical outlets, there may be several volts difference in ground potential. If pin 1 of the devices are interconnected with a cable, several amperes of current could result. This not only may be dangerous for the small wires in a typical cable, but could result in electrical noise that could cause errors. That is the reason that Figure A-1 shows no connection for pin 1. Normally, pin 7 should only be connected to the CHASSIS GROUND at one point, and if several terminals are used with one computer, the logical place for that point is at the computer. The terminals should not have a connection between the logic ground return and the chassis.

Figure A-1. Middle-of-the-Road EIA-232-D Configuration

Figure A-2. Minimum EIA-232-D Connection

#### В

## APPENDIX B Z8530 SCC SERIAL PORT B SETUP EXAMPLE

This example sets up port B (the EIA-232-D port) of the Z8530 SCC as follows:

- 9600 baud, asynchronous only

- Interrupt on received character, transmitter buffer ready, and external status change with common interrupt vector.

#### SETUP:

| Move #\$30 into SCCB_WR                              | (\$FFFA0000)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Clear receiver error status.                                                     |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Move #\$10 into SCCB_WR                              | (\$FFFA0000)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Clear external status interrupts.                                                |

| Move #\$09 into SCCB_WR0 Move #\$40 into SCCB_WR0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Select register 9.<br>Reset channel B.                                           |

| Move #\$0A into SCCB_WR0 Move #\$00 into SCCB_WR0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Select register 10.<br>Make sure NRZ format is set.                              |

| Move #\$0E into SCCB_WRI<br>Move #\$82 into SCCB_WRI |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Select register 14.<br>Disable baud rate generator.                              |

| Move #\$04 into SCCB_WRI                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Select register 4. Divide by 16, no parity, one stop bit.                        |

| Move #\$03 into SCCB_WRI<br>Move #\$C1 into SCCB_WRI | and the second of the second o | Select register 3.<br>Receiver: eight bits, receiver<br>enabled.                 |

| Move #\$05 into SCCB_WRI<br>Move #\$EA into SCCB_WRI |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Select register 5. Transmitter: eight bits, transmitter enabled, RTS on, DTR on. |

| Move #\$0C into SCCB_WR0 Move #\$02 into SCCB_WR0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Select register 12.<br>Lower byte of time constant.                              |

| Move #\$00 into SCCB_WRI<br>Move #\$00 into SCCB_WRI |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Select register 13.<br>Higher byte of time constant.                             |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

В

| Move #\$0E into SCCB_WR0 (\$FFFA0000)  Move #\$81 into SCCB_WR0 (\$FFFA0000)  Move #\$01 into SCCB_WR0 (\$FFFA0000)  Move #\$11 into SCCB_WR0 (\$FFFA0000)  Move #\$0F into SCCB_WR0 (\$FFFA0000)  Move #\$80 into SCCB_WR0 (\$FFFA0000)  Move #\$80 into SCCB_WR0 (\$FFFA0000)  Move #\$02 into SCCB_WR0 (\$FFFA0000)  Move #\$80 into SCCB_WR0 (\$FFFA0000)  Move #\$80 into SCCB_WR0 (\$FFFA0000)  Move #\$90 into SCCB_WR0 (\$FFFA0000)  Move #\$09 into SCCB_WR0 (\$FFFA0000)  Master interrupt enable. Status information NOT to be included in the vector passed to the MPU. | Move #\$0B into SCCB_WR0<br>Move #\$56 into SCCB_WR0 | Select register 11.  RX clock = BR Generator output,  TX clock = BR Generator output,  TRXC = output = BR Generator output. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Move #\$11 into SCCB_WR0 (\$FFFA0000)  Interrupt on all Received Character or Special Condition. Also enable external interrupts.  Move #\$0F into SCCB_WR0 (\$FFFA0000)  Move #\$80 into SCCB_WR0 (\$FFFA0000)  Move #\$02 into SCCB_WR0 (\$FFFA0000)  Move #\$80 into SCCB_WR0 (\$FFFA0000)  Move #\$80 into SCCB_WR0 (\$FFFA0000)  Move #\$09 into SCCB_WR0 (\$FFFA0000)  Move #\$09 into SCCB_WR0 (\$FFFA0000)  Move #\$08 into SCCB_WR0 (\$FFFA0000)  Move #\$08 into SCCB_WR0 (\$FFFA0000)  Master interrupt enable. Status information NOT to be included                                                                                                                                                                                                                                                                                                                                            |                                                      | BR Generator clock source =                                                                                                 |

| Move #\$80 into SCCB_WR0 (\$FFFA0000)  Move #\$02 into SCCB_WR0 (\$FFFA0000)  Move #\$80 into SCCB_WR0 (\$FFFA0000)  Move #\$09 into SCCB_WR0 (\$FFFA0000)  Move #\$08 into SCCB_WR0 (\$FFFA0000)  Move #\$08 into SCCB_WR0 (\$FFFA0000)  Move #\$08 into SCCB_WR0 (\$FFFA0000)  Master interrupt enable. Status information NOT to be included                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      | Interrupt on all Received Character or Special Condition.                                                                   |

| Move #\$80 into SCCB_WR0 (\$FFFA0000)  Interrupt vector number. (\$80 => vector offset = \$200.)  Move #\$09 into SCCB_WR0 (\$FFFA0000)  Move #\$08 into SCCB_WR0 (\$FFFA0000)  Master interrupt enable. Status information NOT to be included                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |                                                                                                                             |

| Move #\$08 into SCCB_WR0 (\$FFFA0000) Master interrupt enable. Status information NOT to be included                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      | Interrupt vector number.                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      | Master interrupt enable. Status information NOT to be included                                                              |

To minimize overhead in the interrupt handling routine, status information may be selected to be included in the vector(s). The vector, then, points directly at the appropriate handling routine according to the interrupt cause. If the Vector-Status-Include (VSI) is set and the content in the vector register is \$80, then the vector passed to the MPU is:

```

$80 (vector offset = $200) for Channel B Transmitter Buffer Empty or $82 (vector offset = $208) for Channel B External Status Change or $84 (vector offset = $210) for Channel B Received Character Available or $86 (vector offset = $218) for Channel B Special Received Character.

```

For this example, place the address of the common interrupt handler at offset \$200 in the vector table.

#### **Z8530 SCC SERIAL PORT B SETUP EXAMPLE**

#### INTERRUPT HANDLER:

Move #\$03 into SCCB\_WR0 (\$FFFA0000)

Read from SCCB\_RR0 (\$FFFA0000) Read the Read Register 3 for

interrupt cause.

Select register 3.

Investigate the interrupt pending bits to determine the cause. Branch to the appropriate handling routine.

#### TRANSMIT A CHARACTER:

If Transmitter Buffer Empty interrupt is desired, it must be enabled before outputting a character or else the interrupt will not occur.

Move #\$01 into SCCB\_WR0 (\$FFFA0000) Select register 1.

Move #\$13 into SCCB\_WR0 (\$FFFA0000) Enable transmitter interrupt.

Move output character

into SCCB\_TDR (\$FFFA0001) Transmit a character.

#### TRANSMITTER BUFFER EMPTY INTERRUPT HANDLER:

Move #\$01 into SCCB\_WR0 (\$FFFA0000) Select register 1.

Move #\$11 into SCCB\_WR0 (\$FFFA0000) Disable transmitter interrupt.

Move #\$38 into SCCB\_WR0 (\$FFFA0000) Reset highest Interrupt-Under-

Service (IUS).

Are there more characters to output?

If Yes, go do TRANSMIT A CHARACTER.

If No, return from exception.

#### RECEIVED CHARACTER INTERRUPT HANDLER:

Move #\$01 into SCCB\_WR0 (\$FFFA0000) Select register 1.

Read from SCCB\_RR0 (\$FFFA0000) Read the Read Register 1 to check

for status.

Check for framing error, receiver overrun, and parity errors.

Read from SCCB\_RDR (\$FFFA0001) Read received character.

Move #\$38 into SCCB\_WR0 (\$FFFA0000) Reset highest IUS.

#### EXTERNAL STATUS CHANGE INTERRUPT HANDLER:

Break — either start of break or end of break.

CTS — a transition has occurred on the CTS input pin.

DCD — a transition has occurred on the DCD input pin.

Move #\$00 into SCCB\_WR0 (\$FFFA0000) Select register 0.

Read from SCCB\_RR0 (\$FFFA0000) Read the Read Register 0 for

status.

Move #\$10 into SCCB\_WR0 (\$FFFA0000) Reset external status interrupt.

Take actions as necessary.

If break bit is low, which is the end of a break, a null character is still in the receive buffer. It should be read and discarded.

Read data from SCCB\_RDR (\$FFFA0001) Read null character.

Return from exception.

#### C

# APPENDIX C MC68901 MFP TIMER A SETUP EXAMPLE

The following example sets up the MC68901 MFP timer A (software tick timer) to interrupt the MPU periodically every 10 milliseconds.

#### SETUP:

| Clear bit #5 of MFP_IERA | (\$FFF80007) | Disable timer A interrupts.                                  |

|--------------------------|--------------|--------------------------------------------------------------|

| Move #\$10 into MFP_TACR | (\$FFF80019) | Reset and stop timer A.                                      |

| Move #\$7B into MFP_TADR | (\$FFF8001F) | Load count down value. (Refer to Table 1 in this Appendix.)  |

| Move #\$06 into MFP_TACR | (\$FFF80019) | Delay mode, prescaler = 100.                                 |

| Move #\$68 into MFP_VR   | (\$FFF80017) | Set starting vector at \$60.<br>Set software interrupt mode. |

#### NOTE

The vector passed to the MPU for the timer A interrupt is  $6D = vector offset = 4 \times 6D = 184$ .

| Move #\$DF into MFP_IPRA (\$FFF8000B) | Clear timer A interrupt pending bit (bit #5 of IPRA).    |

|---------------------------------------|----------------------------------------------------------|

| Move #\$DF into MFP_ISRA (\$FFF8000F) | Clear timer A interrupt-in-service bit (bit #5 of ISRA). |

| Set bit #5 of MFP_IMRA (\$FFF80013)   | Unmask timer A interrupts.                               |

| Set bit #5 of MFP_IERA (\$FFF80007)   | Enable timer A interrupts.                               |

#### TIMER A INTERRUPT HANDLER:

Read MFP\_ISRA (\$FFF8000F) Read interrupt-in-service register A.

Investigate MFP\_ISRA to determine if it was actually from timer A.

Take actions as necessary.

Move #\$DF into MFP\_ISRA (\$FFF8000F) Clear timer A interrupt-in-service bit (bit #5 of ISRA).

Return from exception.

#### COUNTDOWN CALCULATION:

The countdown value used during setup may be calculated using the following equation:

$CD = (TI \times TO) / PS$

where:

CD = countdown value to be loaded into timer data register.

TI = timer input frequency in Hz = 1,230,769 Hz.

TO = tick timer interrupts interval in seconds.

PS = prescaler value (4, 10, 16, 50, 64, 100, or 200).

Table D-1 contains the values for PS and CD for some selected interrupts intervals.

Table C-1. Prescaler and Countdown Values

| T    | 0      |     |      | CD      |

|------|--------|-----|------|---------|

| MSEC | SEC    | PS  | HEX  | DECIMAL |

| 1.0  | 0.0010 | 10  | \$7B | 123     |

| 5.0  | 0.0050 | 50  | \$7B | 123     |

| 10.0 | 0.0100 | 100 | \$7B | 123     |

| 20.0 | 0.0200 | 100 | \$F6 | 246     |

| 40.0 | 0.0400 | 200 | \$F6 | 246     |

| 41.6 | 0.0416 | 200 | \$00 | 256     |

|      | 1      |     |      |         |

C

# INDEX

#### INDEX

When using this index, keep in mind that a page number indicates only where referenced material begins; it may extend to the following page or pages.

#### Δ

Abort 4-35

ABORT Switch S1 3-1, 4-17, 4-35

Accessing the VMEbus 4-8

address option 4-7

arbitration timer 4-11

arbitration

Prioritized mode 2-4

Round-Robin-Select mode 2-4

assert 1-7

asterisk (\*) 1-7

#### B

Bank 1 address base 2-16

bank 2 address base 2-16

battery backup real-time clock 4-3

Battery Backup RTC 4-4

battery backup SRAM 4-3, 4-4

Baud Rate Generator (BRG) 4-28

BRG (see Baud Rate Generator) 4-28

bus error exceptions

local bus timeout 3-10

parity error 3-10

VMEbus bus error 3-10

Bus Error Processing 3-10

#### C

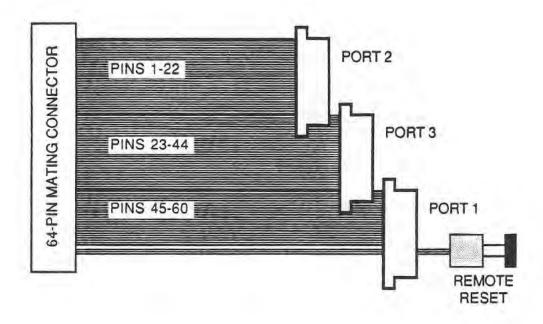

Cabling Connections to P2 2-24

Cache Data 2-3 Instruction 2-3 Connector J14 Interconnect Signals Connector J18 Interconnect Signals control bit VMEA24\* 4-7 Control bit VMED16\* 4-7 Control/Status Register 1 (CSR1) 4-16 Control/Status Register 1 GPIO Pins 4-16 Control/Status Register 2 (CSR2) 4-19 Control/Status Register 2 Port A Pins 4-19 Control/Status Register 3 (CSR3) 4-20 Control/Status Register 3 Port B Pins 4-20 Control/Status Register 4 (CSR4) 4-21 Control/Status Register 4 Port C Pins 4-21 Controls and Indicators 3-1 Cooling Requirements 1-4 Coprocessor Interface Map 3-5 CSR1 (see Control/Status Register 1) CSR2 (see Control/Status Register 2) CSR3 (see Control/Status Register 3) CSR4 (see Control/Status Register 4) 4-21

#### D

Data Bus Structure 4-9 data transfers 4-7 debug monitor 1-6 Debug Port 4-15 default local bus master 4-5 device address lines 2-11 Device Type 2-11 DRAM 3-9, 4-4 DRAM Cycle Times 4-35 DRAM Refresh 4-5 DRAM sequencer 4-5, 4-36

#### E

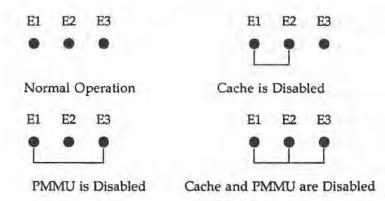

E1, E2, E3 2-3 EEPROM Considerations 4-33 EIA-232-D Interconnections A-1 EPROM Address Map Select Header (J13) 2-16

#### F

FAIL 3-1

fairness mode 2-5

FCC Compliance 1-5

Features 1-1

Floating Point Coprocessor (FPC) 4-2

FPC (see Floating Point Coprocessor)

4-2

front panel debug port 4-15

Front Panel LED Indicators 3-2

Functional Description 4-1

FUSE 3-1

#### G

General Description 1-5 General Purpose I/O (GPIO) 4-16 Global Bus timeout 4-11 global bus timer 4-11 Global Timeout Select Header (J5) 2-7 GPIO (see General Purpose I/O) 4-16

#### H

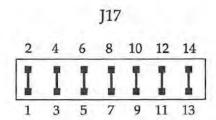

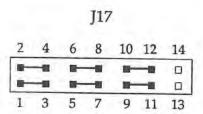

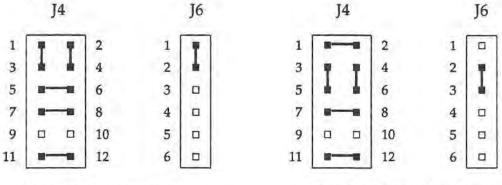

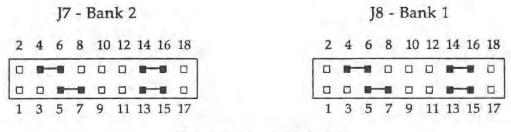

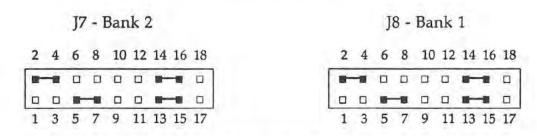

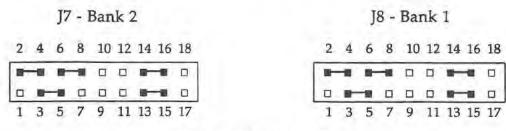

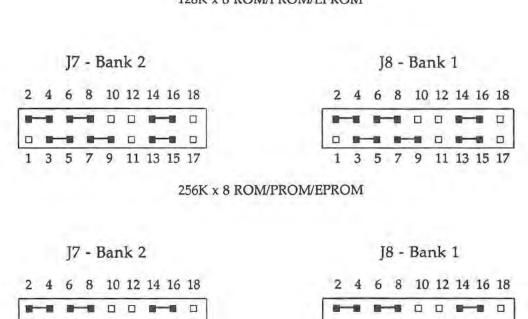

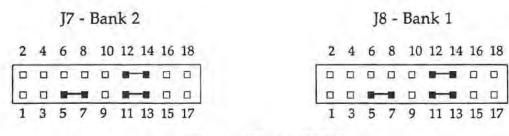

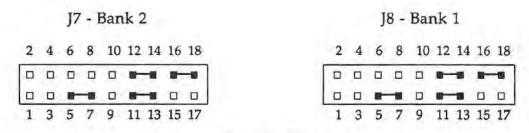

Hardware Preparation 2-1 Header J1 2-4 Header J10 2-14 Header J11 2-15 Header J12 2-15 Header J13 2-16 Header J15 2-17 Header J16 2-17 Header J17 2-17 Header J19 2-20 Header J2 2-4 header J20 2-20 Header J3 2-5 Header J5 2-7 Header J9 2-14 Headers J4 and J6 2-6 Headers J7 and J8 2-7

#### ١

IACK\* (see Interrupt Acknowledge)

4-11

IACK\* Daisy-Chain Driver 4-11

Indicators

FAIL 3-1

FUSE 3-1

RUN 3-1

SCON 3-1

STATUS 3-1

Installation Instructions 2-23

Interrupt Acknowledge (IACK\*) 4-11

interrupt acknowledge cycle 4-33

Interrupt Acknowledge Map 3-6

Interrupt Handler 4-33

IN-2

Interrupt Sources and Vectors 4-34

L

Local Bus timeout 4-35

local bus timeout error (LTOBERR)

3-10

Local MPU to DRAM Accesses 4-5

Local Multiport Arbiter 4-5

Local Processor CPU Space Memory

Map 3-5

local timeout bus error 4-17

Local Timeout Select Header (J11)

2-15

logical (virtual) addresses 2-3

LTOBERR (see local bus timeout error)

3-10

#### M

MAI (see Multiple Address Interlock) Mailbox Interrupt 4-12 Manual Terminology 1-7 Map Decoder 3-3, 4-6 master interface 4-6 mastership of the VMEbus 4-8 MC68030 Microprocessor (MPU) 4-1 MC68230 Parallel Interface/Timer (PI/T) 4-17 MC68230 PI/T Registers 4-23 MC68882 Coprocessor Interface Register Map 3-6 MC68882 Floating Point Coprocessor (FPC) 4-2 MC68901 MFP Timer A Setup Example C-1 MC68901 Multi-Functional Peripheral (MFP) 4-13 MFP (see Multi-Functional Peripheral 4-13

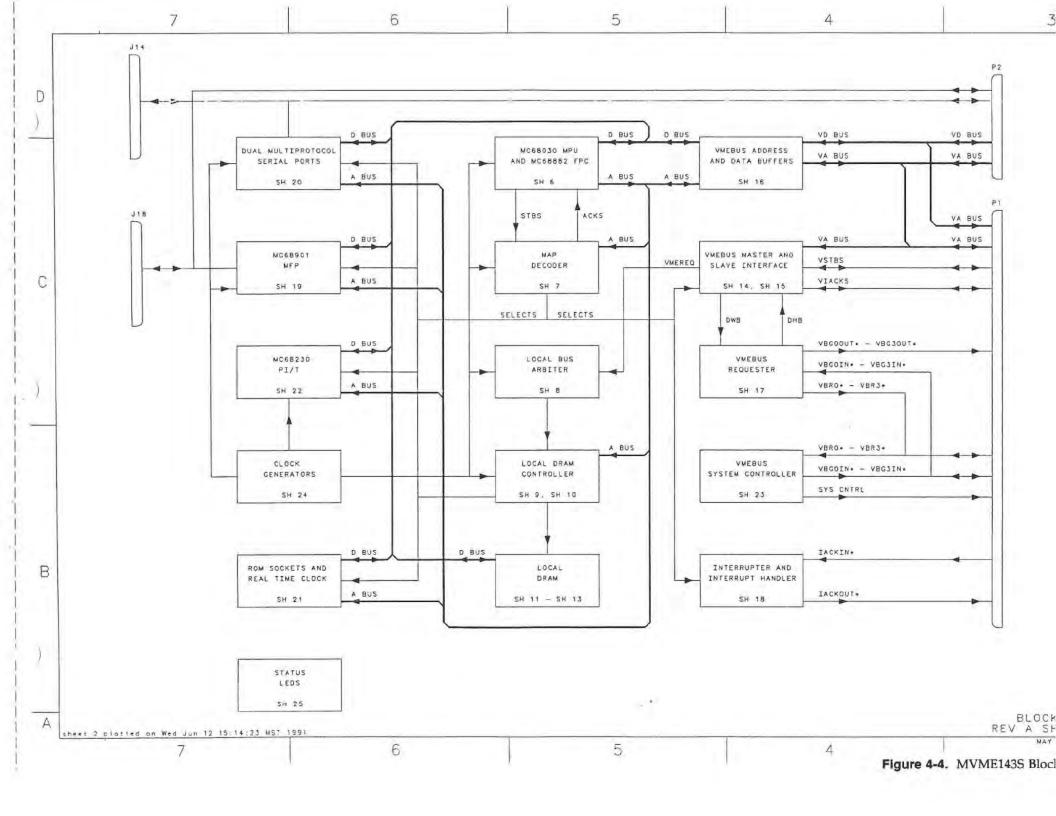

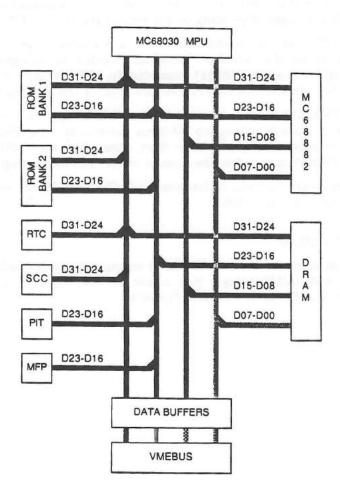

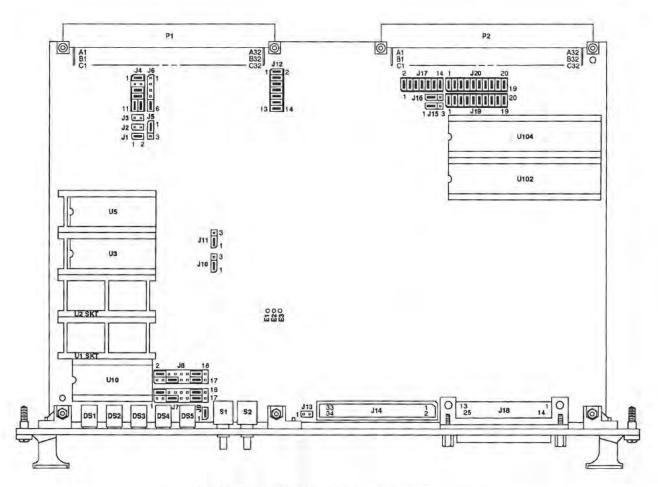

MFP Register Map 4-14 MFP Timer A Setup Example C-1 MFP Timers 4-15 MK48T02 Battery Backup Real-Time Clock with SRAM 4-3 Model Designations 1-1 Multi-Functional Peripheral (MFP) Multiple Address Interlock (MAI) 3-11 multiple address RMW 4-8 Multiple address RMW cycles 4-36 multiport arbiter 4-5, 4-6 MVME143S Address Spaces 3-3 MVME143S Block Diagram 4-39 MVME143S Data Bus Structure 4-10 MVME143S Header Locations 2-2 MVME143S Program and Data Space Memory Map 3-3

N

negate 1-7

0

Onboard Dynamic RAM 4-4

Onchip Cache and PMMU Control

Select Terminals (E1, E2, E3) 2-3

OPERATING INSTRUCTIONS 3-1

P

PACR (see Port A Control Register)

4-23

Paged Memory Management Unit

(PMMU) 2-3

Parallel Interface/Timer (PI/T) 4-17

parallel ports 1-6, 3-9

PARERR (see parity error) 3-10

parity checking 4-4, 4-5, 4-36

parity error 4-17 parity error (PARERR) 3-10 PBCR (see Port B Control Register) 4-24 Performance 4-35 PGCR (see Port General Control Register) 4-23 PI/T (see Parallel Interface/Timer) 4-17 PI/T port A 4-19 PI/T port B 4-20 PI/T Register Map 4-18 PIVR (see Port Interrupt Vector Register) 4-24 PMMU (see Paged Memory Management Unit) 2-3 Port 1 Baud Rates Available 4-15 Port 1 Configured as DCE 2-18 Port 1 Configured as DTE 2-19 Port 2/3 Baud Rates Available with  $BRG\ Clock = PCLK = 4.00\ MHz$ 4-29 Port 2/3 Baud Rates Available with BRG Clock = RTXC 4-29Port A Control Register (PACR) 4-23 Port B Control Register (PBCR) 4-24 Port General Control Register (PGCR) 4-23 Port Interrupt Vector Register (PIVR) 4-24 Port Status Register (PSR) 4-25 Ports 2/3 Configured as DCE 2-21 Ports 2/3 Configured as DTE 2-22 power up Reset 4-34 Prescaler and Countdown Values C-3 PRI (see Prioritized (PRI) mode) 2-4 Prioritized (PRI) mode 2-4 Program and Data Space Memory Map 3-3 programmable baud rate generator 4 - 28programmable vector 4-17 Programmed Values for PI/T Registers

4-25 PSR (see Port Status Register) 4-25

#### R

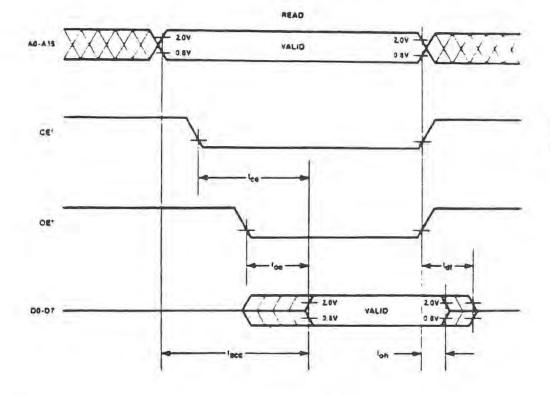

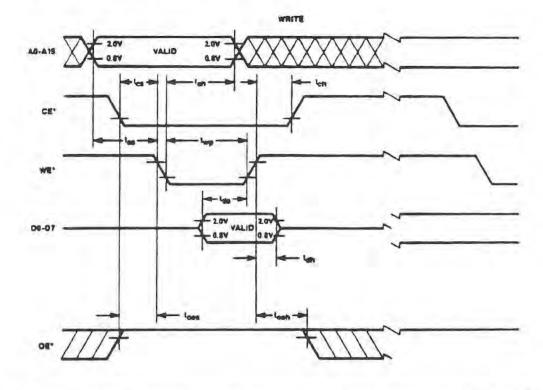

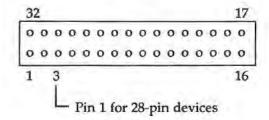

read accesses 4-8 Read Timings Required by the MVME143S 4-31 Read-Modify-Write (RMW) 3-11 read-modify-write cycle 4-8 Real-Time Clock (RTC) 4-4 refresh timer 4-5 Related Documentation 1-6 Release-On-Request (ROR) 4-8 Remote Reset 4-35 Reset Instruction 4-35 RESET Switch 3-34, 4-34 RESET Switch Enable/Disable Select Header (J9) 2-14 Reset power up Reset 4-34 Remote Reset 4-34 Reset Instruction 4-34 RESET Switch 4-34 VMEbus SYSRESET 4-34 Watchdog Reset 4-34 RMW (see Read-Modify-Write) 3-11 RMW cycle 4-8 RMW instructions 3-11 ROM/EEPROM Size Select Headers (J7, J8) 2-7 ROM/PROM/EPROM/EEPROM Cycle Times 4-36

ROM/PROM/EPROM/EEPROM

Sockets 4-30

ROR (see Release-On-Request) 4-8

Round-Robin-Select (RRS) mode 2-4

RRS (see Round-Robin-Select (RRS)

mode) 2-4

RTC (see Real-Time Clock) 4-4

RTC oscillator 4-4

RTC registers 4-4 RUN 3-1

#### S

SCC (see Serial Communications Controller) 4-27 SCC Registers Map 4-28 SCC RTXCA Source Select Header (J15) 2-17 SCC RTXCB Source Select Header (J16) 2-17 SCC Serial Port B Setup Example B-1 SCON 3-1 sequence for interrupting 4-12 Serial Clock Select Header (J10) 2-14 Serial Communications Controller (SCC) 4-27 Serial Port 1 Configuration Select Header (J17) 2-17 Serial Port 1 Front Panel Debug Port 4-15 Serial Port 2 (J19) and Port 3 (J20) Configuration Select Headers 2-20 Serial Ports Configurations 4-30 Shared DRAM Address Map on VMEbus 3-7 sockets 4-30 Software abort 4-17 Software Initialization of the MVME143S 3-8 Specifications 1-2 SRAM access 4-4 STATUS 3-1 SYSCLK (see System Clock) 4-11 SYSCLK Driver 4-11 SYSRESET (see System Reset) 4-12 SYSRESET\* 4-34 System Clock (SYSCLK) 4-11 System Considerations 3-9 system controller 4-11, 4-35

System Controller Enable/Disable Select Header (J1) 2-4 System Reset (SYSRESET\*) 4-12 SYSTEM V/68 3-8

#### T

timeout generator 4-35 Timer A 4-15 Timer B 4-15 Timer C 4-15 Timer D 4-15

#### U

Unpacking Instructions 2-1 Use of RMW Instructions 3-11

#### V

VERSAdos 3-8 VMEBERR (see VMEbus bus error) 3-10 VMEbus access error 4-17 VMEbus Access Time to Onboard DRAM 4-36 VMEbus Address Size 4-7 VMEbus Arbiter 4-11 VMEbus Arbiter Mode Select Header (J2) 2-4 VMEbus Arbitration Time 4-35 VMEbus bus error (VMEBERR) 3-10 VMEbus Cycle Times 4-36 VMEbus Data Width 4-7 VMEbus Interrupt Handler Select Header (J12) 2-15 VMEbus interrupter programmable level 4-12 programmable vector 4-12 VMEbus map decoder 4-6

VMEbus Master Interface 4-6 VMEbus mastership 4-8 VMEbus Memory Map When VMEA24\* = 0 4-7VMEbus Memory Map When VMEA24\* = 1 4-7VMEbus Requester 4-8 VMEbus Requester Level Select Headers (J4, J6) 2-6 VMEbus Requester Mode Select Header (J3) 2-5 VMEbus specification 1-7 VMEbus SYSRESET\* 4-34 VMEbus System Controller 4-11 VMEbus to Onboard DRAM Accesses 4-6 VMEexec 3-8

#### W

Watchdog Reset 4-34 watchdog timeout 4-16 write accesses 4-8 Write Timings Guaranteed by MVME143S 4-33

#### Z

Z8530 SCC Serial Port B Setup Example B-1 Z8530 Serial Communications Controller (SCC) 4-27

## Notes

## Notes

| VID3 | VID2 | VID1 | VID0 | Status ID |

|------|------|------|------|-----------|

| 0    | 0    | 0    | 0    | \$FO      |

| 0    | 0    | 0    | 1    | \$F1      |

| 0    | 0    | 1    | 0    | \$F2      |

| 0    | 0    | 1    | 1    | \$F3      |

| 0    | 1    | 0    | 0    | \$F4      |

| 0    | 1    | 0    | 1    | \$F5      |

| 0    | 1    | 1    | 0    | \$F6      |

| 0    | 1    | 1    | 1    | \$F7      |

| 1    | 0    | 0    | 0    | \$F8      |

| 1    | 0    | 0    | 1    | \$F9      |

| 1    | 0    | 1    | 0    | \$FA      |

| 1    | 0    | 1    | 1    | \$FB      |

| 1    | 1    | 0    | 0    | \$FC      |

| 1    | 1    | 0    | 1    | \$FD      |

| 1    | 1    | 1    | 0    | \$FE      |

| 1    | 1    | 1    | 1    | \$FF      |

#### Control/Status Register 4: Port C Pins

The MVME143S utilizes the PI/T port C pins to form Control/Status Register 4 (CSR4). Five port C pins are used as control outputs and three are used for interrupt request and acknowledge functions. PC6, PC5, and PC3 are assigned as port interrupt acknowledge pin, port interrupt request pin, and timer interrupt request pin, respectively. After a reset, the PI/T makes all parallel pins inputs. Therefore, software must initialize the control bits and make them outputs after each reset. All port C pins default to high when they are not programmed as outputs. The assignment of PC7-PC0 is as follows:

| Address  | PC7   | PC6       | PC5     | PC4   | PC3    | PC2    | PC1    | PC0     |

|----------|-------|-----------|---------|-------|--------|--------|--------|---------|

| FFF90019 | LTOEN | PIACK*    | PIRQ*   | GTOEN | TEIRQ* | WWPAR* | PAREN* | VPAREN* |

|          | R/W   | 11 = - 11 | 11 - 11 | R/W   | R/W    |        | R/W    | R/W     |

4

- LTOEN When LTOEN is low, the local timeout is disabled and the MVME143S hangs if a non-mapped location is accessed or if its requester is prevented from obtaining the VMEbus mastership. When LTOEN is high, the local bus timer is enabled. The timeout period is selectable through header J11.

- PIACK\* PI/T port interrupt acknowledge. This pin is asserted low by the MVME143S interrupt handler in response to a PI/T port interrupt request (PIRQ\* = 0). When the MPU performs an interrupt acknowledge cycle to a PIRQ\*, the PI/T places the programmed vector with the source encoded to the data bus.

- PIRQ\* PI/T port interrupt request. The PI/T may be programmed to assert PIRQ\* low upon detecting the assertion of the ABORT switch or an asserted edge on parity error, VMEbus error, or local timeout. Each one of these four sources may be enabled/disabled individually in the PI/T.

- GTOEN When GTOEN is high, the MVME143S asserts VBERR\* to the VMEbus if VDS0\* and/or VDS1\* is low for more than timeout period if the MVME143S is the system controller. Also, the arbiter rearbitrates if VBBSY\* remains high after a grant has been issued for more than the timeout period. When GTOEN is low, global timeout and arbitration timeout are disabled. The global timeout period is selectable through header J5.

- TEIRQ\* PI/T timer interrupt request. This pin can be cleared by writing a 1 to the ZDS bit in Timer Status Register (TSR). Only auto-vectored interrupt is supported for the PI/T timer. After a reset, software must initialize the PI/T for the desired timer operation.

- WWPAR\* This control bit may be used to force wrong parity to be written to the onboard DRAM for testing purposes. Special care must be taken in using this bit because both the MPU and the VMEbus may write wrong parity to the DRAM when WWPAR\* is low.

- PAREN\* When this bit is low, parity checking is enabled and the MVME143S asserts BERR\* to the MPU if a parity error is detected on a DRAM read cycle. DRAM access time is increased by 1 clock for all read accesses by the MPU when PAREN\* is low.

- VPAREN\* When this bit is low, parity checking is enabled and the MVME143S asserts VBERR\* to the VMEbus if a parity error is detected on a read cycle. DRAM access time is increased by 1 clock for all read accesses by the VMEbus when VPAREN\* is low.

#### MC68230 PI/T Registers

The MVME143S requires that the PI/T is programmed for Mode 00 and Submode 1X for proper operation. Some of the PI/T registers are described in the following paragraphs. Refer to the MC68230 Data Book for further details.

#### Port General Control Register (PGCR)

PGCR is used to select mode 00 and to define ABORT, PARERR, VMEBERR, and LTOBERR signals as high true status inputs. Only bits 5 and 4 are user-programmable. Bit 5 must be set if either software abort or PARERR interrupt is to be enabled. Bit 4 must be set to allow interrupt functions for VMEBERR and/or LTOBERR.

| Address  | BITT  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BITO  |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| FFF90001 | MODE1 | MODE0 | H34EN | H12EN | H4SNS | H3SNS | H2SNS | HISNS |

| VALUE    | 0     | 0     | 0/1   | 0/1   | 1     | 1     | 1     | 1     |

#### Port A Control Register (PACR)

PACR is used to select submode 1X and to define VMEBERR and LTOBERR as edge-sensitive status inputs. Only bits 2 and 1 are user-programmable to enable/disable VMEBERR interrupt and LTOBERR interrupt, respectively.

| Address  | BIT7  | BIT6  | BIT5 | BIT4 | ВІТЗ | BIT2   | BIT1   | BITO |

|----------|-------|-------|------|------|------|--------|--------|------|

| FFF9000D | ASUB1 | ASUB0 | H2C2 | H2C1 | H2C0 | VBEIEN | LTOIEN | HISC |

| VALUE    | 1     | 0     | 0    | 0    | 0    | 0/1    | 0/1    | 0    |

VBEIEN When VBEIEN is set, an occurrence of VMEbus error generates a level 7 interrupt via the PI/T. VMEbus error interrupt is disabled if either VBEIEN or H12EN is cleared.

LTOIEN When LTOIEN is set, an occurrence of local bus timeout generates a level 7 interrupt via the PI/T. Local bus timeout interrupt is disabled if either LTOIEN or H12EN is cleared.

#### Port B Control Register (PBCR)

PBCR is used to select submode 1X and to define PARERR and ABORT as edgesensitive status inputs. Only bits 2 and 1 are user-programmable to enable/disable PARERR interrupt and ABORT interrupt, respectively.

| Address  | ВІТТ  | BIT6  | BIT5 | ВІТ4 | ВІТ3 | BIT2   | BIT1   | віто |

|----------|-------|-------|------|------|------|--------|--------|------|

| FFF9000F | BSUB1 | BSUB0 | H4C2 | H4C1 | H4C0 | PARIEN | ABRTEN | H3SC |

| VALUE    | 1     | 0     | 0    | 0    | 0    | 0/1    | 0/1    | 0    |

PARIEN When PARIEN is set, an occurrence of MPU-to-DRAM parity error generates a level 7 interrupt via the PI/T. Parity error interrupt is disabled if either PARIEN or H34EN is cleared.

ABRTEN When ABRTEN is set, a level 7 interrupt via the PI/T is generated upon an activation of the MVME143S front panel ABORT switch. Software abort interrupt is disabled if either ABRTEN or H34EN is cleared.

#### Port Interrupt Vector Register (PIVR)

| Address  | BIT7  | BIT6  | BIT5  | BIT4  | ВІТЗ  | BIT2  | BIT1  | BIT0  |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| FFF9000B | PIVR7 | PIVR6 | PIVR5 | PIVR4 | PIVR3 | PIVR2 | PIVR1 | PIVR0 |

PIVR contains the upper order six bits of the four port interrupt vectors. The contents of this register may be read in two ways: by an ordinary read cycle, or by a port interrupt acknowledge bus cycle. When reading this register with an ordinary read cycle, the lower two bits are always forced to zero. During a port interrupt acknowledge cycle, bits 1 and 0 encode the interrupt sources as follows:

| SOURCE         | PIVR1 | PIVR0 |

|----------------|-------|-------|

| PARERR         | 1     | 1     |

| ABORT          | 1     | 0     |

| <b>VMEBERR</b> | 0     | 1     |

| LTOBERR        | 0     | 0     |

#### Port Status Register (PSR)

| Address  | впт             | BITTE          | ВП5              | BIT4             | впз              | BITZ            | BIT1              | впо               |

|----------|-----------------|----------------|------------------|------------------|------------------|-----------------|-------------------|-------------------|

| FFF9001B | PARERR<br>Level | ABORT<br>Level | VMEBERR<br>Level | LTOBERR<br>Level | PARERR<br>Status | ABORT<br>Status | VMEBERR<br>Status | LTOBERR<br>Status |

|          | R               | R              | R                | R                | R/C              | R/C             | R/C               | R/C               |

The PSR contains information about software abort and bus error signals activity. Bits 7, 5, and 4 are always read as zero; while bit 6 reflects the instantaneous level of the ABORT signal. Bits 3-0 contain the latched status of PARERR, ABORT, VMEBERR, and LTOBERR, respectively. These bits are set by the assertion edge of the input signals. When set, they can only be cleared by a board reset or by writing a 1 to the set bits.

#### Programmed Values for PI/T Registers

The values of the PI/T registers after reset and the recommended programmed values for proper, intended operation are shown in Table 4-5.

Table 4-5. Programmed Values for PI/T Registers

| Register<br>Address | Register<br>Name | Reset<br>Value | Programmed<br>Value | Notes                                                                                                                                      |

|---------------------|------------------|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| \$FFF90001          | PGCR             | \$00           | \$3F                | Mode 00 and H4-H1 = high true.                                                                                                             |

| \$FFF90003          | PSRR             | \$00           | \$1F                | PC4 = PC4, PC5 = PIRQ*, PC6 = PIACK*.                                                                                                      |

| \$FFF90005          | PADDR            | \$00           | \$FF                | PA7-PA0 = outputs.                                                                                                                         |

| \$FFF90007          | PBDDR            | \$00           | \$7F                | PB6-PB0 = outputs, PB7 = input.                                                                                                            |

| \$FFF90009          | PCDDR            | \$00           | \$BF                | PC7 and PC5-PC0 = outputs,<br>PC6 = input.                                                                                                 |

| \$FFF9000B          | PIVR             | \$0F           | User<br>defined     | Example: if PIVR = \$80 then<br>the vectors for PARERR,<br>ABORT, VMEBERR, and LTOBERR<br>are \$83, \$82, \$81, and \$80,<br>respectively. |

Table 4-5. Programmed Values for PI/T Registers (cont'd)

| Register<br>Address | Register<br>Name | Reset<br>Value | Programmed<br>Value | Notes                                                                                                                                                                                  |  |  |

|---------------------|------------------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| \$FFF9000D          | PACR             | \$00           | \$80                | Sub mode 1X, H2S = latched VMEBERR, H1S = latched LTOBERR, VMEBERR interrupt is disabled LTOBERR interrupt is disabled.                                                                |  |  |

| \$FFF9000F          | PBCR             | \$00           | \$82                | Sub mode 1X, H4S = latched PARERR, H3S = latched ABORT, PARERR interrupt is disabled. ABORT interrupt is enabled.                                                                      |  |  |

| \$FFF90011          | PADR             | No<br>change   | \$01                | VMED16* = 1, MBXIEN* = 0,<br>VMEA24* = 0, SLAVEN* = 0,<br>SLVA3-SLVA0 = %0000.                                                                                                         |  |  |

| \$FFF90013          | PBDR             | No<br>change   | \$00                | Interrupter is disabled, interrupter status ID = \$F0.                                                                                                                                 |  |  |

| \$FFF90015          | PAAR             | N/A            | N/A                 | Reflects current states of pins.                                                                                                                                                       |  |  |

| \$FFF90017          | PBAR             | N/A            | N/A                 | Reflects current states of pins.                                                                                                                                                       |  |  |

| \$FFF90019          | PCDR             | Unknown        | \$FF                | LTOEN = 1, GTOEN = 1,<br>WWPAR* = 1, PAREN* = 1,<br>VPAREN* = 1.                                                                                                                       |  |  |

| \$FFF9001B          | PSR              | Unknown        | N/A                 | Write a 1 to the bit to clear it.                                                                                                                                                      |  |  |

| \$FFF90021          | TCR              | \$00           | \$F0                | PC3/TOUT = TIRQ* and timer interrupt is enabled for autovectored interrupts, counter rolls over on zero detect then continues counting, PC2/TIN = PC2 = WWPAR*, and timer is disabled. |  |  |

Table 4-5. Programmed Values for PI/T Registers (cont'd)

| Register<br>Address | Register<br>Name | Reset<br>Value | Programmed<br>Value | Notes                                      |

|---------------------|------------------|----------------|---------------------|--------------------------------------------|

| \$FFF90023          | TIVR             | \$0F           |                     | Not used.                                  |

| \$FFF90027          | CPRH             | No<br>change   | User<br>defined     |                                            |

| \$FFF90029          | CPRM             | No<br>change   | User<br>defined     |                                            |

| \$FFF9002B          | CPRL             | No<br>change   | User<br>defined     |                                            |

| \$FFF9002F          | CNTRH            | No<br>change   | Read only           | Stop counter before reading this register. |

| \$FFF90031          | CNTRM            | No<br>change   | Read only           | Stop counter before reading this register. |

| \$FFF90033          | CNTRL            | No<br>change   | Read only           | Stop counter before reading this register. |

| \$FFF90035          | TSR              | \$00           | N/A                 | Write a 1 to clear ZDS bit, if set.        |

#### Z8530 Serial Communications Controller (SCC)

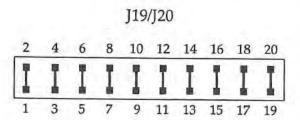

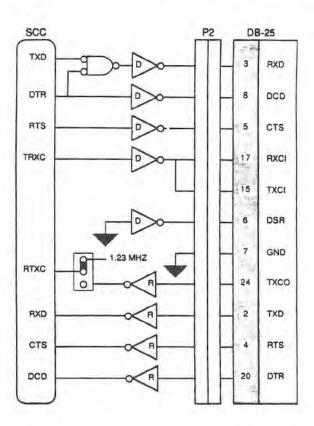

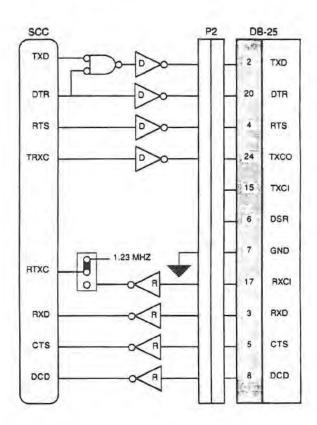

The MVME143S uses the Z8530 Serial Communications Controller (SCC) to implement its two multiprotocol EIA-232-D serial ports (port A = serial port 3 and port B = serial port 2). Headers J20 and J19 allows port 3 and port 2 to be individually configured as DTE or DCE. Refer to Chapter 2 for jumpers configurations. The SCC occupies 128Kb in the MVME143S memory map and is located at a physical base address of \$FFFA0000 and interrupts the MPU on level 5. The address map for the SCC is shown in Table 4-6.

Table 4-6. SCC Registers Map

| Physical Address | Register Name | Register Description             |

|------------------|---------------|----------------------------------|

| \$FFFA0000       | SCCB-RR0      | Port B read register 0           |

|                  | SCCB-WR0      | Port B write register 0          |

| \$FFFA0001       | SCCB-RDR      | Port B received data register    |

|                  | SCCB-TDR      | Port B transmitted data register |

| \$FFFA0002       | SCCA-RR0      | Port A read register 0           |

|                  | SCCA-WR0      | Port A write register 0          |

| \$FFFA0003       | SCCA-RDR      | Port A received data register    |

|                  | SCCA-TDR      | Port A transmitted data register |

In the SCC, register addressing is direct for the data registers only. In all other cases (with the exception of SCCx-WR0 and SCCx-RR0), accessing the internal SCC read and write registers requires a sequence of two operations. The first operation is a write to SCCx-WR0 with the four least significant bits that point to the selected register. If the second operation is a write, then the selected write register is accessed. On the other hand, if the second operation is a read, then the selected read register is selected. The pointer bits are automatically cleared after the second read or write operation so that SCCx-WR0 (or SCCx-RR0) is addressed again on the next access. Refer to the Z8530 Serial Communications Controller Data Sheet for details on programming and using the SCC.

Because of its internal structure, there are several means of obtaining the baud rate clocks for each of the two serial channels. Each channel within the SCC has a programmable baud rate generator. The Baud Rate Generator (BRG) input can be from the RTXC input or from PCLK. The hardware on the MVME143S allows the RTXC pin for each channel to be connected to an external clock source or to the onboard 1.230769 MHz or 2.451538 MHz clock (selectable through header J10). Also, the SCC DPLL input can be either the BRG output or the RTXC pin. The DPLL operates at 32 times the data rate for NRZI and at 16 times the data rate for FM. The values in the SCC time constant register that are required to create some common baud rates are shown in Table 4-7.

Table 4-7. Port 2/3 Baud Rates Available with BRG Clock = RTXC

| 2.461538 MHz<br>Baud Rate | 1.230769 MHz<br>Baud Rate | Clock<br>Mode | Time Constant<br>Register Value | Percent<br>Error |

|---------------------------|---------------------------|---------------|---------------------------------|------------------|

| 38400                     | 19200                     | x16           | 0                               | 0.16             |

| 19200                     | 9600                      | x16           | 2                               | 0.16             |

| 9600                      | 4800                      | x16           | 6                               | 0.16             |

| 4800                      | 2400                      | x16           | \$E                             | 0.16             |

| 2400                      | 1200                      | x16           | \$1E                            | 0.16             |