Force Computers cPCI-522

UltraSPARC IIi

In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/65207-2

nttps://www.artisantg.com/oszo/-z

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

Your **definitive** source for quality pre-owned equipment.

**Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# SPARC/CPCI-52x(G) Technical Reference Manual

P/N 208914 Edition 2.0 November 2000

Force Computers GmbH All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless written permission has been granted.

Copyright by Force Computers

### World Wide Web: www.forcecomputers.com

24-hour access to on-line manuals, driver updates, and application notes is provided via SMART, our SolutionsPLUS customer support program that provides current technical and services information.

## Headquarters

## The Americas

### Force Computers Inc.

5799 Fontanoso Way San Jose, CA 95138-1015 U.S.A.

Tel.: +1 (408) 369-6000 Fax: +1 (408) 371-3382 Email support@fci.com

## **Europe**

### **Force Computers GmbH**

Prof.-Messerschmitt-Str. 1 D-85579 Neubiberg/München Germany

Tel.: +49 (89) 608 14-0 Fax: +49 (89) 609 77 93 Email support@force.de

## Asia

### **Force Computers Japan KK**

Shiba Daimon MF Building 4F 2-1-16 Shiba Daimon Minato-ku, Tokyo 105-0012 Japan

Tel.: +81 (03) 3437 3948 Fax: +81 (03) 3437 3968 Email smiyagawa@fci.com

#### Note

The information in this document has been carefully checked and is believed to be entirely reliable. Force Computers makes no warranty of any kind with regard to the material in this document, and assumes no responsibility for any errors which may appear in this document. Force Computers reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance, or design.

Force Computers assumes no responsibility for the use of any circuitry other than circuitry which is part of a product of Force Computers GmbH. Force Computers does not convey to the purchaser of the product described herein any license under the patent rights of Force Computers GmbH nor the rights of others. All product names as mentioned herein are the trademarks or registered trademarks of their respective companies.

## **Table of Contents**

|   | Usin  | Using This Manualvii |                                          |    |  |  |

|---|-------|----------------------|------------------------------------------|----|--|--|

| 1 | Safe  | ty Notes             |                                          | 1  |  |  |

| 2 | Intro | Introduction         |                                          |    |  |  |

|   | 2.1   | Produc               | ct Nomenclature                          | 8  |  |  |

|   | 2.2   | Orderi               | ing Information                          | 9  |  |  |

| 3 | Insta | allation             |                                          | 11 |  |  |

|   | 3.1   | Installa             | ation Prerequisites and Requirements     | 14 |  |  |

|   |       | 3.1.1                | Requirements                             | 14 |  |  |

|   |       | 3.1.2                | Memory Modules                           | 17 |  |  |

|   |       | 3.1.3                | Solaris Installation                     | 18 |  |  |

|   |       | 3.1.4                | Terminal connection                      | 20 |  |  |

| 4 | Base  | e-520(G)             | Installation                             | 21 |  |  |

|   | 4.1   | Location             | on Overview                              | 21 |  |  |

|   | 4.2   | Mecha                | nnical Construction                      | 23 |  |  |

|   |       | 4.2.1                | FORCE COMPUTERS UPA64S Card Installation | 25 |  |  |

|   | 4.3   | Power                | ing Up                                   | 26 |  |  |

|   | 4.4   | Switch               | Settings                                 | 27 |  |  |

|   | 4.5   | Front 1              | Panel and Connectors                     | 28 |  |  |

|   |       | 4.5.1                | Audio Interface                          | 31 |  |  |

|   |       | 4.5.2                | Ethernet Interfaces                      | 32 |  |  |

|   |       | 4.5.3                | SCSI #1 Connector Pinout                 | 33 |  |  |

|   |       | 4.5.4                | Serial I/O Interface Connector Pinout    | 34 |  |  |

|   |       | 4.5.5                | Keyboard/Mouse Connector                 | 35 |  |  |

|   |       | 4.5.6                | CompactPCI Backplane Connector Pinout    | 36 |  |  |

|   |       |                      |                                          |    |  |  |

|   | 4.6  | SCSI #                       | 1 Configuration                                                         |  |  |  |

|---|------|------------------------------|-------------------------------------------------------------------------|--|--|--|

|   | 4.7  | Ethern                       | et Address and Host ID4                                                 |  |  |  |

|   | 4.8  | OpenB                        | OpenBoot Firmware4                                                      |  |  |  |

|   |      | 4.8.1                        | Boot the System                                                         |  |  |  |

|   |      | 4.8.2                        | NVRAM Boot Parameters                                                   |  |  |  |

|   |      | 4.8.3                        | Diagnostics                                                             |  |  |  |

|   |      | 4.8.4                        | Display System Information                                              |  |  |  |

|   |      | 4.8.5                        | Reset the System                                                        |  |  |  |

|   |      | 4.8.6                        | OpenBoot Help                                                           |  |  |  |

| 5 | I/O- | 52x(G) I                     | nstallation5                                                            |  |  |  |

|   | 5.1  | Locati                       | on Overview5                                                            |  |  |  |

|   | 5.2  | Mecha                        | nical Constructions5                                                    |  |  |  |

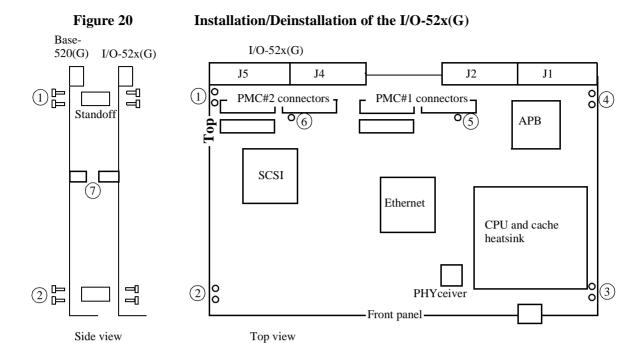

|   |      | 5.2.1                        | Installation/Deinstallation of the I/O-52x(G)                           |  |  |  |

|   | 5.3  | Power                        | ing Up5                                                                 |  |  |  |

|   | 5.4  | <b>.</b>                     |                                                                         |  |  |  |

|   |      | 5.4.1                        | Ethernet #2 Interfaces                                                  |  |  |  |

|   |      | 5.4.2                        | PMC Slots                                                               |  |  |  |

|   |      | 5.4.3                        | CompactPCI Backplane Connector Pinout                                   |  |  |  |

|   | 5.5  | SCSI #                       | <sup>2</sup> Configuration                                              |  |  |  |

|   | 5.6  | .6 Ethernet #2 Configuration |                                                                         |  |  |  |

|   | 5.7  | OpenB                        | oot Firmware Alias Definitions for I/O-52x(G)                           |  |  |  |

| 6 | Har  | dware D                      | escription                                                              |  |  |  |

|   | 6.1  | -                            |                                                                         |  |  |  |

|   |      | 6.1.1                        | Physical Memory Map69                                                   |  |  |  |

|   |      | 6.1.2                        | External Cache Control Unit                                             |  |  |  |

|   |      | 6.1.3                        | Memory Controller Unit, Memory Modules, and Main Memory Configuration . |  |  |  |

|   |      | 6.1.4                        | Interrupt Map                                                           |  |  |  |

|   |      | 6.1.5                        | UltraSPARC-IIi PCI Bus Interface                                        |  |  |  |

|   | 6.2  | APB (A                       | Advanced PCI Bridge) and CompactPCI Interface                           |  |  |  |

|   | 6.3  |                              | et and EBus2 Devices – PCIO                                             |  |  |  |

Page ii SPARC/CPCI-52x(G)

|   |      | 6.3.1     | Ethernet Interface – PCIO                                         | 76  |

|---|------|-----------|-------------------------------------------------------------------|-----|

|   |      | 6.3.2     | EBus2 Interface – PCIO                                            | 77  |

|   |      | 6.3.3     | Boot PROM, Boot and User Flash EPROM                              | 79  |

|   |      | 6.3.4     | Serial Interfaces – SAB 82532                                     | 80  |

|   |      | 6.3.5     | Keyboard/Mouse, FDC and Parallel Interface – Super I/O            | 81  |

|   |      | 6.3.6     | RTC/NVRAM – M48T58                                                | 83  |

|   |      | 6.3.7     | Audio Interface – CS4231A                                         | 84  |

|   |      | 6.3.8     | System Configuration Registers – SCR                              | 85  |

|   |      | 6.3.9     | SCR: Front Panel and Switches                                     | 86  |

|   |      | 6.3.10    | SCR: Boot and User Flash                                          | 89  |

|   |      | 6.3.11    | SCR: Watchdog, Temperature Sensors, and Reset                     | 90  |

|   |      | 6.3.12    | SCR: ENUM Interrupt                                               | 94  |

|   |      | 6.3.13    | SCR: I <sup>2</sup> C-Bus                                         | 95  |

|   | 6.4  | SCSI I    | nterface – SYM53C875                                              | 97  |

|   | 6.5  | PMC S     | lots with Busmode Support                                         | 98  |

|   |      |           |                                                                   |     |

| 7 | FOF  | _         | nBoot Enhancements                                                |     |

|   | 7.1  | System    | Configuration                                                     | 102 |

|   |      | 7.1.1     | System Configuration Register Accesses                            | 102 |

|   |      | 7.1.2     | LEDs, Seven Segment Display and Rotary Switch                     | 106 |

|   |      | 7.1.3     | ID PROM                                                           | 107 |

|   |      | 7.1.4     | Viewing the Switch Status and Controlling the Temperature Sensors | 108 |

|   |      | 7.1.5     | PCI-Probing – NVRAM Configuration Variables                       | 109 |

|   | 7.2  | Flash E   | CPROM Support                                                     | 110 |

|   |      | 7.2.1     | Flash EPROM Programming                                           | 110 |

|   |      | 7.2.2     | Flash EPROM Device Node                                           | 112 |

|   |      | 7.2.3     | Loading and Executing Programs from User Flash EPROM              | 115 |

|   | 7.3  | Hardw     | are Dependencies                                                  | 116 |

|   |      | 7.3.1     | Copying the OpenBoot Image from Boot PROM to Boot Flash EPROM     | 116 |

|   |      | 7.3.2     | Drop-in Drivers                                                   | 118 |

|   |      | 7.3.3     | Flash Memory Driver                                               | 118 |

|   | Prod | luct Erro | or Report                                                         |     |

Page iv SPARC/CPCI-52x(G)

## **List of Tables and Figures**

| Page                                                                 | Tab./ | Fig. |

|----------------------------------------------------------------------|-------|------|

| History of manual publication                                        | Tab.  | a    |

| Fonts, notations and conventions x                                   | Tab.  | b    |

| Product naming conventions                                           | Tab.  | c    |

| Specifications of the SPARC/CPCI-52x(G)                              | Tab.  | 1    |

| Nomenclature of the SPARC/CPCI-52x(G)                                | Tab.  | 2    |

| Excerpt from the product's ordering information                      | Tab.  | 3    |

| SPARC/CPCI-520G (schematic view)                                     | Fig.  | 1    |

| SPARC/CPCI-522 (schematic view)                                      | Fig.  | 2    |

| SPARC/CPCI-522G (schematic view)                                     | Fig.  | 3    |

| SPARC/CPCI-523G (schematic view)                                     | Fig.  | 4    |

| Schematic exploded mechanical construction view                      | Fig.  | 5    |

| Maximum power supply values without UPA64S card and PMC modules 15   | Tab.  | 4    |

| Environmental requirements of the SPARC/CPCI-52x(G)                  | Tab.  | 5    |

| Audio interfaces requirements                                        | Tab.  | 6    |

| Qualified memory modules                                             | Tab.  | 7    |

| MEM-50 – memory module numbering scheme                              | Fig.  | 6    |

| Qualified memory configurations (all data in MByte)                  | Tab.  | 8    |

| Required Solaris Packages                                            | Tab.  | 9    |

| Customizing Solaris                                                  | Tab.  | 10   |

| Location diagram of the Base-520(G) (schematic)                      | Fig.  | 7    |

| Mechanical construction of a Base-520G                               | Fig.  | 8    |

| Mechanical construction of a Base-520G with 4 memory modules         | Fig.  | 9    |

| Mechanical construction of a Base-520                                | Fig.  | 10   |

| Components of a 2-slot configuration with UPA64S card (schematic) 24 | Fig.  | 11   |

| Installing/Deinstalling an UPA64S card                               | Fig.  | 12   |

| Default switch settings                                              | Tab.  | 11   |

| Front panel features                                                 | Tab.  | 12   |

| On-board connectors                                                  | Tab.  | 13   |

| Audio interface signals                                              | Tab.  | 14   |

| Twisted-Pair-Ethernet #1 connector pinout                            | Tab.  | 15   |

| 50-pin SCSI connector pinout                                         | Tab.  | 16   |

| 26-pin serial A+B connector pinout RS232                             | Tab.  | 17   |

| 26-pin serial A+B connector pinout RS422 (factory option)            | Tab.  | 18   |

| Keyboard/mouse connector pinout                                      | Tab.  | 19   |

| CompactPCI J5 connector pinout                                       | Fig.  | 13   |

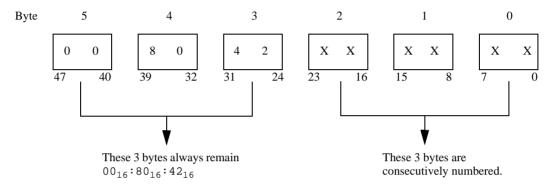

| The 48-bit (6-byte) Ethernet address                                 | Fig.  | 14   |

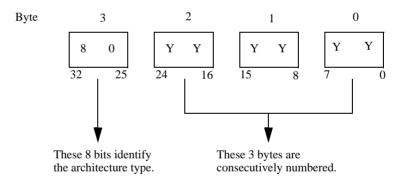

| The 32-bit (4-byte) host ID                                          | Fig.  | 15   |

| Device alias definitions                                             | Tab.  | 20   |

| Setting configuration parameters                                     | Tab.  | 21   |

|                                                                                      | Page | Tab./ | Fig. |

|--------------------------------------------------------------------------------------|------|-------|------|

| Diagnostic routines                                                                  | 47   | Tab.  | 22   |

| Commands to display system information                                               | 49   | Tab.  | 23   |

| Location diagram of the I/O-52x(G) (schematic)                                       | 54   | Fig.  | 16   |

| Mechanical construction of the SPARC/CPCI-522                                        | 55   | Fig.  | 17   |

| Mechanical construction of the SPARC/CPCI-52xG                                       | 55   | Fig.  | 18   |

| Mechanical construction of the SPARC/CPCI-52xG (option)                              | 56   | Fig.  | 19   |

| Installation/Deinstallation of the I/O-52x(G)                                        | 57   | Fig.  | 20   |

| Front panel features                                                                 | 57   | Tab.  | 24   |

| On-board connectors                                                                  | 58   | Tab.  | 25   |

| Twisted-Pair-Ethernet connector pinout                                               | 58   | Tab.  | 26   |

| CompactPCI J4 connector pinout                                                       |      | Fig.  | 21   |

| CompactPCI J5 connector pinout                                                       |      | Fig.  | 22   |

| Device alias definitions                                                             |      | Tab.  | 27   |

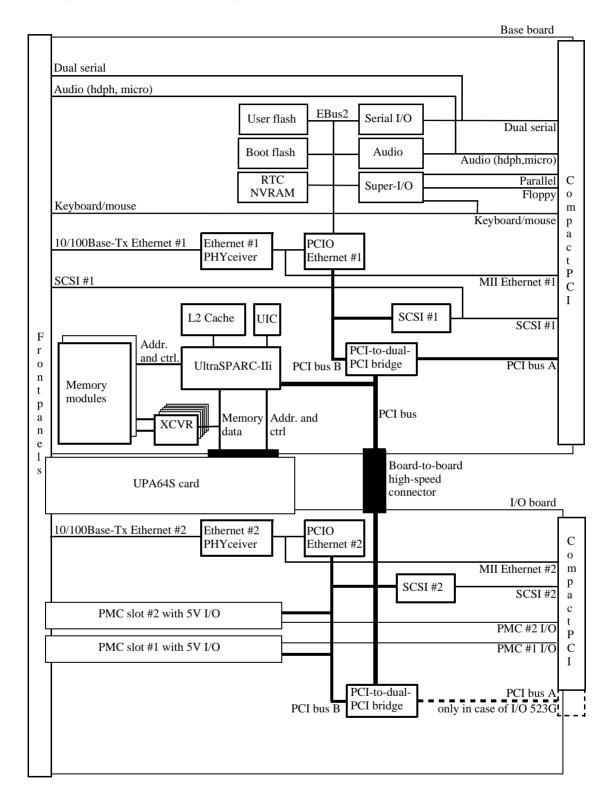

| Block Diagram of the SPARC/CPCI-52x(G)                                               |      | Fig.  | 23   |

| Buses, bus modes, and connected devices                                              |      | Tab.  | 28   |

| UltraSPARC-IIi physical address map (41-bit physical addresses)                      |      | Tab.  | 29   |

| UltraSPARC-IIi internal CSR space (16 MByte)                                         |      | Tab.  | 30   |

| Relating memory capacity to device type and number of banks                          |      | Tab.  | 31   |

| Physical memory addresses for memory modules                                         |      | Tab.  | 32   |

| Interrupt sources from the Base-520(G)                                               |      | Tab.  | 33   |

| Interrupt sources from the I/O-52x(G)                                                |      | Tab.  | 34   |

| UltraSPARC-IIi PCI address space (8 GByte)                                           |      | Tab.  | 35   |

| PCIO EBus2 base address registers                                                    |      | Tab.  | 36   |

| EBus2 memory map in the PCI bus 4 GByte address space                                |      | Tab.  | 37   |

| PCIO EBus2 DMA channels                                                              |      | Tab.  | 38   |

| Boot and user flash address space configuration                                      |      | Tab.  | 39   |

| Address map of the RTC/NVRAM                                                         |      | Tab.  | 40   |

| System configuration register set (SCR), all 8-bit wide                              |      | Tab.  | 41   |

| System Configuration Identification Register                                         |      | Tab.  | 42   |

| User LED $x$ Control Registers, $x = 1, 2$                                           |      | Tab.  | 43   |

| 7-Segment LED Display Control Register                                               |      | Tab.  | 44   |

| Naming the parts of the 7-segment LED display                                        |      | Fig.  | 24   |

| Rotary Switch Status Register                                                        |      | Tab.  | 45   |

| SW4 and SW5 Status Register                                                          |      | Tab.  | 46   |

| Boot and User Flash Size Control Register                                            |      | Tab.  | 47   |

| Miscellaneous Control and Status Register                                            |      | Tab.  | 48   |

| Watchdog Timer Trigger Register                                                      |      | Tab.  | 49   |

| Watchdog and Temperature Control and Status Register                                 |      | Tab.  | 50   |

| Reset Status Register                                                                |      | Tab.  | 51   |

| Miscellaneous Control Register                                                       |      | Tab.  | 52   |

| ENUM Interrupt Control Register                                                      |      | Tab.  | 53   |

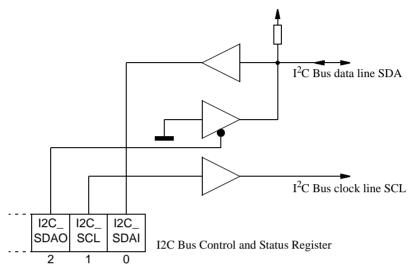

| I <sup>2</sup> C Bus interface                                                       |      | Fig.  | 25   |

| I <sup>2</sup> C Bus slave addresses                                                 |      | Tab.  | 54   |

| I <sup>2</sup> C Bus Control and Status Register                                     |      | Tab.  | 55   |

| I/O pins for PMC busmode function                                                    |      | Tab.  | 56   |

| BUSMODE [42] (r/w) commands                                                          |      | Tab.  | 57   |

| PMC#x BUSMODE[1] (ro) response encoding                                              |      | Tab.  |      |

| * PIC #A - DODPIODE   *   TOTALONOMINO CHOMINE * * * * * * * * * * * * * * * * * * * | //   | iau.  | 20   |

Page vi SPARC/CPCI-52x(G)

## **Using This Manual**

This section does not provide information on the product, but on standard features of the manual itself:

- its structure,

- special layout conventions,

- and related documents.

### **Audience of the Manual**

This *Technical Reference Manual* is intended for hard- and software developers installing and integrating the SPARC/CPCI-52x(G) into their systems.

#### **Overview of the Manual**

This *Technical Reference Manual* provides a comprehensive hardware and software guide to the SPARC/CPCI-52x(G).

The Technical Reference Manual includes

- safety notes: see section 1 "Safety Notes" on page 1.

- a brief overview of the product, the specifications, the ordering information: see section 2 "Introduction" on page 5.

- the installation instructions, a mechanical overview of the product, initialization prerequisites and requirements, the default configuration, for example, the default switch setting and the connector pinouts of the SPARC/CPCI-52x(G).

The installation instructions are separated into 3 sections: one general for the complete SPARC/CPCI-52x(G), one for the Base-520(G), and one for the I/O-52x(G). This modular concept should help you to find the information needed for your SPARC/CPCI-52x(G) configuration easily.

The installation instructions also appear as the product's *Installation* guide – a separate manual delivered together with each product shipped.

- a detailed hardware description : see section 6 "Hardware Description" on page 65.

- a detailed description of OpenBoot which controls the CPU board operations: see section 7 "FORCE OpenBoot Enhancements" on page 101.

The Sun OpenBoot 3.x manuals are available on the following web site: http://docs.sun.com.

The following data sheets of board components are relevant to the SPARC/CPCI-52x(G). They contain appropriate information on configuring and integrating the board in systems and can be found on the respective company's webpage.

- Advanced PCI Bus Bridge Sun SME2411 (http://www.sun.com)

- UltraSPARC-IIi Sun SME1040 (http://www.sun.com)

- PCI I/O Controller Sun STP2003QFP (http://www.sun.com)

- PHYceiver ICS ICS1890 (http://www.icsinc.com)

- PCI-Ultra SCSI (Fast-20) I/O Interface Symbios SYM53C875 (http://www.lsilogic.com)

- Enhanced Serial Communication Controller Siemens SAB82532 (http://www.siemens.com)

- Super I/O NS PC87332VLJ (http://www.national.com)

- Audio Controller Crystal CS4231A (http://www.crystal.com)

- RTC/NVRAM SGS M48T58Y (http://www.st.com)

- Flash Memory AMD Am29F0808B and Am29F016B (http://www.amd.com)

- Temperature Sensor NS LM75 (http://www.national.com)

Page viii SPARC/CPCI-52x(G)

## **Publication History of the Manual**

Table a History of manual publication

| Ed. | Date          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Feb/1998      | First print                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.3 | Jan/1999      | Thoroughly revised, corrected SCSI-related OpenBoot command description, added descriptions for Miscellaneous Control Register, Miscellaneous Control and Status Register as well as ENUM Interrupt Control Register, extended temperature sensor description Added descriptions for installing Solaris, added description for OpenBoot plcc2tsop command (version 3.10.4 or greater) Added note for I2C_SDAO Battery maintenance safety note changed SPARC/MEM-50-5 information added SMART Service information added OpenBoot 3.10.6 information added |

| 2.0 | November 2000 | Section "Safety Notes" included, Solaris versions for required software packages specified, maximum power supply data revised, section "Data Sheets" and data sheet cross-references removed                                                                                                                                                                                                                                                                                                                                                             |

## **Fonts, Notations and Conventions**

Table b Fonts, notations and conventions

| Notation Description    |                                                                                                                                                                                      |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | All numbers are decimal numbers except when used with the following notations:                                                                                                       |

| 0000.0000 <sub>16</sub> | Typical notation for hexadecimal numbers (digits are 0 through F), e.g. used for addresses and offsets.  Note the dot marking the 4th (to its right) and 5th (to its left) digit.    |

| 00008                   | Same for octal numbers (digits are 0 through 7)                                                                                                                                      |

| 00002                   | Same for binary numbers (digits are 0 and 1)                                                                                                                                         |

| Program                 | Typical character format used for names, values, and the like. It is used to indicate when to type literally the same word. Also used for on-screen output.                          |

| Variable                | Typical character format for words that represent a part of a command, a programming statement, or the like, and that will be replaced by an applicable value when actually applied. |

## Table c Product naming conventions

| Used Name         | Description                                                                |

|-------------------|----------------------------------------------------------------------------|

| SPARC/CPCI-52x(G) | General name for all available product configurations                      |

| Base-520(G)       | General name for all available base board configurations                   |

| Base-520G         | Name for base board with UPA64S slot                                       |

| Base-520          | Name for base board with 1 slot front panel                                |

| I/O-52x(G)        | General name for all available I/O-board configurations                    |

| I/O-52xG          | General name for I/O-board configurations, G stands for an additional slot |

| I/O-522(G)        | General name for peripheral slot I/O-board                                 |

| I/O-523G          | Name for system slot I/O-board with second CompactPCI interface            |

Page x SPARC/CPCI-52x(G)

## Icons for Ease of Use: Safety Notes and Tips & Tricks

The following 3 types of safety notes appear in this manual. Be sure to always read and follow the safety notes of a section first – before acting as documented in the other parts of the section.

## **Danger**

Dangerous situation: serious injuries to people or severe damage to objects.

### Caution

Possibly dangerous situation: slight injuries to people or damage to objects possible.

*Note:* No danger encountered. Pay attention to important information marked using this layout.

Page xii SPARC/CPCI-52x(G)

## 1 Safety Notes

This section provides safety precautions to follow when installing, operating, and maintaining the SPARC/CPCI-52x(G). For your protection, follow all warnings and instructions found in the following text.

## General notes

This *Technical Reference Manual* provides the necessary information to install and handle the SPARC/CPCI-52x(G). As the product is complex and its usage manifold, we do not guarantee that the given information is complete. In case you need additional information, ask your Force Computers representative.

The SPARC/CPCI-52x(G) has been designed to meet the standard industrial safety requirements. It must not be used except in its specific area of office telecommunication industry and industrial control.

Only personnel trained by Force Computers or qualified persons in electronics or electrical engineering are authorized to install, uninstall or maintain the SPARC/CPCI-52x(G). The information given in this manual is meant to complete the knowledge of a specialist and must not be taken as replacement for qualified personnel.

Make sure that contacts and cables of the board cannot be touched while the board is operating.

### **Installation**

Electrostatic discharge and incorrect board installation and uninstallation can damage circuits or shorten their life. Therefore:

- Before installing the board, check section 3.1.1 "Requirements" on page 14.

- Before touching integrated circuits, ensure that you are working in an electrostatic-free environment.

- When plugging the board in or removing it, do not press on the front panel but use the handles.

- Before installing or uninstalling the board, read section 3 "Installation" on page 11.

- Before installing or uninstalling an additional device or module, read the respective documentation.

• Ensure that the board is connected to the CompactPCI backplane via both the J1 and the J2 connectors and that power is available on both CompactPCI connectors.

## **Operation**

- While operating the board ensure that the power and environmental requirements as given in table 4 "Maximum power supply values without UPA64S card and PMC modules" on page 15 and table 5 "Environmental requirements of the SPARC/CPCI-52x(G)" on page 15 are met.

- When operating the board in areas of strong electromagnetic radiation ensure that the board is bolted on the CompactPCI rack and shielded by closed housing.

### **EMC**

If boards are integrated into open systems, always cover empty slots.

## **Expansion**

- Check the total power consumption of all components installed (see the technical specification of the respective components). For the total power consumption of the SPARC/CPCI-52x(G), see table 4 "Maximum power supply values without UPA64S card and PMC modules" on page 15.

- Ensure that any individual output current of any source stays within its acceptable limits (see the technical specification of the respective source).

- Only replace components or system parts with those recommended by Force Computers. In case you use components other than those recommended by Force Computers, you are fully responsible for the impact on EMI and the eventually changed functionality of the product.

## Battery change

If a Lithium battery on the board has to be exchanged, observe the following safety notes:

- Incorrect exchange of Lithium batteries can result in a hazardous explosion.

- Always use the same type of Lithium battery as is already installed.

## Protect your environment

Always dispose used batteries and/or old boards according to your country's legislation.

Page 2 SPARC/CPCI-52x(G)

## RJ-45 connector

An RJ-45 connector is available on the board. Take into account that the RJ-45 connector type is used for telephone connectors and for twisted pair Ethernet (TPE) connectors. Note that mismatching these 2 connectors may destroy your telephone as well as your SPARC/CPCI-52x(G). Therefore:

- Make sure that TPE connectors near your working area are clearly marked as network connectors.

- Make sure that TPE bushing of the system is connected only to safety extra low voltage (SELV) circuits.

- Verify that the length of the electric cable connected to a TPE bushing does not exceed 1 kilometer outside the building.

- If in doubt, ask your system administrator.

Page 4 SPARC/CPCI-52x(G)

## 2 Introduction

The SPARC/CPCI-52x(G) is a high performance CompactPCI board computer providing a CompactPCI system controller interface including DMA. It is based on

- the UltraSPARC-IIi processor

- the Advanced PCI Bridge (APB) with interfaces to the CompactPCI bus

An UPA64S card can be connected for high performance graphics support.

## Memory

- 32 to 1024-Mbyte EDO DRAM

- Up to 1 Mbyte secondary (L2) cache

- 1 Mbyte PLCC boot PROM and 2 Mbyte TSOP boot flash EPROM

- Up to 4 Mbyte user flash EPROM

### Interfaces

Interfaces of the Base-520(G):

- PCI bridge for 7 CompactPCI slots

- 10BaseT/100BaseTx Ethernet on front panel and MII on backplane

- Wide Ultra SCSI

- 2 serial I/O ports RS-232

- Floppy disc, parallel and Keyboard/Mouse ports

- UPA64S (only Base-520G)

Interfaces of the I/O-52x(G):

- 10BaseT/100BaseTx Ethernet on front panel and MII on backplane

- Wide Ultra SCSI

- 2 standard PMC card slots

- PCI bridge for additional 7 CompactPCI slots (only I/O-523G)

### Real-time clock

A real-time clock with on-board battery backup is also available.

Page 6 SPARC/CPCI-52x(G)

Table 1

Specifications of the SPARC/CPCI-52x(G)

| Processor                  | UltraSPARC-IIi with 300 MHz                                                                              |  |

|----------------------------|----------------------------------------------------------------------------------------------------------|--|

| Shared main memory         | 32 MByte to 1 GByte EDO DRAM with ECC                                                                    |  |

| L2 cache                   | 256 KByte or 1 MByte late write SRAM with parity                                                         |  |

| PMC slots                  | 2 for 32 bit with 33 MHz PMC modules                                                                     |  |

| CompactPCI interface       | 32 bit with 33 MHz                                                                                       |  |

| SCSI                       | Wide Ultra SCSI I/O on front panel and backplane                                                         |  |

| Ethernet                   | MII and 10BaseT/100BaseTx half and full duplex Ethernet Twisted Pair on front panel and MII on backplane |  |

| Parallel port with DMA     | Centronics compatible, uni- or bidirectional I/O on backplane                                            |  |

| Floppy Disk Interface      | I/O on backplane                                                                                         |  |

| Serial I/O                 | 2 ports with RS-232 configuration (as factory option RS-422) I/O on front panel or backplane             |  |

| Audio Port                 | I/O on front panel (microphone and headphone) or backplane                                               |  |

| Keyboard/Mouse Port        | I/O on front panel or backplane                                                                          |  |

| Boot PROM (PLCC)           | 1 MByte PROM (OTP)                                                                                       |  |

| Boot flash EPROM<br>(TSOP) | 2 MByte flash EPROM<br>On-board programmable with hardware write protection                              |  |

| User flash EPROM<br>(TSOP) | Up to 4 MByte (2 MByte in default configuration) On-board programmable with hardware write protection    |  |

| RTC/NVRAM/Battery          | M48T58; NVRAM reserved for OpenBoot                                                                      |  |

| Additional Features        | Reset and abort key, status LEDs, hexadecimal display, rotary switch                                     |  |

| Firmware                   | OpenBoot with diagnostics                                                                                |  |

| Power consumption          | see "Power supply" on page 14                                                                            |  |

| Environm. Conditions       | see "Thermal requirements" on page 15                                                                    |  |

| PCI compliants             | CompactPCI Specification PICMG 2.0 R2.1 PCI Specification Rev. 2.1.                                      |  |

Product Nomenclature Introduction

## 2.1 Product Nomenclature

The SPARC/CPCI-52x(G) is available in several variants, with or without I/O-52x(G) as well as several memory and speed options. Consult your local sales representative to confirm availability of specific combinations. The table below explains the general product nomenclature.

Table 2

Nomenclature of the SPARC/CPCI-52x(G)

| SPARC/CPCI-52xG/mmm-sss-c-uu-ggg  |                                                                 |  |  |

|-----------------------------------|-----------------------------------------------------------------|--|--|

| x = 0 $x = 2$ $x = 3$             | Base-520(G)<br>Base-520(G) + I/O-522(G)<br>Base-520G + I/O-523G |  |  |

| G extra slot (for an UPA64S card) |                                                                 |  |  |

| mmm DRAM capacity in MByte        |                                                                 |  |  |

| sss CPU speed in MHz              |                                                                 |  |  |

| С                                 | L2-cache size in KByte divided by 256 (e.g.: 4=1024 KByte)      |  |  |

| uu User flash EPROM size in MByte |                                                                 |  |  |

| ggg                               | gg UPA64S card type if preinstalled                             |  |  |

Page 8 SPARC/CPCI-52x(G)

Introduction Ordering Information

## 2.2 Ordering Information

The following table is an excerpt from the SPARC/CPCI-52x(G) ordering information at the time of print. Contact your local FORCE COMPUTERS representative for current information.

Table 3 Excerpt from the product's ordering information

| Product name        | Description                                                                                                                  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| SPARC/CPCI-520      | Base-520(G)                                                                                                                  |  |

| G/64-300-4-2        | with 64 MByte DRAM, 300 MHz CPU, 1 MByte L2 cache, 2 MByte user flash EPROM, and UPA64S slot                                 |  |

| SPARC/CPCI-522      | Base-520(G) and I/O-52x(G) (dual SCSI, dual Ethernet, 2 PMC slots)                                                           |  |

| G/64-300-4-2        | with 64 MByte DRAM, 300 MHz CPU, 1 MByte L2 cache, 2 MByte user flash EPROM, and UPA64S slot                                 |  |

| SPARC/MEM           |                                                                                                                              |  |

| 50M/128             | user upgradable memory module for slot 2 and 3, 128 Mbyte                                                                    |  |

| 50M/256             | user upgradable memory module for slot 2 and 3, 256 Mbyte                                                                    |  |

| 50U/128             | user upgradable memory module for slot 2 or 4, 128 Mbyte                                                                     |  |

| 50U/256             | user upgradable memory module for slot 2 or 4, 256 Mbyte                                                                     |  |

| Accessories SPARC/  |                                                                                                                              |  |

| IOBP-520/CPU        | I/O panel for the Base-520(G)                                                                                                |  |

| IOBP-520/IO         | I/O panel for the I/O-52x(G)                                                                                                 |  |

| CPCI-520/AccKit/CPU | I/O panel for the Base-520(G) with cables: 2 serial splitter cable, 1 Micro D-Sub and 1 flat ribbon SCSI cable, 1 TPE cable. |  |

| CPCI-520/AccKit/IO  | I/O panel for the I/O-52x(G) with cables: 1 flat ribbon SCSI cable, 1 TPE cable.                                             |  |

| UPA/C2D             | Creator 2D graphic card                                                                                                      |  |

| UPA/C3D             | Creator 3D graphic card                                                                                                      |  |

| CPCI-52x/TM         | Technical Reference Manual Set for SPARC/CPCI-52x(G).                                                                        |  |

Ordering Information Introduction

Page 10 SPARC/CPCI-52x(G)

## 3 Installation

This section describes the SPARC/CPCI-52x(G) variants you may purchase from FORCE COMPUTERS. It is intended to get an overview over all possible configurations with named components which will help to find the information necessary for your configuration in this manual.

How to begin installation

First read the Safety Notes and the Installation Prerequisites and Requirements (see section 1 "Safety Notes" on page 1 and section 3.1 "Installation Prerequisites and Requirements" on page 14).

Then go through the Base-520(G) installation section and the I/O-52x(G) installation section, depending on the variant you have purchased from FORCE COMPUTERS (see section 4 "Base-520(G) Installation" on page 21 and see section 5 "I/O-52x(G) Installation" on page 53).

SPARC/ CPCI-52x(G) variants There are 4 variants available:

• a SPARC/CPCI-520G obtaining the 2 slot high base board with UPA64S card option named in this manual as Base-520G (or in general as Base-520G)).

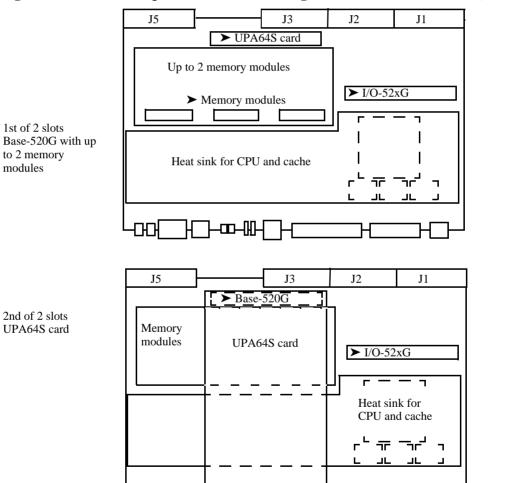

Figure 1 SPARC/CPCI-520G (schematic view)

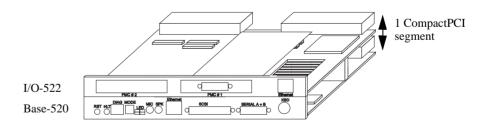

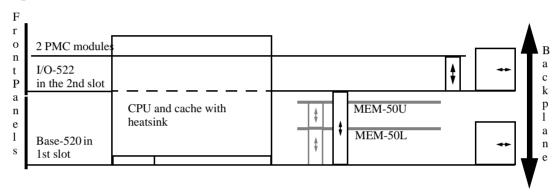

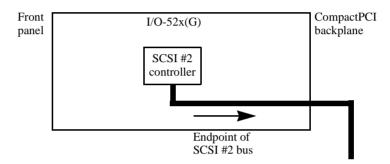

a SPARC/CPCI-522 obtaining the 1 slot Base-520 with the peripheral slot I/O-522.

Figure 2 SPARC/CPCI-522 (schematic view)

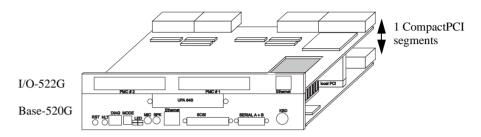

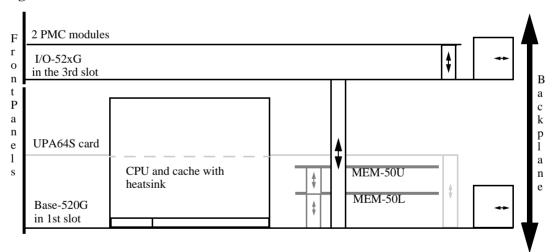

# • a SPARC/CPCI-522G obtaining the 2 slot base board with UPA64S card option (Base-520G) and with the peripheral slot I/O-522G.

Figure 3 SPARC/CPCI-522G (schematic view)

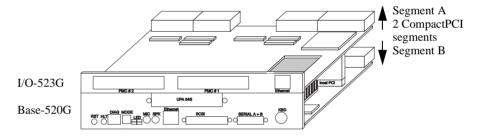

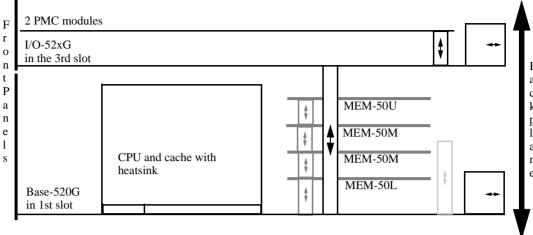

and a SPARC/CPCI-523G

which is a dual-segment CompactPCI variant obtaining the 2 slot

base board with UPA64S card option (Base-520G) and with the sys tem slot I/O-523G. The dual-segment variant is designed for Com pactPCI systems with a backplane consisting of 2 CompactPCI bus

segments.

Figure 4 SPARC/CPCI-523G (schematic view)

Page 12 SPARC/CPCI-52x(G)

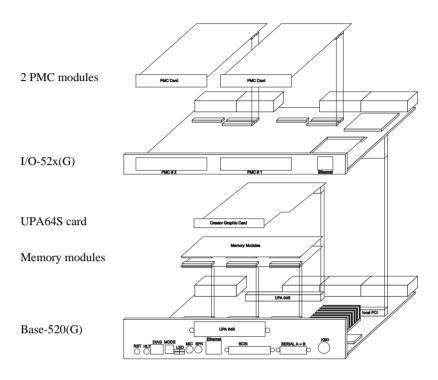

The following figure is intended to get an overview over all available main components of a SPARC/CPCI-52x(G).

Figure 5 Schematic exploded mechanical construction view

## **Caution**

### Danger

The SPARC/CPCI-52x(G) is a sytem board. According to the *CompactPCI Specification PICMG 2.0 R2.1*, the front panel of the SPARC/CPCI-52x(G) shows a triangle. To ensure proper functioning of the board, plug it exclusively in a system slot marked by a triangle.

The Lithium battery of the RTC/NVRAM provides a data retention of at least 7 years summing up all periods of actual battery use. Therefore FORCE COMPUTERS assumes that there usually is no need to exchange the Lithium battery except for example in the case of long-term spare part handling.

Please observe the following:

- Exchange the battery before 7 years of actual battery use have elapsed.

- Exchanging the battery always results in data loss of the devices which use the battery as power backup. Therefore, back up affected data before exchanging the battery.

- Always use the same type of Lithium battery as is already installed.

- Use appropriate tools to remove the battery.

- When installing the new battery ensure that the marked dot on top of the battery covers the dot marked on the chip.

- Used batteries have to be disposed according to your country's legislation.

## 3.1 Installation Prerequisites and Requirements

### Caution

Before powering up check:

- this section for installation prerequisites and requirements

- and the consistency of the current switch setting (see section 4.4 "Switch Settings" on page 27).

## 3.1.1 Requirements

The installation requires at least

- a power supply

- a minimum airflow meeting the thermal requirements,

- and free CompactPCI backplane slots due to your SPARC/CPCI-52x(G) variant:

- a system CompactPCI bus slot for the Base-520(G)

- an additional system CompactPCI bus slot for the IO-523G on the right side of the Base-520(G)

- an additional system or peripheral CompactPCI bus slot for the IO-522(G) on the right side of the Base-520(G).

Peripheral slot

A peripheral slot of a CompactPCI rack is marked by a circle.

System slot

A system slot of a CompactPCI rack is marked by a triangle.

Signaling level

The SPARC/CPCI-52x(G) is a CompactPCI-universal board operational in 3.3 V or 5 V CompactPCI systems. Therefore, no voltage keys are provided on the CompactPCI interface.

Power supply

The power supply must meet the specifications given in the following table. The values in the table below are maximum values without an UPA64S card installed and without PMC modules.

Page 14 SPARC/CPCI-52x(G)

CPU board +5 V +3.3 V+/-12 VV I/O SPARC/CPCI-520 4.6 A 6.5 A not required 200 mA SPARC/CPCI-520G 6.5 A 4.6 A not required 200 mA 7.8 A 5.6 A SPARC/CPCI-522 not required 200 mA SPARC/CPCI-522G 7.8 A 5.6 A 200 mA not required 400 mA SPARC/CPCI-523G 7.8 A 5.6 A not required Creator Graphic Card 1.3 A 2.2 A not required not required

Table 4 Maximum power supply values without UPA64S card and PMC modules

Thermal requirements

The operating temperature is 0 °C to +55 °C (humidity 5 % to 95 % non-condensing at +40 °C), when operating the SPARC/CPCI-52x(G) in systems providing a minimum forced airflow of 300 LFM (linear feet per minute). The typical operating temperature of the system is 0 °C to +40 °C.

Table 5 Environmental requirements of the SPARC/CPCI-52x(G)

|                 | Operating                              | Non-operating                          |

|-----------------|----------------------------------------|----------------------------------------|

| Temperature     | 0 °C to +55 °C                         | -40 °C to +85 °C                       |

| Forced air flow | 300 LFM (linear feet per minute)       | -                                      |

| Temp. change    | +/- 0.5 °C/min                         | +/- 1 °C/min                           |

| Rel. humidity   | 5 % to 95 % noncondensing<br>at +40 °C | 5 % to 95 % noncondensing<br>at +40 °C |

| Altitude        | -300 m to +3,000 m                     | -300 m to +13,000 m                    |

Audio interfaces

Simultaneous use of the audio interfaces available on the front panel and on the backplane can damage on-board hardware or connected devices. For example: never use the headphone/line audio output at the backplane, if a headphone is plugged into the front-panel jack.

• Always use at most one of the interfaces if an audio interface is available on both the front panel and the backplane.

Table 6

Audio interfaces requirements

| Interface                          | Description                                                                                                                           |  |  |  |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Stereo Micro In<br>(op-amp pre-amp | Signal level: single-ended condensator microphones with signal level                                                                  |  |  |  |  |

| with 18 dB gain)                   | -up to 12 mV with 20 dB gain inside Codec enabled                                                                                     |  |  |  |  |

|                                    | -and up to 120 mV with 20 dB gain inside Codec disabled                                                                               |  |  |  |  |

|                                    | Availability: on front panel and as factory option on backplane instead of Aux#2 In                                                   |  |  |  |  |

| Stereo Head-<br>phone/ Line Out    | Signal level: maximum 2 V <sub>RMS</sub> line-level signal output (also designed to directly drive headphones)                        |  |  |  |  |

|                                    | Availability: on front panel and on backplane                                                                                         |  |  |  |  |

| Stereo Line In                     |                                                                                                                                       |  |  |  |  |

|                                    | Availability: on backplane                                                                                                            |  |  |  |  |

| Stereo Aux#1 In                    | • Signal level: ~10 k $\Omega$ input impedance; maximum full scale input of 2 $V_{RMS}$                                               |  |  |  |  |

|                                    | Availability: on backplane                                                                                                            |  |  |  |  |

| Stereo Aux#2 In                    | • Signal level: ~10 k $\Omega$ input impedance; maximum full scale input of 2 $V_{RMS}$                                               |  |  |  |  |

|                                    | Availability: on backplane                                                                                                            |  |  |  |  |

| Mono In                            | • Signal level: typical 47 k $\Omega$ audio input impedance; nominally 1 $V_{RMS}$ maximum (centered around 2.1 V) input signal level |  |  |  |  |

|                                    | Availability: as factory option on front panel instead of Micro In and as factory option on backplane instead of Aux#1 In             |  |  |  |  |

| Mono Out                           | Signal level depends on the setting of OLB which is a bit in the Codecs Alternate Feature Enable I register (I16)                     |  |  |  |  |

|                                    | -maximum 1 $V_{RMS}$ output (centered around 2.1 V) if OLB = 1                                                                        |  |  |  |  |

|                                    | –or maximum 0.707 $V_{RMS}$ (centered around 2.1 V) if OLB = 0                                                                        |  |  |  |  |

|                                    | Default is OLB = 0.                                                                                                                   |  |  |  |  |

|                                    | Availability: as factory option on backplane instead of Head-<br>phone/Line Out                                                       |  |  |  |  |

Page 16 SPARC/CPCI-52x(G)

## 3.1.2 Memory Modules

The main memory capacity is adjustable via installation of the appropriate memory modules.

The qualified memory modules depend on the SPARC/CPCI-52x(G) processor frequency. They are given in the following table.

Table 7 Qualified memory modules

| Processor frequency | Memory modules  |  |

|---------------------|-----------------|--|

| up to 300 MHz       | SPARC/MEM-50x   |  |

|                     | SPARC/MEM-50x-5 |  |

| 333 MHz and above   | SPARC/MEM-50x-5 |  |

## **Caution**

Do not install SPARC/MEM-50x and SPARC/MEM-50x-5 memory modules on the same board, otherwise system malfunction may occur.

In the following it will be refered to all memory module types as SPARC/MEM-50x.

The Base-520(G) can hold 1 to 4 memory modules providing up to 1 GByte DRAM capacity. 1 memory module can carry 2 memory banks.

Note: At least 1 lower memory module MEM-50L is required.

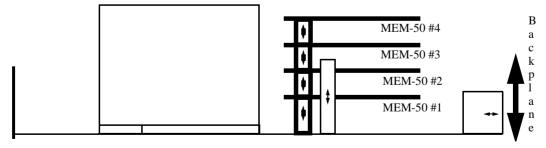

See the following figure for the memory module numbering scheme:

- Memory modules #1 and #2 are located in the first CompactPCI slot the SPARC/CPCI-52x(G) occupies.

- Memory modules #3 and #4 are located in the second CompactPCI slot the SPARC/CPCI-52x(G) occupies.

Figure 6 MEM-50 – memory module numbering scheme

The memory configuration is adjustable to the application's needs via selection of the appropriate memory modules. The memory configuration must fulfill the following requirements:

- The lowest memory module (#1) must be a SPARC/MEM-50L which is a lower memory module.

- The top memory module (with the greatest number in your configuration given the number scheme in the figure above) can be a SPARC/MEM-50M or SPARC/MEM-50U which is a middle (M) or upper (U) memory module. The upper module misses the connectors for another memory module to be stacked on top.

- The memory modules between the lowest and the top memory module must be SPARC/MEM-50M, i.e. middle memory modules.

- If a UPA64S card is installed, at most 2 memory modules can be installed and memory module #2 must be a SPARC/MEM-50U, i.e. an upper memory module.

- Note the limitations given by the SPARC/CPCI-52x(G) configuration under consideration (see section 4.2 "Mechanical Construction" on page 23).

Out of the extensive list of possible configurations the following memory module configurations have been qualified (others may be tested and qualified on request):

Table 8 Qualified memory configurations (all data in MByte)

| Total capacity | 32 | 64 | 128 | 256 | 384 | 512 | 768 | 1024 |

|----------------|----|----|-----|-----|-----|-----|-----|------|

| Mem. module #4 | _  | _  | _   | _   | _   | _   | _   | 256  |

| Mem. module #3 | _  | _  | _   | _   | _   | _   | 256 | 256  |

| Mem. module #2 | _  | _  | _   | _   | 128 | 256 | 256 | 256  |

| Mem. module #1 | 32 | 64 | 128 | 256 | 256 | 256 | 256 | 256  |

For installation information see the respective *Installation Guide* delivered together with the memory module.

#### 3.1.3 Solaris Installation

When installing Solaris, there are some general installation guidelines to be followed before and during Solaris installation and a specific guideline related to SCSI to be followed after Solaris installation (see "SCSI" on page 20).

Page 18 SPARC/CPCI-52x(G)

### **General Installation Guidelines**

*Note:* Solaris versions and hardware updates prior to 2.5.1 11/97 and 2.6 03/98 are not supported.

Required software packages

In case of Solaris 2.5.1 and Solaris 2.6 the following Solaris software packages must be installed, otherwise Solaris fails to boot.

## Table 9 Required Solaris Packages

| Package    | Description                       |  |  |

|------------|-----------------------------------|--|--|

| SUNWvplr.u | SMCC sun4u new platform links     |  |  |

| SUNWvplu.u | SMCC sun4u new usr/platform links |  |  |

When setting up Solaris interactively, these packages can be installed by selecting the proper software group in the Software dialog. Customize the software groups as follows:

Table 10 Customizing Solaris

|                                         | Customization required for     |             |  |

|-----------------------------------------|--------------------------------|-------------|--|

| Software Group                          | Solaris 2.5.1                  | Solaris 2.6 |  |

| Entire distribution plus<br>OEM support | No customization is required   |             |  |

| Entire distribution                     | Select the following clusters: |             |  |

| Developer system support                | SMCC platform links            |             |  |

| End user system support                 |                                |             |  |

| Core system support                     |                                |             |  |

### **SCSI**

The Solaris SCSI driver may revert Wide-SCSI devices, which are connected to the front-panel SCSI connector, to asynchronous mode. However, it is possible to operate such a configuration in synchronous mode also by inserting the following line into /kernel/drv/glm.conf:

targetn-scsi-options=0x5f8

where n is the SCSI ID of the Wide-SCSI device under consideration. In case of several Wide-SCSI devices insert the respective line per device. Terminate the file with a ";".

### 3.1.4 Terminal connection

The SPARC/CPCI-52x(G) provides 2 serial interfaces (A and B) which are implemented on the Base-520(G). For the initial power up, a terminal can be connected to interface A via the front-panel 26-pin-MicroD-Sub connector SERIAL A+B. Per default, all serial I/O interfaces provide an RS-232 interface. As factory option the 2 interfaces can be configured as RS-422 interface.

For information on the serial interface connector pinout, see section 4.5.4 "Serial I/O Interface Connector Pinout" on page 34.

Page 20 SPARC/CPCI-52x(G)

## 4 Base-520(G) Installation

## 4.1 Location Overview

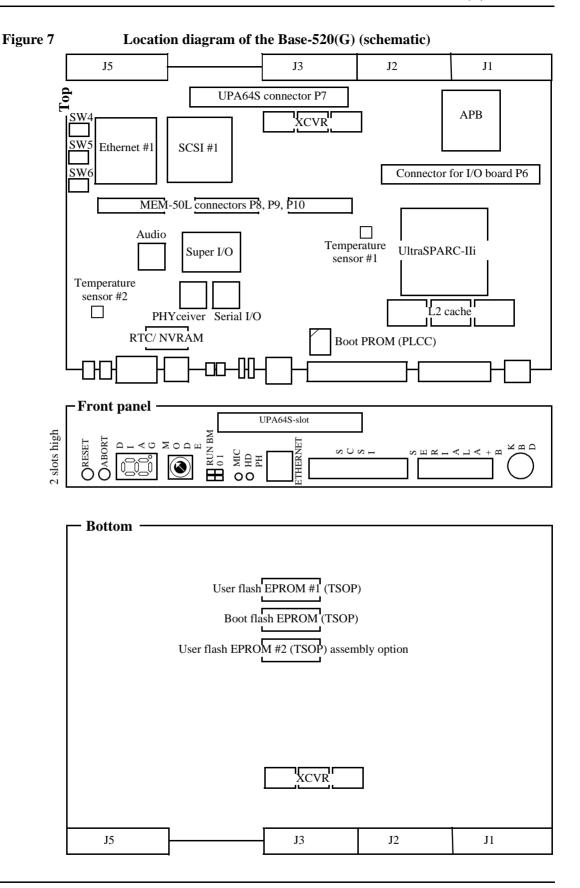

The Base-520(G) contains the following main components:

- a UltraSPARC-IIi processor,

- a second level cache (L2 cache),

- a CompactPCI interface,

- a boot PROM (PLCC),

- a boot flash EPROM (TSOP) and an user flash EPROM (TSOP),

- 3 connectors for the memory modules,

- a connector for interfacing to a UPA64S card,

- a connector for interfacing to the I/O-52x(G),

- switches,

- temperature sensors,

- and the following I/O interfaces: SCSI #1, Ethernet #1, floppy, keyboard and mouse, audio, parallel interface as well as the 2 serial interfaces A+B.

Location Overview Base-520(G) Installation

Page 22 SPARC/CPCI-52x(G)

### 4.2 Mechanical Construction

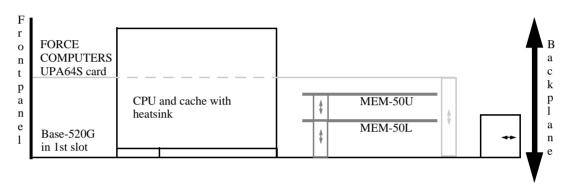

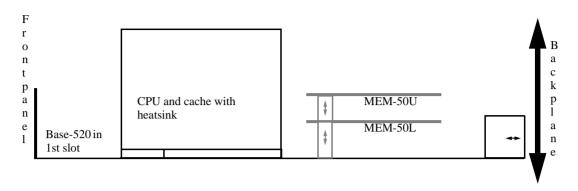

The Base-520(G) is a CompactPCI computer. It occupies 2 CompactPCI slots and consists of the following major components:

- an I/O connector for the I/O-52x(G),

- an UPA64S connector for an UPA64S card (only Base-520G),

- 3 memory module connectors for up to 4 memory modules. With an installed UPA64S card only 2 memory modules are possible.

The following figures show the Base-520(G) in possible configurations:

Figure 8 Mechanical construction of a Base-520G

Figure 9 Mechanical construction of a Base-520G with 4 memory modules

Figure 10 Mechanical construction of a Base-520

The Base-520 is only available as a 2-slot solution with an I/O-522.

Figure 11 Components of a 2-slot configuration with UPA64S card (schematic)

Page 24 SPARC/CPCI-52x(G)

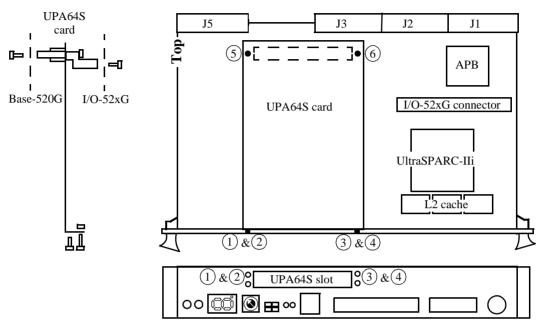

#### **4.2.1 FORCE COMPUTERS UPA64S Card Installation**

You can only install a FORCE COMPUTERS UPA64S card if you purchased a SPARC/CPCI-52xG version. It is connected to the Base-520G via the UPA64S connector P7 (see figure 7 "Location diagram of the Base-520(G) (schematic)" on page 22).

*Note:* Use only UPA64S cards from FORCE COMPUTERS. Throughout this section the term "UPA64S card" always refers to a card purchased from FORCE COMPUTERS and specified for use with a SPARC/CPCI-52xG.

For the locations mentioned in the description see figure 12 "Installing/Deinstalling an UPA64S card" on page 26.

# Installation of a UPA64S card

- 1. If an I/O-52xG is installed, remove it as described in the I/O-52x(G) installation section. Remove the 2 z-standoffs at location 5 and 6 from the Base-520G by loosing the respective 2 screws. Keep them in a save place to have them available for reusing the I/O-52xG without UPA64S card.

- 2. If you do not install an I/O-52xG afterwards: Remove the 2 z-stand-offs fixed on the UPA64S card by loosing the respective 2 screws and fix the UPA64S card again with 2 of the 4 shorter screws delivered with the UPA64S card on the 2 standoffs which connect it to the Base-520G.

- 3. Remove the blind panel fixed in the UPA64S front panel slot. Store it in a safe place for later use.

- 4. Plug the prepared UPA64S card from FORCE COMPUTERS to the respective UPA64S connector on the Base-520G.

- 5. Fix the UPA64S card with 2 of the 4 short screws at location 5 and 6 on the bottom side of the Base-520G and with the 4 screws and 2 nuts from the blind panel on the front panel at location 1...4.

Now the UPA64S card is installed.

6. If an I/O-52xG was installed, fix it again as described in the I/O-52x(G) installation section.

# Uninstalling a UPA64S card

- 1. If an I/O-52xG is installed, remove it as described in the I/O-52x(G) installation section.

- 2. Remove the 4 screws and 2 nuts on the front panel at location 1...4. Remove the 2 screws at location 5 and 6 on the bottom side of the Base-520G.

- 3. Remove the UPA64S card by lifting it.

Powering Up Base-520(G) Installation

- 4. If you do not install the UPA64S card again, fix the blind panel.

- 5. To install the I/O-52xG again refer to the installation section of the I/O-52x(G).

Figure 12 Installing/Deinstalling an UPA64S card

## 4.3 Powering Up

The initial powering up can be done by connecting a terminal to the front panel serial I/O interface A. The advantage of using a terminal is that you do not need any frame buffer, monitor, or keyboard for initial powering up.

**Booting**

The SPARC/CPCI-52x(G) boot PROM consists of a 1 MByte PROM (OTP) PLCC socket device (not writeable). Alternatively a 2 MByte TSOP boot flash EPROM device can be enabled by SW6-2. This boot flash EPROM device is writeable if enabled by SW4-3.

*Note:* If you have an unformatted floppy disk in a floppy connected to your SPARC/CPCI-52x(G) then the OpenBoot does not come up.

Per default the SPARC/CPCI-52x(G) is shipped with its boot PROM containing the OpenBoot firmware (see section 4.8 "OpenBoot Firmware" on page 42).

Page 26 SPARC/CPCI-52x(G)

Base-520(G) Installation Switch Settings

User application

The SPARC/CPCI-52x(G) provides 1 user flash EPROM devices (2M\*8) to store user applications. As factory option 2 user flash EPROM devices (2M\*8) are possible. For write-protection of the user flash EPROM see SW4-4 in section 4.4 "Switch Settings" on page 27.

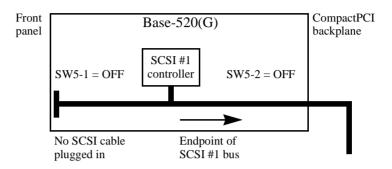

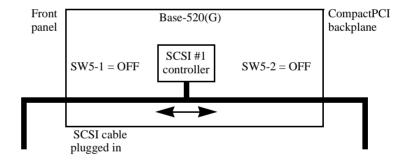

## 4.4 Switch Settings

The following table lists the functions and the default settings of all switches shown in figure 7 "Location diagram of the Base-520(G) (schematic)" on page 22.

*Note:* Before powering up the board check the current switch settings for consistency. Do not switch during operation.

Table 11 Default switch settings

| Name and default setting |              | Function                                                                                                                                            |

|--------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| ON<br>1                  | SW4-1<br>OFF | Reset key on front-panel control  OFF = RESET key enabled  ON = RESET key disabled                                                                  |

| 2                        | SW4-2<br>OFF | Abort key control  OFF = ABORT key enabled  ON = ABORT key disabled                                                                                 |

|                          | SW4-3<br>OFF | Boot flash EPROM write protection<br>(only relevant if SW6-2 = ON)<br>OFF = boot flash EPROM write protected<br>ON = boot flash EPROM write enabled |

|                          | SW4-4<br>OFF | User flash EPROM write protection  OFF = user flash EPROM write protected  ON = user flash EPROM write enabled                                      |

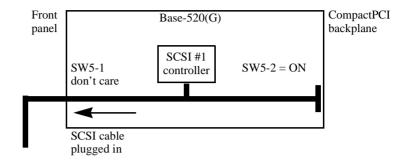

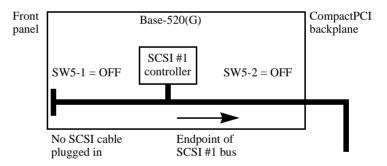

**Function** Name and default setting SW5-1 SCSI termination for SCSI #1 on front panel **OFF** OFF = front panel termination automatic ON ON = front panel termination disabled SW5-2 SCSI termination for SCSI #1 on backplane **OFF** OFF = backplane termination disabled ON = backplane termination enabled SW5-3 Reserved, must be OFF **OFF** SW5-4 Reserved, must be OFF **OFF** SW6-1 Reserved, must be OFF **OFF** ON SW6-2 Select boot device **OFF** OFF = boot from boot PROM ON = boot from boot flash EPROM SW6-3 Reserved, must be OFF **OFF** SW6-4 Watchdog enable switch **OFF** OFF = disabled ON = enabled

Table 11 Default switch settings (cont.)

# 4.5 Front Panel and Connectors

Front panel features

The features of the front panel are described in the following table. For a location diagram see figure 7 "Location diagram of the Base-520(G) (schematic)" on page 22.

Page 28 SPARC/CPCI-52x(G)

Table 12 Front panel features

| Device | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET  | Mechanical reset key: When enabled and toggled it instantaneously affects the SPARC/CPCI-52x(G) by generating a push-button Power On Reset (POR) to the UltraSPARC-IIi. Push-button Power On Reset has the same effect as a Power On Reset from the power supply, with the only difference, that the corresponding status bit (B_POR) in the UltraSPARC-IIi Reset_Control Register is set and the DRAM refresh is not influenced. For information on disabling the reset key, see "SW4-1" on page 27. |

| ABORT  | Mechanical abort key: When enabled and toggled it instantaneously affects the SPARC/CPCI-52x(G) by generating a push-button external initiated reset (XIR). Push-button external initiated reset allows a user-reset (abort) of part of the processor without resetting the whole system. UltraSPARC-IIi sets the B_XIR bit in the Reset_Control Register when a push-button external initiated reset is detected. For information on disabling the abort key, see "SW4-2" on page 27.                |

| DIAG   | Software programmable hexadecimal display for diagnostics.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MODE   | Hexadecimal rotary switch, decoded with 4 bit. Default setting: $F_{16}$ .                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RUN    | CPU status LED: green normal operation  red the processor is halted or reset is active; it starts blinking to signal that the processor did not access the PCI bus for more than 1 second.                                                                                                                                                                                                                                                                                                            |

| ВМ     | CompactPCI busmaster LED: green if the SPARC/CPCI-52x(G) accesses the Compact- PCI as master off otherwise                                                                                                                                                                                                                                                                                                                                                                                            |

Table 12 Front panel features (cont.)

| Device     | Description                                                                                                                                                                           |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0, 1       | 2 software programmable user LEDs.<br>Possible status: off, red, yellow, or green, all colors<br>either permanent or with a blinking frequency of ap-<br>proximately 0.5, 1, or 2 Hz. |

| MIC        | Standard 3.5 mm microphone jack                                                                                                                                                       |

| HDPH       | Standard 3.5 mm headphone jack                                                                                                                                                        |

| ETHERNET   | Standard Twisted-Pair-Ethernet RJ45 connector for 10BaseT/100BaseTX Ethernet.                                                                                                         |

| SCSI       | 50-pin shielded fine-pitch connector for standard SCSI                                                                                                                                |

| SERIAL A+B | 26-pin shielded fine-pitch connector for 2 serial interfaces                                                                                                                          |

| KBD        | Standard 8-pin mini-DIN connector for keyboard and mouse                                                                                                                              |

On-board connectors

In addition to the front-panel connectors, the Base-520(G) provides on-board connectors for memory modules and for the I/O-52x(G), only the Base-520G provides the UPA64S interface connector. An overview of the on-board connectors is shown in the following table.

Table 13 On-board connectors

| Connector description and location        | Connector type                                                       |

|-------------------------------------------|----------------------------------------------------------------------|

| CompactPCI backplane connector J1, J2, J5 | Standard CompactPCI metric,<br>5 row shielded connectors fe-<br>male |

| I/O-52x(G) connector P6                   | 100-pin MBus connector male                                          |

| UPA64S interface connector P7             | 120-pin UPA connector female                                         |

| Memory module connectors P8, P9, P10      | 80-pin SMD connector                                                 |

Available interfaces on J5

The following list shows the available interfaces on the J5 backplane connector. For the J5 connector pinout see Figure 13, "CompactPCI J5 connector pinout," on page 36.

- Ultra Wide SCSI #1

- MII #1 Ethernet interface

Page 30 SPARC/CPCI-52x(G)

- Floppy interface

- Parallel interface

- Serial interface A and B

- Keyboard and mouse

- Audio In:

Stereo Line In.

Stereo Aux#1 In,

Stereo Aux#2 In (or Microphone In as factory option)

• Audio Out:

Stereo Line Out

#### 4.5.1 Audio Interface

The 2 front panel audio interfaces use standard 3.5-mm-phono jacks supporting

- 1 single-ended condenser microphone

- 1 line level signal output, also designed to directly drive low impedance headphones

Table 14 Audio interface signals

| Connector | Headphone     | Microphone |  |

|-----------|---------------|------------|--|

| ↑ Tip     | Left c        | hannel     |  |

| Ring      | Right channel |            |  |

| Shield    | Analog        | g GND      |  |

#### 4.5.2 Ethernet Interfaces

The full duplex Ethernet interface is available at the front panel via a 10BaseT/100BaseTx Twisted-Pair-Ethernet connector.

Table 15 Twisted-Pair-Ethernet #1 connector pinout

| Connector | Pin | Signal |

|-----------|-----|--------|

|           | 1   | TX+    |

|           | 2   | TX-    |

| RJ-45 TPE | 3   | RX+    |

|           | 4   | GND    |

|           | 5   | GND    |

|           | 6   | RX-    |

|           | 7   | GND    |

|           | 8   | GND    |

The Ethernet #1 interface is also accessible at the J5 back panel connector via an MII #1 interface. If Ethernet #1 gets accessed via I/O panel, the front panel connector is normally disabled automatically, for other configurations see the respective jumper settings in the *SPARC/IOBP-520 Installation Guide*. For the J5 connector pinout see Figure 13, "Compact-PCI J5 connector pinout," on page 36.

Page 32 SPARC/CPCI-52x(G)

### 4.5.3 SCSI #1 Connector Pinout

TERMPWR The SCSI #1 interface is single-ended and supports TERMPWR.