# Force Computers cPCI-731 Single Slot CPU Board

In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/63674-1

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

TECHNOLOGY CROUP

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

P/N 211604 Edition 1.2 May 2000

Force Computers GmbH All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless written permission has been granted.

Copyright by Force Computers

#### World Wide Web: www.forcecomputers.com

24-hour access to on-line manuals, driver updates, and application notes is provided via SMART, our SolutionsPLUS customer support program that provides current technical and services information.

# **Headquarters**

# The Americas

# Force Computers Inc.

5799 Fontanoso Way San Jose, CA 95138-1015 U.S.A.

Tel.: +1 (408) 369-6000 Fax: +1 (408) 371-3382 Email: support@fci.com

# **Europe**

#### **Force Computers GmbH**

Prof.-Messerschmitt-Str. 1 D-85579 Neubiberg/München Germany

Tel.: +49 (89) 608 14-0 Fax: +49 (89) 609 77 93 Email: support@force.de

# **Asia**

#### **Force Computers Japan KK**

Shiba Daimon MF Building 4F 2-1-16 Shiba Daimon Minato-ku, Tokyo 105-0012 Japan

Tel.: +81 (03) 3437 3948 Fax: +81 (03) 3437 3968 Email: smiyagawa@fci.com

#### Noti

The information in this document has been carefully checked and is believed to be entirely reliable. Force Computers makes no warranty of any kind with regard to the material in this document, and assumes no responsibility for any errors which may appear in this document. Force Computers reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance, or design.

Force Computers assumes no responsibility for the use of any circuitry other than circuitry which is part of a product of Force Computers GmbH. Force Computers does not convey to the purchaser of the product described herein any license under the patent rights of Force Computers GmbH nor the rights of others. All product names mentioned herein are the trademarks or registered trademarks of their respective companies.

Copyright© 2000 by Force Computers. All rights reserved. This document shall not be reproduced, transmitted, or stored in a retrieval system, nor its contents used for any purpose, without the prior written consent of Force Computers GmbH.

# **Table of Contents**

|         | Usin  | ng This Manual ix |                                                                     |    |  |  |

|---------|-------|-------------------|---------------------------------------------------------------------|----|--|--|

| 1       | Safe  | ety Notes         |                                                                     |    |  |  |

| 2       | Intro | oduction          |                                                                     | 5  |  |  |

|         | 2.1   | Featur            | es and Products                                                     | 5  |  |  |

| 3       | Insta | allation .        |                                                                     | 9  |  |  |

|         | 3.1   | Installa          | ation Prerequisites and Requirements                                | 9  |  |  |

|         | 3.2   | Switch            | Settings                                                            | 4  |  |  |

|         | 3.3   | Front-            | Panel Keys and LEDs1                                                | 5  |  |  |

|         | 3.4   | Front 1           | Panel Connectors 1                                                  | 6  |  |  |

|         | 3.5   | Compa             | nctPCI Interface 1                                                  | 6  |  |  |

|         | 3.6   | BIOS              |                                                                     | 9  |  |  |

|         |       | 3.6.1             | Booting Up and Entering Configuration Utilities (e.g. BIOS Setup) 2 | 1  |  |  |

|         |       | 3.6.2             | The Boot Selection Menu                                             | 2  |  |  |

|         |       | 3.6.3             | Boot Configuration in Setup                                         | :3 |  |  |

|         |       | 3.6.4             | Sample Start-up                                                     | 5  |  |  |

|         |       | 3.6.5             | BIOS Messages                                                       | 6  |  |  |

|         | 3.7   | Upgra             | des and Accessories2                                                | 9  |  |  |

|         |       | 3.7.1             | Installing a PMC Module                                             | 1  |  |  |

| 4       | Har   | dware             |                                                                     | 3  |  |  |

| 4.1 I2C |       | I2C-BUS           |                                                                     | 7  |  |  |

|         |       | 4.1.1             | Module Information I <sup>2</sup> C Bus                             | 7  |  |  |

|         |       | 4.1.2             | System Management I <sup>2</sup> C Bus                              | 7  |  |  |

|         | 4.2   | Board             | Specific Registers                                                  | 9  |  |  |

|         |       | 4.2.1             | ISA-BUS Decoding                                                    | .0 |  |  |

|         |       |                   |                                                                     |    |  |  |

|        | 4.2.1.1                 | BIOS/User Flash Paging                     | . 40 |

|--------|-------------------------|--------------------------------------------|------|

|        | 4.2.1.2                 | Flash Control Register                     | . 40 |

| 4.2.2  | .2 I2C Register         |                                            | . 44 |

| 4.2.3  | Reset and               | Watchdog                                   | . 45 |

|        | 4.2.3.1                 | Reset Types                                |      |

|        | 4.2.3.2                 | NMI/Reset Sources                          | . 45 |

|        | 4.2.3.3                 | Reset Control Register 1                   | . 47 |

|        | 4.2.3.4                 | Reset Control Register 2                   | . 49 |

|        | 4.2.3.5                 | Non Maskable Interrupt NMI                 | . 50 |

|        | 4.2.3.6                 | NMI Control Register                       | . 51 |

|        | 4.2.3.7                 | Reset/NMI Status Register                  |      |

|        | 4.2.3.8                 | Software NMI/Reset                         | . 53 |

|        | 4.2.3.9                 | Software NMI/Reset Register                | . 54 |

|        | 4.2.3.10                | Watchdog                                   | . 54 |

|        | 4.2.3.11                | Watchdog Retrigger                         | . 54 |

|        | 4.2.3.12                | Watchdog Timer                             | . 54 |

|        | 4.2.3.13                | Watchdog Timer Register                    | . 56 |

| 4.2.4  | PCI Conf                | iguration and Interrupt, Operating Modes   | . 57 |

|        | 4.2.4.1                 | Interrupt and Enum Service Mode            | . 57 |

|        | 4.2.4.2                 | Signal Direction                           | . 57 |

|        | 4.2.4.3                 | Interrupt Mask                             | . 58 |

|        | 4.2.4.4                 | Interrupt Routing                          | . 58 |

|        | 4.2.4.5                 | PCI Control Register                       |      |

|        | 4.2.4.6                 | PCI Interrupt Control Register             | . 63 |

| 4.2.5  | Geograph                | ical Addressing and Rear Transition Module | . 65 |

|        | 4.2.5.1                 | Geographical Address                       | . 66 |

|        | 4.2.5.2                 | Rear Transition Module Detection           | . 66 |

|        | 4.2.5.3                 | Geographical Address Register              | . 66 |

| 4.2.6  | Hot Swap                | LED/Switch and ENUM                        | . 66 |

|        | 4.2.6.1                 | Hot Swap ENUM Register                     | . 66 |

| 4.2.7  | LEDs                    |                                            | . 68 |

|        | 4.2.7.1                 | LED Control Register                       | . 68 |

| 4.2.8  | Additiona               | ıl Features                                | . 69 |

|        | 4.2.8.1                 | Register Lock and Page Function            | . 69 |

|        | 4.2.8.2                 | Version Register                           | . 70 |

| 4.2.9  | Spare Cor               | nfiguration Switches                       | . 71 |

| 4.2.10 | PMC Slot Identification |                                            |      |

| 4.2.11 |                         | Monitor                                    |      |

|        |                         |                                            |      |

Page vi PENT/CPCI-731

# **List of Tables and Figures**

| Page                                                            | Tab./Fig. |

|-----------------------------------------------------------------|-----------|

| History of Manual Publicationxiii                               | Tab. a    |

| Fonts, Notations and Conventions                                | Tab. b    |

| Specification of the PENT/CPCI-731                              | Tab. 1    |

| Product Nomenclature                                            | Tab. 2    |

| Excerpt from the PENT/CPCI-731 Ordering Information             | Tab. 3    |

| Environmental Requirements of the PENT/CPCI-731                 | Tab. 4    |

| Typical 5 V and 3.3 V Power Requirements                        | Tab. 5    |

| Location Diagram of the PENT/CPCI-731 (Schematic)               | Fig. 1    |

| PENT/CPCI-731 Switch Settings                                   | Tab. 6    |

| KBD/MS – Keyboard and Mouse Connector Pinout                    | Fig. 2    |

| COM1 Connector Pinout                                           | Fig. 3    |

| CompactPCI J3 Connector Pinout                                  | Fig. 4    |

| CompactPCI J4 Connector Pinout                                  | Fig. 5    |

| CompactPCI J5 Connector Pinout                                  | Fig. 6    |

| A Sample Setup Screen Showing the Boot Configuration Options 24 | Fig. 7    |

| Sample Start-up Screen                                          | Fig. 8    |

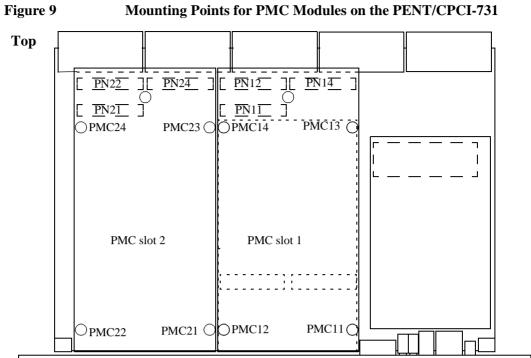

| Mounting Points for PMC Modules on the PENT/CPCI-731            | Fig. 9    |

| Block Diagramm                                                  | Fig. 10   |

| I/O Map                                                         | Tab. 7    |

| Memory Map                                                      | Fig. 11   |

| Module Information I <sup>2</sup> C bus                         | Tab. 8    |

| System Management I <sup>2</sup> C Bus                          | Tab. 9    |

| Register on Page 1 Overview                                     | Tab. 10   |

| Register on Page 2 Overview                                     | Tab. 11   |

| Independent Register Overview 3                                 | Tab. 12   |

| Flash Device Address Mapping                                    | Fig. 12   |

| Flash Control Register                                          | Tab. 13   |

| I2C Register                                                    | Tab. 14   |

| NMI/Reset Sources                                               | Tab. 15   |

| Possible NMI/Reset Configurations                               | Tab. 16   |

| Reset Control Register 1                                        | Tab. 17   |

| Reset Control Register 2                                        | Tab. 18   |

| NMI Control Register                                            | Tab. 19   |

| Reset/NMI Status Register                                       | Tab. 20   |

| Software NMI/Reset Register                                     | Tab. 21   |

| Watchdog Timer         55                                       | Tab. 22   |

| Watchdog Timer Register                                         | Tab. 23   |

| Signal Direction                                                | Tab. 24   |

| PCI Control Register                                            | Tab. 25   |

PENT/CPCI-731 Page vii

# **Tables and Figures**

|                                                                 | Page | Tab./ | Fig. |

|-----------------------------------------------------------------|------|-------|------|

| PCI Interrupt Control Register                                  | 63   | Tab.  | 26   |

| TM_PRNT Signal                                                  | 66   | Tab.  | 27   |

| Geographical Address Register                                   | 66   | Tab.  | 28   |

| Hot Swap ENUM Register                                          | 67   | Tab.  | 29   |

| LED Control Register                                            | 68   | Tab.  | 30   |

| Lock and Page Register                                          | 69   | Tab.  | 31   |

| Flag Register                                                   |      | Tab.  | 32   |

| Version Register                                                | 71   | Tab.  | 33   |

| Configuration Switches                                          | 71   | Tab.  | 34   |

| Busmode/GPIO Routing                                            | 72   | Tab.  | 35   |

| General Purpose I/O Registers in Intel21150                     | 72   | Tab.  | 36   |

| Monitored Board Voltages versus Hardware Monitor Voltage Inputs | 73   | Tab.  | 37   |

| Hardware Monitor Base Address                                   | 73   | Tab.  | 38   |

Page viii PENT/CPCI-731

# **Using This Manual**

This section does not provide information on the product, but on standard features of the manual itself:

- · Its structure

- Special layout conventions

- Related documents

#### **Audience of the Manual**

This *Reference Guide* is intended for hard- and software developers installing and integrating the PENT/CPCI-731 into their systems.

#### Overview of the Manual

This *Reference Guide* provides a comprehensive hardware and software guide to your board.

*Note:* Please take a moment to examine the "Table of Contents" to see how this documentation is structured. This will be of value to you when looking for information in the future.

#### It includes:

- Brief overview of the PENT/CPCI-731: see section 2 "Introduction" on page 5.

- Installation instructions for powering up the board: see section 3 "Installation" on page 9. It includes the default configuration (switches and the like), initialization, connector pinouts, and the BIOS details.

- Block diagram relating the most important components and a description of the PENT/CPCI-731 specific registers: section 4 "Hardware" on page 33.

**Data Sheets**

It is assumed that the PENT/CPCI-731 is integrated into systems at the operating system level. Therefore, no data sheets are provided in this *Reference Guide*. Nevertheless, all data sheets of the most important board components are listed below. They can be found on the respective company's webpage.

- BIOS flash 1Mx8, 28F008S5, 28F800B5 (developer.intel.com)

- CPU Intel Pentium II

Intel Pentium II Processor Mobile Module: Mobile Module Connector 2 (MMC-2) (developer.intel.com)

Intel Architecture Software Developer's Manual; Volume 1: Basic Architecture, Volume 2: Instruction Set Reference Manual, Volume 3: System Programming Guide

- EIDE, PCI-to-ISA bridge, USB 82371AB (82371EB) (developer.intel.com)

- Ethernet 82559 (developer.intel.com)

- Hardware monitor W83781D (http://www.winbond.com)

- Host-to-PCI bridge 82443BX (developer.intel.com)

- IDE flash disk SanDisk FlashChipset, SDFCSTB-128-366 (www.sandisk.com)

- I<sup>2</sup>C bus "The I<sup>2</sup>C-bus and how to use it (including specifications)" (http://www.philips.com)

- Keyboard, PS2 mouse, COM1, COM2, LPT1, floppy National PC87309 SuperI/O (www.national.com)

- PCI-to-PCI bridge 21150 (developer.intel.com)

- PCI-to-PCI bridge 21554 (developer.intel.com)

- Synchronous DRAM Hitachi/Micron/Mitsubishi 8Mx8 (M5M4V64S30A) (www.halsp.hitachi.com)

PENT/CPCI-731

Table a History of Manual Publication

| Edition | Date          | Description                                                                                                                                                               |

|---------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | December 1999 | First Print                                                                                                                                                               |

| 1.1     | January 2000  | Corrected Forced Air Flow in table 4 "Environmental Requirements of the PENT/CPCI-731" on page 9; corrected table 19 "NMI Control Register" on page 51; editorial changes |

| 1.2     | May 2000      | Corrected IRQ settings in table 29 "Hot Swap ENUM Register" on page 67; changed SW2-3 to ON in table 6 "PENT/CPCI-731 Switch Settings" on page 14; editorial changes      |

# Table b Fonts, Notations and Conventions

| Notation                | Description                                                                                                                                                                          |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | All numbers are decimal numbers except when used with the following notations:                                                                                                       |

| 0000.0000 <sub>16</sub> | Typical notation for hexadecimal numbers (digits are 0 through F), e.g. used for addresses and offsets.  Note the dot marking the 4th (to its right) and 5th (to its left) digit.    |

| 00008                   | Same for octal numbers (digits are 0 through 7)                                                                                                                                      |

| 00002                   | Same for binary numbers (digits are 0 and 1)                                                                                                                                         |

| Program                 | Typical character format used for names, values, and the like. It is used to indicate when to type literally the same word. Also used for on-screen output.                          |

| Variable                | Typical character format for words that represent a part of a command, a programming statement, or the like, and that will be replaced by an applicable value when actually applied. |

## Icons for Ease of Use: Safety Notes and Tips & Tricks

There are three levels of safety notes used in this manual which are described below in brief by displaying a typical layout example.

Be sure to always read and follow the safety notes of a section first – before acting as documented in the other parts of the section.

**Danger**

Dangerous situation: injuries to people and severe damage to objects possible.

Caution

Possibly dangerous situation: no injuries to people but damage to objects possible.

*Note:* No danger encountered. Pay attention to important information marked using this layout.

Page xii PENT/CPCI-731

# 1 Safety Notes

This section provides safety precautions to follow when installing, operating, and maintaining the PENT/CPCI-731. For your protection, follow all warnings and instructions found in the following text.

## General

This *Reference Guide* provides the necessary information to install and handle the PENT/CPCI-731. As the product is complex and its usage manifold, we do not guarantee that the given information is complete. In case you need additional information, ask your Force Computers representative.

The PENT/CPCI-731 has been designed to meet the standard industrial safety requirements. It must not be used except in its specific area of office telecommunication industry and industrial control.

Only personnel trained by Force Computers or persons qualified in electronics or electrical engineering are authorized to install, uninstall or maintain the PENT/CPCI-731. The information given in this manual is meant to complete the knowledge of a specialist and must not be taken as replacement for qualified personnel.

Make sure that contacts and cables of the board cannot be touched while the board is operating.

## **Hot Swap**

The PENT/CPCI-731 provides hot-swap support, i.e. it may be installed in or removed from a powered system supporting hot swap. Never install or uninstall the board in a system under hot-swap conditions unless the hot-swap or high-availability platform is used and the system documentation explicitly includes appropriate guidelines. For detailed information on the hot-swap support and the relevant safety notes, see "Hot Swap" on page 12. All of the following safety notes refer to the installation and uninstallation of the board in a non-powered system.

## **Installation**

Electrostatic discharge and incorrect board installation and uninstallation can damage circuits or shorten their life. Therefore:

- Before installing or uninstalling the board, read section 3 "Installation" on page 9.

- Before touching integrated circuits, ensure that you are working in an ESD safe environment.

- Before installing or uninstalling the board in a CompactPCI rack:

- Check all installed boards for steps that have to be taken before turning off the power.

- Take those steps.

- Finally turn off the power.

- When plugging the board in or removing it, do not press on the front panel but use the handles.

- Before installing or uninstalling an additional device or module, read the respective documentation.

- Ensure that the board is connected to the CompactPCI backplane via all assembled connectors and that power is available on all power pins.

## **CompactPCI**

The PENT/CPCI-731 is a peripheral (or non host) board. Therefore:

- Plug the PENT/CPCI-731 only into a peripheral slot of a CompactPCI system.

- Never plug the PENT/CPCI-731 into another slot of a Compact-PCI system or into a system rack other than a CompactPCI system.

- Ensure that the board is connected to the CompactCI backplane via all its connectors, and that power is available on all power pins.

- When operating the board in areas of strong electro-magnetic radiation, ensure that the board is:

- Bolted on the CompactPCI rack

- Shielded by enclosure

# Hard Disk Limitation

If the PENT/CPCI-731/HD-AccKit is installed on the PENT/CPCI-731, the operating temperature and the shock and vibration values are limited by the hard disk environmental requirements. For details, refer to the Installation Guide of the PENT/CPCI-731/HD-AccKit.

# Power Consumption

The total maximal power consumption per PMC slot at  $\pm 1.12$  V, 5 V, and 3.3 V level must not exceed 7.5 W (total over all used voltages).

Page 2 PENT/CPCI-731

## **Operation**

While operating the board ensure that the environmental and power requirements as given in table 4 "Environmental Requirements of the PENT/CPCI-731" on page 9 and table 5 "Typical 5 V and 3.3 V Power Requirements" on page 10 are met.

#### **EMC**

- If boards are integrated into open systems, always cover empty slots.

- The front panel of the PENT/CPCI-731 provides one cutout for a PMC module. If the board is shipped without the module installed, the front-panel cutout is covered by a blind panel to ensure proper EMC shielding. To ensure proper EMC shielding, always operate the PENT/CPCI-731 with the blind panel or with a PMC module installed.

# **Expansion**

- Check the total power consumption of all components installed (see the technical specification of the respective components). For the total power consumption of the PENT/CPCI-731, see table 5 "Typical 5 V and 3.3 V Power Requirements" on page 10.

- Ensure that any individual output current of any source stays within its acceptable limits (see the technical specification of the respective source).

- Only replace components or system parts with those recommended by Force Computers. In case you use components other than those recommended by Force Computers, you are fully responsible for the impact on EMC/Safety and the eventually changed functionality of the product.

#### **IOBP**

The IOBP-CPCI-731 is especially designed for the base board of the PENT/CPCI-731. Do not use any other I/O panels on the PENT/CPCI-731.

#### **Environment**

Always dispose of used batteries and/or old boards according to your country's legislation.

#### **Battery**

The board is designed to be maintenance-free. However, note that a Lithium battery is installed on the board. The battery provides a data retention of five years summing up all periods of actual battery use. Therefore, Force Computers assumes that there usually is no need to exchange the Lithium battery except for example in the case of long-term spare part handling.

- Incorrect exchange of Lithium batteries can result in a hazardous explosion.

- Exchange the battery before five years of actual battery use have elapsed.

- Exchanging the battery always results in data loss of the devices which use the battery as power backup. Therefore, back up affected data before exchanging the battery.

- Always use the same type of Lithium battery as is already installed.

- If the battery is covered by a PMC module on slot 1 or a memory module, the module must be removed first.

- Use an appropriate tool to remove the battery from its holder to avoid possible damage to the PCB or the battery holder.

- When installing the new battery ensure that the '+' on top of the battery stays at the top and therefore is visible when viewing the board from its component side. If necessary reinstall the PMC or memory module in its correct position.

Page 4 PENT/CPCI-731

# 2 Introduction

The PENT/CPCI-731 is a 6U CompactPCI computer based on the Intel Pentium II/III CPU and is a CompactPCI non host or I/O board. It requires the space of one slot. All PENT/CPCI-731 PCI buses are 32-bit wide and operate at 33 MHz PCI bus frequency.

The PENT/CPCI-731 is designed to run with Windows NT Version 4.0. or higher, VxWorks and LynxOS.

# 2.1 Features and Products

The PENT/CPCI-731 features include:

- Mobile module based on Intel Pentium II/III CPU

- CompactPCI I/O slot functionality

- Inrush current protection and full hot swap support

- Two PMC slots for I/O extensions, both supporting the front panel I/O and I/O via CompactPCI connector

- Synchronous DRAM (SDRAM) with ECC support running at 66/100 MHz clock frequency

- 10/100 BaseT Ethernet available via CompactPCI connector (IOBP-CPCI-731)

- On-board 16 MByte IDE flash disk

- One MByte flash BIOS, 8-bit wide

- Two RS-232 serial interfaces with 115 KBaud maximum data rate and 16-byte deep FIFO

- COM1 available on front-panel and CompactPCI connector J3

- COM2 available on CompactPCI connector J3

- One IEEE 1284 compatible parallel interface LPT with ECP (Extended Capabilities Port) and EPP (1.7/1.9) support available at the CompactPCI connector

- Two USB interfaces, available at CompactPCI connector J3

- Floppy controller, compatible with PC8477 which contains a superset of NECuPD72065B and N82077, accessible via CompactPCI connector J4

- IDE controller with primary and secondary EIDE support, the primary IDE interface accessible via on-board connector, the primary and secondary via CompactPCI connector J4 and J5

- Motorola 146818 compatible real time clock and CMOS RAM for storing factory settings, both RTC and RAM with battery backup

- Two 82C37A compatible DMA controllers

- Two 82C29 compatible interrupt controllers

- 8254 compatible 3-channel timer

- PS/2 keyboard and mouse controller, 8042 compatible, available on front-panel and CompactPCI connector J5

- Software-controllable, scalable watchdog, which controls the CPU activity and causes a RESET or an NMI in case of malfunction

- Program-readable vintage registers for board information protocol (BIP)

- Additional front-panel features include:

- RESET key which can be disabled via switch or software, the RESET signal is available on the CompactPCI connector.

- Two LEDs for network link and activity, LED for signaling access to devices connected to IDE, latter both also user available for user applications

- 2x PMC front-panel I/O

Page 6 PENT/CPCI-731

Factory Options, Upgrades and Accessories The PENT/CPCI-731 has been designed to cost-effectively support a wide range of hardware requirements. Therefore a number of factory options and accessory kits are available. These are the following:

- Intel Pentium II based mobile module with 266/333 MHz, Pentium III based mobile module with 500 MHz internal frequency

- On-board SDRAM capacity: up to 256 MByte

- On-board IDE flash disk and its capacity: 16 MByte

- On-board 2,5" IDE hard disk drive

- PMC VGA card

- Memory module: up to 512MByte capacity.

For a list of upgrades and accessories, see table 3 "Excerpt from the PENT/CPCI-731 Ordering Information" on page 8. The upgrades and accessories available depend on the variant of the PENT/CPCI-731 under consideration.

The following table gives an excerpt from the PENT/CPCI-731 specification:

Table 1

Specification of the PENT/CPCI-731

| Additional Features                                                                    | Optional on-board IDE flash disk, 16 MByte, PIO mode 1                  |  |  |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|

| <b>Board Form Factor</b>                                                               | 6HE, 4TE                                                                |  |  |

| CompactPCI Interface                                                                   | 32 bit with 33 MHz, PCI Specification Rev. 2.1., 3.3/5 V level          |  |  |

| EIDE                                                                                   | PIO mode 4 via rear I/O                                                 |  |  |

| <b>Environmental conditions</b>                                                        | See table 4 "Environmental Requirements of the PENT/CPCI-731" on page 9 |  |  |

| Ethernet Twisted-pair, 10/100 Mbit, according to IEEE802.3, v.                         |                                                                         |  |  |

| Firmware Phoenix BIOS, see section 3.6 "BIOS" on page 19                               |                                                                         |  |  |

| PC-AT floppy, e.g. 360 KByte, 720 KByte, 1.2 M<br>1.44 MByte, 2.88 MByte, via rear I/O |                                                                         |  |  |

| <b>Inrush Current Protection</b>                                                       | Protected/switched: +5 V, +3.3 V, switched: VIO, +12 V, -12 V           |  |  |

| Keyboard/Mouse Port                                                                    | PS/2 compatible                                                         |  |  |

| L2 Cache                                                                               | 512 KByte/256 KByte depending on Processor                              |  |  |

| Main Memory  Up to 768 MByte (depending on selected memory option ECC                  |                                                                         |  |  |

| Parallel I/O                                                                           | IEEE 1284, ECP, EPP modes via rear I/O                                  |  |  |

Table 1

Specification of the PENT/CPCI-731 (cont.)

| PMC Slots                | 2 for 32 bit with 33 MHz PMC modules, PCI Specification Rev. 2.1, 5 V and 3.3 V level (assembly option) |  |

|--------------------------|---------------------------------------------------------------------------------------------------------|--|

| <b>Power Consumption</b> | See table 5 "Typical 5 V and 3.3 V Power Requirements" on page 10                                       |  |

| Processor                | Pentium II with 266/333 MHz or higher, Pentium III with 500 MHz                                         |  |

| Serial I/O               | 2x, RS232 level, max. rate 115.2 KBaud                                                                  |  |

| USB Port                 | 2x, via rear I/O                                                                                        |  |

Data Sheets For a list of data sheets see the front matter of this manual.

Ordering Information

Due to the flexible design, the PENT/CPCI-731 is available in several variants as well as in several memory and speed options. Consult your local sales representative to confirm availability of specific combinations. The following table explains the general product nomenclature.

Table 2 Product Nomenclature

| PENT/CPCI-731/ddd-ppp-Lccc-u     |                                      |                        |                          |  |

|----------------------------------|--------------------------------------|------------------------|--------------------------|--|

| ddd = MByte DRAM                 | ppp = Processor type                 | Lccc = 2nd level cache | u = MByte IDE flash disk |  |

| 128 =128 MByte<br>256 =256 MByte | 333 =<br>Intel Pentium II<br>333 MHz | L512 = 256 KByte       | 16 = 16MByte             |  |

The following table is an excerpt from the PENT/CPCI-731 data sheet. For current information ask your local Force Computers representative.

Table 3 Excerpt from the PENT/CPCI-731 Ordering Information

| <b>Product Name</b> | Description                                                                                        |  |

|---------------------|----------------------------------------------------------------------------------------------------|--|

| PENT/CPCI-731/      |                                                                                                    |  |

| /128-266-L512-0     | Intel Pentium II 266 MHz with 128MByte main memory, 512 KByte 2nd level cache, no flash disk       |  |

| /256-333-L256-16    | Intel Pentium II 333 MHz with 256MByte main memory, 256 KByte 2nd level cache, 16 MByte flash disk |  |

Page 8 PENT/CPCI-731

# 3 Installation

Before installing or dismounting the board, refer to section 1 "Safety Notes" on page 1.

# 3.1 Installation Prerequisites and Requirements

*Note:* Before powering up check the items described in the following list.

- Check this section for installation prerequisites and requirements concerning the PENT/CPCI-731

- Check the consistency of the current switch settings (see section 3.2 "Switch Settings" on page 14)

- Check section 3.7 "Upgrades and Accessories" on page 29 for installation prerequisites and requirements concerning PENT/CPCI-731 accessories, like e.g. a PMC module

#### Caution

If the PENT/CPCI-731/HD-AccKit is installed on the PENT/CPCI-731, operating temperature, shock and vibration values are limited by the hard disk environmental requirements. For details, refer to the Installation Guide of the PENT/CPCI-731/HD-AccKit.

Table 4

#### **Environmental Requirements of the PENT/CPCI-731**

|                                                   | Operating                         | Non-operating                     |

|---------------------------------------------------|-----------------------------------|-----------------------------------|

| Temperature                                       | 0°C to +55°C                      | -40°C to +85°C                    |

| Forced Air Flow (in LFM = Linear Feet per Minute) | 300 LFM                           | _                                 |

| <b>Temperature Change</b>                         | +/- 0.5°C/min                     | +/- 1°C/min                       |

| Relative Humidity                                 | 5% to 95% non-condensing at +40°C | 5% to 95% non-condensing at +40°C |

| Altitude                                          | -300 m to +3,000 m                | -300 m to +13,000 m               |

Table 4 Environmental Requirements of the PENT/CPCI-731 (cont.)

|              | Operating          | Non-operating                                 |

|--------------|--------------------|-----------------------------------------------|

| Vibration    | 2 mm amplitude     | 5 mm amplitude                                |

| 10 to 15 Hz  | 2 g                | 5 g                                           |

| 15 to 150 Hz |                    |                                               |

| Shock        | 5 g/11 ms halfsine | 15 g/11 ms halfsine                           |

| Free Fall    | 100 mm/3 axis      | 1,200 mm/all edges and corners (packed state) |

These environmental values must be tested and proven in the used system configuration. These conditions refer to the surroundings of the board within the user environment. Operating temperatures refer to the temperature of the air circulating around the board and not to the actual component temperature. To ensure that the operating conditions are met, forced air cooling is required within the chassis environment.

Power Requirements The board's +/- 12 V power requirements depend on the PMC modules installed. The PENT/CPCI-731 provides a limited current at the PMC supply pins.

#### Caution

The total maximal power consumption per PMC slot at  $\pm 1.12$  V, 5 V, and 3.3 V level must not exceed 7.5 W (total over-all used voltages).

Typical 5 V and 3.3 V power requirements of the PENT/CPCI-731 are given in the following table:

# Table 5 Typical 5 V and 3.3 V Power Requirements

| PENT/CPCI-731 (no Memory Board, PMC Module Installed) | +5 V  | +3.3 V |

|-------------------------------------------------------|-------|--------|

| PENT/CPCI-731/256-333-L256-16                         | 1.8 A | 1.7 A  |

Keyboard, Mouse, USB Make sure that the lengths of the keyboard/mouse cable and of the USB cable do not exceed 3m each and that the two cables are installed apart from other cables.

Floppy Disk Connector The floppy disk connector is assembled to provide BIOS field upgrade ability of the PENT/CPCI-731 if no IOBP-CPCI-731 is available.

Page 10 PENT/CPCI-731

**IDE Devices**

The PENT/CPCI-731 provides a primary and a secondary IDE interface for connecting up to four IDE devices. An on-board flash disk may be provided at the primary IDE interface as a factory option (see below). A hard disk can be connected to the primary IDE port via the on-board connector using the PENT/CPCI-731/HD-AccKit. If two devices are connected to an IDE interface, one device has to be the master, the other has to be the slave. If only one drive is connected to an IDE interface, that device must be set as master.

Due to the nature of IDE some further limitations apply:

- There can be up to three connectors on each ribbon cable connected to the primary or secondary PENT/CPCI-731 IDE interface. Thereby, up to two IDE devices per ribbon cable can be connected to a PENT/CPCI-731 IDE interface.

- Never connect more than two devices to the primary or secondary PENT/CPCI-731 IDE interface.

- Before connecting IDE devices to an IDE interface, do the following:

- Check for IDE devices already connected to the IDE interface.

- Decide which IDE device should be master and which should be slave. If only one IDE device is connected to an IDE interface, this device must be master.

- Configure the device which you want to connect.

- Ribbon cable length must not exceed 0.45 m (18 inches).

At the first boot after connecting an IDE device use the according menu in Setup to modify the BIOS parameters appropriately (see section 3.6.1 "Booting Up and Entering Configuration Utilities (e.g. BIOS Setup)" on page 21 <F2>).

If the PENT/CPCI-731 is provided without on-board flash disk, up to four hard disks can be connected to the PENT/CPCI-731 via the IOBP-CPCI-731 and on-board connector.

IDE Flash Disk (Factory Option)

If the PENT/CPCI-731 is provided with an on-board flash disk connected to its primary IDE interface, a hard disk can be connected as second device to the primary IDE interface. This can be done by either assembling the PENT/CPCI-731/HD-AccKit or via an IOBP-CPCI-731 board. The flash disk can be enabled or disabled via switch SW1-3 (see "Switch Settings" on page 14).

If the flash disk is enabled and a second device is connected to the primary IDE interface, any of the two devices can be the master while the other is the slave. The flash disk is set to master or slave mode via switch SW1-4. If the flash disk is disabled, the second device at the primary IDE interface must be the master.

For the IDE flash disk a data endurance of 300,000 erase/program cycles per logical sector is guaranteed.

**EMC**

The PENT/CPCI-731 front panel provides two cutouts to enable the installation of PMC modules. If the PENT/CPCI-731 is shipped without modules installed, the front-panel cutouts are covered by blind panels to ensure proper EMC shielding.

*Note:* To ensure proper EMC shielding, check the items described in the following list.

- Always operate a PENT/CPCI-731:

- With the blind panels for the PENT/CPCI-731 front panel installed

- With the modules installed

- If the PENT/CPCI-731 is upgraded with PMC modules, ensure that the blind panels are stored in a safe place to be used again when uninstalling the upgrades.

Hot Swap

The PENT/CPCI-731 provides full Hot Swap functionality. This, however, does only cover the CPCI interface of connector J1 and J2. If I/O devices are used at the connectors J3, J4 and J5 (e.g. via IOBP-CPCI-731), refer to the respective documentation of these signals and interfaces for hot swap capability.

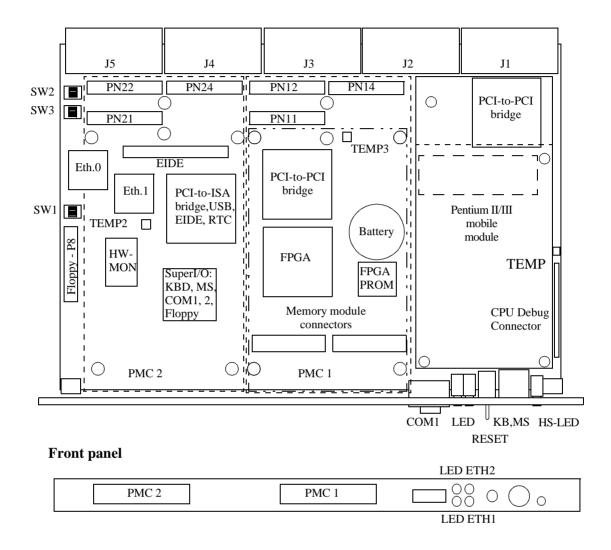

Location Overview Figure 1 highlights the location of the important base board components.

Page 12 PENT/CPCI-731

Figure 1 Location Diagram of the PENT/CPCI-731 (Schematic)

Top

# 3.2 Switch Settings

The PENT/CPCI-731 is configurable via three micro switches. The switches are located on the left-hand side of the base board seen from the front panel (see "Location Diagram of the PENT/CPCI-731 (Schematic)" on page 13).

Table 6

PENT/CPCI-731 Switch Settings

| Name and Default<br>Setting |              | Description                                                                                                         |  |  |

|-----------------------------|--------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| ON<br>1                     | SW1-1<br>OFF | I2C USER EEPROM write protection OFF = Write protected ON = Write enabled                                           |  |  |

| 3                           | SW1-2<br>OFF | Boot Block write protection  OFF = Write enabled  ON = Write protected                                              |  |  |

|                             | SW1-3<br>OFF | Flash disk enable (see "IDE Flash Disk (Factory Option)" on page 11)  = Flash disk disabled ON = Flash disk enabled |  |  |

|                             | SW1-4<br>OFF | Flash Disk Master/Slave (boot enable) OFF = Primary IDE slave ON = Primary IDE master                               |  |  |

| ON                          | SW2-1<br>OFF | FPGA Download source OFF = via EEPROM ON = via Download Cable                                                       |  |  |

| 3 0 0 0                     | SW2-2<br>OFF | FPGA Init Select OFF = Lower 64KB ON = Upper 64KB                                                                   |  |  |

|                             | SW2-3<br>ON  | 12V Supervising OFF = Enabled ON = Disabled                                                                         |  |  |

|                             | SW2-4<br>OFF | Reset Key OFF = Enabled ON = Disabled                                                                               |  |  |

Page 14 PENT/CPCI-731

Table 6 PENT/CPCI-731 Switch Settings (cont.)

| Name and Default<br>Setting |              | Description       |  |

|-----------------------------|--------------|-------------------|--|

| ON                          | SW3-1<br>OFF | FPGA Spare Switch |  |

|                             | SW3-2<br>OFF | FPGA Spare Switch |  |

| 4                           | SW3-3<br>OFF | FPGA Spare Switch |  |

|                             | SW3-4<br>OFF | FPGA Spare Switch |  |

# 3.3 Front-Panel Keys and LEDs

The following front-panel keys and LEDs are provided on the PENT/CPCI-731:

- RESET Key

Mechanical reset key: When enabled via switch SW2-4 (see "Switch Settings" on page 14) and toggled, it instantaneously affects the system board by generating a reset. The reset behavior of the board (reset source, destructive-, non destructive reset) is fully configurable via registers (refer to "Reset and Watchdog" on page 45 for details). A reset is performed when the RESET key is pushed to the active position. RESET is held active until the key is back in the inactive position. For information on how to disable the key, see "Switch Settings" on page 14.

- LED 1,2

Per default the U1 signals Board Power and U2 signals IDE activity. These LEDs are fully software programmable by means of a register. Possible LED status: Green, red, or off.

- LED ETH1

Ethernet 1 active, link LED: signals status of Ethernet Interface 1. Possible LED status:

- LED is illuminated when properly connected to an Ethernet Network.

- LED flashes during network access.

- LED ETH2

Ethernet 2 active, link LED: signals status of ethernet interface 2. Possible LED status:

- LED is illuminated when properly connected to an Ethernet Network.

- LED flashes during network access.

#### 3.4 **Front Panel Connectors**

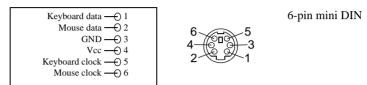

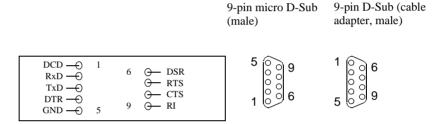

In addition to its CompactPCI interface (see section 3.5 "CompactPCI Interface" on page 16) the PENT/CPCI-731 provides one keyboard or mouse connector and one serial interface connector. The following figures show the pinouts.

Figure 2 KBD/MS - Keyboard and Mouse Connector Pinout

Figure 3 **COM1 Connector Pinout**

#### **CompactPCI Interface** 3.5

Hot Swap

The PENT/CPCI-731 is a CompactPCI system peripheral board. The PCI bus supports a 32-bit data bus width with a frequency of 33 MHz.

The interfaces available on the CompactPCI interface can be routed to interface-dependent standard connectors via the IOBP-CPCI-731 (see page 19).

Signaling Level

Due to the hot swap capability and compliance to the CompactPCI Hot Swap Specification 2.1, the PENT/CPCI-731 board can only be used in a 5V system. A 5V key within the CPCI P1 Connector prevents the board from being installed in a non 5V System.

The PENT/CPCI-731 provides full hot swap functionality signals of the CPCI connectors J1 and J2. If I/O devices are used at the connectors J3. J4 and J5 (e.g. via IOBP-CPCI-731), refer to the respective documenta-

tion for hot swap capability.

Page 16 PENT/CPCI-731

J1 and J2

The J1 and J2 connectors implement the CompactPCI 64-bit connector pinout as specified by the CompactPCI specification. Therefore, this manual only documents the pinout of the J3, J4 and J5 connectors.

J3

The following interfaces are available via the PENT/CPCI-731 Compact-PCI J3 connector (the designations used in the following pinout are given in brackets):

- USB 1 (USB1), USB 2 (USB2), COM 1 (COM1), COM 2 (COM2)

- PMC Slot 1 I/O signals (PMC1IO)

Figure 4 CompactPCI J3 Connector Pinout

| A         | В         | C                         | D                    | E         |

|-----------|-----------|---------------------------|----------------------|-----------|

| USB2 P+   | USB2 P-   | USB1 P+ — 19              | O → USB1 P-          | reserved  |

| COM1 DTR  | COM1 RI   | COM2 DTR <del>─</del> 18  | O COM2 RI            | reserved  |

| COM1 DSR  | COM1 DCD  | COM2 DSR <del>→</del> 17  | O COM2 DCD           | reserved  |

| COM1 CTS  | COM1 TXD  | COM2 CTS <del>−</del> 16  | ⊙— COM2 TXD          | reserved  |

| COM1 RTS  | COM1 RXD  | COM2 RTS <del>→</del> 15  | ⊙— COM2 RXD          | reserved  |

| 3.3 V     | 3.3 V     | 3.3 V — 14                | ↓ <u></u> 5V         | 5V        |

| PMC1IO-05 | PMC1IO-04 | PMC1IO-03 — 13            | 3 → PMC1IO-02        | PMC1IO-01 |

| PMC1IO-10 | PMC1IO-09 | PMC1IO-08 <del>→</del> 12 | 2 <u>→ PMC1IO-07</u> | PMC1IO-06 |

| PMC1IO-15 | PMC1IO-14 | PMC1IO-13 <del>─</del> 11 | → PMC1IO-12          | PMC1IO-11 |

| PMC1IO-20 | PMC1IO-19 | PMC1IO-18 <del>─</del> 10 | → PMC1IO-17          | PMC1IO-16 |

| PMC1IO-25 | PMC1IO-24 | PMC1IO-23 <del>─</del> 9  | → PMC1IO-22          | PMC1IO-21 |

| PMC1IO-30 | PMC1IO-29 | PMC1IO-28 <del>─</del> 8  | — PMC1IO-27          | PMC1IO-26 |

| PMC1IO-35 | PMC1IO-34 | PMC1IO-33 <del>→</del> 7  | — PMC1IO-32          | PMC1IO-31 |

| PMC1IO-40 | PMC1IO-39 | PMC1IO-38 <del>−</del> 6  | — PMC1IO-37          | PMC1IO-36 |

| PMC1IO-45 | PMC1IO-44 | PMC1IO-43 <del>─</del> 5  | — PMC1IO-42          | PMC1IO-41 |

| PMC1IO-50 | PMC1IO-49 | PMC1IO-48 <del></del> 4   | — PMC1IO-47          | PMC1IO-46 |

| PMC1IO-55 | PMC1IO-54 | PMC1IO-53 <del>─</del> 3  | — PMC1IO-52          | PMC1IO-51 |

| PMC1IO-60 | PMC1IO-59 | PMC1IO-58 — 2             | — PMC1IO-57          | PMC1IO-56 |

| GND       | PMC1IO-64 | PMC1IO-63 — 0 1           | — PMC1IO-62          | PMC1IO-61 |

|           |           |                           |                      |           |

J4

The following interfaces are available via the PENT/CPCI-731 Compact-PCI J4 connector (the designations used in the following pinout are given in brackets):

- Primary IDE (PIDE)

- LPT (LPT), Floppy Disk (FD)

J5

Figure 5 CompactPCI J4 Connector Pinout

|            | _           |                           |    |                  |             |

|------------|-------------|---------------------------|----|------------------|-------------|

| A          | В           | C                         |    | D                | ${f E}$     |

| GND        | PIDE CS1#   | PIDE INTRQ — 2            | 25 | — PIDE RSTDR#    | NC          |

| PIDE IOW#  | PIDE DREQ   | PIDE IORDY → 2            | 24 | O—PIDE CS3#      | PIDE DMACK# |

| PIDE D15   | PIDE DA0    | PIDE DA1 → 2              | 23 | → PIDE DIOR#     | PIDE DA2    |

| PIDE D10   | PIDE D11    | PIDE D12 <del>−</del> O 2 | 22 | O—PIDE D13       | PIDE D14    |

| PIDE D05   | PIDE D06    | PIDE D07 — 2              | 21 | O—PIDE D08       | PIDE D09    |

| PIDE D00   | PIDE D01    | PIDE D02 → 2              | 20 | O—PIDE D03       | PIDE D04    |

| PIDE DASP# | PIDE PDIAG# | $NC \longrightarrow 1$    | 19 | <u></u> ∩ NC     | NC          |

| NC         | NC          | NC <del></del> ○ 1        | 18 | <u></u> NC       | NC          |

| NC         | NC          | NC <del></del> ○ 1        | 17 | <u></u> NC       | NC          |

| NC         | NC          | NC <del>−</del> O 1       | 16 | O—NC             | NC          |

| NC         | NC          | NC <del></del> ○ 1        | 15 | <u></u> NC       | NC          |

| key        | key         | key <del>─</del> 1        | 14 | <del>○</del> key | key         |

| key        | key         | key <del>─</del> 1        | 13 | <del>○</del> key | key         |

| key        | key         | key — 1                   | 12 | <del>○</del> key | key         |

| NC         | NC          | NC <del></del> ○ 1        | 11 | <u></u> —NC      | NC          |

| NC         | NC          | NC <del></del> ○ 1        | 10 | <u></u> NC       | NC          |

| NC         | NC          | NC —O                     | 9  | → NC             | NC          |

| NC         | NC          | NC —O                     | 8  | <u></u> NC       | NC          |

| NC         | NC          | LPT STB# <del>─</del>     | 7  | → LPT AFD#       | LPT PD2     |

| LPT INIT#  | LPT PD1     | LPT ERR# —⊖ (             | 6  | → LPT PD0        | LPT PD6     |

| LPT PD5    | LPT PD4     | LPT PD3 — 5               | 5  | → LPT SLIN#      | LPT SLCT    |

| LPT PE     | LPT BUSY#   |                           | 4  | •                | FD DENSEL   |

| FD TRK0#   | FD WP#      | _                         | 3  | O—FD HDSEL#      | FD DSKCHG#  |

| FD MTR1#   | FD DIR#     | FD STEP# ─ 2              | 2  | ⊖FD WDATA#       | FD WGATE#   |

| FD DRATE0  | FD INDEX#   | FD MTR0# —                | 1  | O—FD DS1#        | FD DS0#     |

The following interfaces are available via the PENT/CPCI-731 Compact-PCI J5 connector (the name used in the following pinout is given in brackets):

- Secondary IDE (SIDE)

- Keyboard (KBD), PS2 mouse (MS)

- Ethernet 1 (ETH1)

- Ethernet 2 (ETH2)

- PMC Slot 2 I/O signals (PMC2IO)

Page 18 PENT/CPCI-731

Figure 6

## **CompactPCI J5 Connector Pinout**

| A         | В         | С                          | D            | E           |

|-----------|-----------|----------------------------|--------------|-------------|

| ETH1 TX + | ETH1 RX + | KBD DAT <u>→</u> 22        | SIDE INTR    | SIDE RSTDR# |

| ETH1 TX - | ETH1 RX - | KBD CLK → 21               | → SIDE DACK# | SIDE CS1#   |

| GND       | AUXVCC    | RESET IN — 20              | SIDE IORDY   | SIDE CS3#   |

| ETH2 TX + | ETH2 RX + | MS DAT — 19                | → SIDE IOW#  | SIDE DREQ   |

| ETH2 TX - | ETH2 RX - | MS CLK — 18                | → SIDE IOR#  | SIDE A2     |

| GND       | AUXVCC    | SIDE D15 — 17              | → SIDE A0    | SIDE A1     |

| SIDE D10  | SIDE D11  | SIDE D12 <del>─</del> 16   | → SIDE D13   | SIDE D14    |

| SIDE D05  | SIDE D06  | SIDE D07 — 15              | O  SIDE D08  | SIDE D09    |

| SIDE D00  | SIDE D01  | SIDE D02 — 14              | → SIDE D03   | SIDE D04    |

| PMC2IO-05 | PMC2IO-04 | PMC2IO-03 <del>─</del> 13  | → PMC2IO-02  | PMC2IO-01   |

| PMC2IO-10 | PMC2IO-09 | PMC2IO-08 <del>─</del> 12  | → PMC2IO-07  | PMC2IO-06   |

| PMC2IO-15 | PMC2IO-14 | PMC2IO-13 — 11             | → PMC2IO-12  | PMC2IO-11   |

| PMC2IO-20 | PMC2IO-19 | PMC2IO-18 <del>─</del> 10  | → PMC2IO-17  | PMC2IO-16   |

| PMC2IO-25 | PMC2IO-24 | PMC2IO-23 <del>─</del> 9   | → PMC2IO-22  | PMC2IO-21   |

| PMC2IO-30 | PMC2IO-29 | PMC2IO-28 <del>─</del> 8   | → PMC2IO-27  | PMC2IO-26   |

| PMC2IO-35 | PMC2IO-34 | PMC2IO-33 <del>─</del> 7   | → PMC2IO-32  | PMC2IO-31   |

| PMC2IO-40 | PMC2IO-39 | PMC2IO-38 <del>─</del> 6   | → PMC2IO-37  | PMC2IO-36   |

| PMC2IO-45 | PMC2IO-44 | PMC2IO-43 <del>─</del> 5   | O—PMC2IO-42  | PMC2IO-41   |

| PMC2IO-50 | PMC2IO-49 | PMC2IO-48 <del>─</del> 4   | → PMC2IO-47  | PMC2IO-46   |

| PMC2IO-55 | PMC2IO-54 | PMC2IO-53 <del>─</del> 3   | → PMC2IO-52  | PMC2IO-51   |

| PMC2IO-60 | PMC2IO-59 | PMC2IO-58 <del>─</del> 2   | → PMC2IO-57  | PMC2IO-56   |

| TM_PRNT   | PMC2IO-64 | PMC2IO-63 <del>−</del> 0 1 | O—PMC2IO-62  | PMC2IO-61   |

#### IOBP-CPCI-731

The IOBP-CPCI-731 I/O panel is available as separate price list item for the PENT/CPCI-731. The I/O panel supports the following interfaces:

- Two Ethernet interfaces

- Keyboard

- Mouse

- Two USB interfaces

- Two serial interfaces

- Two parallel interfaces

- IDE interfaces (primary and secondary)

- Floppy interface

#### Caution

The IOBP-CPCI-731 is especially designed for the base board of the PENT/CPCI-731. Do not use any other I/O panels on the PENT/CPCI-731.

# **3.6 BIOS**

The PENT/CPCI-731 is designed to run with Windows NT Version 4.0 in host mode. The initial boot-up procedure is performed by BIOS which provides the following features:

- Year 2000 support

- Upgradable via software utility

- PCI 2.1 compliant

- Plug-and-Play BIOS Specification Version 1.0A compliant (PnP)

- Flexible booting via Multiboot

- Advanced power management

- Two-level password control provided by system security

- Hardware setup via setup program:

- For information on general system configuration via the system BIOS, see section 3.6.1 "Booting Up and Entering Configuration Utilities (e.g. BIOS Setup)" on page 21. Detailed on-line help is available for the system BIOS setup.

- For information on option ROMs which may be implemented on other boards in the CompactPCI rack, see the respective board documentation.

Using the setup program BIOS allocates and optimizes resources (memory, interrupts, etc.) for each of the hardware components (video, disk drives, etc.).

Hardware initialization at boot: At power-on or reset, BIOS performs Power-On Self Test (POST) routines to test system resources. Afterwards it loads and starts the operating system.

The POST performs the following tasks:

- Run basic and limited RAM test

- Conduct an inventory of the devices installed on the system board

- Configure hard and floppy disks, keyboard, VGA, serial or parallel ports

- Configure other devices installed on the system board, e.g.

CD-ROM drives

- Initialize hardware required for system board features such as plug-and-play and power management

- Run Setup if requested

Page 20 PENT/CPCI-731

#### 3.6.1 Booting Up and Entering Configuration Utilities (e.g. BIOS Setup)

BIOS automatically starts during power up or reset:

<Esc>

When pressing <Esc> BIOS continues with the POST screen until the end of POST. It then displays a boot selection menu.

For further information, see section 3.6.2 "The Boot Selection Menu" on page 22.

<F2>

When pressing <F2> BIOS enters Setup.

BIOS provides the Setup program to configure the setting of a wide range of system board features. For example:

- LPT, COM1 and COM2 can be remapped via the advanced configuration option for integrated peripherals in BIOS Setup.

- The IDE devices can be configured via the main configuration options for primary and secondary IDE masters and slaves and via the advanced configuration option for integrated peripherals. This configuration capability is used for example at the first boot after connecting an IDE device.

- The floppy type can be configured via the respective main configuration options for diskettes. This configuration capability is used for example at the first boot after installing a floppy via the respective I/O panel (see note on the IOBP-CPCI-731 on page 19).

Note: If you save the changes you made in Setup, the selections in the menus are stored in NVRAM (CMOS). The next time the system board boots, the BIOS configures the system according to the Setup selections stored in NVRAM (CMOS). If those values cause the system boot to fail, reboot and press <F2> to enter Setup. In Setup, you can get the default values or try to change the selections that caused the boot to fail. If you get the default values, note that the displayed default values are not yet stored to be effective for the next boot. They are just loaded to be displayed. However, they are effective when the current boot-up procedure is resumed.

Input Requests

If the BIOS or an Option ROM (e.g. of an add-on card) requests keyboard input, you are prompted for entering the information. POST continues from there with the regular POST screen.

**POST Error**

Whenever POST detects a non-fatal error, BIOS displays a message asking you to choose between boot continuation or error correction via Setup.

#### 3.6.2 The Boot Selection Menu

The boot selection menu is used to rearrange the boot-order list or to enter Setup.

- 1. In order to override the existing boot sequence (for this boot only) select another boot device from the boot-order list.

- If the specified device does not load the operating system, BIOS reverts to the previous boot sequence.

- 2. In order to boot via the boot configuration options in Setup, enter Setup and change the device as described in the following section.

- 3. In order to continue with the previous boot sequence, press <Esc>.

Page 22 PENT/CPCI-731

#### 3.6.3 Boot Configuration in Setup

The order of the devices from which BIOS attempts to boot the operating system can be selected by the boot configuration options in Setup. During POST, BIOS tries the next one on the list if it is unsuccessful at booting from one device.

Each device listed represents the first of a group of devices if more than one device of this group is installed on the system. For example, if there is more than one hard disk drive, the displayed entry represents the first of such drives as specified in the boot configuration option for fixed media. The same applies to removable media.

The same options determine the order in which POST installs the devices and the operating system assigns device letters. BIOS supports up to two floppy devices, to which the operating system may assign, for example, drive letters A: and B:. C:, D:, E:, etc. are assigned to hard-disk drives.

Note: There is not always an exact correspondence between the order specified in these menus and the letters assigned by the operating system. Many devices such as legacy Option ROMs support more than one device, to which can be assigned more than one letter. If you want the CD-ROM drive to have a letter coming before the hard drive, move it in front of the hard drive. The group of bootable add-in cards refers to devices with non-multiboot-compliant BIOS Option ROM from which you can boot the operating system.

Figure 7 A Sample Setup Screen Showing the Boot Configuration Options

| PhoenixBIOS Setup - Copyright 1992-97 Phoenix Tech<br>Main Advanced <b>Boot</b> Exit                                         | nologies Ltd.                                                                 |  |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|

|                                                                                                                              | Item Specific Help                                                            |  |

| <ol> <li>Hard Drive</li> <li>Diskette Drive</li> <li>ATAPI CD-ROM</li> </ol>                                                 | Select item to relocate using the UP and DOWN arrow keys. Use the '+' and '-' |  |

| > Removable Format                                                                                                           | keys to move the highlighted boot device up ('+') or                          |  |

| > Fixed Media<br>> Removable Media                                                                                           | down ('-') in the priority list                                               |  |

| F1 Help ↑↓Select Item -/+ Change Values F9 Setup Defaults<br>ESC Exit ↔Select Menu Enter Select>Sub-Menu F10 Previous Values |                                                                               |  |

In the example above BIOS first attempts to boot in the following order:

- 1. Hard Drive from hard disk

- 2. Diskette Drive from floppy disk

- 3. ATAPI CD-ROM from CD-ROM.

Page 24 PENT/CPCI-731

#### 3.6.4 Sample Start-up

The following figure shows a sample start-up message following the video BIOS message which displays the graphic card type and the video RAM size.

#### Figure 8 Sample Start-up Screen

```

PhoenixPICO BIOS Version 4.xx

Copyright 1985-1997 Phoenix Technologies Ltd., All Rights Reserved

FORCE COMPUTERS- CPCI-731 BIOS Revision 1.0

08/07/97 09:44:57

CPU = Intel(R) Mobile PentiumII processor 333 MHz

0000640K System RAM Passed

0255M Extended RAM Passed

0256K Cache SRAM Passed

System BIOS shadowed

Video BIOS shadowed

UMB upper limit segment address: F4B2

Fixed Disk 0: SunDisk SDP3B-16

ATAPI CD-ROM: TOSHIBA CD_ROM XM-5702B

```

#### **Problems**

The NVRAM (CMOS) values may have been corrupted or modified incorrectly, perhaps by an application program that changes data stored in NVRAM (CMOS). BIOS detects such problems by verifying a so-called System CMOS Checksum.

If, during boot-up, BIOS detects a problem in the integrity of values stored in NVRAM (CMOS), it displays a message asking you to choose between boot continuation or entering Setup with the ROM default values already loaded into the menus.

*Note:* After entering Setup with the ROM default values already loaded into the menus, it might be possible to restore some values as saved in NVRAM (CMOS) via the exit configuration option to load previous values. However, you should then try to fix the erroneous values which are causing BIOS problems.

### 3.6.5 BIOS Messages

*Note:* If your system fails after you made changes in the Setup menus, you may be able to correct the problem by entering Setup and restoring the original values. If your system displays one of the following messages, write down the message and contact Force Computers.

- Extended RAM Failed at offset: nnnn

- Failing Bits: nnnn

- Keyboard controller error

- Parity Check 1 nnnn

- Parity Check 2 nnnn

- Real time clock error

- Shadow Ram Failed at offset: nnnn

- System cache error Cache disabled

- System RAM Failed at offset: nnnn

- System timer error

## **Message Explanations**

```

nnnn Cache SRAM Passed

nnnn is the amount of system cache in KBytes successfully tested.

```

CD-ROM Drive Identified

Autotyping identified CD-ROM Drive

Diskette drive A error Diskette drive B error

Drive A: or B: is present but fails the BIOS POST diskette tests. Check to see that the drive is defined with the proper diskette type in Setup and that the diskette drive is attached correctly.

Entering SETUP ... Starting Setup program.

Extended RAM Failed at offset: nnnn

Extended memory not working or not configured properly at offset *nnnn*.

nnnn Extended RAM Passed nnnn being the amount of RAM in KBytes successfully tested.

Page 26 PENT/CPCI-731

```

Failing Bits: nnnn

```

The hex number *nnnn* is a map of the bits at the RAM address (in system, extended, or shadow memory) which failed the memory test. Each 1 (one) in the map indicates a failed bit.

```

Fixed Disk 0 Failure

Fixed Disk 1 Failure

Fixed Disk Controller Failure

```

Fixed disk is not working or not configured properly. Check to see if fixed disk is attached properly. Run Setup to be sure the fixed-disk type is correctly identified.

Fixed Disk 0...3 Identified

Autotyping identified specified fixed disk.

```

Incorrect Drive A type - run SETUP

Incorrect Drive B type - run SETUP

```

Type of floppy drive not correctly identified in Setup.

Invalid NVRAM media type

Problem with NVRAM (CMOS) access.

Keyboard controller error

The keyboard controller failed test. You may have to replace the keyboard.

Keyboard error

Keyboard not working.

Keyboard error nn

BIOS discovered a stuck key and displays the scan code *nn* for the stuck key.

Keyboard locked - Unlock key switch Unlock the system to proceed.

Monitor type does not match CMOS - Run SETUP Monitor type not correctly identified in Setup.

Operating system not found

Operating system cannot be located on either drive A: or drive C:. Enter Setup and see if fixed disk and drive A: are properly identified.

Parity Check 1 nnnn

Parity error found in the system bus. BIOS attempts to locate the address *nnnn* and display it on the screen. If it cannot locate the address, it displays ????.

Parity Check 2 nnnn

Parity error found in the I/O bus. BIOS attempts to locate the address *nnnn* and display it on the screen. If it cannot locate the address, it displays ????.

Press <F1> to resume, <F2> to Setup

Displayed after any recoverable error message. Press <F1> to start the boot process or <F2> to enter Setup and change any settings.

Previous boot incomplete - Default configuration used

Previous POST did not complete successfully. POST loads default values and offers to run Setup. If the failure was caused by incorrect values and they are not corrected, the next boot is likely to fail. On systems with control of wait states, improper Setup settings can also terminate POST and cause this error on the next boot. Run Setup and verify that the wait-state configuration is correct. This error is cleared the next time the system is booted.

Real time clock error

Real-time clock fails BIOS test. May require board repair.

Resource allocation conflict on motherboard - Run Configuration Utility

Run ISA or EISA Configuration Utility to resolve resource conflict.

Shadow Ram Failed at offset: nnnn

Shadow RAM failed at offset *nnnn* of the 64k block at which the error was detected.

nnnn Shadow RAM Passed

nnnn being the amount of shadow RAM in KBytes successfully tested.

System BIOS shadowed

System BIOS copied to shadow RAM.

System cache error - Cache disabled

RAM cache failed the BIOS test. BIOS disabled the cache.

System CMOS checksum bad - run SETUP

System NVRAM (CMOS) has been corrupted or modified incorrectly, perhaps by an application program that changes data stored in NVRAM (CMOS). Run Setup and reconfigure the system either by getting the Default Values and/or making your own selections.

System RAM Failed at offset: nnnn

System RAM failed at offset *nnnn* in the 64k block at which the error was detected.

nnnn System RAM Passed

Where *nnnn* is the amount of system RAM in KBytes successfully tested

System timer error

The timer test failed. Requires repair of system board.

UMB upper limit segment address: nnnn

Displays the address *nnnn* of the upper limit of upper memory blocks, indicating released segments of the BIOS which may be reclaimed by a virtual memory manager.

Video BIOS shadowed

Video BIOS successfully copied to shadow RAM.

Page 28 PENT/CPCI-731

Invalid System Configuration Data - run configuration utility

Enter Setup and use the advanced configuration option to reset the configuration data (due to corrupted ESCD data).

# 3.7 Upgrades and Accessories

Apart from the extensions which are possible via the CompactPCI system, the PENT/CPCI-731 itself allows for an easy and cost-efficient way to adapt the board to the application's needs.

PMC Slot 1 The PMC slot 1 can be used to install a standard PMC module with front-

panel I/O and rear I/O onto the PENT/CPCI-731. The memory module option can only be installed on this location if no PMC is required on this slot. For further information, see section 3.7.1 "Installing a PMC Mod-

ule" on page 31.

PMC Slot 2 The PMC slot 2 can be used to install a standard PMC module with front-

panel I/O and rear I/O onto the PENT/CPCI-731. A 2.5" hard drive may be installed at the location of PMC slot 2 instead of a PMC Module. For further information, see section 3.7.1 "Installing a PMC Module" on

page 31.

Memory Module In addition to the local SDRAM of the PENT/CPCI-731 the memory

module PENT/MEM-700 with SDRAM chips can be installed on the PENT/CPCI-731. The maximum possible memory size of the memory module is 512 MByte. This allows a maximum possible system memory of 768 MByte in total. For installation information, refer to the Installa-

tion Guide delivered together with the memory module.

HD-AccKit The IDE hard disk accessory kit PENT/CPCI-731/HD-AccKit can be in-

stalled on PMC slot 2 of the PENT/CPCI-731 providing a local mass storage device. For installation information refer to the Installation Guide

delivered together with the accessory kit.

IOBP-CPCI-731 The IOBP-CPCI-731 provides access to the base board's CompactPCI

user I/O interfaces via industry standard connectors. It is included in the rear I/O panel accessory kit for PENT/CPCI-731 base boards, containing

the I/O panel itself and the cables.

VGA-AccKit The VGA accessory kit PMC/VGA is a PMC based VGA card. It can be

installed in one of the PMC slots of the PENT/CPCI-731.

For installation information refer to the Installation Guide delivered to-

gether with the VGA accessory kit.

BIOS-UpKit

The BIOS upgrade kit PENT/CPCI-731/BIOS-UpKit contains a DOS-formatted floppy disk with a BIOS upgrade file and upgrade utilities e.g. to reflect extended hardware support. For installation information refer to the README file contained on the floppy disk.

Page 30 PENT/CPCI-731

### 3.7.1 Installing a PMC Module

The PENT/CPCI-731 provides two PMC slots. Both slots consist of three connectors identified as PNxx (see "Mounting Points for PMC Modules on the PENT/CPCI-731" on page 32) and support a 32-bit data bus width with a maximum frequency of 33 MHz. +/-12V are available at the PMC slots.

*Note:* Slot 1 is only available if no memory module is installed and Slot 2 is only available if no hard drive is assembled.

PMC Voltage Keys The PCI bus uses a 5V or 3.3V voltage signal level on the PMC slots (factory option). The appropriate voltage keys prevent 3.3V PMC cards, or respective 5V PMC cards, from being plugged into the PMC slots.

Connector Configuration The 32-bit PCI bus requires two PMC connectors. The third PMC connector connects additional user I/O signals of PMC slot 1 and 2 with the CompactPCI J3 and J5 connector.

Installation

In order to install a PMC module on a PMC slot, proceed as follows:

1. If PMC slot 1 is intended to be used, the memory module option cannot be used. If the space for PMC slot 1 is occupied by a memory module the memory module must be removed first.

If PMC slot 2 is intended to be used, the on-board hard drive option cannot be used. If the space of PMC slot 2 is occupied by a hard drive the hard drive must be removed first.

- 2. Plug the PMC module on the connectors PN11, PN12 and PN14 for PMC slot 1 or PN21, PN22, and PN24 for PMC slot 2, so that the stand-offs of the module fit on the mounting holes PMC11...PMC14 or PMC21...PMC24 (see figure 9 "Mounting Points for PMC Modules on the PENT/CPCI-731" on page 32).

- 3. Fasten the PMC module onto the PENT/CPCI-731 with the four screws delivered together with the PMC module.

Page 32 PENT/CPCI-731

## 4 Hardware

The PENT/CPCI-731 is a high performance CompactPCI platform. The I/O board is based on:

- Intel Pentium II/III Mobile Module

- PCI bus with 33 MHz clock frequency

### Device Information

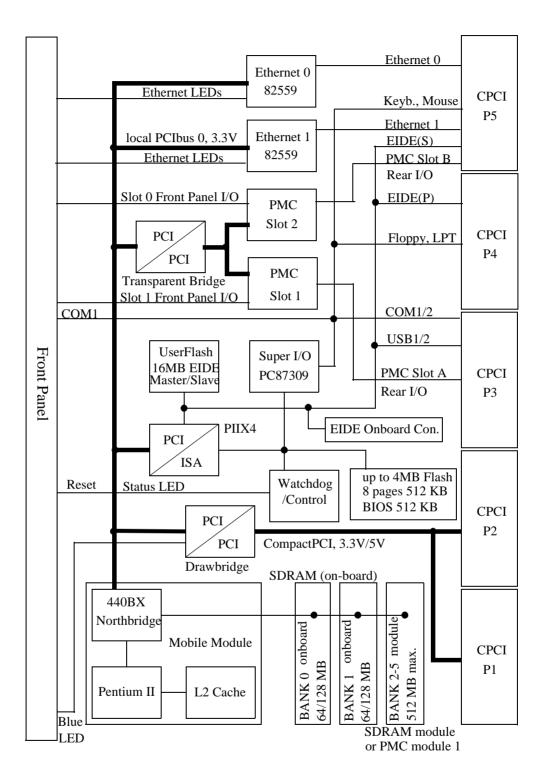

Wherever applicable, the PENT/CPCI-731 uses standard PC devices and related software to implement the features listed in section 2 "Introduction" on page 5. The following block diagram gives an overview on how those devices work together and which data paths they use.

**Data Sheets**

It is assumed that the PENT/CPCI-731 is integrated into systems at the operating system level. Therefore, no data sheets are provided in this *Reference Guide*. For a list of applicable data sheets, see the front matter of this manual.

Board Specific Registers

Following the block diagram for the PENT/CPCI-731, this section gives an overview on the I/O and memory maps and describes all PENT/CPCI-731 specific registers.

Figure 10 Block Diagramm

Page 34 PENT/CPCI-731

Table 7 I/O Map