In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/54709-2

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

Your **definitive** source for quality pre-owned equipment.

### Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

- Critical and expedited services

- In stock / Ready-to-ship

- We buy your excess, underutilized, and idle equipment

- Full-service, independent repair center

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# Agilent E2925B PCI Analyzer

# **User's Guide**

#### **Important Notice**

This document contains propriety information that is protected by copyright. All rights are reserved. Neither the documentation nor software may be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form, in whole or in part, without the prior written consent of Agilent Technologies.

© Copyright 1998, 2000 by: Agilent Technologies Herrenberger Straße 130 D-71034 Böblingen Germany

The information in this manual is subject to change without notice. Agilent Technologies makes no warranty of any kind with regard to this manual, including but not limited to the implied warranties of merchantability and fitness for a particular purpose.

Agilent Technologies shall not be liable for errors contained herein or direct, indirect, special, incidental, or consequential damages in connection with the furnishing, performance, or use of this manual.

Brand or product names are trademarks or registered trademarks of their respective companies or organizations.

Authors: Stephan Greisinger and Stefan Kunzi, t<br/>3 medien GmbH

# Contents

| System Overview  |                                                              | 7  |

|------------------|--------------------------------------------------------------|----|

|                  | A Window To The System                                       | 8  |

|                  | User Interface                                               | 10 |

|                  | Test Setup Overview                                          | 11 |

|                  | Analyzer Overview                                            | 11 |

|                  | Exerciser Overview                                           | 13 |

|                  | Hardware and Interfaces                                      | 14 |

| Running A Sample | e PCI Analyzer Session                                       | 17 |

|                  | PCI Analyzer Scenarios                                       | 18 |

|                  | Preparing for the Guided Tour                                | 18 |

|                  | Guided Tour: Analyzing PCI Traffic to a Graphics             |    |

|                  | Controller                                                   | 20 |

|                  | Setting Up the Trigger                                       | 20 |

|                  | Setting Up the Storage Qualifier                             | 22 |

|                  | Running the PCI Analyzer                                     | 23 |

|                  | Analyzing the Captured Waveforms                             | 24 |

|                  | Analyzing the Captured Bus Cycles                            | 25 |

|                  | Analyzing the Captured Transactions                          | 26 |

|                  | Getting Help                                                 | 27 |

|                  | <b>Guided Tour: Analyzing Protocol and Timing Violations</b> | 28 |

|                  | Setting Up the Protocol Observer                             | 28 |

|                  | Triggering on Protocol Errors                                | 29 |

|                  | Analyzing the Captured Waveforms                             | 30 |

|                  | Detecting Setup/Hold Timing Violations                       | 31 |

|                  | Guided Tour: Using the State Sequencer                       | 33 |

|                  | Changing to Sequencer Mode                                   | 33 |

|                  | Setting Up the Trigger Sequencer                             | 34 |

|                  | Guided Tour: PCI Performance Analysis                        | 36 |

|                  | Identifying Overall System Performance                       | 37 |

| Setting Up a PCI Analyzer Test |                                                      |    |

|--------------------------------|------------------------------------------------------|----|

|                                | Possible PCI Analyzer Configurations                 | 39 |

|                                | Dedicated Control PC                                 | 40 |

|                                | Software Running on System Under Test                | 41 |

|                                | Concealing the Card from the System                  | 42 |

|                                | Connecting to the Testcard                           | 43 |

|                                | How to Select the Connection                         | 44 |

|                                | Connection Troubleshooting                           | 45 |

| Analyzing Protoco              | ol Violations                                        | 47 |

|                                | Protocol Observation                                 | 47 |

|                                | How to Set Up the Protocol Observer                  | 48 |

|                                | Watching the Protocol Observer                       | 49 |

|                                | How to Upload Protocol Observer Results              | 49 |

|                                | How to Reset the Protocol Observer                   | 50 |

| Analyzing Timing               | Violations                                           | 51 |

|                                | Observed Timing Rules                                | 51 |

|                                | Timing Check Limitations                             | 52 |

|                                | Adapting the Timing Checker                          | 53 |

|                                | How to Set Up the Timing Checker                     | 54 |

|                                | How to Modify Timing Limits                          | 55 |

|                                | Watching the Timing Checker                          | 56 |

|                                | How to Upload Timing Checker Results                 | 56 |

|                                | How to Reset the Timing Checker                      | 56 |

|                                | How to Debug Timing Violations                       | 57 |

| Analyzing PCI Per              | formance                                             | 59 |

|                                | Predefined Performance Measures                      | 60 |

|                                | How to Select Predefined Performance Measures        | 61 |

|                                | How to Run a Performance Measurement                 | 62 |

|                                | Advanced Performance Measures                        | 64 |

|                                | Sample Advanced Performance Setup                    | 66 |

|                                | How to Set Up the Measures for the Example           | 67 |

|                                | How to Program the Counter Sequencer for the Example | 68 |

| Capturing Data In The Trace Memory |                                        |     |

|------------------------------------|----------------------------------------|-----|

|                                    | Data Stored In The Trace Memory        | 72  |

|                                    | Capture Mode                           | 74  |

| ;                                  | Setting Up the Data Capture            | 75  |

|                                    | How to Select the Capture Mode         | 75  |

|                                    | How to Set Up the Trigger              | 76  |

|                                    | How to Specify a Trigger Pattern       | 77  |

|                                    | How to Set Up the Storage Qualifier    | 79  |

|                                    | How to Specify Transactions and States | 80  |

| ;                                  | Setting Up the Trigger Sequencer       | 81  |

|                                    | Sample Sequencer Setup                 | 83  |

|                                    | How to Set Up the Trigger Sequencer    | 85  |

|                                    | Running the Data Capture               | 87  |

| Viewing And Proc                   | essing The Trace Memory Capture        | 89  |

|                                    | Using the Waveform Lister              | 90  |

|                                    | How to Arrange the Signal Display      | 91  |

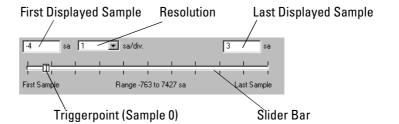

|                                    | Adjusting Range and Resolution         | 92  |

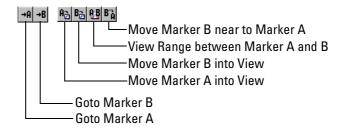

|                                    | Using the Markers                      | 92  |

|                                    | How to Synchronize the Listers         | 94  |

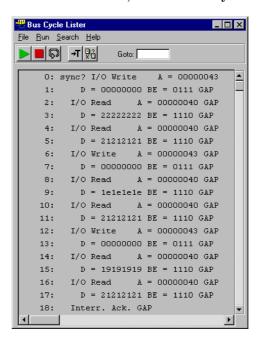

|                                    | Using the Bus Cycle Lister             | 94  |

|                                    | Browsing Through the Cycles            | 95  |

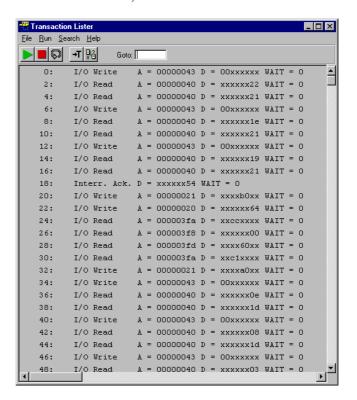

|                                    | Using the Transaction Lister           | 96  |

|                                    | Processing the Captured Data           | 97  |

| Saving and Re-Using the Setups     |                                        | 99  |

|                                    | Re-Using Test Setups                   | 99  |

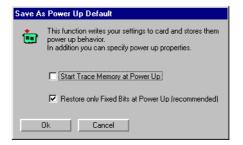

|                                    | How to Overwrite the Power Up Defaults | 100 |

| Upgrading the PCI Analyzer         |                                        | 101 |

|                                    | How to Install Software Options        | 101 |

|                                    | Upgrading the Testcard Hardware        | 102 |

#### **Contents**

| Updating the Testcard |                                            | 103 |

|-----------------------|--------------------------------------------|-----|

|                       | How to Check the Hardware                  | 103 |

|                       | How to Update the Testcard Hardware        | 103 |

| Analyzer Reference    |                                            | 105 |

|                       | List of Rules Observed by the PCI Analyzer | 105 |

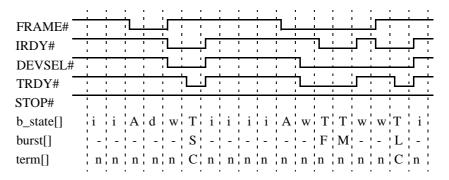

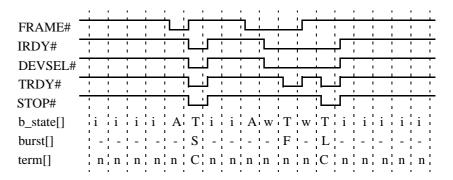

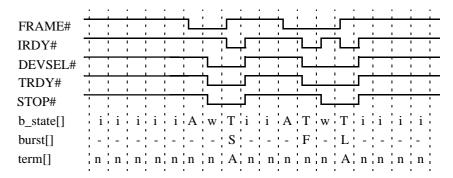

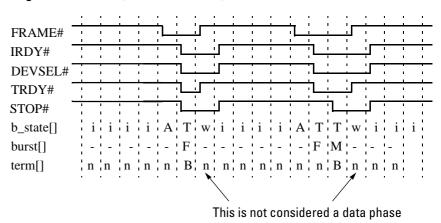

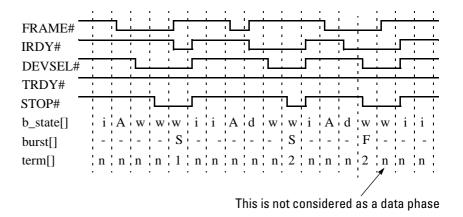

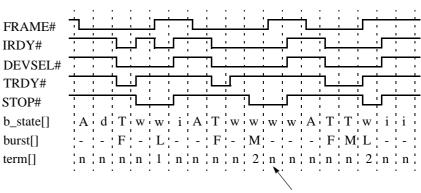

|                       | Sample Timing Diagrams                     | 112 |

|                       | Application Interfaces                     | 115 |

|                       | Static I/O Port                            | 115 |

|                       | Trigger I/O Connector                      | 117 |

|                       | LEDs on the Testcard                       | 119 |

| Glossary              |                                            | 121 |

# System Overview

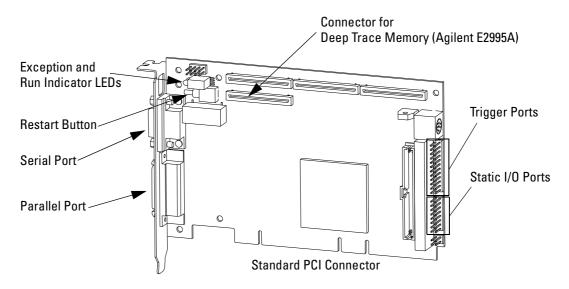

Before going into the details of the PCI Analyzer, take a look at the features and interfaces of the Agilent E2925B testcard and its options:

- "A Window To The System" on page 8 describes the use models and scenarios in which the testcard and its options are intended to be used

- "User Interface" on page 10 provides an overview of the user interface software coming with the testcard, and, thus, lists the card's basic features.

- "Hardware and Interfaces" on page 14 identifies the most important elements on the testcard.

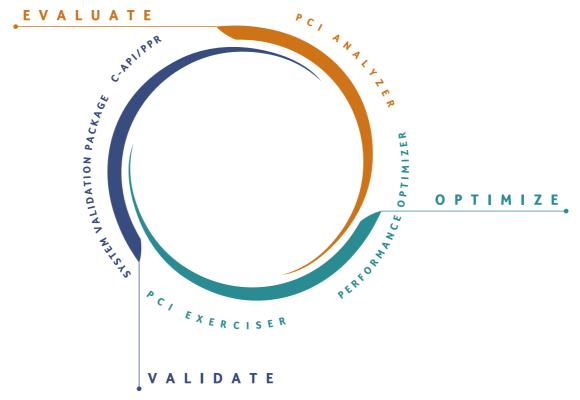

# A Window To The System

The Agilent E2925B testcard is your window on the system during product development, giving you access to almost all of the system components located on the PCI bus, as well as devices and adapters on secondary buses such as ISA.

The options available for the testcard support you in all phases of the design cycle—and all along the value chain of the computer industry.

This is how you can use the card in the individual phases:

When bringing up and debugging a PCI-based system, device, or firmware, the PCI Analyzer coming with the card lets you evaluate its behavior on the PCI bus.

While tools like oscilloscopes and logic analyzers focus on problems on your device (for example, timings, signal integrity), the PCI Analyzer allows you to examine the device's behavior on the bus, as well as to perform functional tests like data compares.

For example, when testing LAN interface cards, you can sample the data packages and compare incoming and outgoing data.

The PCI Analyzer also features real-time performance measurement, using predefined, standardized measures like efficiency, throughput, and utilization. It also allows to set up user-defined measures.

- When optimizing a system or a device to improve its performance, the Performance Optimizer (option #200) gives you in-depth postprocessed performance analysis and hints for performance optimization.

- The PCI Exerciser (option #300) allows you to overcome the passive role in monitoring the PCI bus. With the PCI Exerciser, the testcard can be programmed to behave as a master and/or target device.

With the PCI Exerciser you can set up complex PCI scenarios and worst case test patterns quickly and in a repeatable way.

Using these features, you can optimize for reliability, by ensuring that your system or device will handle even worst PCI conditions.

You can also run functional tests, directing the PCI Exerciser to generate and transmit large blocks of data in specified time intervals, thus testing how much PCI traffic your device can handle.

- To proceed even further and validate that your PCI design works under all real-life conditions, the **System Validation Pack** (option #310) provides a sophisticated user interface and pre-defined tests.

- Finally, the C-API / PPR (option #320) programming interface provides full flexibility for integrating the testcard into existing test environments and controlling all details on the testcard.

Agilent's unique PCI Protocol Permutator and Randomizer (PPR) prepares the PCI Exerciser to transfer a single block of data with as many protocol variations as possible, giving you the optimum test

**coverage** in the minimum amount of time.

System Overview User Interface

# **User Interface**

The Agilent E2925B testcard comes with a graphical user interface software providing a basic framework and the controls for the PCI Analyzer. The options available for the testcard also use this framework, expanding it by their own specific features.

Buttons The most important features are available via the framework buttons.

For example, for the PCI Analyzer you can set up the data capture and display the results in different formats—all by means of the buttons.

**Menus** All these features and more are available via the menus of the framework window, as well.

**Overview Windows** As a third possibility, there are the overview windows provided by the user interface. These windows provide process-oriented access to the individual features.

User Interface System Overview

# **Test Setup Overview**

The test setup overview shows the basic test configuration.

The test setup is described by the following aspects:

- The *Host* group identifies the type of connection between the user interface software and the testcard. Clicking the button allows you to change the current settings in the Testcard Configuration dialog box.

- To the right, there is a group showing the detected testcard and its capabilities. The *Exerciser* and *Analyzer* buttons open the respective overview windows (if registered).

- The System group describes the properties of the detected PCI bus.

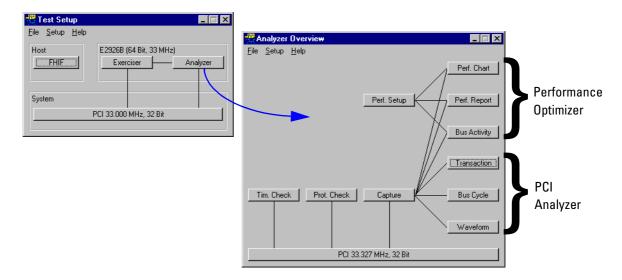

## **Analyzer Overview**

Clicking the *Analyzer* button in the Test Setup window shows the Analyzer Overview window.

System Overview User Interface

The Analyzer Overview window shows the individual components of the PCI Analyzer (and the Performance Optimizer), how they interact, and how they act on the bus. Clicking the buttons brings up the respective setup or result windows.

For the PCI Analyzer, there is

· the Timing Check

The timing checker continuously monitors the PCI bus to detect timing violations.

• the Protocol Check

The protocol observer continuously monitors the PCI bus to detect protocol errors.

• the Capture control

The PCI Analyzer allows you to specify exactly when and which data is to be captured from the PCI bus, thus making optimum use of the available trace memory.

the result windows: waveform lister, bus cycle lister, and transaction lister

The result windows interpret and display the captured data using different levels of abstraction (from signal level to transaction level).

Additionally, the PCI Analyzer provides features for real-time performance measurements.

If the Performance Optimizer option has been installed and enabled, there are additional features available for post-processed performance analysis and optimization:

• the Performance Setup

For the Performance Optimizer you can set up the structure of the report to be generated, identify master and target devices to be considered, and control the capture for performance analysis.

• the Performance Chart

The performance charts show graphical representations of the performance-relevant aspects found in the captured PCI traffic.

• the Performance Report

The performance report summarizes the results in a hierarchical way, so you can focus on your level of detail.

• the Bus Activity Lister

The bus activity lister summarizes all transactions found in the captured data. However, for each bus activity, only those properties are displayed that are of interest in a performance analysis.

User Interface System Overview

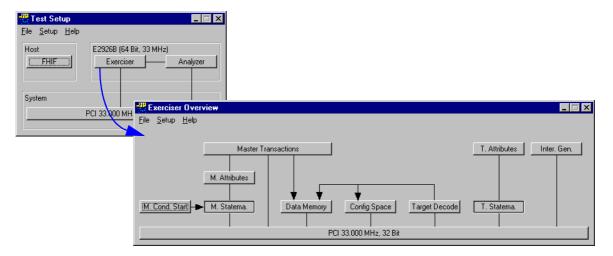

### **Exerciser Overview**

Clicking the *Exerciser* button in the Test Setup window shows the Exerciser Overview window. Both button and window are only available if the PCI Exerciser option has been installed.

The Exerciser Overview window shows the individual components of the PCI Exerciser, how they interact, and how they act on the bus. Clicking the buttons brings up the respective setup windows.

The Agilent E2925B testcard can act as a master or a target device on the PCI bus. You have full control over the testcard's **configuration space**.

For the **master** you can specify,

- transactions to be performed,

- protocol attributes to be used with the transactions,

- data to be used for the transactions,

- · conditions to be fulfilled before the transactions are started.

For the target you can specify

- which addresses are to be decoded (target decode and configuration space),

- how received data is to be handled,

- the data to be transferred on request,

- the protocol attributes to be used during transactions.

Furthermore, the Agilent E2925B testcard is able to generate any **PCI** interrupt INTA# ... INTD#.

System Overview Hardware and Interfaces

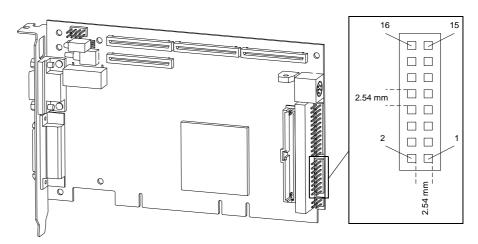

# **Hardware and Interfaces**

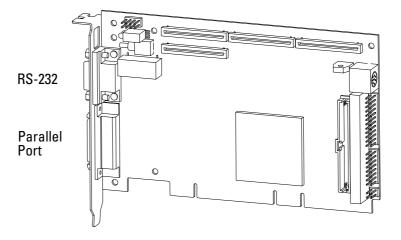

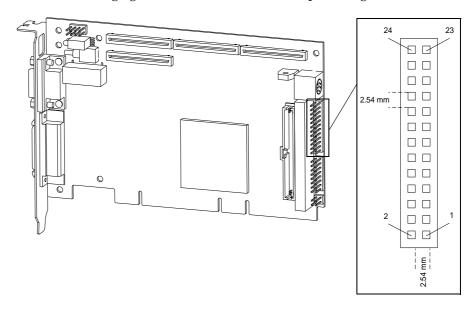

The following figure shows an overview of the interfaces provided by the Agilent E2925B testcard.

The following list roughly describes the most important interfaces of the card. For information on the other connectors to be found on the card, please refer to your supplementary information.

- The **restart button** allows you to restart the current test. For example, if your test is to trigger on a certain event after power up, but the event has already occurred during power up, you can easily restart the test with the restart button. The card will then be ready to trigger on the event again.

- The restart button restarts the trace memory and performance counters, the protocol observer and the timing checker (and master and target if the PCI Exerciser option has been installed).

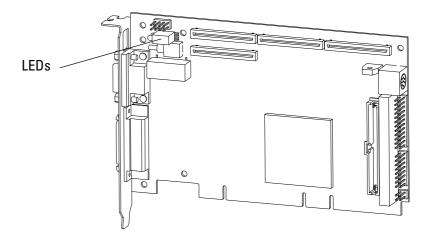

- The **exception and run indicator LEDs** show the card's status and are visible even if the card is plugged into a closed system. For more details, refer to "*LEDs on the Testcard*" on page 119.

- The **parallel and serial ports** are the control interfaces used to connect the card to the user interface software running on a host PC. The parallel port is the preferred interface, used in combination with the Fast Host Interface card plugged into the host PC. For more details, refer to "Connecting to the Testcard" on page 43.

Hardware and Interfaces System Overview

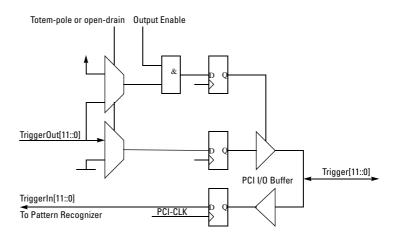

• The **trigger ports** provide access to the card's trigger I/O lines. For more details, refer to "*Trigger I/O Connector*" on page 117.

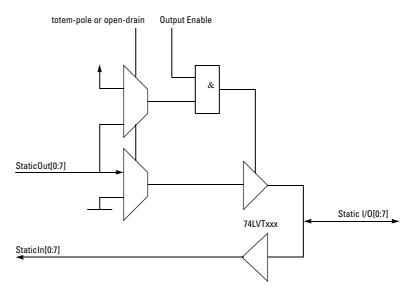

- The **static I/O ports** can be used to transfer data (for example, status information) between the testcard and the test environment during execution of a test provide. For more details, refer to "Static I/O Port" on page 115.

- The **PCI connector** is used to plug the card into the system under test. If the user interface software is running on the system under test, this connector can also be used as control interface.

System Overview Hardware and Interfaces

# Running A Sample PCI Analyzer Session

The following application examples explain how the testcard can be used in various analyzing tasks. After introducing the major scenarios for the PCI Analyzer and showing how to prepare for the sample sessions, you will find guided tours covering the following topics:

- Guided Tour: Analyzing PCI Traffic to a Graphics Controller

- Guided Tour: Analyzing Protocol and Timing Violations

- Guided Tour: Using the State Sequencer

- Guided Tour: PCI Performance Analysis

NOTE The examples given here are also part of the *Agilent E2920 Software Demo guide*. If you have already worked through this guide, you may skip these guided tours.

# **PCI Analyzer Scenarios**

#### If you are

- designing a PCI chip and you need to do bring-up or debugging,

- using a third party PCI chip on your motherboard or adapter card that you need to evaluate,

- trying to find the root cause of a failure that occurred during your chip or system level validation,

- writing and debugging low level software (for example, BIOS code, device drivers),

you probably need to monitor the PCI bus to find out whether your software generates the correct PCI transactions, and also whether your device under test reacts correctly, both at the protocol and the data level. Monitoring the PCI transactions of your device also allows you to judge its performance in relation to other devices.

The built-in 64k state PCI logic analyzer (optional 4M state) allows you to capture PCI traffic and view it as a state waveform, a bus cycle listing or as a transaction listing. The following examples show you how to set up the PCI Analyzer and how to interpret the results.

# **Preparing for the Guided Tour**

The examples described in the guided tours are designed to be performed in Offline/Demo Mode—without hardware. All the setup files (\*.bst) and logic analyzer trace files (\*.wfm) that are mentioned in the following text can be found under

<your\_installation\_directory>\samples\demo. If you did not change the

default setting during installation, <your\_installation\_directory> will be

C:\Program Files\Agilent\E2920 PCI Series <release number>.

To prepare for the guided tour:

- **1** Launch the Agilent E2920 software.

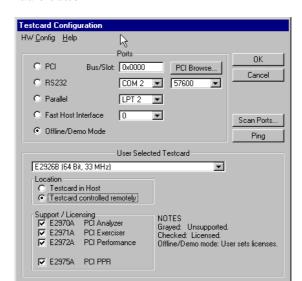

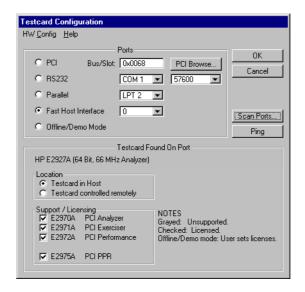

- **2** From the *Setup* menu, choose *Testcard Configuration*.

**3** In the Testcard Configuration window, select the *Offline/Demo Mode* radio button.

- **4** Now choose *E2926B* (*64 bit*, *33 MHz*) from the *User Selected Testcard* listbox, and check all license boxes in the *Support/Licensing* group.

- Your display should look like the window shown above.

- **5** Click *OK* and the main window should look like this.

You are now ready to start the guided tours.

**NOTE** The examples in the guided tours use an Agilent E2926B (64 bit, 33 MHz) testcard, but also apply to all other testcards of the Agilent E2920 series.

# **Guided Tour: Analyzing PCI Traffic to a Graphics Controller**

This example shows how to set up the testcard to trigger on a particular address range and capture PCI traffic that occurs around this triggerpoint. Afterwards, the captured data can be viewed at various levels of abstraction to analyze the PCI behavior of the participating devices (in this case a Host-PCI bridge and a PCI graphics controller).

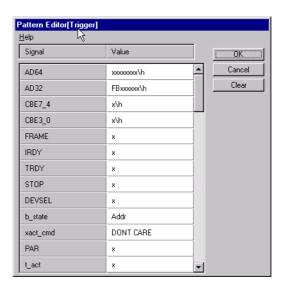

For this example, the built-in logic analyzer will be set up to trigger on a PCI address phase with an address in the range between 0xFB000000 and 0xFBFFFFFF, which corresponds to the video frame buffer. All PCI cycles will be stored, including idle cycles.

## **Setting Up the Trigger**

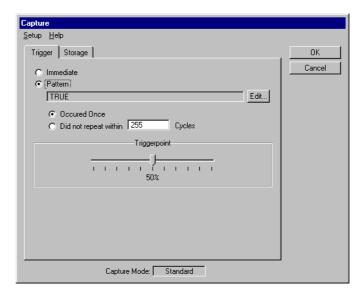

To set up a trigger and storage qualifier for the built-in logic analyzer:

1 Use the Capture button in the icon bar of the main window, or choose *Capture* from the *Analyzer* menu.

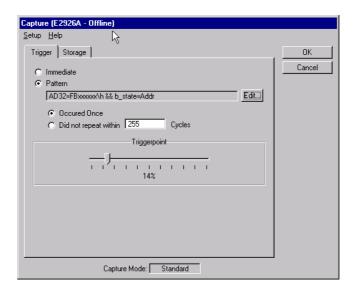

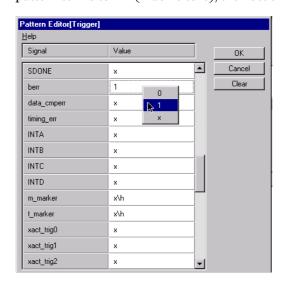

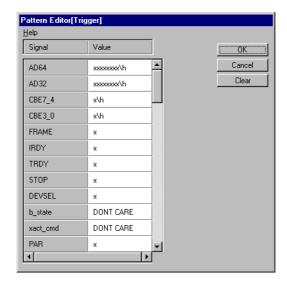

- **2** In the Capture dialog box, select the *Trigger* tab, choose trigger on *Pattern*, and select the *Occurred Once* radio button.

- **3** Click the *Edit* button next to the pattern term and set the *AD32* field to **FBxxxxx**\h.

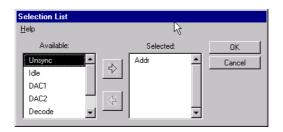

- 4 Now click on the text field to the right of the signal  $b\_state$  to open a Selection List dialog box.

**5** Highlight **Addr** and click the right-arrow button to place it in the right (*Selected*) box and press *OK*. You can use the left-arrow button to remove the "DON'T CARE" entry from the *Selected* list.

The **b\_state** signal is internally generated by the testcard to provide easy trigger setup for the multiplexed PCI bus.

The Pattern editor window should now look like this.

#### 6 Click OK.

The Capture window should now look like this.

# **Setting Up the Storage Qualifier**

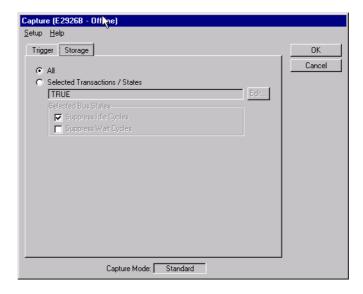

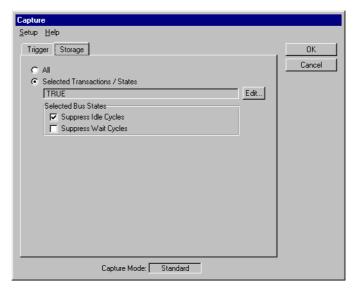

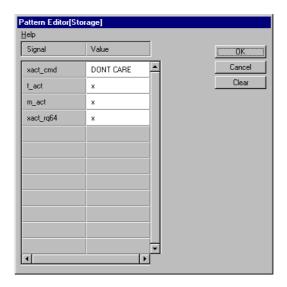

Now, take a look at the *Storage* tab of the Capture window. On this tab, you can define the storage qualifier. The default is *All*, which instructs the built-in logic analyzer to unconditionally capture one sample per PCI clock. Alternatively, you can choose *Selected Transactions/States*, which allows you, for example, to suppress idle cycles between transactions and/or wait states during a transaction (that is, PCI transactions are stored back-to-back).

With the pattern fields, you can further restrict what is captured in the trace memory by storing only particular transaction types (for example, only memory writes) or storing only transactions where the testcard is participating as a master or target.

1 In the Capture window, select the *Storage* tab. For this example, the default *All* can be used.

**2** Press *OK* in the Capture window, and the built-in logic analyzer is ready to run.

## **Running the PCI Analyzer**

Starting the PCI Analyzer in offline mode results in an error, but this would be the next step in our procedure if we were connected to a testcard.

This is normally done by pressing the Run button in the main window (the large green arrow, which also starts the PCI Exerciser if installed) or by selecting the *Run* from the *Analyzer* menu. When connected to a testcard, the status bar of the Analyzer group in the main window changes to *Running*... to indicate that the Analyzer is running and waiting for a trigger signal.

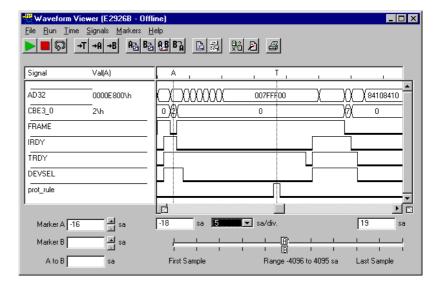

# **Analyzing the Captured Waveforms**

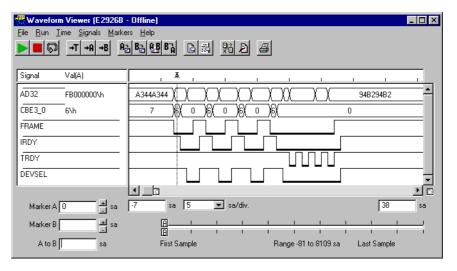

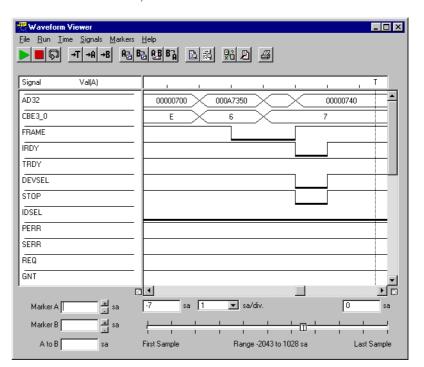

The captured data can be analyzed at different levels of abstraction. We start by using the waveform viewer:

- 1 Click the Waveform Viewer button in the main window (or use the *Waveform Lister* item from the Analyzer menu) to open the waveform viewer.

- **2** From the *File* menu in the Waveform Viewer window select *Load from file* and load the trace file video1.wfm.

- **3** To navigate within the waveform viewer,

- press the Goto Trigger button to view data at the trigger,

- enter a sample number in the left or right boxes below each corner of the waveform display, or

- use the scroll bar to move the viewed data.

Markers A and B can also be moved just by grabbing them with the mouse or through numeric entry.

If you need more information about the buttons and other controls in the waveform viewer, drag your mouse over the control icons to view the tool tips.

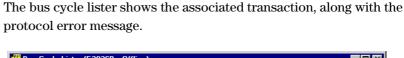

# **Analyzing the Captured Bus Cycles**

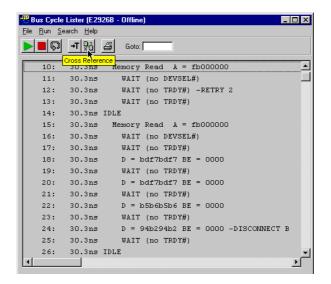

Although the waveform viewer is appropriate for analyzing single transactions or when you need to check the state of individual control signals, it is tedious to "read" PCI transactions by looking at the waveform viewer. This is where the bus cycle lister helps.

- 1 Click the Bus Cycle Lister button in the main window (or use the *Bus Cycle Lister* item from the Analyzer menu) to open the bus cycle lister.

- 2 In the Bus Cycle Lister window, press the Goto Trigger button to go to the triggerpoint. Scroll around to see how it works.

3 If you want to view the waveform for a given set of lines in the bus cycle lister, highlight the desired lines in the bus cycle lister and press the Cross Reference button (make sure that the waveform viewer is still open or minimized).

# **Analyzing the Captured Transactions**

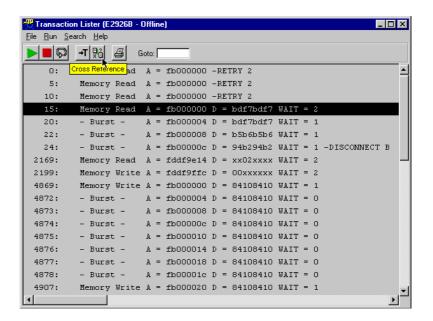

To get a more compressed overview of the transactions that occurred on the bus:

1 Click the Transaction Lister button in the main window (or use the *Transaction Lister* item from the Analyzer menu).

The transaction lister removes idles from the display and summarizes the number of waits for each data phase, just showing useful information such as address and data phases. Address reconstruction is also done during bursts.

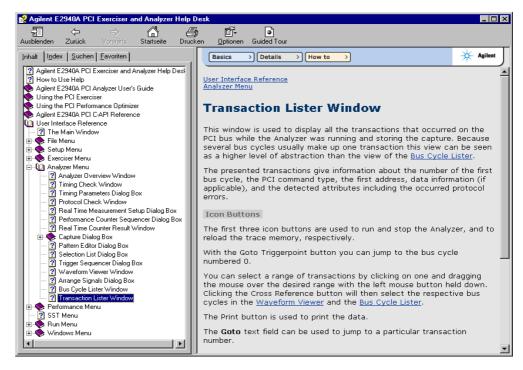

## **Getting Help**

With the cursor in any Analyzer window, pressing the keyboard's **F1** key brings up context sensitive help.

Starting from here, you can use the signposts on top of the topic to find more information:

- Use the *Basics* signpost to find related basic and background information.

- Use the *Details* signpost to find more advanced information and reference data.

- Use the *How to* signpost to find procedural information and instructions for using the currently selected window.

- NOTE The online help requires Internet Explorer 4.0 or higher to work. The online help is also currently focussed on Analyzer and Exerciser functions. Additional on-line help will be added for other features in future software releases.

# **Guided Tour: Analyzing Protocol** and **Timing Violations**

In this example, the protocol observer of the testcard is used in conjunction with the built-in logic analyzer to trigger on a protocol violation that occurred during an access to a device's I/O space. You can load the setup for this example from video2.bst, and the trace data from video2.wfm (load video2.bst with *Load* from the *File* menu in the main window, and video2.wfm with *Load* from the *File* menu in the waveform viewer).

The protocol observer of the Agilent PCI Analyzer monitors 53 protocol rules from Appendix C of the PCI Spec. 2.1 in real time and flags the violation of an error with an LED on the rear panel of the board.

At the end of this tour, we will also take a glance at the timing checker.

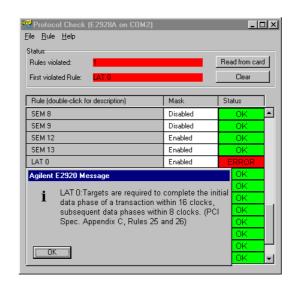

## **Setting Up the Protocol Observer**

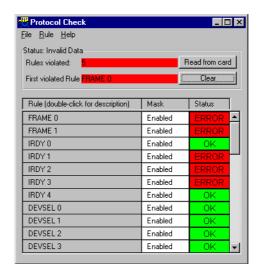

From the user interface, the status of the protocol observer can be checked by opening the protocol check window:

1 From the *Analyzer* menu select *Protocol Check*.

The Protocol Check window indicates the first rule that was violated, as well as the total number of violated rules. Each rule can be individually enabled or disabled to prevent flagging of known errors. In demo mode, the software displays random errors to give you an idea of how it works.

You can double-click on any rule name field to get an explanation of what that rule checks.

## **Triggering on Protocol Errors**

In order to analyze a protocol violation and find out which PCI device caused the violation, you can use the protocol observer's output *berr* to trigger the built-in logic analyzer. The *berr* signal is asserted when any one of the enabled protocol rules has been violated.

- 1 Open the Capture window, select *Pattern*, and press the *Edit* button next to the pattern term.

- **2** In the Pattern Editor window press the *Clear* button to reset all pattern terms to "x" (= don't care), then set the *berr* field to 1.

3 Run the analyzer to trigger on protocol errors.

# **Analyzing the Captured Waveforms**

When the analyzer is started and the above mentioned device is accessed, the analyzer triggers when the violation occurs. To view the results, proceed as follows:

#### 1 Open the waveform viewer.

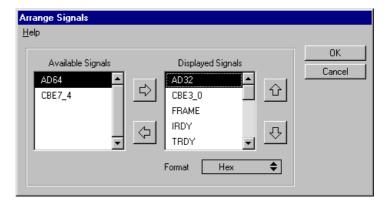

Your display will look different than that shown, but you can add and move signals within the display using the Arrange item from the Signals menu.

Note that the *berr* signal is labeled *prot\_rule* in the waveform viewer and is asserted at the triggerpoint. The error in this particular case is that the target did not respond with the first word of data within 16 clocks (LAT0).

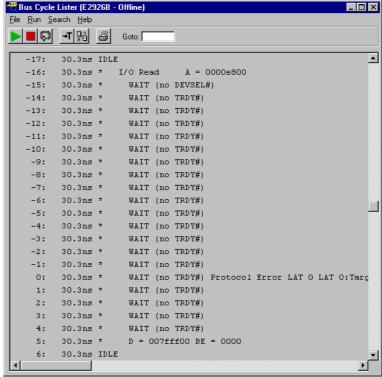

## **Detecting Setup/Hold Timing Violations**

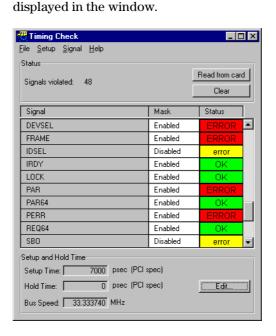

Independent of the Protocol Check, the Agilent PCI testcard's Timing Check can also examine all relevant 32/64-bit PCI signals for setup/hold time violations.

The Timing Check window is invoked by selecting *Timing Check* from the *Analyzer* menu. In this window, each signal that violates timing is marked separately, making it very quick and easy to identify those signals to probe first with an oscilloscope.

Once a bad signal has been identified, the timing check can be used to trigger the oscilloscope from the testcard's trigger I/O signals when the violation occurs. An adjustable measurement window allows up to  $2\,\mathrm{ns}$  variation from the PCI timing specification to check timing margins.

The timing check feature currently operates at speeds from 26 MHz to 35 MHz.

# **Guided Tour: Using the State Sequencer**

For some analysis tasks, a single level trigger is not sufficient. The Agilent PCI testcard provides very sophisticated trigger capabilities for advanced triggering needs.

- The *Performance* mode is used to capture traces for post-processed performance measurements. It allows you to set up an arbitrary trigger pattern but has a fixed storage qualifier that is optimized to capture performance-related information.

- The *Sequencer* mode allows you to set up a sophisticated trigger sequence that can consist of up to 8 sequence states and 255 transitions. The transition, trigger, and storage qualifier conditions can be specified individually for each transition.

The conditions are specified as boolean expressions built with up to 4 pattern terms. In addition, a counter is available that can be loaded and decremented under sequencer control. The terminal count signal of this counter is available in the conditions.

**NOTE** When the testcard is used through the Command Line Interface or with the C-API, up to 8 pattern terms are available, depending on the number of states used.

## **Changing to Sequencer Mode**

The PCI Analyzer can be changed to sequencer mode using the *Mode* command from the *Setup* menu to get a list of analyzer options. The trace memory depth can also be decreased from the actual size on the hardware to optimize the size and speed for uploaded trace files.

# **Setting Up the Trigger Sequencer**

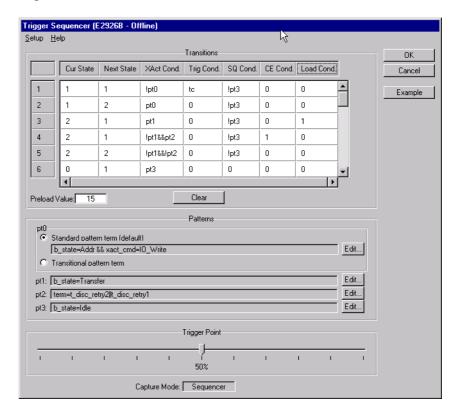

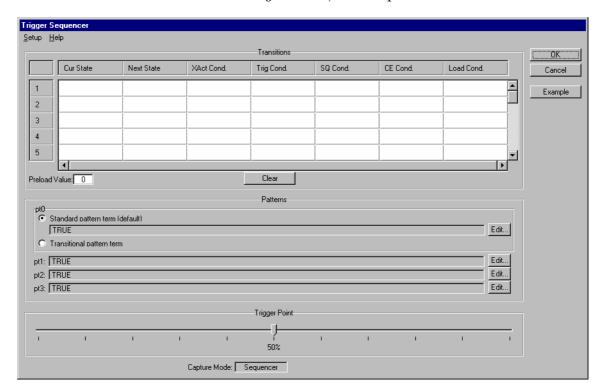

After you have set the trigger mode to *Sequencer*, open the Capture window to set up a trigger sequence. You can find the sample sequencer setup file shown below in seq.bst and the sample data in seq.wfm.

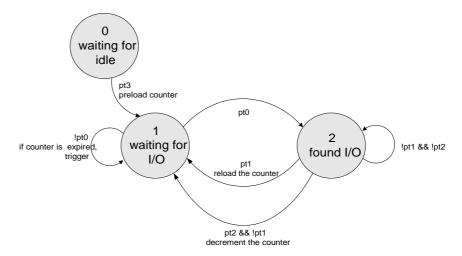

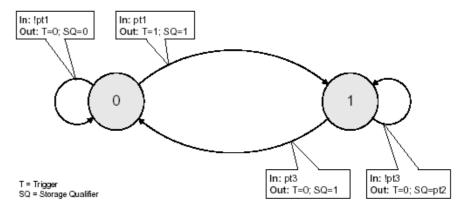

This example shows how to set up the trigger sequencer to trigger on 16 consecutive I/O transfers that are terminated with Target Retry before a successful one completes. The storage qualifier is set to store all cycles within transactions and ignore IDLE cycles.

The trigger sequencer is a user-programmable state-machine. In order to fill out the fields in the trigger sequencer window, it is helpful to draw a bubble diagram of the states and transitions first. The preload value of the feedback counter is set to 15 because the terminal count is -1.

where: pt0 = the address phase of an I/O cycle pt1 = a data transfer pt2 = a target indicating Retry pt3 = IDLE state And this is how the bubble diagram is implemented in the trigger sequencer:

# **Guided Tour: PCI Performance Analysis**

When PCI was initially used in the PC, it was a lot faster than previous buses (ISA, EISA) and there was no need to optimize PCI performance. This has changed. Now PCI is often the performance bottleneck, especially in high-performance servers that deal with lots of disk and network traffic. Due to the complex protocol there are many ways to improve PCI performance both on a component level as well as on a system level.

#### If you are:

- · designing a chip or an add-in card,

- integrating a system and you need to select between different add-in cards on the market,

- tuning system parameters in order to optimize overall performance,

you need a powerful, yet easy-to-use way to analyze the PCI performance to find out bottlenecks in your system and isolate the "bad guy" that potentially ruins the overall system performance.

There are two different approaches to PCI performance analysis and it depends on the application which one to use.

### • Real-Time Analysis

Real-time analysis is based on programmable counters and provides long term average measurements of performance numbers, latencies, etc. This method provides valuable information over long time periods about *what* the performance of your system is. It is limited, however, in its ability to provide meaningful insight to track down the root cause of performance issues.

The real-time analysis capabilities are available with the PCI Analyzer.

#### • Post-Processed Analysis

Post-processed analysis is based on 1 or more captured traces in the 64K/4M trace memory and provides detailed analysis of all performance aspects like bus utilization, command usage, burst efficiency, wait histograms for the whole bus as well as for a specific master/target pair. This information helps you to quickly determine why your performance problems may exist by allowing you to identify poorly performing PCI devices, drivers, or mismatched master/target pairs.

The post-processed analysis capabilities are available with the PCI Performance Optimizer (option 200).

This guided tour introduces the real-time analysis features provided by the PCI Analyzer.

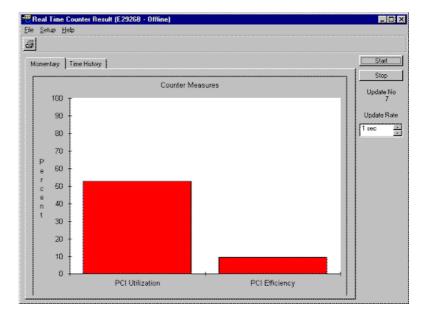

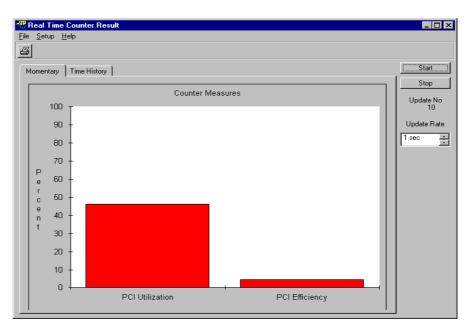

## **Identifying Overall System Performance**

Using the real-time performance measures of the Agilent PCI testcard provides very quick insight into what your overall system performance is.

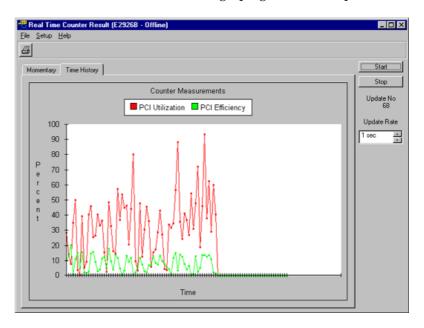

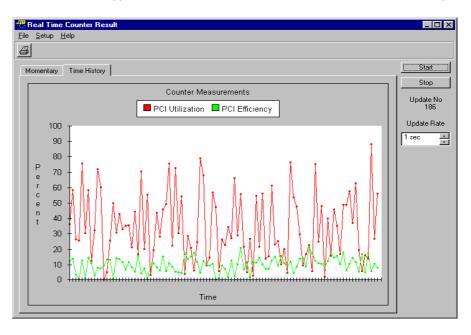

- 1 From the *Analyzer* menu select *Real Time Counter Result*.

- **2** Click the *Start* button.

Now you should see a simulation that shows a PCI Utilization and Efficiency measurement varying over time.

The *Momentary* tab shows the actual measurement values calculated from the performance counters after each update interval.

The *Time History* tab shows a running history of the counter values. Both performance measures can be set up with pre-defined measures or custom measures using a programmable sequencer.

**NOTE** The performance sequencers (one for each performance measure) have the same capabilities as the trigger sequencer, except that its outputs control the three counters that are available for each measure.

The graphical user interface provides access to two of the eight performance measures. The others can be accessed through the C-API.

## Setting Up a PCI Analyzer Test

Setting up a PCI Analyzer test includes the following steps:

- According to your test requirements you need to decide for one of the basic PCI Analyzer configurations (see "Possible PCI Analyzer Configurations" on page 39).

- To debug any problems in the power up phase of a system, you can completely hide the testcard from the system (see "Concealing the Card from the System" on page 42).

- You need to establish the connection between the user interface software and the testcard (see "Connecting to the Testcard" on page 43).

NOTE For information on how to insert the testcard into the system under test, please refer to the installation instructions shipped with the testcard.

# Possible PCI Analyzer Configurations

The Agilent E2925B PCI Analyzer basically consists of two components:

- · the testcard

- the graphical user interface software

The *testcard* plugs into the PCI bus of the system to be tested—or of the system hosting the device to be tested. The *software* can be run either on a remote system (a dedicated Control PC) connected via a fast host interface, or directly on the system under test.

The former configuration provides the following benefits:

- The user interface software does not interfere with the traffic generated to examine the system or device behavior.

- You can easily switch between different systems under test by just moving the testcard from one system to another.

- Different devices under test can easily be exchanged without changing the setup of the Control PC.

## **Dedicated Control PC**

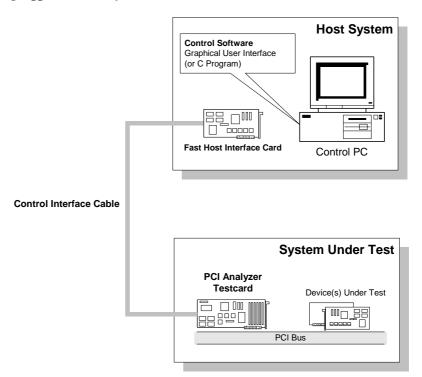

The following figure shows a typical configuration where the user interface software is running on the Control PC and controls the testcard plugged into the system under test.

When running extensive tests using more than one testcard, you only need one Control PC, which can be connected to the individual cards one after the other. There is no need for a permanent connection between testcard and user interface software. While the test on one testcard is still running, the Control PC can get connected to another testcard.

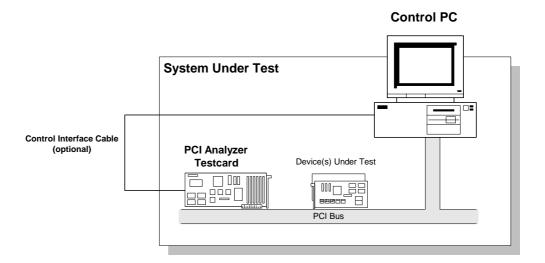

## **Software Running on System Under Test**

The following figure shows a configuration where the user interface software is running on the system under test itself. Thus, there is no extra Control PC required.

The PCI Analyzer software usually connects to the testcard directly via the PCI bus. However, you can also use the fast host interface—or the serial interface—for connection.

If there is more than one testcard installed in the system, all cards can be reached directly via the PCI bus.

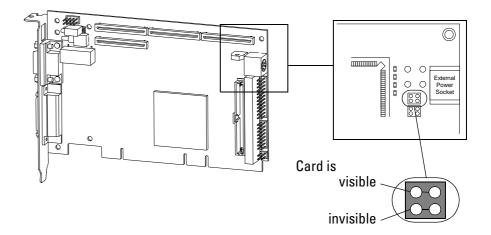

# **Concealing the Card from the System**

Concealing the card is useful, for example, for debugging a system that does not boot properly. You can run the PCI Analyzer to see what is happening on the PCI bus.

A jumper allows you to conceal the Agilent E2925B testcard from the system under test before you run your test. The card will not reply to any configuration access from BIOS and will, therefore, be completely invisible for the system.

**NOTE** If the card is invisible for the PCI system, you cannot control the card via the PCI port.

## **Connecting to the Testcard**

To transfer control information between control software and card, the card's control interfaces are used. The Agilent E2925B testcard features the following control interfaces:

#### • Fast Host Interface

This is the fastest connection to a testcard plugged into a remote system under test. The Fast Host Interface card coming with the PCI Analyzer must be plugged into the Control PC and connected to the parallel port on the testcard using the included bi-directional Centronics cable.

#### • PCI Port

The PCI port can be used for in-system analysis (when the software is running on the system under test). No cable or hardware required.

### • RS-232 Port

The RS-232 port of the testcard can be connected to the serial interface of the Control PC using the included RS-232 cable.

The Agilent E2925B testcard supports baud rates up to 57600 Bit/s. The actual value depends on the maximum baud rate supported by the serial interface of the Control PC.

Different testcards can be connected to the control software simultaneously using different control interfaces, and be activated alternately.

**NOTE** The user interface software also provides an Offline/Demo Mode. In this mode, all features of the software can be used without hardware, for example, for analysis of previously stored data or test preparation without hardware. No connection is established in this case.

## **How to Select the Connection**

After the hardware connection has been established, the user interface software supports you in identifying the available testcards and selecting the connection.

To connect to a testcard:

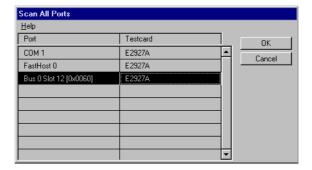

**1** From the Setup menu, select Testcard Configuration.

**2** Click the *Scan Ports* button.

The software scans all available control interfaces and lists the testcards available at the associated ports.

**3** Select one of the listed ports by double-clicking the entry in the list.

If no error messages occur, the connection has been established successfully, and your selection will be displayed in the Testcard Configuration dialog box.

In case of any problem, refer to "Connection Troubleshooting" on page 45.

**NOTE** Using the *PCI Browse* button in the Testcard Configuration dialog box, you can select from a list of devices found on the PCI bus of the Control PC.

Using the *Ping* button, you can check the connection between the user interface software and the testcard on the selected port.

## **Connection Troubleshooting**

If the selected connection cannot be established, an error message is displayed. Read the error message carefully and follow the steps described in the error message to eliminate the problem.

The following table provides additional information:

Table 1 Troubleshooting Tips

| Error Mes-<br>sage    | Reason                                 | Help                                                                                                                  |  |

|-----------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| Version<br>mismatch   | Version conflict.                      | Refer to "Updating the<br>Testcard" on page 103.                                                                      |  |

| Port is not connected | Cable loose or disconnected.           | Ensure that the cable is properly connected.                                                                          |  |

|                       | Wrong type of RS-232 cable or adapter. | Use a adapter shipped with the testcard.                                                                              |  |

|                       | Wrong bi-directional centronics cable. | Use the cable shipped with the testcard.                                                                              |  |

|                       | Wrong port settings.                   | Correct the port settings in the Testcard Configuration dialog box.                                                   |  |

|                       | Wrong setting of user jumper.          | Correct the setting of the user jumper, refer to Agilent E2925B User's Manual, "Concealing the Card from the System". |  |

You can check the connection at any time while tracking down the error by selecting *Check Connection* from the *Setup* menu.

## **Analyzing Protocol Violations**

When bringing up or debugging devices or complete systems, you have to check whether all devices keep to the protocol rules defined by the PCI Specification.

The PCI Analyzer provides an onboard protocol observer that monitors the PCI bus in real time to detect any protocol violations.

## **Protocol Observation**

The Agilent E2925B testcard provides an hardware-implemented protocol observer that monitors the PCI bus to detect protocol violations.

**Operation Principles**

The protocol observer monitors the PCI bus in real time with 100 % observation time. The PCI bus is monitored continuously while the testcard is powered.

The protocol observer monitors 53 protocol rules simultaneously. These rules refer to the rules of the PCI specification. Each rule can be individually masked to disable its observation (for a list of monitored protocol rules, refer to "List of Rules Observed by the PCI Analyzer" on page 105).

Multiple violations may occur in a sequence because a protocol violation of a PCI device will often cause malfunctions of other devices. Therefore, the protocol observer stores the first protocol violation and also counts and lists subsequent violations.

**Processing Protocol Violations**

A detected protocol violation can be used as input for pattern terms (*berr* signal), for example, to trigger a data capture.

# How to Set Up the Protocol Observer

The protocol observer is controlled from the Protocol Check window. This window allows you to mask and unmask rules, and displays the contents of the error register.

To set up the protocol observer:

From the *Analyzer* menu, select *Protocol Check*.

The current observation settings and results are uploaded from the testcard and displayed in the window.

The *Status* group provides a result summary, showing the number of rules that have been violated and identifying the rule that has been violated first. The *Status* column in the *Rule* table shows error flags for each individual rule.

**2** Select the rules to be monitored for your test by masking those rules that are not relevant.

The current status for the individual rules is shown in the *Mask* column. To modify the mask:

- Click an entry in the *Mask* column to toggle its state (enabled/disabled).

- From the *Rule* menu, select *Enable All* or *Disable All* to set the state for all rules at once.

**3** After changing the rule mask, click the *Clear* button to reset the protocol observer.

**NOTE** Double-clicking an entry in the Rule column pops up a description of that rule.

## **Watching the Protocol Observer**

The protocol observer monitors the PCI bus continuously while the testcard is powered. The results displayed in the Protocol Observer window, however, are only updated on demand. Therefore, there is the need to upload the result data from the testcard, and maybe to reset the observer (this is, to clear the results).

## **How to Upload Protocol Observer Results**

The results of the protocol observer are not automatically uploaded to be displayed in the Protocol Observer window.

To upload the current state of the testcard registers to the display:

- 1 If the Protocol Check window is not displayed yet, select *Protocol Check...* from the *Analyzer* menu.

- **2** Click the *Read from card* button.

The current data will be uploaded from the testcard and be displayed in the window.

## **How to Reset the Protocol Observer**

To restart a test, for example after changing the masking of protocol rules or for detecting the repeated occurrence of a protocol violation, you can reset the protocol observer.

To reset the protocol observer:

- **1** If the Protocol Check window is not displayed yet, select *Protocol Check...* from the *Analyzer* menu.

- **2** Click the *Clear* button.

This sets all rule states to OK, the total of *Rules violated* to 0, and the *First violated* rule to none. The protocol observer continues immediately. If a protocol violation cannot be cleared, this indicates that the violation still is present on the bus.

**NOTE** You can set the run options to clear the protocol check results with each start of a data capture.

## **Analyzing Timing Violations**

When bringing up or debugging devices or complete systems, you have to check whether all devices keep to the timing rules defined by the PCI Specification.

The PCI Analyzer provides an onboard timing checker that monitors the PCI bus in real time to detect any timing violations. The timing check indicates an error when a PCI signal change is detected at a moment at which the PCI Specification calls for stable signals.

**NOTE** At the time being the timing check is only available for 33 MHz PCI busses

## **Observed Timing Rules**

**Operation Principles**

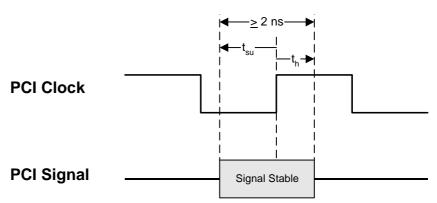

When checking for timing violations, the Agilent E2925B testcard uses the set-up time  $t_{\rm su}$  and the hold time  $t_h$  of each synchronous bus signal to determine the time window in which a PCI signal must be stable.

The permissible values of set-up and hold time are given by the PCI Specification.

The timing check automatically measures the bus clock frequency and checks against the permissible values. This is the default behavior. However, you can also adapt the timing checkerto special requirements by changing the range of permissible values.

**Processing Timing Violations**

A detected timing violation can be used as input for pattern terms (*timing\_err* signal), for example, to trigger a data capture.

## **Timing Check Limitations**

Keep the following in mind when checking for timing violations:

### • List of checked signals

Some signals are excluded from timing checks due to their particular timing behavior. For a list of checked signals refer to "b\_signaltype (for Timing Check)" in the C-API/PPR Reference.

### • Typical measurement accuracy

The typical measurement accuracy is below 250 ps.

However, the measurement accuracy can be guaranteed only if both setup and hold time values are set to the default values given by the PCI Specification.

The measurement accuracy also depends on the clock frequency and the environmental temperature.

### • Clock frequency

The PCI clock must be lower or equal than 33 MHz and is not allowed to vary more than 0.5 %. Note that "Green PCs" may switch down clock frequency to decrease power consumption. When this happens during a timing check, it will result in a timing error.

The best measurement accuracy can be guaranteed only if the clock frequency is 33 (calibration point).

#### • Environmental temperature

The environmental temperature must be between 20 and 30 °C, otherwise the typical measurement accuracy cannot be guaranteed.

## **Adapting the Timing Checker**

You can adapt the timing check to your test requirements by adjusting the permissible values, thus relaxing or tightening the measurement constraints.

The following table shows the PCI Specification values and the value ranges of the timing check:

**Table 2** Timing Parameter Values

| Timing          | 33 MHz PCI Bus (29 35 MHz) |                    |  |

|-----------------|----------------------------|--------------------|--|

| Parameter [ns]  | PCI Spec                   | Timing Check Range |  |

| t <sub>su</sub> | 7                          | 5 9                |  |

| t <sub>h</sub>  | 0                          | -2 +2              |  |

The following expression must apply:

$$2 \text{ ns} \leq t_{su} + t_h \leq \frac{1}{2 \times f} - 2 \text{ ns}$$

(f = frequency in Hz)

Within the timing check ranges, you can vary the values in steps of  $250~\mathrm{ps}$ .

# How to Set Up the Timing Checker

The timing checker is controlled from the Timing Check window. This window allows you to mask and unmask signals, and displays timing check results.

To set up the timing checker:

From the Analyzer menu, select Timing Check.

The current settings and results are uploaded from the testcard and

The *Status* group provides a result summary, showing the number of signals that have violated timing rules. The *Status* column in the *Signal* table shows error flags for each individual signal.

**2** Select the signals to be checked for your test by masking those signals that are not relevant.

The current status for the individual signals is shown in the *Mask* column. To modify the mask:

- click an entry in the Mask column to toggle its state (enabled/disabled), or

- from the *Signal* menu, select *Enable All* or *Disable All* to set the state for all signals at once.

**3** After changing the signal mask, click the *Clear* button to reset the timing checker.

**NOTE** The mask only affects the trigger—the status of a disabled signal is still displayed.

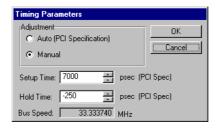

## **How to Modify Timing Limits**

By default, the timing checker checks against the permissible values of set-up and hold time as given by the PCI Specification. These values can be adapted to meet custom testing requirements.

The current values and the measured PCI bus clock are displayed in the Timing Check window (see "How to Set Up the Timing Checker" on page 54).

To modify the timing limits:

**1** In the Timing Check window click the *Edit* button.

**2** In the *Adjustment* group, select *Manual* and edit the parameter values,

or

select *Auto* to select the default values defined in the PCI Specification (depending on the PCI bus speed).

3 Click OK.

The accumulated error registers of the timing checker are cleared automatically, and the timing check continues with the new values.

## **Watching the Timing Checker**

The timing checker monitors the PCI bus continuously while the testcard is powered. The results displayed in the Timing Check window, however, are only updated on demand. Therefore, there is the need to upload the result data from the testcard, and maybe to reset the checker (this is, to clear the results).

## **How to Upload Timing Checker Results**

The results of the timing checker are not automatically uploaded to be displayed in the Timing Check window.

To upload the testcard registers to the display:

- 1 If the Timing Check window is not displayed yet, select *Timing Check...* from the *Analyzer* menu.

- **2** Click the *Read from card* button.

The current data will be uploaded from the testcard and displayed in the window.

## **How to Reset the Timing Checker**

To restart a test, for example after changing the signal mask, you can reset the timing checker by clearing the results.

To reset the timing checker:

- **1** If the Timing Check window is not displayed yet, select *Timing Check...* from the *Analyzer* menu.

- **2** Click the *Clear* button.

This sets the results for all signals to OK and the total of Signals violated to 0.

The timing check is restarted immediately. Therefore, a displayed timing error will not disappear by clicking the *Clear* button, if the error is still present.

**NOTE** You can set the run options to clear the timing check results with each start of a data capture.

## **How to Debug Timing Violations**

If a timing violation has been detected, you can use the trigger I/O on the Agilent E2925B testcard and an oscilloscope for in-depth analysis:

#### 1 Select a signal

Use the Timing Check window to set the focus on a signal line on which a timing violation has been detected. Enable this signal and disable all remaining signals.

### 2 Set up the trigger I/O sequencer

A command line script shipped with the Agilent E2925B testcard software sets up the trigger I/O sequencer. When the script runs, a positive pulse is issued on trigger I/O 0 after a timing error.

To run the script, enter the following in the command line interface:

do ..\samples\gui\tmgchktr.cli

#### 3 Connect an oscilloscope

Connect an oscilloscope's trigger input to the Agilent E2925B testcard's trigger I/O line 0, and connect the oscilloscope's inputs to the PCI signal of interest and to the PCI clock.

#### 4 Run the Timing Check

Generate traffic and run the PCI Analyzer of the Agilent E2925B testcard.

### 5 Analyze the waveform

Watch the oscilloscope. Look for glitch, overshoot, undershoot, ringing, marginal voltage levels, and so on. Try also various locations on the signal's PCI trace, such as locations close to the driver or to the receiver of the signal.

## Analyzing PCI Performance

In the bring-up and debug phase of a PCI device or a system (containing PCI bus and PCI devices), you need to evaluate the performance of the device or system under test.

The PCI Analyzer supports real-time performance measurement by providing predefined, standardized performance measures, such as PCI efficiency and PCI utilization.

These measures can be set up easily. The results are shown in graphical charts.

Performance measurement is based on counting certain events on the PCI bus. For the predefined measures, the counters are set up automatically.

For more advanced measurements, you can program the counters by yourself, providing full flexibility.

The Performance Optimizer (option #200) expands the possibilities of real-time performance measurements, by providing means for detailed post-processed analysis.

**Generating PCI Traffic**

The PCI Analyzer can measure any kind of PCI traffic, regardless of how it was generated. However, it is useful to generate traffic in a controlled way for reproducibility in case of troubleshooting or root cause analysis.

Typically, you will use benchmark tests to generate traffic for this purpose.

# Predefined Performance Measures

For real-time performance measurements, the PCI Analyzer counts occurrences of predefined events or sequences of events on the PCI bus. The results are derived and displayed in real time.

#### **Available Measures**

The following predefined measures are provided by the PCI Analyzer:

#### • Throughput

Throughput is the amount of transferred data per time. It is measured in Mbyte per second. When running a real-time measurement, this value is displayed in percent of the maximum value (for 33 MHz systems: 132 Mbyte per second in a 32-bit system, 264 Mbyte per second in a 64-bit system).

#### • Utilization

Utilization measures the relation between busy bus time and total bus time during a transfer.

### • Efficiency

Efficiency is a measure of how well the bus is used. It is the most important value when considering PCI performance.

The efficiency of a transfer is the relation between the amount of data that was *really* transferred and the amount of data that could have been transferred by the used cycles of that transfer (busy clocks). Efficiency is derived from throughput and utilization. An efficiency near 100 % means that a device made best use of the time it occupied the bus (utilization) by transferring as much data as possible during that time frame (high throughput).

#### • Retry Rate

This is the ratio between retry transactions and all transactions.

## How to Select Predefined Performance Measures

The PCI Analyzer can calculate two real-time measures simultaneously. The test results are displayed side by side on screen.

To select the predefined performance measures to be used:

1 From the Analyzer menu, select Real Time Counter Setup.

- **2** Check the *Relative Values (Ratio)* option (this is the default). When selecting *Absolute Values (Event Count)*, the pure counter values will be displayed instead of the predefined measures.

- **3** From the *Setting for* selection list, select *Measure 1*.

- **4** From the *Predefined Measures* selection list, choose the predefined measure to be calculated and displayed for measure 1.

- 5 Make sure *Accumulative* is not checked.

The measured values will be reset after each measurement time interval. This allows you to better observe peaks. Otherwise the values will be accumulated over time.

- **6** Repeat steps 3 to 5 for *Measure 2*.

- 7 Click OK.

The new settings will be used the next time you start a performance measurement.

## **How to Run a Performance Measurement**

After completing the setup the real-time performance measurement can be started.

To run a real-time performance measurement:

- 1 From the Analyzer menu select Real Time Counter Result.

- **2** To set the time interval in which the display is to be updated, enter an *Update Rate* between 1 and 60 seconds.

- **3** Click the *Start* button.

This shows the results of the selected measures per time interval. If you have selected *Accumulative* in the Real Time Measurement Setup, the results will be accumulated.

The diagram on the Momentary tab shows the current values of the selected measures.

**4** To see the result history over time, select the *Time History* tab. You can toggle between both tabs while the measurement is running.

**5** To stop the measurement, click the *Stop* button and close the window.

# Advanced Performance Measures

The PCI Analyzer can calculate and display two performance measures simultaneously. Each measure can either show one of the predefined measures or be programmed manually for advanced performance measurements.

## **Operation Principles**

The performance measures of the Agilent E2925B testcard employ programmable counters, which are controlled by sequencers to count signal states or sequences of signal states. For an advanced real-time measurement, you can *manually* specify the events to be counted and program the sequencers. For an example, refer to "Sample Advanced Performance Setup" on page 66.

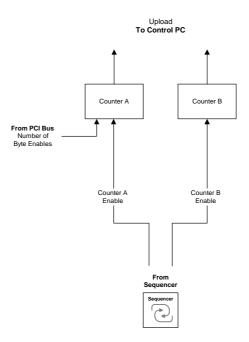

For each performance measure there are two programmable counters. The following figure shows—for one performance measure—how the counters are controlled by the sequencer. Additionally, there is a reference counter counting the bus cycles.

### **Incrementing the Counters**

By means of programmable conditions, the sequencer enables the counters to be incremented:

- If enabled, counter B is incremented by 1 per bus cycle.

- If enabled, counter A is either incremented by 1 per bus cycle, or by the number of byte enables currently set (0...4 for 32-bit, 0 ... 8 for 64-bit accesses).

This feature is controlled by the *Ctr A counts Byte Enable* check box in the Real Time Measurement Setup dialog box. Counting byte enables allows you to count actually transferred data (and not only data phases).

#### **Counter Sequencers**

The behavior of the counter sequencers is determined by a sequencer description table and pattern terms in the same way as the data capture is controlled by the trace memory trigger sequencer.

However, the sequencer's outputs are the count enables for the counters A and B. The count enables are changed while the sequencer switches through its states as described by the transitions. Its output conditions determine whether or not the referenced counter is incremented.

If *Relative Values* is selected in the Real Time Measurement dialog box, the performance measure is calculated as the ratio of counter A and B, using counter A as *nominator* counter and counter B as *denominator* counter.

### NOTE

The counter C in the *Transitions* table in the Performance Counter Sequencer dialog box is a feedback counter, which can be used for programming sequencer loops.

## **PCI Clock Reference Counter**

The testcard also provides a 64-bit wide PCI clock reference counter. It counts PCI clocks only, and is started, stopped and updated together with the other counters. It is used as a time reference for the performance measures and is displayed only if *Absolute Values (Event Count)* is selected in the Real Time Measurement Setup dialog box.

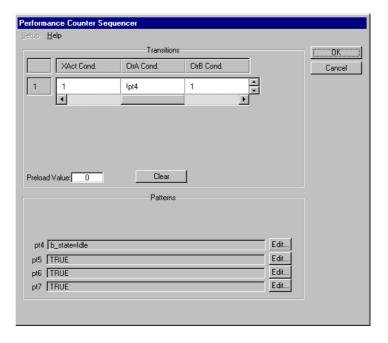

# **Sample Advanced Performance Setup**

To explain how to program an advanced performance measure, an example shows how to measure the proportion of non-idle cycles in PCI traffic.

The required sequencer setup is quite simple. It uses the **pattern term** pt4 as follows:

• pt4: b\_state=Idle

This makes pattern term pt4 sensitive to idle cycles.

The **sequencer** of performance measure 1 is programmed to remain in state 0 only, incrementing counter A and B if their enable conditions are true:

- Counter A must be incremented with each non-idle cycle. Therefore, pattern term pt4 must be inverted.

- Counter B must be incremented with each clock cycle.

The sequencer description table must be set up as follows:

Table 3

Sample Sequencer Description Table

| State | Next State | Transition<br>Condition | Counter A<br>Enable<br>Condition<br>(Output) | Counter B<br>Enable<br>Condition<br>(Output) |

|-------|------------|-------------------------|----------------------------------------------|----------------------------------------------|

| 0     | 0          | 1                       | !pt4                                         | 1                                            |

**NOTE** In the table above, only those columns are shown that need to be programmed for the example.

## How to Set Up the Measures for the Example

To program the counter sequencer according to the example, proceed as follows:

**1** From the *Analyzer* menu, select *Real Time Counter Setup*.

- **2** Check the *Relative Values (Ratios)* option.

Otherwise, the absolute values of the counters would be displayed.

- **3** From the *Setting for* selection list, select *Measure 1*.

- 4 Ensure that *Accumulative* is deactivated. The software calculates the ratio of the two current counter values. Otherwise, the software would calculate the ratio of the accumulated counter values over the testing time.

- **5** Select Advanced Setup.

- **6** If you wish to have a title for the measure on the Counter Result window, enter a name for your measurement in the *Title* text field.

- **7** Ensure that *Ctr A counts Byte Enable* is deactivated. Otherwise, counter A will count byte enables to measure the amount of transferred data.

## How to Program the Counter Sequencer for the Example

After basically setting up the measures for the example, go on to program the counter sequencer as required:

1 In the Real Time Measurement Setup dialog box, click the *Edit Sequencer* button.

The Performance Counter Sequencer dialog box will be opened.

Now edit the sequencer description table and the pattern term:

- **1** Enter the required conditions and terms in the *Transitions* table. You can scroll horizontally and vertically through the sequencer table.

- **2** Leave the *Preload Value* at its default value.

The preload value allows you to specify an initial value for the feedback counter C. This is used to wait for a certain number of events before transition output.

**3** Click the *Edit...* button of pattern term pt4 to edit the pattern. The Pattern Editor dialog box will be opened (see "*How to Specify a Trigger Pattern*" on page 77).

For the example, set b\_state=Idle for pattern term pt4.

NOTE pt4 to pt7 are associated with Measure 1.

pt8 to pt11 are associated with Measure 2.

- **4** Click OK to close the Performance Counter Sequencer dialog box.

- ${f 5}$  Click OK to close the Real Time Measurement Setup dialog box.

Now you can start the real-time measurement using your counter setup as described in "How to Run a Performance Measurement" on page 62.

## Capturing Data In The Trace Memory

The PCI Analyzer records information like PCI signals and bus states in its trace memory. The information is stored in one trace memory line per PCI clock cycle. By default, the Agilent E2925B testcard stores 64 k lines. With the option #100, you can expand the trace memory to 4 M lines.

### **Controlling the Data Capture**

The PCI Analyzer provides all features required to make optimum use of the available memory depth.

- The trigger allows you to start capturing data when a programmable trigger event has occurred. Furthermore, by specifying the triggerpoint you can additionally control the number of bus cycles stored before and after the trigger event.

- Storage qualification allows you to selectively capture only certain types of data. For example, you can focus on accesses to a particular device, or on data transfers only.

- A heartbeat function allows you to implement a watchdog by triggering on a particular event that does *not* occur after a programmable time.

- Trigger and storage qualifier can be controlled by a programmable sequencer.

#### **Using the Data Capture**

Data stored in the trace memory can be displayed at different levels of abstraction: as waveforms, bus cycles, or transactions.

You can not only analyze the data in terms of PCI behavior, but also implement functional tests like data compares. For example, if you are debugging a LAN interface, you could capture all of the blocks of data going into and coming out of the card. Once this data has been captured, you can analyze it further for debugging.

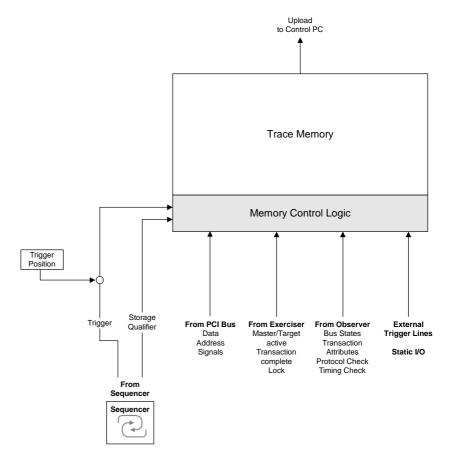

# **Data Stored In The Trace Memory**

The trace memory on the Agilent E2925B testcard stores all PCI signals and bus states, the Exerciser states, and additional information. The trace data is stored in one trace memory line for each PCI clock cycle and can be used for low-level debugging and understanding of bus traffic.

**Trace Memory Components**

The capture is controlled by the trace memory *trigger* and the *storage* qualifier.

These are in turn controlled by the programmable *trace memory trigger sequencer*. This sequencer implements a state machine, allowing to define individual trigger and storage qualifier conditions for each state.

The sequencer is only available if the capture mode *Sequencer* has been selected.

The figure below gives an overview of the components building the trace memory.

Agilent E2925B PCI Analyzer User's Guide, August 2002

#### **Recording Data**

The trace memory is a circular memory that is filled continuously while the Analyzer is running. The storage qualifier controls which bus states are recorded. If one or more lines are filtered, a gap information is stored instead.

Recording is stopped after the trigger event has occurred. The trigger position specifies the amount of pre-trigger and post-trigger data to be kept in the data capture.

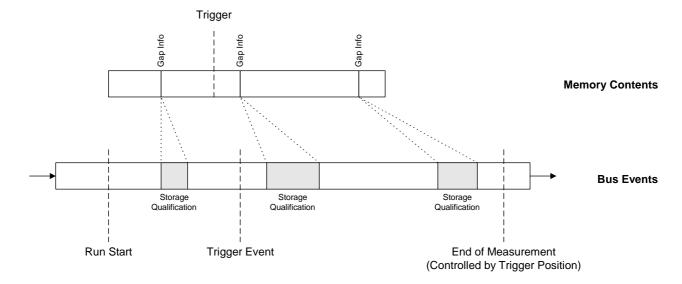

The following figure illustrates these mechanisms:

The lower bar in the figure represents events on the bus. Some of them do not meet the storage qualifier condition and are therefore filtered (gray areas). Gap information is stored instead of the events.

After the Analyzer has been started, the memory is filled. Because the trace memory is a circular memory, previously captured states will be overwritten until the trigger event occurs.

Stored data is represented by the upper bar in the figure: not suppressed bus events and gap information. When the trigger event occurs, the trace memory continues to be filled until the specified amount of post-trigger information is stored.

#### **Uploading Data**

At this time, the measurement is complete, and the trace memory contents are uploaded. They can be displayed in the waveform viewer, the bus cycle lister, and the transaction lister.

To reduce the upload time you can specify the size of the trace memory to be uploaded. This does not reduce the amount of data that is recorded.

NOTE If the Analyzer is set up to fill the trace memory after a trigger event and the event does not occur, stopping the Analyzer sets an artificial triggerpoint. The trace memory will then contain 100 % pre-trigger history. The last captured state is the state before the Analyzer has been stopped.

Nevertheless, the trace memory can still be empty if no samples were taken because of the storage qualification.

## **Capture Mode**

The availability of the sequencer depends on the selected capture mode. The Agilent E2925B testcard provides the following modes for capture control:

#### • Standard

In the standard mode, the trace memory trigger and storage qualifier are directly controlled by pattern terms. Pattern terms are programmable pattern recognizes. If the programmed pattern is found on the bus, the pattern term signals

- the trigger to initiate the sampling, or

- the storage qualifier to capture the current sample.

### • Sequencer

In the sequencer mode, the trigger sequencer controls the trace memory's trigger and storage qualifier. The sequencer detects sequences of patterns. To detect the patterns, it uses pattern terms as input. Each state of the sequence can be used to control the sequencer's output, trigger and storage qualifier.

#### • Performance

The performance mode is only available if the PCI Optimizer (option #200) has been installed.

In the performance mode, the storage qualifier is automatically programmed as required for performance measurements. A trigger can be set up to start the measurement.

## **Setting Up the Data Capture**

- Select the capture mode.

- Set up the trigger.

If required, specify a trigger pattern.

- Set up the storage qualifier.

If required, select transactions and states to be stored in the trace memory.

For more advanced measurements the sequencer can be programmed as described in "Setting Up the Trigger Sequencer" on page 81.

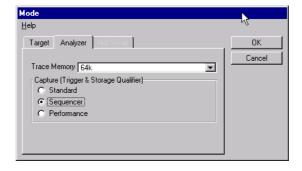

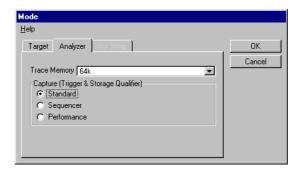

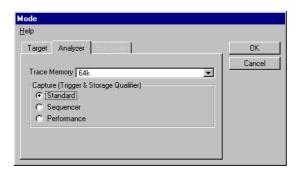

## **How to Select the Capture Mode**

Start setting up the data capture by specifying the amount of data to be uploaded after the trigger event, and by selecting the capture mode:

1 From the Setup menu, select Mode and then the Analyzer tab.

- **2** From the *Trace Memory* selection list, choose the amount of data to be uploaded to the user interface software after the trigger event. Choose a small size in order to minimize uploading time.

- **3** In the *Capture (Trigger & Storage Qualifier)* section, select the required mode.

- 4 Click OK.