#### Motorola MVME177-003 **Single Board Computer**

In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/62702-5

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

Your definitive source for quality pre-owned equipment.

**Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# 177Bug Diagnostics User's Manual

V177DIAA/UM1

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

No part of this material may be reproduced or copied in any tangible medium, or stored in a retrieval system, or transmitted in any form, or by any means, radio, electronic, mechanical, photocopying, recording or facsimile, or otherwise, without the prior written permission of Motorola, Inc.

It is possible that this publication may contain reference to, or information about Motorola products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

#### **Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

#### **Preface**

The 177Bug Diagnostics User's Manual provides information on using the MVME177Bug diagnostics.

This edition (/UM1) applies to 177Bug versions 1.2 and up only, and is usable with all versions of the MVME177 series of microcomputers.

Use of the debugger, the debugger command set, use of the one-line assembler/disassembler, and system calls for the Debugging Package are all contained in the Debugging Package for Motorola 68K CISC CPUs User's Manual (68KBUG1/Dx and 68KBUG2/Dx).

This manual is intended for anyone who designs OEM systems, supplies additional capability to an existing compatible system, or uses the 177Bug for experimental purposes. A basic knowledge of computers and digital logic is assumed.

In addition, commands that act on words or longwords over a range of addresses may truncate the selected range so as to end on a properly aligned boundary.

To use this manual, you should be familiar with the publications listed in the *Related Documentation* section in Appendix A of this manual.

#### Conventions

The following conventions are used in this document:

#### bold

is used for user input that you type just as it appears. Bold is also used for commands, options and arguments to commands, and names of programs, directories, and files.

italic

is used for names of variables to which you assign values. Italic is also used for comments in screen displays and examples.

#### courier

is used for system output (e.g., screen displays, reports), examples, and system prompts.

#### <Return>

represents the Enter or Return key.

#### **CTRL**

represents the Control key. Execute control characters by pressing the CTRL key and the letter simultaneously, e.g., CTRL-d.

#### **Manual Terminology**

Throughout this manual, a convention has been maintained whereby data and address parameters are preceded by a character which specifies the numeric format as follows:

- S hexadecimal character

- % binary number

- & decimal number

Unless otherwise specified, all address references are in hexadecimal throughout this manual.

An asterisk (\*) following the signal name for signals which are *level significant* denotes that the signal is *true* or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are *edge significant* denotes that the actions initiated by that signal occur on high to low transition.

In this manual, *assertion* and *negation* are used to specify forcing a signal to a particular state. In particular, *assertion* and *assert* refer to a signal that is active or *true*; *negation* and *negate* indicate a signal that is inactive or *false*. These terms are used independently of the voltage level (high or low) that they represent.

Data and address sizes are defined as follows:

- $\Box$  A *byte* is eight bits, numbered 0 through 7, with bit 0 being the least significant.

- ☐ A *word* is 16 bits, numbered 0 through 15, with bit 0 being the least significant.

- ☐ A *longword* is 32 bits, numbered 0 through 31, with bit 0 being the least significant.

The computer programs stored in the Read Only Memory of this device contain material copyrighted by Motorola Inc., first published 1990, and may be used only under a license such as the License for Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

The software described herein and the documentation appearing herein are furnished under a license agreement and may be used and/or disclosed only in accordance with the terms of the agreement.

#### Safety Summary Safety Depends On You

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Motorola, Inc. assumes no liability for the customer's failure to comply with these requirements.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. The equipment is supplied with a three-conductor ac power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter, with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

#### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

#### **Keep Away From Live Circuits.**

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone.

Do not attempt internal service or adjustment unless another person capable of rendering first aid and resuscitation is present.

#### Use Caution When Exposing or Handling the CRT.

Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. Handling of the CRT should be done only by qualified maintenance personnel using approved safety mask and gloves.

#### Do Not Substitute Parts or Modify Equipment.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that safety features are maintained.

#### **Dangerous Procedure Warnings.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

The software and documentation are copyrighted materials. Making unauthorized copies is prohibited by law. No part of the software or documentation may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means without the prior written permission of Motorola, Inc.

This equipment generates, uses, and can radiate electromagnetic energy. It may cause or be susceptible to electro-magnetic interference (EMI) if not installed and used in a cabinet with adequate EMI protection.

Motorola and the Motorola symbol are registered trademarks of Motorola, Inc.

Zeropower<sup>TM</sup> is a trademark of Thompson Components.

All other products mentioned in this document are trademarks or registered trademarks of their respective holders.

#### DISCLAIMER OF WARRANTY

Unless otherwise provided by written agreement with Motorola, Inc., the software and the documentation are provided on an "as is" basis and without warranty. This disclaimer of warranty is in lieu of all warranties whether express, implied, or statutory, including implied warranties of merchantability or fitness for any particular purpose.

© Copyright Motorola, Inc. 1995 All Rights Reserved

Printed in the United States of America August 1995

# **Contents**

#### **CHAPTER 1 General Information**

Description of 177Bug1-1

Debug and Diagnostic Commands1-1

177Bug Implementation1-2

User Interface1-2

Language1-2

Start-Up1-2

ROMboot1-7

Memory Requirements1-7

#### **CHAPTER 2** Using the Diagnostics

Introduction2-1 **Running Commands2-1** Command Entry2-1 Diagnostic Commands2-2 AEM - Append Error Messages Mode2-3 CEM - Clear Error Messages2-3 CF - Test Group Configuration Parameters Editor2-3 DE - Display Error Counters2-4 DEM - Display Error Messages2-4 DP - Display Pass Count2-4 HE - Help2-4 HEX - Interactive Help2-6 MASK - Self Test Mask2-6 SD - Switch Directories2-6 ST - Self Test2-7 ZE - Clear Error Counters2-7 ZP - Zero Pass Count2-7 Test Prefixes2-8 LA - Loop Always2-8 LC - Loop-Continue2-8 LE - Loop-On-Error2-9

| LF - Line Feed Suppression                | 2-9    |

|-------------------------------------------|--------|

| LN - Loop Non-Verbose                     | 2-9    |

| NV - Non-Verbose                          | 2-9    |

| SE - Stop-On-Error                        | 2-9    |

|                                           |        |

| CHAPTER 3 Diagnostic Tests                |        |

| Introduction                              | 3-1    |

| Running the Tests                         | 3-1    |

| RAM - Local RAM,                          |        |

| SRAM - Static RAM                         | 3-3    |

| Configuration Parameters                  | 3-3    |

| ADR - Memory Addressing                   |        |

| ALTS - Alternating Ones/Zeros             |        |

| BTOG - Bit Toggle                         |        |

| CODE - Code Execution/Copy                |        |

| PATS - Data Patterns                      | . 3-10 |

| PED - Local Parity Memory Error Detection | 3-11   |

| PERM - Permutations                       |        |

| QUIK - Quick Write/Read                   |        |

| REF - Memory Refresh Testing              | . 3-15 |

| RNDM - Random Data                        |        |

| RTC - MK48T08 Real Time Clock             | . 3-18 |

| Configuration Parameter                   | 3-18   |

| ADR - NVRAM Addressing                    | . 3-19 |

| CLK - Check Real Time Clock               |        |

| RAM - Battery Backed-Up SRAM              | . 3-23 |

| PCC2 - Peripheral Channel Controller      |        |

| ADJ - Prescaler Clock Adjust              | . 3-25 |

| FAST - FAST Bit                           | . 3-26 |

| GPIO - GPIO Interrupts                    |        |

| LANC - LANC Interrupts                    | . 3-29 |

| MIEN - MIEN Bit                           | . 3-31 |

| PCLK - Prescaler Clock                    |        |

| PRINTA - Printer ACK Interrupts           |        |

| PRINTB - Printer FAULT Interrupts         |        |

| PRINTC - Printer SEL Interrupts           |        |

| PRNTD - Printer PE Interrupts             | . 3-39 |

|     | PRNTE - Printer BUSY Interrupts3                 | -41 |

|-----|--------------------------------------------------|-----|

|     | REGA - Device Access                             | -43 |

|     | REGB - Register Access3                          | -44 |

|     | TMR1A - Timer 1 Counter3                         | -45 |

|     | TMR1B - Timer 1 Free-Run3                        | -46 |

|     | TMR1C - Timer 1 Clear On Compare3                | -47 |

|     | TMR1D - Timer 1 Overflow Counter                 | -48 |

|     | TMR1E - Timer 1 Interrupts                       | -49 |

|     | TMR2A - Timer 2 Counter                          | -51 |

|     | TMR2B - Timer 2 Free-Run                         | -52 |

|     | TMR2C - Timer 2 Clear On Compare3                | -53 |

|     | TMR2D - Timer 2 Overflow Counter                 |     |

|     | TMR2E - Timer 2 Interrupts                       | -55 |

|     | VBR - Vector Base Register                       |     |

| MC  | CECC - ECC Memory Board3                         | -58 |

|     | Configuration Parameters3                        | -58 |

|     | CBIT - Check-Bit DRAM3                           | -60 |

|     | EXCPTN - Exceptions3                             | -62 |

|     | MBE - Multi-Bit-Error                            |     |

|     | SBE - Single-Bit-Error                           | -64 |

|     | SCRUB - Scrubbing3                               |     |

| ME  | MC1, MEMC2 - MEMC040 Memory Controller           |     |

|     | Configuration Parameters3                        |     |

|     | ALTC_2 - Alternate Control and Status Registers3 | -68 |

|     | BUSCLK - Bus Clock Register3                     |     |

|     | CHIPID - Chip ID Register3                       |     |

|     | CHIPREV - Chip Revision Register3                |     |

|     | RAMCNTRL - RAM Control Register3                 |     |

| ST2 | 2401 - Serial Port                               |     |

|     | Configuration Parameters3                        | -75 |

|     | BAUD - Baud Rates, Async, Internal Loopback 3    |     |

|     | DMA - DMA I/O, Async, Internal Loopback          |     |

|     | POLL - Polled I/O, Async, Internal Loopback3     |     |

|     | INTR - Interrupt I/O, Async, Internal Loopback   |     |

|     | ST2401 Test Group Error Messages3                |     |

| CM  | IMU - Cache and Memory Management Unit3          |     |

|     | Configuration Parameters3                        |     |

|     | CCHCODE - Cache Code Copy/Execution              |     |

|     | 1 3                                              | -   |

| CCHCPYB - Cache Copyback                              | 3-90  |

|-------------------------------------------------------|-------|

| CCHSC - Cache Supervisor Code                         |       |

| CCHSCC - Cache Supervisor Code Cache Inhibit          | 3-96  |

| CCHSD - Cache Supervisor Data                         | 3-99  |

| CCHSDC - Cache Supervisor Data Cache Inhibit          | 3-101 |

| CCHSDWT - Cache Supervisor Data Write Through         | 3-103 |

| CCHTTM - Translation Table Memory                     | 3-106 |

| CCHUC - Cache User Code                               | 3-108 |

| CCHUCCI - Cache User Code Cache Inhibit               | 3-111 |

| CCHUD - Cache User Data                               | 3-114 |

| CCHUDCI - Cache User Data Cache Inhibit               | 3-117 |

| CCHUDWT - Cache User Data Write Through               | 3-120 |

| MMUMU - MMU Modified/Used Data/Code                   | 3-123 |

| MMUSC - MMU Supervisor Code                           | 3-125 |

| MMUSD - MMU Supervisor Data                           | 3-128 |

| MMUSP - MMU Supervisor Protect Data/Code              |       |

| MMUSPF - MMU Segment/Page Fault Data/Code             | 3-134 |

| MMUUC - MMU User Code                                 |       |

| MMUUD - MMU User Data                                 | 3-140 |

| MMUWP - MMU Write Protect                             | 3-143 |

| TTRSC - TTR Supervisor Code                           | 3-146 |

| TTRSD - TTR Supervisor Data                           | 3-148 |

| TTRUC - TTR User Code                                 | 3-150 |

| TTRUD - TTR User Data                                 | 3-152 |

| TTRWP - TTR Write Protect - TTR                       | 3-154 |

| VME2 - VME Interface ASICs                            | 3-156 |

| Configuration Parameters                              | 3-157 |

| REGA - Register Access                                |       |

| REGB - Register Walking Bit                           |       |

| SWIA - Software Interrupts (Polled Mode)              |       |

| SWIB - Software Interrupts (Processor Interrupt Mode) |       |

| SWIC - Software Interrupts Priority                   |       |

| TACU - Timer Accuracy Test                            |       |

| TMRA, TMRB - Tick Timer Increment                     |       |

| TMRC - Prescaler Clock Adjust                         |       |

| TMRD, TMRE - Tick Timer No Clear On Compare           |       |

| TMRF, TMRG - Tick Timer Clear On Compare              |       |

| TMRH TMRI - Overflow Counter                          |       |

| TMRJ - Watchdog Timer Counter            | . 3-176 |

|------------------------------------------|---------|

| TMRK - Watchdog Timer Board Fail         |         |

| LANC - LAN Coprocessor                   |         |

| Configuration Parameters                 |         |

| CST - Chip Self Test                     |         |

| DIAG - Diagnose Internal Hardware        |         |

| DUMP - Dump Configuration/Registers      |         |

| ELBC - External Loopback Cable           |         |

| ELBT - External Loopback Transceiver     |         |

| FUSE - 12Vdc Fuse                        |         |

| ILB - Internal Loopback                  | . 3-191 |

| IRQ - Interrupt Request                  | . 3-194 |

| MON - Monitor (Incoming Frames) Mode     |         |

| TDF -Time Domain Reflectometry           | . 3-196 |

| LANC Test Group Error Messages           |         |

| NCR - NCR 53C710 SCSI I/O Processor      | . 3-203 |

| Configuration Parameters                 | . 3-203 |

| ACC1 - Device Access                     | . 3-204 |

| ACC2 - Register Access                   | . 3-206 |

| DFIFO - DMA FIFO                         | . 3-208 |

| IRQ - Interrupts                         | . 3-209 |

| LPBK - Loopback                          | . 3-212 |

| SCRIPTS - SCRIPTS Processor              | . 3-213 |

| SFIFO - SCSI FIFO                        | . 3-216 |

| FLASH - FLASH Memory Tests               | . 3-217 |

| Configuration Parameters                 | . 3-218 |

| ERASE - Erase FLASH Memory               | . 3-219 |

| FILL - Fill FLASH Memory                 | . 3-220 |

| PATS - FLASH Patterns                    | . 3-221 |

| FLASH Test Group Error Messages          | . 3-222 |

|                                          |         |

| CHAPTER 4 177Bug Environment             |         |

| Introduction                             | 4-1     |

| CNFG - Configure Board Information Block |         |

| ENV - Set Environment                    |         |

| Configuring 177Bug Parameters            |         |

| VMEbus Interface Parameters              |         |

## **APPENDIX A Related Documentation**

|     | Related Documentation                                     | A-1   |

|-----|-----------------------------------------------------------|-------|

|     | Table 2-1. Diagnostic Commands                            | 2-2   |

|     | Table 2-2. Diagnostic Command Prefixes                    | 2-8   |

|     | Table 3-1. Diagnostic Test Groups                         | 3-1   |

|     | Table 3-2. RAM and SRAM Tests                             | 3-3   |

|     | Table 3-3. RTC Tests                                      | 3-18  |

|     | Table 3-4. PCC2 Tests                                     | 3-24  |

|     | Table 3-5. MCECC Tests                                    | 3-58  |

|     | Table 3-6. MEMC1/MEMC2 Tests                              | 3-67  |

|     | Table 3-7. ST2401 Tests                                   | 3-75  |

|     | Table 3-1. ST2401 Error Messages                          | 3-84  |

|     | Table 3-8. CMMU Tests                                     | 3-86  |

|     | Table 3-9. VME2 Tests                                     | 3-157 |

|     | Table 3-10. LANC Tests                                    | 3-179 |

|     | Table 3-11. LANC Error Messages                           | 3-199 |

|     | Table 3-12. NCR Tests                                     | 3-204 |

|     | Table 3-13. FLASH Tests                                   | 3-218 |

| FIC | UDE6                                                      |       |

| FIG | URES                                                      |       |

|     | Figure 1-1. 177Bug Start-up Flow                          | 1-4   |

|     |                                                           |       |

| TAE | BLES                                                      |       |

|     | Table 2-1. Diagnostic Commands                            | 2-2   |

|     | Table 2-2. Diagnostic Command Prefixes                    |       |

|     | Table 3-1. Diagnostic Test Groups                         | 3-1   |

|     | Table 3-2. RAM and SRAM Tests                             | 3-3   |

|     | Table 3-3. RTC Tests                                      | 3-18  |

|     | Table 3-4. PCC2 Tests                                     | 3-24  |

|     | Table 3-5. MCECC Tests                                    | 3-58  |

|     | Table 3-6. MEMC1/MEMC2 Tests                              | 3-67  |

|     | Table 3-7. ST2401 Tests                                   | 3-75  |

|     |                                                           |       |

|     | Table 3-1. ST2401 Error Messages                          | 3-84  |

|     | Table 3-1. ST2401 Error Messages<br>Table 3-8. CMMU Tests |       |

| Table 3-9. VME2 Tests            | 3-156 |

|----------------------------------|-------|

| Table 3-10. LANC Tests           | 3-178 |

| Table 3-11. LANC Error Messages  | 3-198 |

| Table 3-12. NCR Tests            | 3-203 |

| Table 3-13. FLASH Tests          | 3-217 |

| Table 3-14. FLASH Error Messages | 3-222 |

# **Description of 177Bug**

The 177Bug is a member of the M68000 firmware family which is implemented on the MVME177 Single Board Computer. The 177Bug consists of three parts:

- □ A command-driven, user-interactive software debugger. 177Bug performs its various operations in response to user commands entered at the keyboard. It is described in the *Debugging Package for Motorola 68K CISC CPUs User's Manual*, and is hereafter referred to as the *debugger*.

- □ A command-driven diagnostic package for the MVME177 board, described in chapters 2 and 3, and which are hereafter referred to as the *diagnostics*.

- MPU, firmware, and hardware initialization routines, which is described in the *Debugging Package for Motorola 68K CISC* CPUs User's Manual.

## **Debug and Diagnostic Commands**

There are three types of commands: debugger commands, diagnostic commands, and diagnostic tests. In addition, the execution of the diagnostic commands and tests may be modified by using command prefixes. The diagnostic commands and prefixes are described in Chapter 2. The diagnostic tests are described in Chapter 3. The debugger commands are described in the *Debugging Package for Motorola 68K CISC CPUs User's Manual.*

When you are running the diagnostics, the 177-Diag> prompt appears. If you are running the debugger (177-Bug> prompt), switch to the diagnostics by entering the debugger **SD** command.

# 177Bug Implementation

177Bug is installed in two 44-pin PLCC/CLCC PROM devices. The PROMSs are 256K x 16 each, providing 512KB of storage. Both PROMs are necessary because of the 32-bit longword-oriented MC68060 memory bus architecture.

#### **User Interface**

The firmware user interface allows users to run commands and tests from the command prompt. The interface reports results to the diagnostic video display terminal. This interface is command line driven and provides input/output facilities, command parsing, error reporting, and interrupt handling. The user interface is similar to those in existing diagnostic packages.

## Language

The C programming language is used for most 177Bug modules. The CPU-specific low-level hardware interface code is written in assembly language.

# Start-Up

When 177Bug is brought up at either power up or RESET, the following is displayed on the diagnostic video display terminal (port 1/console terminal):

```

Copyright Motorola Inc. 1988 - 1994, All Rights Reserved

MVME177 Debugger/Diagnostics Release Version x.x - mm/dd/yy

COLD Start

Local Memory Found =02000000 (&33554432)

MPU Clock Speed =50Mhz

```

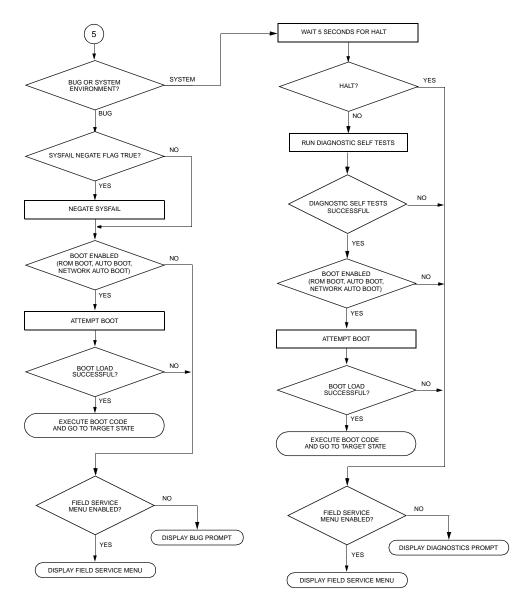

The firmware runs the diagnostic self tests, and displays the test result messages on the bottom line of the screen. Once the tests are complete, the Field Service Menu appears. Select option **3** Go To System Debugger from the menu to go to the 177-Diag> prompt. Enter **SD** if you want to switch to the debugger prompt (177-Bug>).

There is a five-second delay prior to the diagnostic self tests. You may bypass the diagnostics and exit to the Field Service Menu by pressing the ABORT switch during this halt.

Refer to the *Debugging Package for Motorola 68K CISC CPUs User's Manual* for more information on using the debugger and the Field Service Menu.

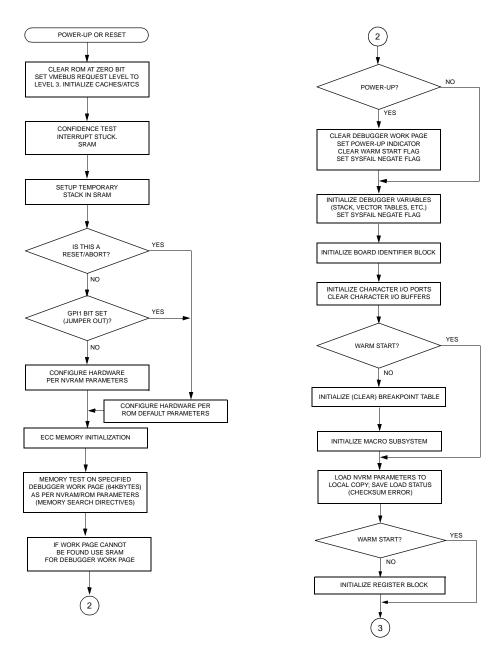

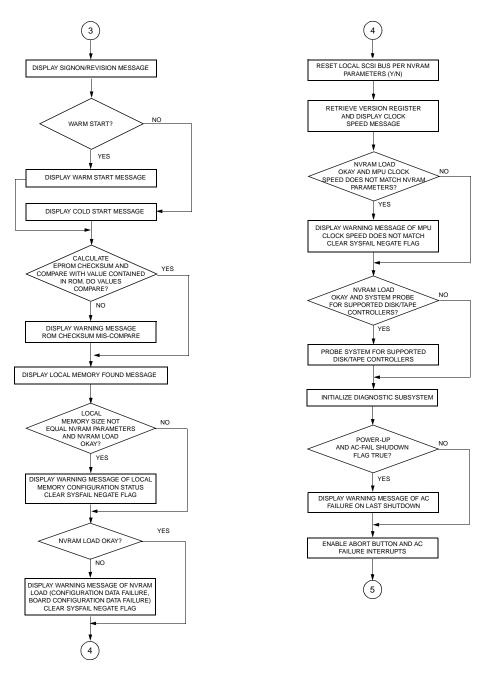

The start-up and boot-load sequence is shown in Figure 1-1.

Figure 1-1. 177Bug Start-up Flow (Sheet 1 of 3)

Figure 1-1. 177Bug Start-up Flow (Sheet 2 of 3)

Figure 1-1. 177Bug Start-up Flow (Sheet 3 of 3)

## **ROMboot**

177Bug occupies the PROM sockets (U1 and U2). This leaves 4MB of FLASH memory available, of which 2MB at a time may be switched into the visible memory map. See the **SFLASH** debugger command in the *Debugging Package for Motorola 68K CISC CPUs User's Manual*.

The MVME177 provides many possible memory mapping configurations for storing a ROMboot program. See the MVME177 Single Board Computer User's Manual or the MVME177 Single Board Computer Programmer's Reference Guide for more information, or contact your Motorola sales office for assistance.

# **Memory Requirements**

The program portion of 177Bug is approximately 512KB of code consisting of download, debugger, and diagnostic packages. It is contained entirely in EPROM/FLASH. The firmware memory on the MVME177 is mapped starting at location \$FF800000. 177Bug requires a minimum of 64KB of contiguous read/write memory to operate.

The ENV command controls where this block of memory is located. Regardless of where the onboard RAM is located, the first 64KB is used for 177Bug stack and static variable space and the rest is reserved as user space. Whenever the MVME177 is reset, the target PC is initialized to the address corresponding to the beginning of the user space, and the target stack pointers are initialized to addresses within the user space, with the target Interrupt Stack Pointer (ISP) set to the top of the user space.

At power up or reset, all 8KB of memory at addresses \$FFE0C000 through \$FFE0DFFF is completely changed by the 177Bug initial stack.

## Introduction

This chapter contains information about entering the 177Bug diagnostic commands and tests. The diagnostic commands and test prefixes are also described in this chapter. The diagnostic tests are described in Chapter 3.

# **Running Commands**

When using 177Bug, you operate the debugger or the diagnostics. If you are in the debugger, the prompt 177-Bug> is displayed and you have all of the debugger commands at your disposal. If you are in the diagnostics, the prompt 177-Diag> is displayed and you have all of the diagnostic commands, diagnostic tests, and debugger commands at your disposal. You may switch between the diagnostics and the debugger by using the **SD** command.

Set the parameters that control the operation of all tests in a test group, such as memory range, with the **CF** command.

You may view a list of the debugger or diagnostics commands and test groups by using the **HE** command (when at the diagnostics prompt, **HE** does not list the debugger commands even thought those commands are available).

## **Command Entry**

To execute a command, enter the command at the 177-Diag> prompt and press the Return key. 177Bug executes the command and the prompt reappears.

You may enter multiple commands on one line. If a command expects parameters and another command is to follow it, separate the two with a semicolon (;).

2

For instance, to invoke the command RTC CLK after the command RAM ADR, you may enter RAM ADR; RTC CLK on the command line.

Test prefixes are available to modify the execution of a test. Insert a semicolon between the prefix and the test that it modifies. For instance **LF**; **RAM** (spaces are not required before or after the semicolon).

# **Diagnostic Commands**

The diagnostic package supports the root-level commands and general commands, which are listed in the table below and described on the following pages.

**Table 2-1. Diagnostic Commands**

| Command | Description                                |

|---------|--------------------------------------------|

| AEM     | Append Error Messages Mode                 |

| CEM     | Clear Error Messages                       |

| CF      | Test Group Configuration Parameters Editor |

| DE      | Display Error Counters                     |

| DEM     | Display Error Messages                     |

| DP      | Display Pass Count                         |

| HE      | Help                                       |

| HEX     | Help Extended                              |

| MASK    | Self Test Mask                             |

| SD      | Switch Directories                         |

| ST      | Self Test                                  |

| ZE      | Clear (Zero) Error Counters                |

| ZP      | Zero Pass Count                            |

## **AEM - Append Error Messages Mode**

The **AEM** command allows you to accumulate error messages in the internal error message buffer of the diagnostics. The **AEM** command sets the internal append error messages flag of the diagnostics. When the internal append error messages flag is clear, the diagnostic error message buffer is erased (cleared of all character data) before each test is executed. The duration of this command is for the life of the command line being parsed by the diagnostics. The default of the internal append error messages flag is clear. The internal flag is not set until it is encountered in the command line by the diagnostics.

## **CEM - Clear Error Messages**

The **CEM** command allows you to clear the internal error message buffer of the diagnostics manually.

## **CF - Test Group Configuration Parameters Editor**

The **CF** command allows you to modify the parameters that control the operation of the diagnostic tests. For example, the **RAM** test group has parameters for the starting address, ending address, and parity enable that you can set with the **CF** command.

The **CF** command prompts you with the parameter and the current value. You may enter a new value for that parameter, or press the Return key leave the parameter unchanged.

You may enter one or more test groups as argument(s) to the **CF** command. Only the parameters for those tests will be displayed. If no test group name is entered, the parameters for all test groups are displayed.

At the time of initial execution of the diagnostic tests, the default configuration parameters are copied from the firmware into the debugger work page.

## **DE - Display Error Counters**

The **DE** command displays all errors in the test error counters. Each test or command in the diagnostics has an individual error counter. As errors are encountered in a particular test, that error counter is incremented. If you were to run a self-test or just a series of tests, the results could be broken down as to which tests passed by examining the error counters.

To view the errors of an individual test, enter the full test name after the **DE** command. For example, to view errors from the test error counter on RAM Code Execution/Copy test routine, enter **DE RAM CODE**.

Only nonzero values are displayed.

## **DEM - Display Error Messages**

The **DEM** command displays the internal error message buffer of the diagnostics.

## **DP - Display Pass Count**

The **DP** command displays a count of the number of passes of tests run in Loop-Continue (**LC**) mode.

## HE - Help

The **HE** command displays the available diagnostic commands, test groups, and test prefixes. The character string (DIR) appears after a test group name. If there are more entries than fit on the screen, the message Press "RETURN" to continue appears.

**HE** does not list the debugger commands even thought those commands are available from the 177-Diag> prompt.

To view the tests in a test group, enter the test group name after the **HE** command. For example, to list all the RAM tests, enter **HE RAM**.

To view a description of an individual test, enter the full test name. For example, to view information on the RAM Code Execution/Copy test routine, enter **HE RAM CODE**.

#### The following is an example of the **HE** command:

```

177-Diag>HE

AEM

Append Error Messages Mode

CEM

Clear Error Messages

CF

Configuration Editor

Cache/Memory Management Unit Tests (DIR)

CMMU

DE

Display Errors

DEM

Display Error Messages

DΡ

Display Pass Count

Flash Memory Tests (DIR)

FLASH

HE

Help on Tests/Commands

HEX

Help Extended

LΑ

Loop Always Mode

LANC

LAN Coprocessor (Intel 82596) Tests (DIR)

LC

Loop Continuous Mode

Loop on Error Mode

_{

m LE}

LF

Line Feed Mode

LN

Loop Non-Verbose Mode

MASK

Self Test Mask

MCECC ECC Memory Board Diagnostics (DIR)

MEMC1

Memory Controller #1 ASIC (DIR)

Memory Controller #2 ASIC (DIR)

MEMC2

NCR

NCR 53C710 SCSI I/O Processor Test (DIR)

NV

Non-Verbose Mode

PCCchip2 Tests (DIR)

PCC2

RAM

Random Access Memory Tests (DIR)

Press "RETURN" to continue

MK48T0x Timekeeping (DIR)

RTC

Stop on Error Mode

SE

SRAM

Static Random Access Memory Tests (DIR)

ST

Self Test (DIR)

ST2401 CD2401 Serial Self-Tests (DIR)

VME2

VME2Chip2 Tests (DIR)

Zero Errors

ZE

Zero Pass Count

ZΡ

177-Diag>

```

## **HEX - Interactive Help**

The **HEX** command enters a continuous interactive mode of the **HE** command. When you execute **HEX**, the question mark (?) is displayed as a prompt. You may then enter the name of a test group or diagnostic command. Type **QUIT** to return to the diagnostics prompt.

#### MASK - Self Test Mask

The MASK command enables or disables a test from running as part of the start-up diagnostic self tests or when executing the ST command. (effective release 1.3). The MASK command "toggles" the test's state. If the specified test is enabled, it will be disabled by running MASK; if the is disabled, it will be enabled. The default for a test is the enabled state. The mask values are saved in non-volatile memory.

The syntax is **MASK** *TEST NAME*, where *TEST NAME* is the full name of a diagnostic test. For example, to disable the **RAM CODE** test, enter **MASK RAM CODE**.

If the **MASK** command is invoked with an invalid test group name, an appropriate error message is displayed.

To display the current disabled tests, invoke **MASK** without a test name. A list of disabled (masked) tests is also displayed each time the command is run for a test.

#### **SD - Switch Directories**

Use the **SD** command to toggle between the diagnostic and debugger directories. When you are running the diagnostics, the 177-Diag> prompt appears. All of the debugger and diagnostics commands are available. When you are running the debugger, the prompt is 177-Bug>, and only the debugger commands are available.

#### ST - Self Test

The **ST** command runs the system self tests that the bug runs at system start-up. The command **HE ST** lists the test groups that are run with the self tests.

This command is useful for debugging board failures that may require running the test suite while using the debugger. Upon completion of running the test suite, the debugger prompt is displayed.

#### **ZE - Clear Error Counters**

The **ZE** command resets all of the error counters to zero. The error counters are initialized with the value of zero. After tests run, it may desirable to reset them to zero.

To clear the error counter for a particular test, enter the test name with the **ZE** command. For example, **ZE VME2 TMRA** clears the error counter for **VME2 TMRA**.

#### **ZP - Zero Pass Count**

The **ZP** command resets the pass counter to zero. This is frequently desirable before using the Loop Continue mode.

To reset the counter at each pass of a particular test, enter the **ZP** command on the same line as **LC** and the test. For example, **ZP LC VME2 TMRA**.

2

## **Test Prefixes**

The tests execution can be modified with the prefixes, which are listed in Table 2-2 and are described on the following pages.

**Table 2-2. Diagnostic Command Prefixes**

| Prefix | Description                |

|--------|----------------------------|

| LA     | Loop Always Mode           |

| LC     | Loop-Continue Mode         |

| LE     | Loop-On-Error Mode         |

| LF     | Line Feed Suppression Mode |

| LN     | Loop Non-Verbose Mode      |

| NV     | Non-Verbose Mode           |

| SE     | Stop-On-Error Mode         |

## LA - Loop Always

The LA prefix causes a failed test or series of failed tests to be reexecuted endlessly. To break the loop, press the BREAK key. Certain tests disable the BREAK key interrupt, so it may be necessary to press the ABORT or RESET switches on the MVME177 front panel.

## LC - Loop-Continue

The LC prefix causes a test or series of tests to be re-executed endlessly. To break the loop, press the BREAK key. Certain tests disable the BREAK key interrupt, so it may be necessary to press the ABORT or RESET switches on the MVME177 front panel.

### LE - Loop-On-Error

The **LE** prefix causes a test to be re-executed if the previous execution returns a failure status. To break a loop, press the BREAK key. Certain tests disable the BREAK key interrupt, so it may be necessary to press the ABORT or RESET switches on the MVME177 front panel.

The **LE** prefix is useful to endlessly repeat (loop) a test when an oscilloscope or logic analyzer is in use.

## LF - Line Feed Suppression

The **LF** prefix toggles the internal line feed mode flag of the diagnostics. The default state of the internal line feed mode flag is clear which causes the executing test title/status line(s) to be terminated with a line feed character (scrolled). The line feed mode flag is normally used by the diagnostics when executing a system self test.

## LN - Loop Non-Verbose

The LN prefix causes the test to be re-executed endlessly, and suppresses display of the test title and pass/fail status. This is useful for more rapid execution of the failing test.

#### **NV - Non-Verbose**

The NV prefix suppresses the display of test status and error data. Only the test name and result (PASSED or FAILED) are listed.

### SE - Stop-On-Error

The **SE** prefix stops a test or series of tests when an error is detected.

## Introduction

This chapter contains detailed descriptions of the 177Bug diagnostic tests. The test sets are shown in Table 3-1.

**Test Group Description RAM Local RAM Tests SRAM** Static RAM Tests RTC MK48T0x Real-Time Clock Tests PCC2 Peripheral Channel Controller Tests **MCECC Memory Board Tests** MEMC1 MC040 Memory Controller 1 ASIC Tests MEMC2 MC040 Memory Controller 2 ASIC Tests ST2401 CD2401 Serial Port Tests **CMMU** Cache and Memory Management Unit Tests VME2 VME Interface ASIC VMEchip2 Tests LANC LAN Coprocessor (Intel 82596) Tests NCR NCR 53C710 SCSI I/O Processor Tests

Flash Memory Tests

**Table 3-1. Diagnostic Test Groups**

# Running the Tests

**FLASH**

The diagnostic test commands consist of a test group name and a test name. To run a test, enter the test group name and the test name on the command line. For instance, **RAM** is a test group, and **ADR** is the name of a test in the group. To invoke the **ADR** test, enter **RAM ADR** on the command line.

3

To run all tests in a test group, enter the test group name without any test names (the **FLASH** tests must be run individually).

You may enter any number or sequence of tests after the test group name as long as the bug's input buffer size limit is not exceeded.

Upon execution of a test, a status message appears indicating the test name and the current status. For example, the following message appears for the **PCC2 PRINTE** test:

```

PCC2 PRNTE: Printer `BUSY' Interrupts..... Running --->

```

If all parts of the test pass, passed appears at the end of the message line. If any part of the test fails, failed appears at the end of the message line, followed by one or more error messages.

# RAM - Local RAM, SRAM - Static RAM

The **RAM** tests check the local RAM and the **SRAM** tests check the Static RAM.

The **RAM** and **SRAM** tests are listed in Table 3-2, and are described in alphabetical order on the following pages. The **RAM** and **SRAM** tests are identical in function.

Enter **RAM** or **SRAM** without a test name to run all tests in the group (**PED** and **REF** do not run with the **SRAM** test group). They will be executed in the order shown in Table 3-2.

Table 3-2. RAM and SRAM Tests

| Test | Description            |

|------|------------------------|

| QUIK | Quick Write/Read       |

| ALTS | Alternating Ones/Zeros |

| PATS | Data Patterns          |

| ADR  | Memory Addressing      |

| CODE | Code Execution/Copy    |

| PERM | Permutations           |

| RNDM | Random Data            |

| BTOG | Bit Toggle             |

| PED  | Parity Error Detection |

| REF  | Memory Refresh         |

# **Configuration Parameters**

You may set the following parameters with the **CF** command (the default values are shown):

3

```

Starting/Ending Address Enable [Y/N] =N ?

Starting Address =00000000 ? (FFE00000 for SRAM)

Ending Address =01000000 ? (FFE1FFFC for SRAM)

Random Data Seed =12301983 ?

March Address Pattern =00000000 ?

Instruction (Code) Cache Enable [Y/N] =Y ?

Parity Enable [Y/N] =Y ?

MCECC Error Correction Enable [Y/N] =N ?

Parity Interrupt Enable [Y/N] =Y ?

Parity Error Detection Test Address Increment =00001001 ?

Break Key Check Delay Counter =00000100 ?

```

# **ADR - Memory Addressing**

The **ADR** test verifies addressing of memory in the range specified by the configuration parameters for the **RAM** test group. Addressing errors are sought by using a memory location's address as the data for that location. This test is coded to use only 32-bit data entities.

The test runs as follows:

- 1. A Locations Address is written to its location (*n*).

- 2. The next location (*n*+4) is written with its address complemented.

- 3. The next location (n+8) is written with the most significant 16 bits and least significant 16 bits of its address swapped with each other.

- 4. Steps 1, 2, and 3 are repeated throughout the specified memory range.

- 5. The memory is read and verified for the correct data pattern(s) and any errors are reported.

- 6. The test is repeated (steps 1 through 5) except that inverted data is used to insure that every data bit is written and verified at both "0" and "1".

## **Command Input**

177-Diag>RAM ADR

or

177-Diag>**SRAM ADR**

## Messages

| Data Miscompare | Error:       |          |   |

|-----------------|--------------|----------|---|

| Address =       | , Expected = | , Actual | = |

# **ALTS - Alternating Ones/Zeros**

This test verifies addressing of memory in the range specified by the configuration parameters for the **RAM** test group. Addressing errors are sought by using a memory locations address as the data for that location. This test is coded to use only 32-bit data entities.

The test runs as follows:

- 1. Location (*n*) is written with data of all bits 0.

- 2. The next location (n+4) is written with all bits 1.

- 3. Steps 1 and 2 are repeated throughout the specified memory range.

- 4. The memory is read and verified for the correct data pattern(s) and any errors are reported.

#### **Command Input**

177-Diag>RAM ALTS

or

177-Diag>SRAM ALTS

## Messages

```

Data Miscompare Error:

Address = _____, Expected = ____, Actual = _____

```

# **BTOG - Bit Toggle**

This test toggles the bits in the memory range specified by the configuration parameters for the **RAM** test group. The **RAM** test group configuration parameters also determine the value of the global random data seed used by this test. The global random data seed is incremented after it is used by this test.

This test uses the following test data pattern generation algorithm:

- 1. The random data seed is copied into a work register.

- 2. Work register data is shifted right one bit position.

- 3. The random data seed is added to work register using unsigned arithmetic.

- 4. Data in the work register may or may not be complemented.

- 5. Data in the work register is written to current memory location.

If the **RAM** test group configuration parameter for code cache enable equals "Y", the microprocessor code cache is enabled. This test is coded to operate using the 32-bit data size only.

The test runs as follows:

- 1. The memory locations are written with the test data pattern.

- 2. The memory locations are written with the complement of the test data pattern complemented.

- 3. The memory under test is read back to verify that the complement test data is properly retained.

- 4. The memory locations are written with the test data pattern.

- 5. The memory under test is read back to verify that the test data is properly retained.

3

# **Command Input**

177-Diag>**RAM BTOG**

or

177-Diag>**SRAM BTOG**

## Messages

| Data  | Miscompare | Error:     |    |        |   |

|-------|------------|------------|----|--------|---|

| Addre | ss =       | , Expected | =, | Actual | = |

# **CODE - Code Execution/Copy**

This test copies test code to a memory location and executes the code. The test code copies itself to the next higher memory address and executes the new copy. This process is repeated until there is not enough memory, as specified by the configuration parameters, to perform another code copy and execution.

A hardware reset is required to recover if the test fails (MPU irrecoverably crashes).

#### **Command Input**

177-Diag>RAM CODE

or

177-Diag>SRAM CODE

#### Messages

If the test passes, the Passed message appears. If the Passed message does not appear within a minute of executing the test, the test has failed (the Failed message does not appear).

#### **PATS - Data Patterns**

This test writes and reads a series of test patterns to the test memory range. Each location is filled with all ones (\$FFFFFFF). The test runs eight passes, one for each of the following data patterns:

```

$00000000

$01010101

$03030303

$07070707

$0F0F0F0F

$1F1F1F1F

$3F3F3F3F

$7F7F7F7F

```

During each pass of the test, each location is written with the current pattern and the 1's complement of the current pattern. Each write is read back and verified. each location is filled with the data pattern. This test is coded to use only 32-bit data entities.

If the test address range is less than 8 bytes, the test immediately returns pass status. The effective test range end address is reduced to the next lower 8-byte boundary if necessary.

## **Command Input**

```

177-Diag>RAM PATS

or

177-Diag>SRAM PATS

```

## Messages

```

Data Miscompare Error:

Address = _____, Expected = ____, Actual = _____

```

# **PED - Local Parity Memory Error Detection**

This test checks memory parity for memory range and address increment is specified by the **RAM** test group configuration parameters.

First, the test verifies a portion of each memory location to be tested by writing and verifying all zeros, and writing an verifying all ones. Each memory location is tested once with parity interrupt disabled, and once with parity interrupt enabled. Parity checking is enabled, and data is written and verified at the test location that causes the parity bit to toggle on and off (verifying that the parity bit of memory is good). Next, data with incorrect parity is written to the test location. The data is read, and if a parity error exception occurs, the fault address is compared to the test address. If the addresses are the same, the test passed and the test location is incremented until the end of the test range has been reached.

#### **Command Input**

177-Diag>RAM PED

or

177-Diag>SRAM PED

## Messages

If a data verification error occurs, the following message appears:

```

RAM/PED Test Failure Data:

Data Miscompare Error:

Address = _____, Expected = ____, Actual = _____

```

If an unexpected exception (parity error detected as the parity bit was being toggled), the following message appears:

```

RAM/PED Test Failure Data:

Unexpected Exception Error, Vector =_____

Address Under Test =_____

```

If no exception occurred when data with bad parity was read, the following message appears:

| RAM/PED Test Failur                    | e Data:                     |

|----------------------------------------|-----------------------------|

| Parity Error Detect                    | ion Exception Did Not Occur |

| Exception Vector =_ Address Under Test |                             |

If the exception address was different from that of the test location, the following message appears:

| RAM/PED   | Test Failu  | re Data:          |            |

|-----------|-------------|-------------------|------------|

| Fault Add | dress Misco | mpare, Expected = | , Actual = |

#### **PERM - Permutations**

This test verifies that the memory in the test range can accommodate 8-, 16-, and 32-bit writes and reads in any combination. The test range is the memory range specified by the **RAM** test group configuration parameters for starting and ending address. If the test range is less than 16 bytes, the test immediately returns pass status. The effective test range end address is reduced to the next lower 16-byte boundary if necessary.

This test performs three data size test phases in the following order: 8, 16, and 32 bits. Each test phase writes a 16-byte data pattern (using its data size) to the first 16 bytes of every 256-byte block of memory in the test range. The 256-byte blocks of memory are aligned to the starting address configuration parameter for the **RAM** test group. The test phase then reads and verifies the 16-byte block using 8-, 16-, and 32-bit access modes.

#### **Command Input**

177-Diag>RAM PERM

or

177-Diag>**SRAM PERM**

## Messages

| Data Miscompare | Error:   |          |   |

|-----------------|----------|----------|---|

| Addrogg -       | Exported | - 7atual | _ |

## **QUIK - Quick Write/Read**

This test writes and reads a pair of test patterns, 0 and \$FFFFFFFF, to the test memory range. Each pass of this test fills the test range with a data pattern by writing the current data pattern to each memory location from a local variable and reading it back into that same register. The local variable is verified to be unchanged only after the write pass through the test range.

This test uses only 32-bit data entities.

#### **Command Input**

177-Diag>RAM QUIK

or

177-Diag>**SRAM QUIK**

#### Messages

```

Data Miscompare Error:

Expected =_____, Actual =_____

```

# **REF - Memory Refresh Testing**

This test verifies memory locations after a refresh wait cycle. The memory range and address increment is specified by the RAM test group configuration parameters.

The test runs as follows:

- 1. The real time clock is checked to see if it is functioning properly.

- 2. Each memory location to be tested has the data portion verified by writing and verifying patterns of all zeros, and all ones.

- 3. A data pattern is written to the test location.

- 4. After all the data patterns are filled for all test locations, a refresh wait cycle is executed.

- 5. The data is read.

If the previously entered data pattern does not match the data pattern read in, a failure occurs. If the data patterns match, the test is passed.

**Note SRAM REF** will not execute because SRAM does not refresh.

## **Command Input**

177-Diag>RAM REF

## Messages

If the real time clock is not functioning properly, one of the following messages appear:

RAM/REF Test Failure Data:

RTC is stopped, invoke SET command.

```

Or

RAM/REF Test Failure Data:

RTC is in write mode, invoke SET command.

Or

RAM/REF Test Failure Data:

RTC is in read mode, invoke SET command.

```

If a data verification error occurs before the refresh wait cycle, the following message appears:

```

RAM/REF Test Failure Data:

Immediate Data Miscompare Error:

Address = ______, Expected = _____, Actual = ______

```

If a data verification error occurs following the refresh wait cycle, the following message appears:

```

RAM/REF Test Failure Data:

Unrefreshed Data Miscompare Error:

Address = _____, Expected = ____, Actual = _____

```

#### **RNDM - Random Data**

This test writes and verifies a random test patterns and the complement of the test pattern. The test memory range specified by the **RAM** test group configuration parameters.

The test runs as follows:

- 1. A random pattern is written throughout the test range.

- 2. The random pattern complemented is written throughout the test range.

- 3. The complemented pattern is verified.

- 4. The random pattern is rewritten throughout the test range.

- 5. The random pattern is verified.

This test uses only 32-bit data entities. Each time this test is executed, the random seed in the **RAM** test group configuration parameters is post incremented by 1.

#### **Command Input**

177-Diag>RAM RNDM

or

177-Diag>**SRAM RNDM**

## Messages

```

Data Miscompare Error:

Address = _____, Expected = ____, Actual = _____

```

# RTC - MK48T08 Real Time Clock

The **RTC** tests check the NVRAM, SRAM, and clock portions of the MK48T08 Real Time Clock (RTC) chip. The tests are listed in Table 3-3, and are described in alphabetical order on the following pages.

Enter **RTC** without a test name to run all tests in the group. They will be executed in the order shown in Table 3-3.

Table 3-3. RTC Tests

| Test | Description            |

|------|------------------------|

| CLK  | Clock Function         |

| RAM  | Battery Backed-Up SRAM |

| ADR  | BBRAM Addressing       |

# **Configuration Parameter**

You may set the Restore BBRAM contents on test exit parameter, used in the ADR test, with the CF command (the default is Y).

# **ADR - NVRAM Addressing**

This test checks the proper addressing of the MK48T0x NVRAM. The test runs as follows:

- 1. The NVRAM is filled with data pattern "a."

- 2. A single address line of the MK48T0x is set to one, and pattern "b" is written to the resultant address.

- 3. All other locations in the NVRAM are checked to ensure that they were not affected by this write.

- The "a" pattern is restored to the resultant address.

All address lines connected to the MK48T0x are tested in this manner.

Since this test overwrites all memory locations in the NVRAM, the NVRAM contents are saved in debugger system memory prior to writing the NVRAM. The RTC test group features a configuration parameter which overrides automatic restoration of the NVRAM contents. The default for this parameter is to restore NVRAM contents upon test completion.

## **Command Input**

177-Diag>RTC ADR

## Messages

If debugger system memory cannot be allocated for use as a save area for the NVRAM contents, the following message appears:

| RAM allocate |            |  |

|--------------|------------|--|

|              |            |  |

| memc.next=   | memc.size= |  |

If the NVRAM cannot be initialized with pattern "a," the following message appears:

Data Verify Error: Address =\_\_\_\_\_, Expected =\_\_, Actual =\_\_ Memory initialization error If a pattern "b" write affects any NVRAM location other than the resultant address, the following message appears:

| Data Ve | rify Er | ror: A | ddress | =     | Expected | =, | Actual |

|---------|---------|--------|--------|-------|----------|----|--------|

| =       |         |        |        |       |          |    |        |

| Memory  | addres  | sing e | rror - | wrote | -0       |    |        |

#### **CLK - Check Real Time Clock**

This test verifies that the RTC is operating. It does not check clock accuracy. This test requires approximately nine seconds to run. At the conclusion of the test, nine seconds are added to the clock time to compensate for the test delay. Because the clock can only be set to the nearest second, this test may induce up to one second of error into the clock time.

#### Note

The Low Battery test only assures Battery OK if the MK48T02 (used on other boards) has not been written since powerup. The Battery test is performed here in case the debugger currently in use does not perform a Low Battery test on powerup. Although the MK48T08 does not support the internal battery voltage check (BOK), the BOK flag status check algorithm is performed by this test on all parts.

The RTC time registers are configured for constant updating by the clock internal counters. The seconds register is read initially and monitored (read) to verify that the seconds value changes. A predetermined number of reads are made of the seconds register.

The RTC time registers are configured for reading. A predetermined number of MPU "do nothing" loops are executed.

## **Command Input**

177-Diag>RTC CLK

## Messages

If the check for low battery fails, the following message appears:

RTC low battery

If the predetermined number of reads are made before the seconds register changed, the following message appears:

RTC not running

3

If the seconds register changes before the full count of MPU loops is executed, the following message appears:

RTC did not freeze for reading

If the real time clock registers fail the data pattern test:

| Data Miscompare | Error:       |            |   |

|-----------------|--------------|------------|---|

| Address =       | , Expected = | <br>Actual | = |

If there is a a programming error, the following message appears:

WARNING -- Real Time Clock NOT compensated for test delay.

# RAM - Battery Backed-Up SRAM

This test performs a data test on each SRAM location of the MK48T08 "Zeropower" RAM. RAM contents are unchanged upon completion of test, regardless of pass or fail test return status. This test is coded to test only byte data entities.

The RAM test runs seven passes, once for each the following values: \$1, \$3, \$7, \$F, \$1F, \$3F, and \$7F. During each pass:

- 1. The value is written to each valid byte of the MK48T08.

- 2. The value is verified.

- 3. The complement of each value is written to each valid byte of the MK48T08

- 4. The complement is verified.

#### **Command Input**

177-Diag>RTC RAM

#### Messages

| Data Miscompare | Error:       |            |  |

|-----------------|--------------|------------|--|

| Address =       | , Expected = | , Actual = |  |

# **PCC2 - Peripheral Channel Controller**

The **PCC2** tests check the PCCchip2. The tests are listed in Table 3-4, and are described in alphabetical order on the following pages.

Enter **PCC2** without a test name to run all of the **PCC2** tests. They will be executed in the order shown in Table 3-4.

Table 3-4. PCC2 Tests

| Test  | Description                |

|-------|----------------------------|

| REGA  | Device Access              |

| REGB  | Register Access            |

| TMR1A | Timer 1 Counter            |

| TMR1B | Timer 1 Free-Run           |

| TMR1C | Timer 1 Clear On Compare   |

| TMR1D | Timer 1 Overflow Counter   |

| TMR1E | Timer 1 Interrupts         |

| TMR2A | Timer 2 Counter            |

| TMR2B | Timer 2 Free-Run           |

| TMR2C | Timer 2 Clear On Compare   |

| TMR2D | Timer 2 Overflow Counter   |

| TMR2E | Timer 2 Interrupts         |

| ADJ   | Prescaler Clock Adjust     |

| PCLK  | Prescaler Clock            |

| GPIO  | GPIO Interrupts            |

| LANC  | LANC Interrupts            |

| PRNTA | Printer `ACK' Interrupts   |

| PRNTB | Printer `FAULT' Interrupts |

| PRNTC | Printer `SEL' Interrupts   |

| PRNTD | Printer `PE' Interrupts    |

| PRNTE | Printer `BUSY' Interrupts  |

| MIEN  | `MIEN' Bit                 |

| FAST  | `FAST' Bit                 |

| VBR   | Vector Base Register       |

# **ADJ - Prescaler Clock Adjust**

The **ADJ** test verifies that the Prescaler Clock Adjust Register can vary the period of the Tick Timer input clock. This is accomplished by setting the Clock Adjust Register to zero and allowing Tick Timer 1 to free-run for a small software delay, this will establish a reference count. Next a 1 is walked through the Clock Adjust Register and the timer is allowed to run for the same delay period, the resulting count should be greater than the last count.

Higher level software will always initialize the prescaler prior to calling the test, so a check of the register with a result of zero will be treated as a failure.

#### **Command Input**

177-Diag>PCC2 ADJ

#### Messages

| Prescaler Clock Adjust Register not initialized |

|-------------------------------------------------|

| Register, should not be zero                    |

| Clock Adjust did not vary tick period correctly |

| Register Address =, Adjust value =              |

| Test count :, should be greater than            |

| Previous count:                                 |

#### **FAST - FAST Bit**

The **FAST** test uses Tick Timer 1 to verify the FAST/SLOW access time to BBRAM. To ensure a stable timer count, the BBRAM is accessed 2048 times.

The test runs as follows:

- 1. Tick Timer 1 is initialized to zero and set for free-run.

- 2. The "FAST" bit is set.

- 3. The timer is started.

- 4. BBRAM is accessed.

- 5. The timer is stopped and the count is saved.

- 6. The "FAST" bit is cleared.

- 7. The timer is initialized to zero.

- 8. The timer is started.

- 9. BBRAM is accessed.

- 10. The timer is stopped and the count is saved.

- 11. Slow count is checked against fast count.

An error is reported if fast count not less than slow count.

## **Command Input**

177-Diag>PCC2 FAST

## Messages

```

PCC2/FAST Test Failure Data:

`FAST' bit did not vary access time correctly

Fast access count =_____,

Slow access count =_____,

Fast count should be less than Slow count

```

## **GPIO - GPIO Interrupts**

The **GPIO** test verifies the General Purpose I/O (GPIO) interrupts. It checks that level 0 interrupts set the appropriate status and do not generate an interrupt. It then verifies that all interrupts (1 through 7) can be generated and received and that the appropriate status is set.

#### **Command Input**

177-Diag>PCC2 GPIO

#### Messages

```

Interrupt Control Register did not clear

Address =_____, Expected =___, Actual =___

Interrupt Enable bit did not set

Address =____, Expected =__, Actual =__

Interrupt Status bit did not set

Status: Expected =___, Actual =___

Vector: Expected =__, Actual =__

State : IRQ Level =_, VBR =__

Incorrect Vector type

Status: Expected =___, Actual =___

Vector: Expected =__, Actual =__

State : IRQ Level =_, VBR =__

Unexpected Vector taken

Status: Expected =___, Actual =___

Vector: Expected =__, Actual =__

State : IRQ Level =_, VBR =__

Incorrect Interrupt Level

Level : Expected =_, Actual =_

State : IRQ Level =_, VBR =__

Interrupt did not occur

Status: Expected =___, Actual =___

Vector: Expected =__, Actual =__

State : IRQ Level =_, VBR =__

```

```

Interrupt Status bit did not set

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Interrupt Status bit did not clear

Address =____, Expected =__, Actual =__

Bus Error Information:

Address _____

Data _____

Access Size ___

Access Type _

Address Space Code _

Vector Number ____

Unsolicited Exception:

Program Counter _____

Vector Number ____

Status Register ____

Interrupt Level _

```

# **LANC - LANC Interrupts**

The **LANC** test verifies the LANC (LAN Coprocessor) interrupts. It checks that level 0 interrupts set the appropriate status and do not generate an interrupt. It then verifies that all interrupts (1 through 7) can be generated and received and that the appropriate status is set.

#### **Command Input**

177-Diag>PCC2 LANC

#### Messages

```

Interrupt Control Register did not clear

Address =_____, Expected =___, Actual =___

Interrupt Enable bit did not set

Address =____, Expected =__, Actual =__

Interrupt Status bit did not set

Status: Expected =___, Actual =___

Vector: Expected =__, Actual =__

State : IRQ Level =_, VBR =__

Incorrect Vector type

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Unexpected Vector taken

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Incorrect Interrupt Level

Level : Expected =_, Actual =_

State : IRQ Level =_, VBR =__

Interrupt did not occur

Status: Expected =___, Actual =___

Vector: Expected =__, Actual =__

State : IRQ Level =_, VBR =__

```

```

Interrupt Status bit did not set

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Interrupt Status bit did not clear

Address =____, Expected =__, Actual =__

Bus Error Information:

Address _____

Data _____

Access Size ___

Access Type _

Address Space Code _

Vector Number ____

Unsolicited Exception:

Program Counter _____

Vector Number ____

Status Register ____

Interrupt Level _

```

#### **MIEN - MIEN Bit**

The **MIEN** test uses the General Purpose I/O Interrupt Control to generate and service a level 7 interrupt with the Master Interrupt Enable bit set. The bit is then cleared and a level 7 interrupt is generated and checked for interrupt not serviced.

#### **Command Input**

177-Diag>PCC2 MIEN

#### Messages

| Interrupt did not occur                 |

|-----------------------------------------|

| Status: Expected =, Actual =            |

| <pre>Vector: Expected =, Actual =</pre> |

| State : IRQ Level =_, VBR =             |

| `MIEN' bit did not disable interrupts   |

| Status: Expected =, Actual =            |

| <pre>Vector: Expected =, Actual =</pre> |

| State : IRQ Level =_, VBR =             |

| Bus Error Information:                  |

| Address                                 |

| Data                                    |

| Access Size                             |

| Access Type _                           |

| Address Space Code _                    |

| Vector Number                           |

| Unsolicited Exception:                  |

| Program Counter                         |

| Vector Number                           |

| Status Register                         |

| Interrupt Level                         |

#### **PCLK - Prescaler Clock**

The **PCLK** test verifies the accuracy of the Prescaler Clock. Using a constant time source, it allows Tick Timer 1 to free-run for one second. It then compares the accumulated timer count with the expected count for the time period.

#### **Command Input**

177-Diag>PCC2 PCLK

#### Messages

```

Illegal prescaler calibration:

Expected EF, EC, E7, or DF, Actual = __

RTC is stopped, invoke SET command.

RTC is in write mode, invoke SET command.

RTC is in read mode, invoke SET command.

RTC seconds register didn't increment

Timer count register read greater/less than expected Address = _____, Expected = ___, Actual = ___

```

## **PRINTA - Printer ACK Interrupts**

The **PRNTA** test verifies the printer "ACK" interrupts. It checks that level 0 interrupts set the appropriate status rather than generating an interrupt. It then verifies that all interrupts (1 through 7) can be generated and received and that the appropriate status is set.

#### **Command Input**

177-Diag>PCC2 PRNTA

#### **Messages**

```

Interrupt Control Register did not clear

Address =____, Expected =__, Actual =__

Interrupt Enable bit did not set

Address =____, Expected =__, Actual =__

Interrupt Status bit did not set

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Incorrect Vector type

Status: Expected =___, Actual =___

Vector: Expected =__, Actual =__

State : IRQ Level =_, VBR =__

Unexpected Vector taken

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Incorrect Interrupt Level

Level : Expected =_, Actual =_

State : IRQ Level =_, VBR =__

Interrupt did not occur

Status: Expected =___, Actual =___

Vector: Expected =__, Actual =__

State : IRQ Level =_, VBR =__

```

```

Interrupt Status bit did not set

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Interrupt Status bit did not clear

Address =____, Expected =__, Actual =__

Bus Error Information:

Address _____

Data _____

Access Size ___

Access Type _

Address Space Code _

Vector Number ____

Unsolicited Exception:

Program Counter _____

Vector Number ____

Status Register ____

Interrupt Level _

```

# **PRINTB - Printer FAULT Interrupts**

The **PRNTB** test verifies the printer "FAULT" interrupts. It checks that level 0 interrupts set the appropriate status rather than generating an interrupt. It then verifies that all interrupts (1 through 7) can be generated and received and that the appropriate status is set.

#### **Command Input**

177-Diag>PCC2PRNTB

#### **Messages**

```

Interrupt Control Register did not clear

Address =____, Expected =__, Actual =__

Interrupt Enable bit did not set

Address =____, Expected =__, Actual =__

Interrupt Status bit did not set

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Incorrect Vector type

Status: Expected =___, Actual =___

Vector: Expected =__, Actual =__

State : IRQ Level =_, VBR =__

Unexpected Vector taken

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Incorrect Interrupt Level

Level : Expected =_, Actual =_

State : IRQ Level =_, VBR =__

Interrupt did not occur

Status: Expected =___, Actual =___

Vector: Expected =__, Actual =__

State : IRQ Level =_, VBR =__

```

```

Interrupt Status bit did not set

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Interrupt Status bit did not clear

Address =____, Expected =__, Actual =__

Bus Error Information:

Address _____

Data _____

Access Size ___

Access Type _

Address Space Code _

Vector Number ____

Unsolicited Exception:

Program Counter _____

Vector Number ____

Status Register ____

Interrupt Level _

```

# **PRINTC - Printer SEL Interrupts**

The **PRNTC** test verifies the printer "SEL" interrupts. It checks that level 0 interrupts set the appropriate status and do not generate an interrupt. It then verifies that all interrupts (1 through 7) can be generated and received and that the appropriate status is set.

#### **Command Input**

177-Diag>PCC2 PRNTC

#### Messages

```

Interrupt Control Register did not clear

Address =_____, Expected =___, Actual =___

Interrupt Enable bit did not set

Address =____, Expected =__, Actual =__

Interrupt Status bit did not set

Status: Expected =___, Actual =___

Vector: Expected =__, Actual =__

State : IRQ Level =_, VBR =__

Incorrect Vector type

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Unexpected Vector taken

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

Incorrect Interrupt Level

Level : Expected =_, Actual =_

State : IRQ Level =_, VBR =__

Interrupt did not occur

Status: Expected =___, Actual =___

Vector: Expected =___, Actual =___

State : IRQ Level =_, VBR =__

```

```

Interrupt Status bit did not set