### Datel DVMF-624C2 12-Bit, 4-Channel VMEbus D/A Board

In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/71726-1

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

Your definitive source for quality pre-owned equipment.

**Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# **User Manual** for **DVME-624**

September, 1993

8221056

11 Cabot Boulevard, Mansfield, MA 02048 U.S.A.

Tel:

(508) 339-3000

(800) 233-2765

Email: sales@datel.com

Fax:

(508) 339-6356

Data Sheet Fax Back: (508) 261-2857

Internet:

www.datel.com

#### UNPACKING

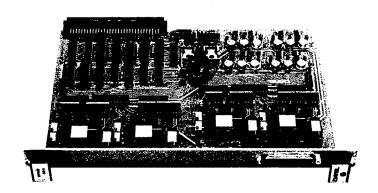

This package should contain a DVME-624 board, a user's manual and a diagnostic program on a 5 1/4" diskette. Upon receipt of this package, visually inspect the board for missing or damaged material. In the event of damage, save all packing materials and immediately notify your carrier to validate shipping claims.

### ALWAYS STORE THE BOARD IN THE ANTISTATIC COVER

This board contains components that are susceptable to static discharge, and should be handled with appopriate caution. The plastic, antistatic cover protects CMOS components from being damaged by static discharge. It also protects against dust and moisture condensation.

### RETAIN THE ORIGINAL PACKING MATERIALS

Should the board need repair at a later date, it can safely be returned if packed in the original materials.

### WARRANTY

DATEL warrants that the articles delivered are free from defects in material and workmanship under normal use and service as described in the literature for this product. Obligations under this warranty are limited to replacing or repairing, at DATEL's option, any of said articles returned to DATEL's factory within one year of shipment, with transportation charges prepaid.

### **DISCLAIMER**

All information contained within this document has been carefully checked and is believed to be entirely accurate. However, DATEL assumes no responsibilities for errors and/or omissions. DATEL reserves the right to make changes to any portion of this manual.

### PROPRIETARY NOTICE

The information and the design of equipment described herein are the property of DATEL. This document is proprietary to the company and the information contained herein is for the use of the company, its authorized representatives, and by users of the equipment. This information is not to be reprinted in whole or in part without written permission by an authorized official of DATEL. The foregoing does not apply to vendor proprietary parts.

# TABLE OF CONTENTS

|           |                                                | Page : |

|-----------|------------------------------------------------|--------|

| SECTION 1 | GENERAL INFORMATION                            | 1-1    |

| 1.1       | Introduction                                   | 1-1    |

| 1.2       | General Description                            | 1-1    |

| 1.3       | General Description                            | 1-4    |

| SECTION 2 | BOARD INSTALLATION AND JUMPERING               | 2-1    |

| 2.1       | Introduction                                   | 2-1    |

| 2.2       | Base Address Selection                         | 2-1    |

| 2.3       | Address Modifier Selection                     |        |

| 2.4       | DTACK* Delay Selection                         | 2-4    |

| 2.5       | DAC Output Range Jumpering                     |        |

| 2.6       | Current Loop Output Option                     | 2-7    |

| 2.7       | High-speed Output Settling Time Option -       | 2-7    |

| 2.8       | DAC Input Coding Jumpering                     | 2-9    |

| 2.9       | Installing The DVME-624 Into A System          | 2-10   |

| 2.10      | Typical Output Wiring                          | 2-11   |

| 2.11      | DVME-691D Screw Termination Panel              | 2-12   |

| SECTION 3 | CONNECTOR PIN ASSIGNMENTS                      | 3-1    |

| 3.1       | Introduction                                   | 3-1    |

| 3.2       | Analog Output Connector J1                     | 3-1    |

| 3.3       | Analog Output Connector J1 VMEbus Connector P1 | 3-4    |

| SECTION 4 | DVME-624 PROGRAMMING INFORMATION               | 4-1    |

| 4.1       | Introduction                                   |        |

| 4.2       | Internal Hardware Register Assignments -       | 4-1    |

| 4.3       | Board ID Prom                                  | 4-3    |

| 4.4       | DAC Data Registers                             | 4-5    |

| 4.5       | General Programming Considerations             | 4-6    |

| 4.6       | Example Program                                | 4-6    |

| 4.7       | DVME-IOTEST Test And Calibration Software      | e4-7   |

| 4.8       | Board Calibration                              | 4-7    |

| 4.9       | DVME-UTIL                                      | 4-9    |

| SECTION 5                                                                                                                                                                            | THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-1                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 5.1<br>5.2<br>5.3<br>5.4                                                                                                                                                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-1                                                                                     |

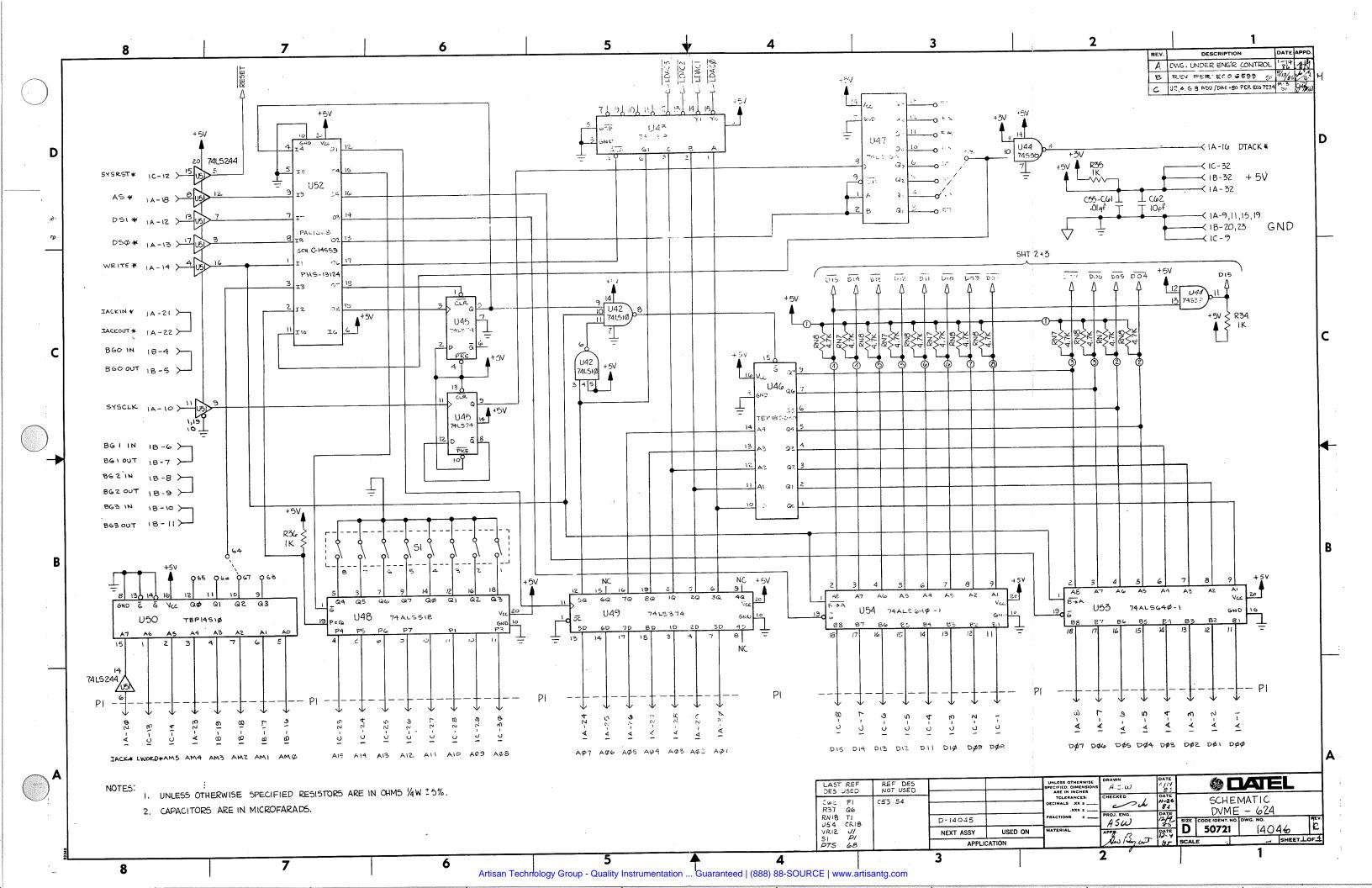

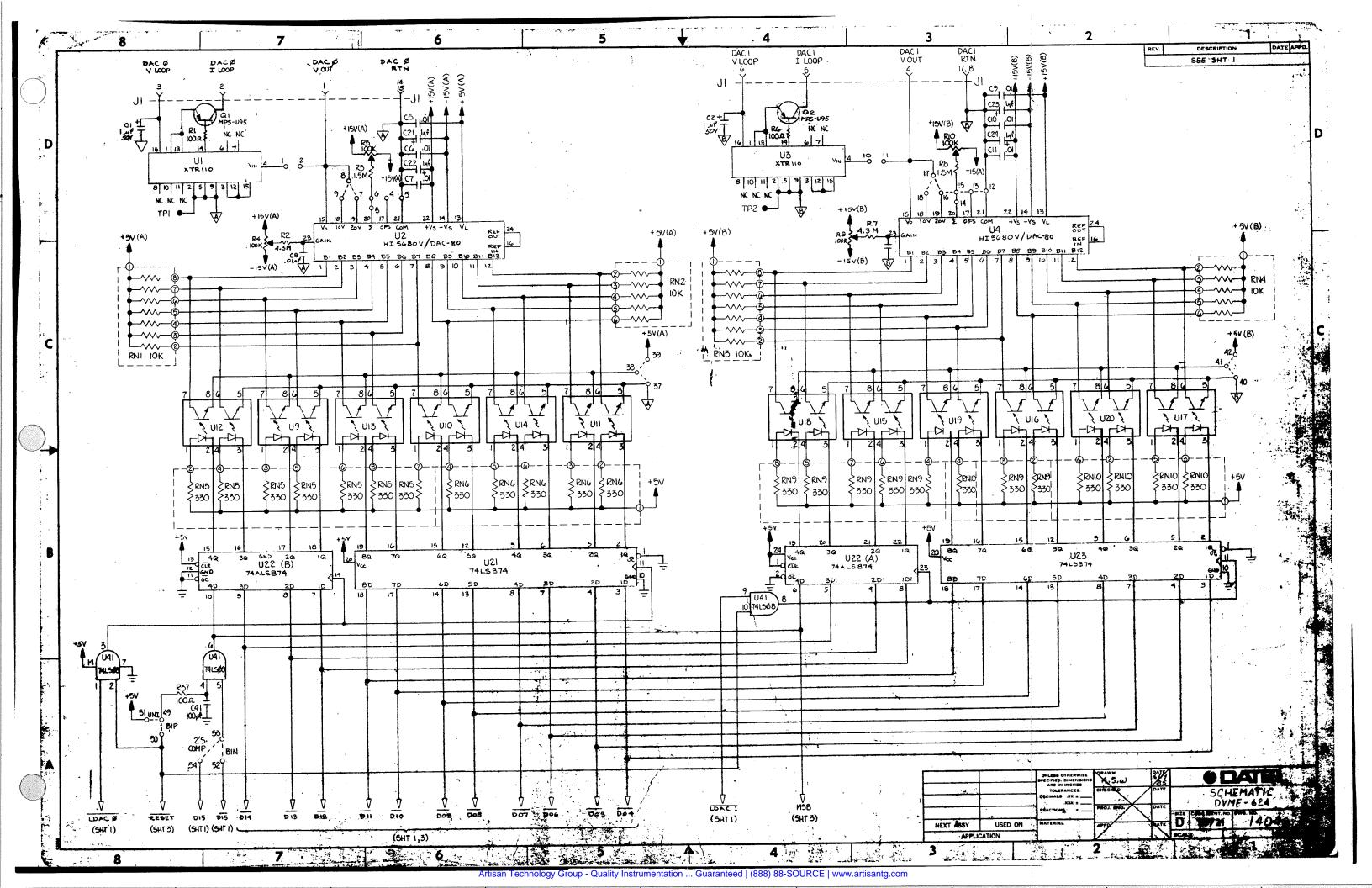

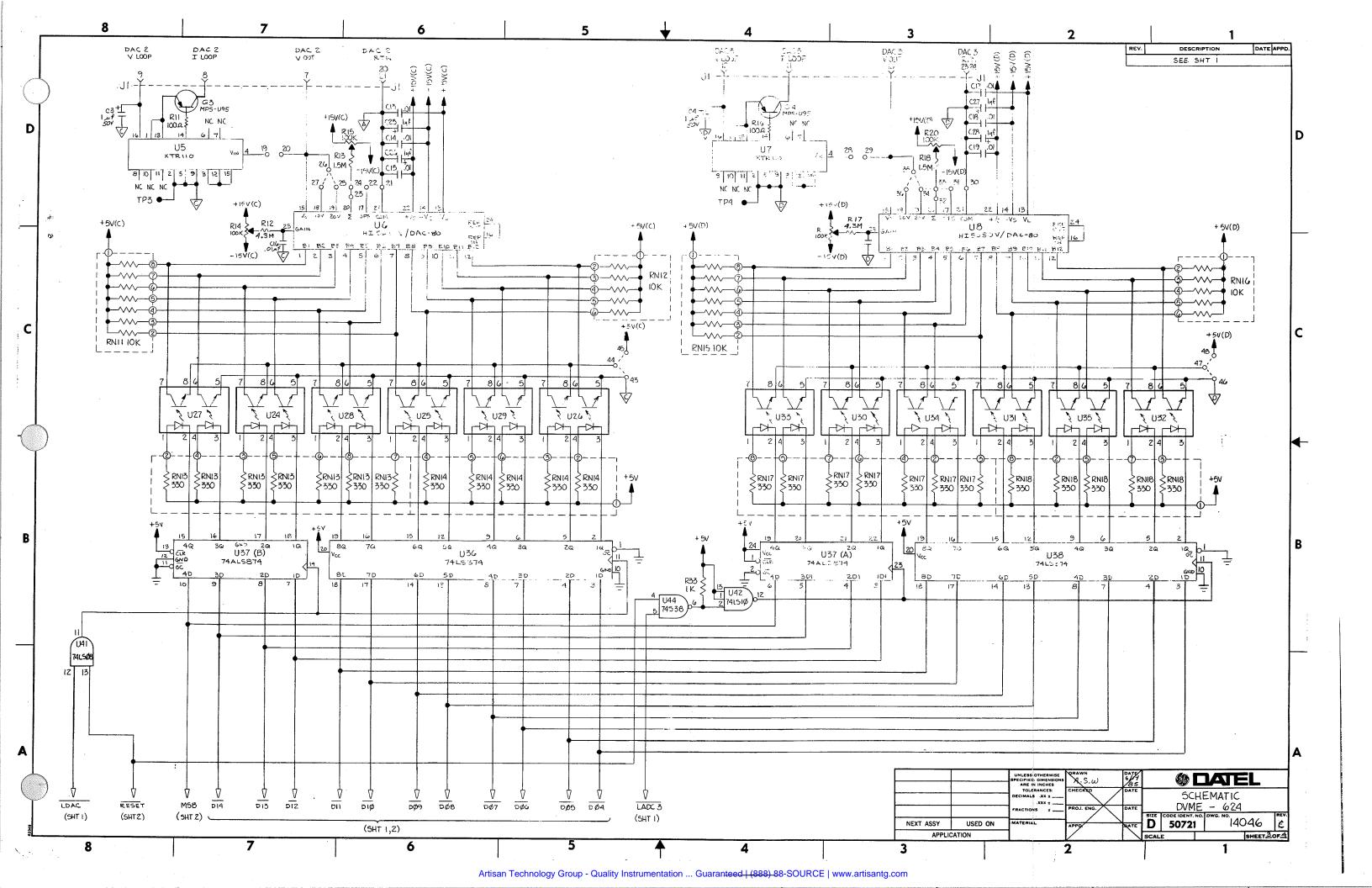

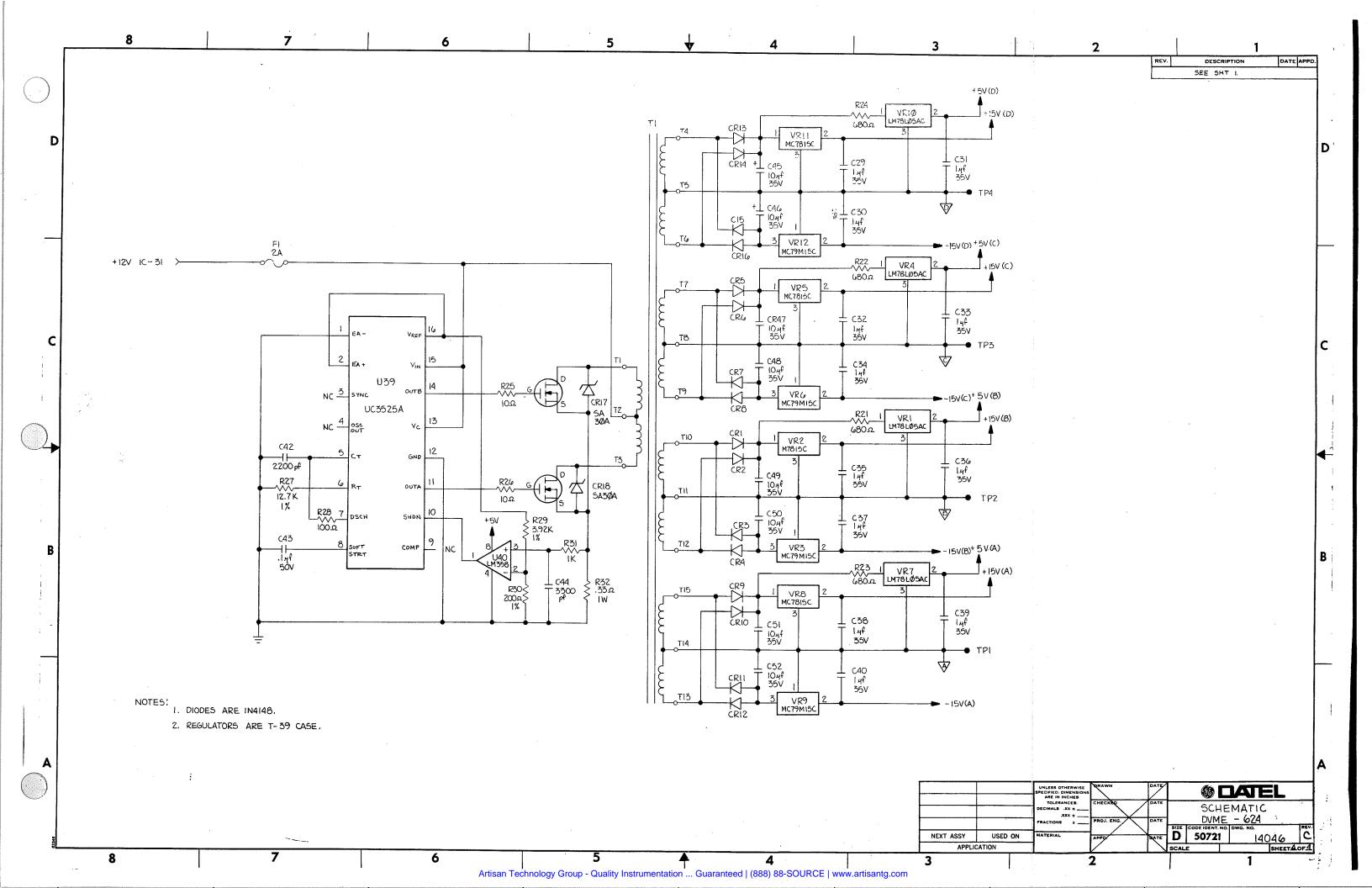

| APPENDIX A APPENDIX B APPENDIX C APPENDIX D APPENDIX E Program Exampl                                                                                                                | Schematic Assembly D/A Calibration Table Ordering Information DVME-624 Data Sheet                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

| LISTING OF FIG                                                                                                                                                                       | SURES                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

| Figure 1-1. Figure 2-1 Figure 2-2.  Figure 2-3. Figure 2-4.  Figure 3-1. Figure 4-1.                                                                                                 | Block Diagram of the DVME-624 Board Layout of the DVME-624 DVME-624 Base Address Switch Factory Setting DVME-624 Board Installation Typical Circuits for Voltage and Current Outputs 25-Pin "D" Connector Pinout of J2 D/A Register High and Low Bytes                                                                                                                                                                                 | 1-3<br>2-2<br>2-3<br>2-10<br>2-11<br>3-3<br>4-5                                         |

| Table 2-1 Table 2-2. Table 2-3. Table 2-4. Table 2-5 Table 2-6. Table 2-7. Table 3-1. Table 3-2 Table 3-3. Table 4-1. Table 4-2 Table 4-2 Table 4-3. Table 4-4. Table 4-5. Table 4-6 | [ deleted ] Address Modifier Code Jumpers DTACK* Delay Jumper DAC Output Range Jumpers (Chan 0 to 3) DAC Current Output Jumpers Optoisolator/Settling Time Jumpers DAC Input Coding Jumpers Analog Output Mating Connector Analog Output Connector J1 VMEbus P1 Pin Assignments DVME-624 Register Assignments Board Identification Code Zero/Offset Potentiometers Minus Full Scale Readings Gain Potentiometers + Full Scale readings | 2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>3-1<br>3-2<br>3-4<br>4-2<br>4-7<br>4-8<br>4-8 |

#### SECTION 1

### GENERAL INFORMATION

#### 1.1 INTRODUCTION

This manual provides the necessary information needed to configure, install, program, and fully operate DATEL's DVME-624 VMEbus D/A board. All specifications, connector pin-outs, and engineering drawings are included to assist the user in the use and implementation of the DVME-624 into its intended application.

Section one gives a general description of the DVME-624 and presents a list of the boards specifications. All information needed to set up and configure the DVME-624 for installation into VMEbus system is found in section two. Section three provides pin assignment information of all the DVME-624 connectors. Section four presents all the necessary information needed to program the DVME-624. The last section gives a more detailed description of the DVME-624's operation.

### 1.2 GENERAL DESCRIPTION

The DVME-624 is a double height (6U) VMEbus analog output module. It provides four channels of isolated digital-to-analog (D/A) conversion with 12 bits of resolution. Overall accuracy is within +/- 0.05 % of full scale range. To ensure the board's compatibility with popular process control and test instrumentation, five voltage ranges and a 4-20 mA current loop output option are jumper selectable for the D/A channels.

The DVME-624 is available in four different versions; DVME-624V1, DVME-624V2, DVME-624C1 and DVME-624C2. Each version is differentiated by output settling time and availability of 4-20mA current loop drivers. The -C suffix designates that the board provides 4-20 mA voltage-to-current converters at each output in addition to voltage outputs while the -V suffix designates that the board provides voltage outputs only. The -1 suffix specifies outputs that settle to the rated accuracy within 30 microseconds while the 2 suffix specifies a 6 microsecond settling time. The use of the term DVME-624 in this manual applies to all versions unless specifically differentiated with the V1, V2, C1, or C2 suffix.

The most important and unique feature of the DVME-624 board is its 300 Volt channel-to-channel and channel-to-bus isolation. The DVME-624 is suited for applications where high common mode voltages or actuator failure could cause high voltages to be applied to the outputs of a controlling analog output board.

Without isolation these voltages could migrate through the analog output board and interfere with the VMEbus. These type of applications often have a low level analog signal superimposed on a high voltage such as in the testing of power supplies, isolation amplifiers, etc. Isolation is accomplished through a combination of optoisolators for digital signals and transformer isolation for power distribution. Discrete on-board dc-to-dc converters provide four individually isolated supplies for each D/A converter.

The DVME-624 features a D/A converter power-on reset circuit which forces the D/A outputs to zero volts at power-on time regardless of output voltage range or input coding selection. This feature is useful where external actuators must initialize to an off state at power-on. All the analog outputs of the DVME-624 are brought out to a single DB-25 style connector on the front panel. DATEL offers a convenient screw termination panel, model DVME-691D, with cables that plug directly into the output connectors of up to two DVME-624 boards. The DVME-624 installs into the VMEbus through the Pl connector and does not utilize the P2 connector.

The DVME-624 is fully bus and card cage compatible with the VMEbus. It supports non-privileged user or supervisory short I/O addressing capabilities and is shipped as a memory mapped peripheral occupying 256 bytes in the CPU address space. The board is  $9.2"W \times 6.3"D \times 0.6"H$  (233.3 x 160 x 15.2 mm). Multiple DVME-624 boards may be mounted in adjacent card slots when used with a standard .80" spacing card cage.

The DVME-624 draws all of its power from the VMEbus +5V and +12V lines. On-board DC to DC Converters provide the isolated +/-15V to drive the board's analog circuitry. Total typical current drawn from the VMEbus +5V and +12V is 1.2 A and 0.4 A, respectively.

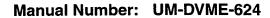

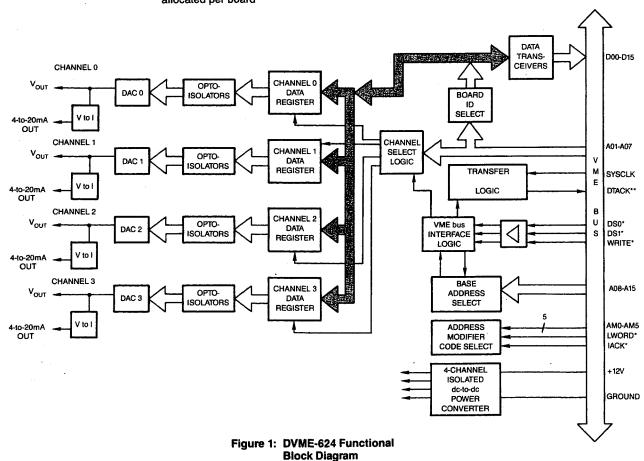

Figure 1-1. illustrates the block diagram of the DVME-624 D/A board. The board consists basically of the VMEbus interface logic, D/A converter section, isolation circuitry, data register hardware, optional 4-20 mA current loop drivers, and DC-to-DC converter circuitry.

Figure 1-1. Block Diagram of the DVME-624

#### 1.3 SPECIFICATIONS

All specifications typical at 25 degrees C, Vexc = +24VDC, RLoop = 250 ohms unless otherwise noted.

INTERFACE SPECIFICATIONS

[ comments ]

Interface

**VMEbus**

[ IEEE P1014/D1.0 ]

Al6, Dl6 slave

Data Bus

16 bits

Address Bus

Short I/O Space 16 address lines 6 address modifiers

[ Board selected by address modifiers 29h, 2Dh, 39h and

3Dh]

Interrupts

none

Memory Mapping

Short I/O

[ 256 bytes allocated

User or Supervisor per board ]

Data Transfer Acknowledge Line

DTACK\*

[ Acknowledge to the VME BUS host that data has been placed or accepted from the VMEbus data lines.]

Note: DTACK\* is derived from the 16 MHZ bus SYSCLK which must be supplied.

# CONNECTOR SPECIFICATIONS

VME BUS - P1

96 Pin Male DIN

Female Connector

Connector

Analog Output - J1

One - 25 Pin "D" Type [ Amp P/N

Amp P/N 745783-1 or

equivalent ]

| ANALOG SPECIFICATONS               |                                                                 | [ comments ]                                                                 |

|------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------|

| GENERAL - ANALOG OUTPUT            |                                                                 |                                                                              |

| Number of Channels                 | 4                                                               |                                                                              |

| Isolation                          | 300 VRMS                                                        | [sustained, max.]                                                            |

| Output Range                       | 0 to 5 V<br>0 to 10 V<br>+/- 2.5 V<br>+/- 5 V<br>+/- 10 V (std) | [jumperable]                                                                 |

|                                    | 4-20 mA                                                         | [ Current loop ]                                                             |

| Digital Input Coding               | Bipolar 2's<br>Complement                                       | [ Jumperable to Bipolar<br>Offset Binary or<br>Unipolar Straight<br>Binary ] |

| Resolution                         | 12 Bits                                                         | [ Left Justified,<br>Bits D0 through D3<br>not used ]                        |

| Reset                              | Minus Full Scale                                                | [ Output will reset<br>to 0.000 VDC<br>at power up ]                         |

| Current Loop<br>Excitation Voltage | 15-36Vdc                                                        | [ Supplied by user ]                                                         |

# PERFORMANCE - ANALOG OUTPUT

Typical at  $+25 \ \text{deg C}$ ,  $\text{Vexc} = +24 \text{VDC Rloop} = 250 \ \text{ohms unless}$  otherwise specified.

| +                                        |             |                       |                     |

|------------------------------------------|-------------|-----------------------|---------------------|

| SPECIFICATION                            | MINIMUM     | TYPICAL               | MAXIMUM             |

| Accuracy                                 | .05% of FSR |                       |                     |

| Differential nonlinearity                |             |                       | +/-0.5 LSB          |

| Zero temp<br>drift                       |             | 3 ppm/degC <br>       | 5 ppm/degC          |

| Offset temp drift                        | ·           | <br>  5 ppm/degC <br> | 10 ppm/degC         |

| Gain temp drift                          |             | <br> 15 ppm/degC      | 30 ppm/degC         |

| Settling time                            |             |                       |                     |

| DVME624-x2<br>DVME624-x1                 |             |                       | 6 u sec<br>30 u sec |

| Output current                           |             |                       | +/ <b>-</b> 5 mA    |

| Output<br>impedance                      |             | 50 mohm               |                     |

| Isolation<br>  (channel to<br>  channel) | 300 VRMS    |                       |                     |

| Isolation,<br>  output to bus            | 300 VRMS    |                       |                     |

| CURRENT LOOP DVME-624Cx only             |             |                       |                     |

| Accuracy                                 | 0.1% of FSR |                       |                     |

| Excitation                               | 15 Vdc      | 24 VDC                | 36 Vdc              |

| <br>  Load  <br>  Resistance             | 100 Ohm     |                       | 1000 Ohm            |

Page 1-6

## POWER SUPPLY AND PHYSICAL CHARACTERISTICS

# POWER SUPPLY REQUIREMENTS

+ 5VDC +/- 0.5% @ 1.0A ( 1.2A max )

+12VDC +/- 2.0% @ 0.4A ( 0.7A max )

# PHYSICAL CHARACTERISTICS

Outline Dimensions 9.19"W x 6.3"D x 0.6"H (minus connectors) (233.35 x 160 x 15.24 mm)

Weight 11 oz.

Operating Temperature Range 0 to 60 Degree C

Storage Temperature Range -20 to +80 Degree C

Relative Humidity 0 to 90% Non-Condensing

#### SECTION 2

### BOARD INSTALLATION AND JUMPERING

#### 2.1 INTRODUCTION

The DVME-624 has a base address selection DIP switch and five basic jumper blocks. The jumpers select DAC voltage output ranges, data input coding, address modifier code, DTACK\* delay, and current output option. This section describes the selection and configuration of the DVME-624 for installation into the targeted application. This section also describes how to calibrate the DVME-624 using the DVME-IOTEST menu driven test software provided.

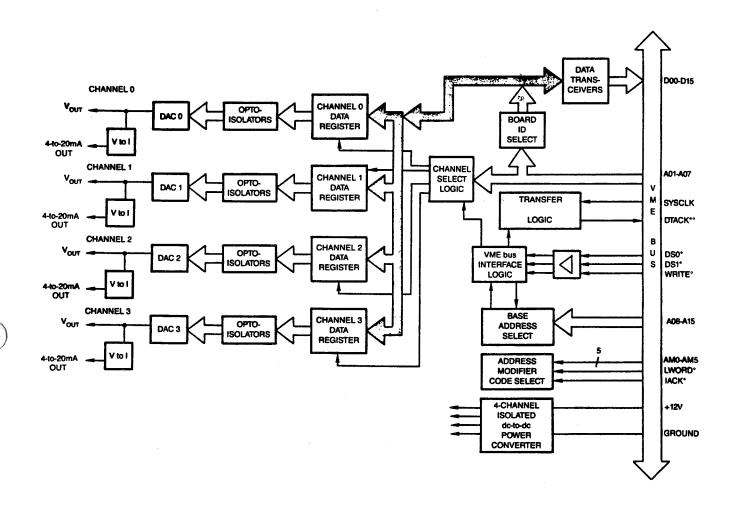

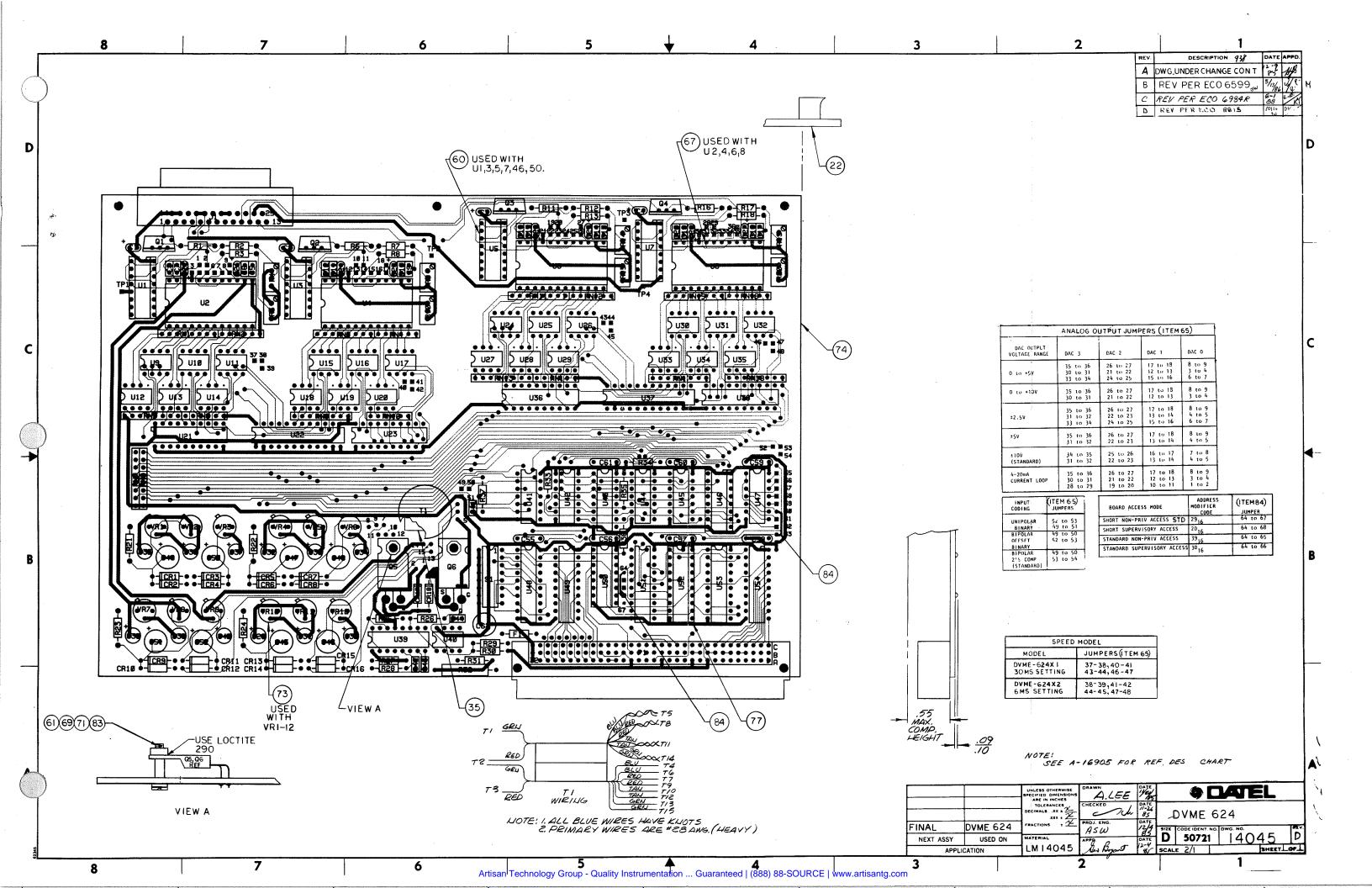

Figure 2-1 illustrates the DVME-624 board layout specifically showing switch S1, jumper, and component positioning.

### 2.2 Base Address Selection

The DVME-624 is configured to appear as 256 bytes of memory locations in the CPU's Address space. The board is shipped with a standard base address of C900 hex and is a short I/O device. It utilizes the 16 bit addressing mode of the VMEbus and responds to either Address Modifier codes 29H, 2DH, 39H or 3DH through user jumper selection. The base address of the DVME-624 is selected using DIP switch S1 which decodes VMEbus Address lines Al5 through A08. The high 8 Address lines A23 - A16 are not decoded due to short I/O addressing. Figure 2-2 shows the DVME-624's base address switch factory setting and selection convention. Note that an ON switch corresponds to a logic 0 and an OFF corresponds to a logic 1. Refer to Figure 2-1 for the location of the Base address switch S1 on the DVME-624. When selecting the base address of the DVME-624 be sure that you do not allocate any address space that overlaps with any other devices already configured in your system. In the event that more than one (1) DVME-624 D/A board is used in a system be sure to set each board to a different base address.

The base address of DATEL's DVME-624 is selectable within the range of \$0000 to \$FF00 in the short I/O address space of the targeted VMEbus system. The short I/O address space is typically mapped to addresses \$FF0000 - \$FFFFFF in the VMEbus systems memory map.

Figure 2-1. Board Layout of the DVME-624

# DVME-624 Base Address Switch Sl

When setting the base address, remember that the DVME-624 board functions in "blocks" of 256 decimal locations (100 HEX).

| X    | X    |     |          | X         | [    |      | X           |

|------|------|-----|----------|-----------|------|------|-------------|

| <br> |      | х   | х        |           | x    | x    | 1           |

| S1-8 | S1-7 |     | S1-5     | S1-4      | S1-3 | S1-2 |             |

| A15  | Al4  | A13 | A12      | All       | AlO  | A09  | <b>A</b> 08 |

| 1    | 1    | 0   | 0<br>BII | l<br>NARY | 0    | 0    | 1           |

|      | C    | :   | н        | <br>EX    | 9    |      |             |

NOTE: Lower 8 bits select the DVME-624 on-board registers. (256 locations). The upper 8 bits (A15 - A08) are not decoded by the DVME-624 and are not used for short I/O devices.

Figure 2-2. DVME-624 Base Address Switch Factory Setting

### 2.3 Address Modifier Selection

The DVME-624 Board may be jumpered to respond to one of four Address Modifier Codes on the VMEbus AM5 - AM0 lines. Normally only modifier codes 29H and 2DH should be used. These are Short I/O (16 bit address) access codes and the DVME-624 is designed as a Short I/O device. Address modifier Codes 39H and 3DH are reserved for standard (24-bit address) data access and are available for future expansion. The board is shipped standard for Short Non-Privileged and supervisory I/O Access (29 hex). Address Modifier Selection is summarized in Table 2-2. Refer to Figure 2-1 for Address Modifier Code jumper locations.

TABLE 2-2 Address Modifier Code Jumpers

| Address<br>  Modifier<br>  Code(hex) | Function                                                    | Connect  <br>  Jumper  <br>  64 to |

|--------------------------------------|-------------------------------------------------------------|------------------------------------|

| 29 or 2D                             | Short Non-Privileged or short supervisory I/O Access        | <br>  67  <br>                     |

| 2D                                   | Short Supervisory I/O Access only                           | <br>  68                           |

| 39 or 3D  <br>*                      | Standard Non-Privileged or standard supervisory Data Access | <br>  65  <br>                     |

| 3D *                                 | Standard Supervisory Data Access only                       | 66                                 |

<sup>\*</sup> Codes 39h and 3Dh are not intended for use on this board. They are used for 24-bit addressing.

# 2.4 DTACK\* Delay Selection

The DVME-624 generates a Transfer Acknowledge (DTACK) signal in response to read or write commands from the host computer.

A jumper selectable delay ranging from 125 to 1000 nanoseconds is available on the DVME-624. The DTACK\* delay is generated from the VMEbus SYSCLK signal which is assumed to have a period of 62 nsec. Note that the VMEbus SYSCLK is REQUIRED for the DVME-624 to operate. The selectable DTACK delays are mainly for use by DATEL to handle different data set up times for various present and future models. The DVME-624 comes from the factory configured with a delay of 250nS selected and should not be changed for most applications. Table 2-3 lists the selectable delay times available to the corresponding jumpers. Refer to Figure 2-1 for the location of the DTACK\* Delay jumpers.

TABLE 2-3 DTACK\* DELAY JUMPER

| DELAY (nsec)                                                        | JUMPER                                                                                |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 125<br>  250<br>  375<br>  500<br>  625<br>  750<br>  875<br>  1000 | 57 to 63   60 to 63 (standard)   61 to 63   62 to 63   59 to 63   58 to 63   56 to 63 |

# 2.5 D/A Output Range Selection

The output voltage range of the four on-board D/A converters may be jumpered as described in TABLE 2-4. The DVME-624 can be jumpered to set its outputs to zero volts on reset. If the power-on reset feature of the board is used, all four channels must be configured for either unipolar or bipolar outputs. If the reset to zero feature is not required, the output range may be individually selected. In either case, the DAC input coding is selected for the entire board. Refer to Figure 2-1 for the output voltage range jumper locations.

TABLE 2-4 DAC OUTPUT RANGE JUMPERS (CHAN 0 to 3)

| 1                          | L                                | L                                          | L                                          |                                |

|----------------------------|----------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------|

| <br>  VOLTAGE<br>  RANGE   | DAC 3                            | DAC 2                                      | DAC 1                                      | DAC 0                          |

| <br>  0 to 5V<br>          | 35 to 36<br>30 to 31<br>33 to 34 | •                                          | 17 to 18<br>  12 to 13<br>  15 to 16       | 8 to 9<br>3 to 4<br>6 to 7     |

| <br>  0 to 10V<br>         | 35 to 36<br>30 to 31             | 26 to 27<br>  21 to 22                     | <br>  17 to 18<br>  12 to 13               | 8 to 9<br>3 to 4               |

| <br>  +/-2.5V<br>          | 35 to 36<br>31 to 32<br>33 to 34 | <br>  26 to 27<br>  22 to 23<br>  24 to 25 | <br>  17 to 18<br>  13 to 14<br>  15 to 16 | 8 to 9  <br>4 to 5  <br>6 to 7 |

| <br>  +/-5V<br>            | 35 to 36<br>31 to 32             | 26 to 27<br>22 to 23                       | <br>  17 to 18<br>  13 to 14<br>           | 8 to 9<br>4 to 5               |

| <br>  +/-10V<br>  standard | 34 to 35<br>31 to 32             | <br>  25 to 26<br>  22 to 23               | <br>  16 to 17<br>  13 to 14               | 7 to 8<br>4 to 5               |

| <br>  4-20 mA              | 35 to 36<br>30 to 31<br>28 to 29 | 26 to 27<br>  21 to 22<br>  19 to 20       | 17 to 18<br>  12 to 13<br>  10 to 11       | 8 to 9  <br>3 to 4  <br>1 to 2 |

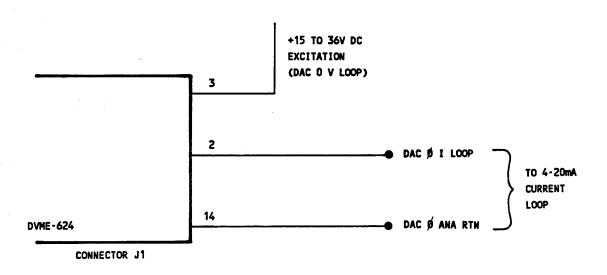

## 2.6 Current Loop Output Option

The DVME-624Cx offers 4-20mA current outputs in addition to the five selectable voltage output ranges. Each channel has its own voltage to current converter output circuitry. A user-supplied external 15 - 36V dc excitation voltage is required for each current output. Table 2-5 lists the necessary jumper selection to configure each channel for current output. Note that the digital-to-analog converter must be jumpered for 0 - 10V dc range when using current outputs. If the jumpers are not configured as listed in Table 2-5 the voltage to current converters may be damaged.

The voltage to current converter chips are socketed on the DVME-624Cx. Unpopulated sockets are on the DVME-624Vx versions. Refer to Figure 2-1 for output current component and jumper positioning.

Table 2-5: DAC Current Output Jumpers

|         | DAC                     | 3  | <br> | DAC | 2 |   | I  | DAC | 1  | + | DAC            | 0 |

|---------|-------------------------|----|------|-----|---|---|----|-----|----|---|----------------|---|

| 4-20 mA | 35 to<br>30 to<br>28 to | 31 | 21   | to  |   | İ | 12 | to  | 13 | 3 | to<br>to<br>to | 4 |

Warning: Jumpers 28 to 29, 19 to 20, 10 to 11, and 1 to 2 must be removed for any D/A converter with an output voltage range other than 0-10V dc. Other ranges could damage the voltage to current converters.

### 2.7 High-speed Output Settling Time Option

The DVME-624 is offered with a choice of one of two output settling times depending on the version selected. The lower-cost DVME-624V1 and DVME-624C1 provide outputs that settle within 30 microseconds. For more demanding high-performance applications the outputs of the DVME-624V2 and DVME-624C2 settle within 6 microseconds. Jumpers are provided on the DVME-624 board to select whether the normal or high-speed optoisolators are installed on the PC Board. Normally these jumpers are installed at the factory relative to the DVME-624 version and shouldn't be changed by the user. Table 2-6 lists the correct jumpering for each version.

TABLE 2-6 OptoIsolator/ Settling Time Jumper Settings

| Model Number | Output<br>  Settling Time | Jumpers                    |

|--------------|---------------------------|----------------------------|

| DVME-624 x 1 | 30 us                     | 37-38, 40-41, 43-44, 46-47 |

| DVME-624 x 2 | 6 uS                      | 38-39, 41-42, 44-45, 47-48 |

(The "x" refers to the "V" or "C" version)

Refer to Figure 2-1 for the location of the Opto-isolator jumpers.

## 2.8 DAC Input Coding Jumpers

The input coding for all four D/A channels is selected by jumpers on the DVME-624 board. These jumpers also cause the DAC outputs to output 0.000V at power-on regardless of whether unipolar or bipolar output is selected. Table 2-7 lists the correct jumpering corresponding to the choices of D/A input coding. Refer to Figure 2-1 for the positioning of the input coding jumpers.

TABLE 2-7 DAC INPUT CODING JUMPERS

| <del></del>                  | L                    |

|------------------------------|----------------------|

| INPUT CODING                 | JUMPER               |

| Unipolar Binary              | 52 to 53<br>49 to 51 |

| Bipolar,<br>  Offset Binary  | 49 to 50<br>52 to 53 |

| Bipolar,<br>  2's Comp (Std) | 49 to 50<br>53 to 54 |

| T                            |                      |

Refer to the Calibration Table in APPENDIX C for corresponding voltage output values for a sample of input codes in hex. Note that the column labled BIN CODE represents "offset binary" for bipolar ranges and straight binary for unipolar ranges.

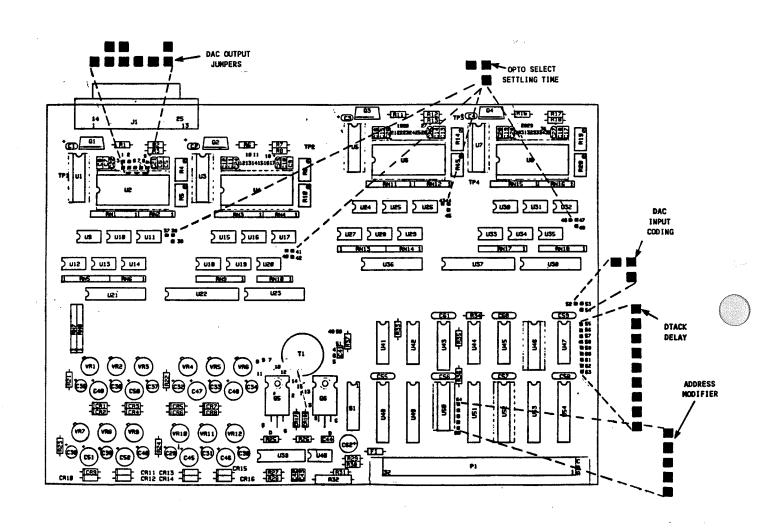

# 2.9 Installing The DVME-624 Into A System

Following the instructions in the previous section should properly configure all board jumpers. The DVME-624 is very easy to install into a VMEbus system. The following "check list" provides you with a step-by-step procedure to successfully install the DVME-624.

- 1) Remove power from the VMEbus card cage.

- 2) Rearrange the existing cards in the card cage to accommodate the new board addition(s). Study your host manuals to position the IACK and bus grant jumpers the card cage backplane. If you want interrupts from boards further away from the CPU board than the 624, they will be daisy chained by the 624. Board slots between the 624 and the CPU board must either contain boards which daisy-chains these signals or must have the backplane jumpers installed.

- 3) OBSERVE THE RULES GOVERNING ESD (ELECTROSTATIC DISCHARGE) IN THE HANDLING OF THE VMEbus BOARDS. Make yourself the same voltage potential as the grounded card cage by placing your hand on the card cage BEFORE handling the VME boards.

- 4) Carefully insert the DVME-624 board(s) into a normal 6U height slot in the VMEbus rack, making sure that the component side of the board is to the right. Make sure the Pl connector seats properly to avoid damaging it.

- 5) DO NOT CONNECT any analog output signals to the DVME-624 boards until you have read this entire manual. Figure 2-3 shows the typical installation of a DVME-624 into a VMEbus system. Note that the DVME-624 only uses the VMEbus Pl connector.

Figure 2-3. DVME-624 Board Installation

# 2.10 Typical Output Wiring

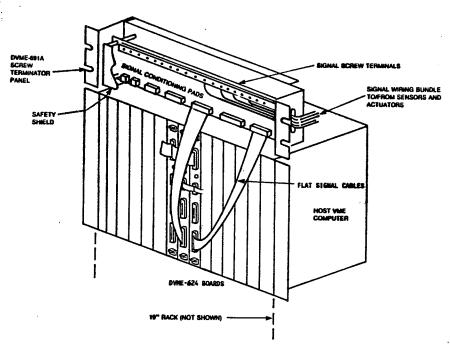

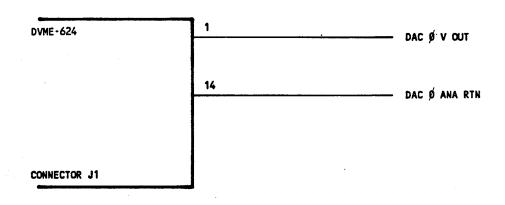

Analog outputs can be taken directly from the output connector on the DVME-624's front panel. Since its possible to have voltage or currents outputs on connector J1, it is extremely important to observe the correct channel pinouts listed in the Tables in Section 3. Figure 2-4 shows typical voltage and current output channel configurations. As an aid to connection of field wiring for each channel, DATEL offers the DVME-691D termination panel.

The following are examples of how to connect the output of the DVME-624 to your application.

VOLTAGE OUTPUT ON DAC CHANNEL Ø

Figure 2-4. Typical Circuits for Voltage and Current Outputs.

# 2.11 DVME-691D Screw Termination Panel

Datel offers a rack-mountable screw termination panel for easy connection to your application's field wiring. Located on these screw termination panels are power rails that run adjacent to each channel for an optional user-supplied excitation voltage for current outputs. Contact Datel for a data sheet on Model DVME-691A/691D.

\*

### SECTION 3

### CONNECTOR PIN ASSIGNMENTS

### 3.1 Introduction

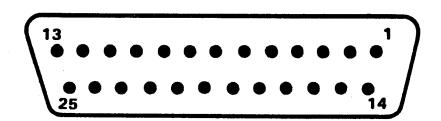

The DVME-624 has one connector on its front panel and the VMEbus P1 connector at the rear. This section shows the pin-outs of each of the DVME-624's connectors. The mating connector used to interface to the external user application circuitry is not supplied with the DVME-624. It is a common DB-25P style connector. A description and AMP part number is provided in Table 3-1 below for easy ordering information.

Table 3-1 Analog Output Connector Part Number

Description

Ordering Part Number

25-Pin D

AMP P/N 745783 or equivalent

### 3.2 Analog Output Connector Jl

The pin assignments of the DAC Analog Output connector J1 is described in Table 3-2. There is a screw termination panel available, DATEL Model DVME-691 permitting easy connection to your application field wiring. The screw termination panel eliminates the requirement for the construction of custom cable assemblies to connect the DVME-624 to the field wiring. Each DVME-624 connector has four voltage output channels. The DVME-624Cx version also supports four current outputs per connector. Two DVME-624 can be directly connected to a single DVME-691D. Note that V LOOP represents the extenal, user supplied, excitation voltage needed if current outputs are desired.

TABLE 3-2 ANALOG OUTPUT CONNECTOR J1

| PIN<br>NUMBER | DESCRIPTION   |

|---------------|---------------|

| 1             | DAC 0 V OUT   |

| 2             | DAC 0 I LOOP  |

| 3             | DAC 0 V LOOP  |

| 4             | DAC 1 V OUT   |

| 5             | DAC 1 I LOOP  |

| 6             | DAC 1 V LOOP  |

| 7             | DAC 2 V OUT   |

| 8             | DAC 2 I LOOP  |

| 9             | DAC 2 V LOOP  |

| 10            | DAC 3 V OUT   |

| 11            | DAC 3 I LOOP  |

| 12            | DAC 3 V LOOP  |

| 13            |               |

| 14            | DAC 0 ANA RTN |

| 15            | DAC 0 ANA RTN |

| 16            |               |

| 17            | DAC 1 ANA RTN |

| 18            | DAC 1 ANA RTN |

| 19            |               |

| 20            | DAC 2 ANA RTN |

| 21            | DAC 2 ANA RTN |

| 22            |               |

| 23            | DAC 3 ANA RTN |

| 24            | DAC 3 ANA RTN |

| 25            |               |

Page 3-2

Figure 3-1. 25-Pin "D" Connector Pinout of J1 (Refer to Figure 2-1 for the location of connector J1).

3.3 - This section lists the pin assignments of the VMEbus (IEEE-P1014/D1.0) P1 connector The DVME-624 is a slave output device and consequently does not utilize the bus arbitration or interrupt signals. All bus grant and interrupt acknowledge signals are jumpered by the DVME-624 so that these daisy chains are not broken. The DVME-624 does not use VMEbus connector P2.

TABLE 3-3 VMEbus Pl PIN ASSIGNMENTS

| ROW A   ROW B   ROW C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |               |                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|---------------|-----------------------------------------|

| NUMBER         MNEMONIC         MNEMONIC         MNEMONIC           1         D00         BBSY*         D08           2         D01         BCLR*         D09           3         D02         ACFAIL*         D10           4         D03         BGOIN*         D11           5         D04         BGOOUT*         D12           6         D05         BGIIN*         D13           7         D06         BGIOUT*         D14           8         D07         BG2IN*         D15           9         GND         BG2OUT*         GND           10         SYSCLK         BG3IN*         SYSFAIL*           11         GND         BG3OUT*         BERR*           12         DS1*         BR0*         SYSRESET* |        |              | 1             |                                         |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1      |              |               |                                         |

| D01   BCLR*   D09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NUMBER | MNEMONIC     | MNEMONIC      | MNEMONIC                                |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1      | D00          | BBSY*         | D08                                     |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2 j    | DOl          | BCLR*         | D09                                     |

| 5         D04         BG00UT*         D12           6         D05         BG1IN*         D13           7         D06         BG1OUT*         D14           8         D07         BG2IN*         D15           9         GND         BG2OUT*         GND           10         SYSCLK         BG3IN*         SYSFAIL*           11         GND         BG3OUT*         BERR*           12         DS1*         BR0*         SYSRESET*                                                                                                                                                                                                                                                                                | 3 j    | D02          | ACFAIL*       | D10                                     |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4      | D03          | BG0IN*        | D11                                     |

| 7 D06 BG1OUT* D14 8 D07 BG2IN* D15 9 GND BG2OUT* GND 10 SYSCLK BG3IN* SYSFAIL* 11 GND BG3OUT* BERR* 12 DS1* BR0* SYSRESET*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 j    | D04          | BG00UT*       | D12                                     |

| 8       D07       BG2IN*       D15         9       GND       BG2OUT*       GND         10       SYSCLK       BG3IN*       SYSFAIL*         11       GND       BG3OUT*       BERR*         12       DS1*       BR0*       SYSRESET*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6 j    | D05          | BG1IN*        | D13                                     |

| 9   GND   BG2OUT*   GND   10   SYSCLK   BG3IN*   SYSFAIL*   11   GND   BG3OUT*   BERR*   12   DS1*   BR0*   SYSRESET*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7 j    | D06          | BG10UT*       | D14                                     |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8 j    | D07          | BG2IN*        | D15                                     |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9 j    | GND          | BG2OUT*       | GND                                     |

| 12 DS1* BRO* SYSRESET*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10 j   | SYSCLK       | BG3IN*        | SYSFAIL*                                |

| ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11 j   | GND          | BG3OUT*       | BERR*                                   |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12     | DS1*         | BRO*          | SYSRESET*                               |

| I TO I DOO" I DAI" I IMORD"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13     | DSO*         | BR1*          | LWORD*                                  |

| 14   WRITE*   BR2*   AM5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14     | WRITE*       | BR2*          | AM5                                     |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        | GND          | BR3*          | A23                                     |

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •      | DTACK*       | AMO           | A22                                     |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        | GND          | AM1           | A21 ′                                   |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        | AS*          | AM2           | A20                                     |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ,      | GND          | AM3           | A19                                     |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        | IACK*        | GND           | A18                                     |

| 21   IACKIN*   SERCLK   A17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |              | SERCLK        |                                         |

| 22   IACKOUT*   SERDAT   A16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |              | SERDAT        |                                         |

| 23   AM4   GND   A15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |              | •             |                                         |

| 24   A07   IRQ7*   A14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |              |               | 1                                       |

| 25   A06   IRQ6*   A13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •      |              | IRQ6*         | i e e e e e e e e e e e e e e e e e e e |

| 26   A05   IRQ5*   A12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | •            |               |                                         |

| 27   A04   IRQ4*   All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | •            | <del></del>   |                                         |

| 28   A03   IRQ3*   A10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |              |               |                                         |

| 29   A02   IRQ2*   A09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | •            | <del></del>   |                                         |

| 30   A01   IRQ1*   A08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |              |               |                                         |

| 31   -12V   +5V STDBY   +12V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ,      |              |               |                                         |

| 32   +5V   +5V   +5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | <b>1</b> 577 | ⊥ <b>⊑₹</b> 7 |                                         |

#### SECTION 4

### DVME-624 PROGRAMMING INFORMATION

# 4.1 Introduction

The DVME-624 appears as a block of 256 consecutive bytes in the CPU's address space. Within the DVME-624's 256 byte block are the boards identification code and DAC data registers. The DVME-624 register assignments are straight forward and the board is easy to program. This section describes each of the DVME-624's register assignments and explains in detail how to successfully program this board.

# 4.2 Internal Hardware Register Assignments.

The DVME-624's 256 byte block of register locations are mapped into the VMEbus systems address space through the boards base address. Table 4-1 lists the DVME-624's register assignments relative to the base address setting.

TABLE 4-1 DVME-624 REGISTER ASSIGNMENTS

(All offsets are in decimal)

|                    |                                     | ·                |  |  |

|--------------------|-------------------------------------|------------------|--|--|

| BYTE ADDRESS       | FUNCTION                            | READ/WRITE       |  |  |

| <br>  Base + 0<br> | <br>  Board Identification Code<br> | Read Only        |  |  |

| <br>  Base + 63    | Board Identification Code           | Read Only        |  |  |

| Base + 64          | See Note 1                          | Read Only        |  |  |

| Base + 127         | Dec Note 1                          | Read Only        |  |  |

| Base + 128         | See Note 2                          |                  |  |  |

| Base + 159         |                                     |                  |  |  |

| Base + 160         | D/A Channel 0                       | Write Only       |  |  |

| Base + 162         | D/A Channel l                       |                  |  |  |

| Base + 164         | D/A Channel 2                       | i<br> <br>       |  |  |

| Base + 166         | D/A Channel 3                       | ;<br> <br>       |  |  |

| Base + 168         | <br>  See Note 2                    | <br>  Write Only |  |  |

| Base + 255         |                                     |                  |  |  |

Note 1: These addressss are redundant with the ID PROM addresses (Base + 0 to Base + 63).

Note 2: These addresses are redundant in 8 byte blocks with the D/A output registers ( BASE + 160 to BASE + 166)

### 4.3 Board ID PROM

DATEL DVME board products reserve the first 64 bytes of their allocated block of address space for the boards identification code. This code identifies the board model number and the number of 256 byte blocks mapped to the device. It allows the VMEbus host to easily identify the systems I/O configuration and allows the implementation of self configuring and menu driven software.

The DVME-IOTEST software provided with each of DATEL's DVME board products demonstrates one of the benefits of the ID code. It is a menu driven software package that tests any of DATEL's DVME boards given its base address. Because of the board ID code, one program can test all models by jumping into the specific test menus for each board independent of its location in the system. Without the ID code the software would have to map specific models to particular address locations.

Table 4-2 list the contents of the DVME-624's ID PROM relative to the boards base address.

Table 4-2 Board Identification Code

|                                   |                                                      |                                      | L+                                                              |

|-----------------------------------|------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------|

| BYTE ADDR                         | PROM CONTENTS                                        | ASCII EQUIV                          | FUNCTION                                                        |

| Base + 1   + 3   + 5   + 7   + 9  | 56H<br>4DH<br>45H<br>49H<br>44H                      | V<br>M<br>E<br>I<br>D                | Prom Module Identifier. This Ascii Code is always present here. |

| Base + 0B  <br>  + 0D  <br>  + 0F | 44H<br>41H<br>54H                                    | D<br>A<br>T                          | Manufacturer ID   DAT" = Datel                                  |

| Base + 11                         | 64H<br>56H<br>4DH<br>45H<br>2DH<br>36H<br>32H<br>34H | d<br>V<br>M<br>E<br>-<br>6<br>2<br>4 | Board Model No.                                                 |

| Base + 2F  <br>+                  |                                                      |                                      | Board Model No.                                                 |

| <br>  Base + 31  <br> <br>        | 31H                                                  | 1                                    | Number of 256  Byte Blocks Memory  Mapped to this  Board.       |

# 4.4 D/A Data Registers

The DVME-624 has four data registers corresponding to the four D/A output channels. Refer to Table 4-1 for the address locations of these registers. The D/A Data Registers are loaded by the host computer with the digital data to be converted and output by the D/A Converters. The D/A conversion begins on the write operation to the data registers. The register format is illustrated in Figure 4-1. Observe that the data is left justified and may be either binary or 2's complement depending on the board jumpers.

D/A DATA REGISTER HIGH BYTE (BASE+160,162,164,166)

|  | 15        | 14        | 13       | 12         | 11             | 10       | 09       | 08         |

|--|-----------|-----------|----------|------------|----------------|----------|----------|------------|

|  | BIT<br>11 | BIT<br>10 | BIT<br>9 | BIT  <br>8 | BIT<br>7<br> _ | BIT<br>6 | BIT<br>5 | BIT  <br>4 |

MSB

D/A DATA REGISTER LOW BYTE (BASE+161,163,165,167)

| 7   | 6                | 5        | 4        | 3          | 2      | 1 | 0 |

|-----|------------------|----------|----------|------------|--------|---|---|

| BIT | <br>  BIT<br>  2 | BIT<br>1 | BIT<br>0 | x<br> <br> | x<br>l | x | x |

LSB

"X" bits are don't care.

Note that some A/D - D/A converter literature refers to the MSB as bit 1. This convention for converters is because the first decision bit for successive approximation A/D's is the MSB.

Figure 4-1. D/A Register High and Low Bytes

### 4.5 General Programming Considerations

The DVME-624 responds only to word data transfers on write operations; it does not recognize byte operations on write or longword transfers on either read or write. Thus, when writing data to the board registers, word instructions (e.g. MOVE.W) must be used. Normally, the effective address will be the high (even) byte of the register. If this rule is not followed and a byte write instruction is used, the other byte of the register will be loaded with false data. If longword transfers are attempted, a bus error will result. Byte read operations will operate in the expected fashion.

### 4.6 Example Program

The following 68000 assembly language program is provided as an example to aid the user in writing application software to drive the DVME-624. In this example the factory base address setting of C900H and the standard bipolar 2's complement DAC output configuration are assumed. At the beginning of the program, the data register addresses of the DAC channels 0 through 3 are "equated" to mnemonic labels DAC0 - DAC3. The actual program performs three main functions. It clears DAC channel 0, sets DAC channel 1 to -10V dc (- FSR), and sets DAC channel 2 to +9.9951V dc (+ FSR).

```

1 00001000

ORG.L

$1000

3 00FFC9A0 DACO EQU $FFC9A0 ; DAC 0 ADDRESS

4 00FFC9A2 DAC1 EQU $FFC9A2 ; DAC 1 ADDRESS

5 00FFC9A4 DAC2 EQU $FFC9A4 ; DAC 2 ADDRESS

6 00FFC9A6 DAC3 EQU $FFC9A6 ; DAC 3 ADDRESS

7

8

;

9

10 ;

11

12

START:

13 00001000 CLR.W

DACO

;DAC 0 -> +1/2 FSR

14 00001006 MOVE.W #$8000,DAC1

;DAC 1 -> -FSR

15 0000100E MOVE.W #$7FF0,DAC2

;DAC 2 -> +FSR

16

17

END

```

# 4.7 DVME-IOTEST Test And Calibration Software

The DVME-624 comes complete with a DVME-IOTEST test and calibration software package. The use of this software is described in the self-explanatory IOTEST menus. More information can be derived by examining the source listing. For hosts other than Motorola VERSAdos, IOTEST will need modification (specifically in the TRAP system calls). After editing, the program should be assembled on the new host system. Datel also offers the IOTEST ASCII source files on 360K IBM-PC/XT/AT 5.25" disks as a universal interchange media.

## 4.8 Board Calibration

Calibration should be performed by a qualified user and he/she must have operational understanding of the DVME-624. For best performance of the DVME-624, calibration is recommended every 3 months under normal conditions. The following is the procedure to calibrate the DVME-624.

# [1.0] Equipment

- [1.1] Connect a digital voltmeter between the Analog Hi Output and the Analog Low output for the D/A channel to be calibrated. Refer to Section 4 for Jl connector pinouts. If the 4-20 mA current loop is to be calibrated, connect a 250 ohm, 0.1% resistor from the LOOP Iout pin to Analog Low. Connect the DVM across this resistor. Also, Connect a +15V to +30VDC source from the Loop V+ pin to Analog Low.

- [1.2] Load the DAC Data Register with 0000 hex for Straight Binary or 8000 hex for 2's Complement configuration. The Calibration Test software may be used to load the data value.

- [1.3] Adjust the zero or offset pot to observe a reading of minus full scale on the DVM. The offset pots for each channel are as follows:

TABLE 4-3 ZERO/OFFSET POTENTIOMETERS

| +<br> <br>+ | DAC | ZERO/OFFSET POT |

|-------------|-----|-----------------|

| i           | 0   | R5              |

| -1          | 1   | R10             |

|             | 2   | R15             |

| 1           | 3   | R20             |

| +           |     | <del> </del>    |

Refer to Figure 2-1 for the location of the Zero/Offset potentiometers.

Minus full scale readings are as follows:

TABLE 4-4 MINUS FULL SCALE READINGS

| +                                                              |                                                                         | 4        |

|----------------------------------------------------------------|-------------------------------------------------------------------------|----------|

| RANGE                                                          | -FULL SCALE READING                                                     | <u>.</u> |

| 0 to +5V<br>0 to +10V<br>+/-2.5V<br>+/-5V<br>+/-10V<br>4-20 mA | 0.0000 V<br>0.0000 V<br>-2.5000 V<br>-5.0000 V<br>-10.0000 V<br>1.0000V | T        |

[1.4] Load the DAC Data Register with FFFO hex for Straight Binary or 7FFO for 2's Complement configuration. Adjust the Gain potentiometer for the channel under calibration to produce the + Full Scale Reading on the DVM. The gain pot number and + Full Scale reading is given in Tables 4-5 and 4-6. Refer to Figure 2-1 for the location of the Gain Potentiometers.

Table 4-5 GAIN POTENTIOMETERS

| DAC | GAIN POT |

|-----|----------|

| 0   | R4       |

| 1   | R9       |

| 2   | R14      |

| 3   | R19      |

Table 4-6 + FULL SCALE READINGS

| RANGE                                                          | +FULL SCALE                                              | READING     |