# Digital I/O for PCI Express

Limited Availability

Used and in Excellent Condition

**Open Web Page**

https://www.artisantg.com/70634-1

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

TECHNOLOGY GROUP

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

#### Requirements and Compatibility | Detailed Specifications

For user manuals and dimensional drawings, visit the product page resources tab on ni.com.

Last Revised: 2010-04-08 11:04:00.0

# NI PCIe/PXIe 6535, 6536, 6537

- 10 MHz maximum clock rate

- 40 MB/s maximum throughput

- 32 channels with per-channel directional control

- Selectable voltage levels of 2.5 and 3.3 V (5 V compatible)

- Synchronous and asynchronous timing modes

- Software compatible with NI 6533 and NI 6534 NI-DAQmx applications

#### **Overview**

NI 6535, NI 6536, and NI 6537 digital I/O devices are high-speed 32-bit interfaces built on PCI Express bus technology. These cost-effective devices provide an ideal way to interface with a variety of digital applications requiring a high number of channels for digital I/O including high-speed functional digital tests, handshaking, chip testing, pattern generation, memory testing, and logic vector capture. This family features maximum clock rates of 10, 25, or 50 MHz; selectable voltage levels compatible with 2.5, 3.3, and 5 V TTL logic; and individually configured pins for input or output. With both synchronous and asynchronous timing modes, handshaking, and a software API designed around the NI-DAQmx driver, NI 6535/36/37 devices have the flexibility to meet the requirements of semiconductor, consumer electronics, and communications applications.

Back to Top

# **Requirements and Compatibility**

### **OS** Information

- Windows XP

- Windows XP x64

## **Driver Information**

• NI-DAQmx

## Software Compatibility

- ANSI C/C++

- LabVIEW

- LabVIEW Base Development System

- Measurement Studio

- Measurement Studio .NET Support

- Visual Studio

- Visual Studio .NET

Back to Top

### **Application and Technology**

### **Digital Interfacing**

- Use NI 6535/36/37 devices to interface digital systems and devices directly with PC-based applications

- Control, communicate with, or send data to a digital device or system

- Analyze and record digital data

- Perform bidirectional communications with handshaking

### **Timing Modes**

- Pattern I/O or sample clock (synchronous) transfer patterns using an internal or external clock signal

- Burst handshaking (synchronous) handshake an NI 6535, NI 6536, or NI 6537 device and the peripheral device during synchronous transfer to maximize the transfer rate

- Handshaking I/O (asynchronous) transfer patterns when both the NI 6535, NI 6536, or NI 6537 device and the peripheral device are ready

- On-demand (unstrobed or static I/O) acquire or generate data through software-timed commands

• Change detection – acquire data whenever a change occurs on one or more digital lines

### **High Signal Quality**

NI 6535/36/37 devices feature an improved architecture, offering not only higher clock rates up to 50 MHz at low cost but also superior signal integrity and impedance matching.

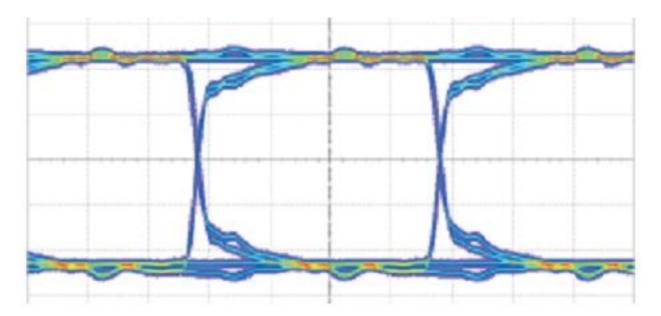

Figure 1. Eye Diagram of PXIe-6537 at 50 MHz

Improved Architecture Compatible with NI 6533 and NI 6534 Applications

These devices are ideal replacements for future-proofing applications currently using NI 6533/34 devices.

- NI 6535/36/37 devices are software-compatible with existing NI 6533/34 NI-DAQmx applications

- You can interface to existing NI 6533/34 fixtures and terminal blocks with the NI 653x cable adapter

- NI 6535/36/37 devices are compatible with most NI 6533/34 timing modes pattern I/O, handshaking, change detection, and burst

Figure 2. You can use NI 6535/36/37 devices with an NI 653x cable adapter to connect to existing NI 6533/34 applications.

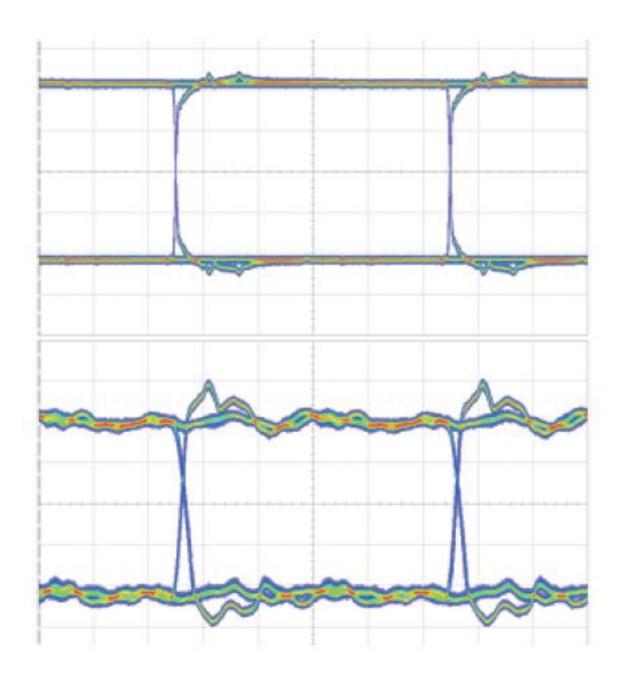

• In comparison to legacy digital I/O boards, NI 6535/36/37 devices have improved signal quality. In Figure 3, the top eye diagram is from an NI PXIe-6535 generating at 10 MHz. The bottom diagram shows an NI PXI-6534 generating a 10 MHz signal using signal termination recommended by NI.

Figure 3. Eye Diagram Comparison of the NI 6535 (top) with the NI 6534 (bottom) Using Recommended Signal Termination

#### **Connectivity Options**

To meet connectivity requirements for high-speed digital applications, you can use NI 6535/36/37 devices with a variety of accessories.

- A CB-2162 connector block

- A 50 ½ shielded flying lead cable

- A VHDCI high-density connector

### **High-Speed Data Streaming**

- Generate and acquire larger digital waveforms with PCI Express high-speed devices, using the ideal, low-cost NI 6535/36/37 devices Stream continuously at up to 200 MB/s of data

- Stream data from the host computer's memory or high-end storage solution such as NI RAID arrays and controllers

- Use for applications requiring high speeds and fast streaming capabilities such as LCD testing, wireless protocols, ADC/DAC interfacing, or digital pattern capture

- Visit ni.com/streaming for more information

### **Multidevice Synchronization**

These products use the PXI trigger bus or RTSI bus to send and receive clock and trigger signals to and from other NI 6535/36/37 devices in your system. With these capabilities, you can create synchronized systems with large numbers of digital I/O lines.

Back to Top

www.ni.com

### **Support and Services**

### **System Assurance Programs**

NI system assurance programs are designed to make it even easier for you to own an NI system. These programs include configuration and deployment services for your NI PXI, CompactRIO, or Compact FieldPoint system. The NI Basic System Assurance Program provides a simple integration test and ensures that your system is delivered completely assembled in one box. When you configure your system with the NI Standard System Assurance Program, you can select from available NI system driver sets and application development environments to create customized, reorderable software configurations. Your system arrives fully assembled and tested in one box with your software preinstalled. When you order your system with the standard program, you also receive system-specific documentation including a bill of materials, an integration test report, a recommended maintenance plan, and frequently asked question documents. Finally, the standard program reduces the total cost of owning an NI system by providing three years of warranty coverage and calibration service. Use the online product advisors at ni.com/advisor to find a system assurance program to meet your needs.

#### Calibration

NI measurement hardware is calibrated to ensure measurement accuracy and verify that the device meets its published specifications. NI offers a number of calibration services to help maintain the ongoing accuracy of your measurement hardware. These services allow you to be completely confident in your measurements, and help you maintain compliance to standards like ISO 9001, ANSI/NCSL Z540-1 and ISO/IEC 17025. To learn more about NI calibration services or to locate a qualified service center near you, contact your local sales office or visit ni.com/calibration.

### **Technical Support**

Get answers to your technical questions using the following National Instruments resources.

- **Support** Visit ni.com/support to access the NI KnowledgeBase, example programs, and tutorials or to contact our applications engineers who are located in NI sales offices around the world and speak the local language.

- Discussion Forums Visit forums.ni.com for a diverse set of discussion boards on topics you care about.

- Online Community Visit community.ni.com to find, contribute, or collaborate on customer-contributed technical content with users like you.

### Repair

While you may never need your hardware repaired, NI understands that unexpected events may lead to necessary repairs. NI offers repair services performed by highly trained technicians who quickly return your device with the guarantee that it will perform to factory specifications. For more information, visit ni.com/repair.

#### **Training and Certifications**

The NI training and certification program delivers the fastest, most certain route to increased proficiency and productivity using NI software and hardware. Training builds the skills to more efficiently develop robust, maintainable applications, while certification validates your knowledge and ability.

- Classroom training in cities worldwide the most comprehensive hands-on training taught by engineers.

- On-site training at your facility an excellent option to train multiple employees at the same time.

- Online instructor-led training lower-cost, remote training if classroom or on-site courses are not possible.

- Course kits lowest-cost, self-paced training that you can use as reference guides.

- Training memberships and training credits to buy now and schedule training later.

Visit ni.com/training for more information.

### **Extended Warranty**

NI offers options for extending the standard product warranty to meet the life-cycle requirements of your project. In addition, because NI understands that your requirements may change, the extended warranty is flexible in length and easily renewed. For more information, visit ni.com/warranty.

#### **OEM**

NI offers design-in consulting and product integration assistance if you need NI products for OEM applications. For information about special pricing and services for OEM customers, visit ni.com/oem.

#### **Alliance**

Our Professional Services Team is comprised of NI applications engineers, NI Consulting Services, and a worldwide National Instruments Alliance Partner program of more than 600 independent consultants and integrators. Services range from start-up assistance to turnkey system integration. Visit ni.com/alliance.

Back to Top

www.ni.com

# **Detailed Specifications**

This document provides the specifications for the NI PXIe/PCIe-6535/6536/6537 (NI 6535/6536/6537).

Typical values are representative of an average unit operating at room temperature. Specifications are subject to change without notice. For the most recent NI 6535/6536/6537 specifications, visit ni.com/manuals.

# **Channel Specifications**

| Specification                                            | Value                                                                                                                                                                                   |               |  |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|

| Number of data channels                                  | 32                                                                                                                                                                                      |               |  |

| Direction control of data channels                       | Per channel                                                                                                                                                                             |               |  |

| Number of Programmable Function Interface (PFI) channels | 6                                                                                                                                                                                       |               |  |

| Direction control of PFI channels                        | Per channel                                                                                                                                                                             |               |  |

| Number of RTSI/PXI trigger channels                      | PXI Express                                                                                                                                                                             | PCI Express   |  |

|                                                          | 10 (PXI_TRIG<07>, PXIe_DSTARB, PXIe_DSTARC)                                                                                                                                             | 8 (RTSI <07>) |  |

| Direction control of RTSI/PXI trigger channels           | RTSI <07>/PXI_TRIG<07>: Bidirectional; per channel PXIe_DSTARB: Unidirectional input (PXI Express only) PXIe_DSTARC: Unidirectional output (PXI Express only)                           |               |  |

| Number of Sample clock terminals                         | 3 bidirectional clock terminals (PFI 4, PFI 5, RTSI 7)  1 exported clock terminal (PXIe_DSTARC) (PXI Express only)  2 clock source terminals (PXIe_DSTARA, PXI_STAR) (PXI Express only) |               |  |

Generation Channels (Data and PFI <0..5> Channels)

| Specification                              |                                                             | Value                                |                     |         |  |

|--------------------------------------------|-------------------------------------------------------------|--------------------------------------|---------------------|---------|--|

| Generation voltage families                | 2.5 V, 3.3 V (5 V TTL co                                    | 2.5 V, 3.3 V (5 V TTL compatible)    |                     |         |  |

| Generation signal type                     | Single-ended                                                |                                      |                     |         |  |

| Generation voltage levels                  | Low Voltage Levels                                          |                                      | High Voltage Levels |         |  |

|                                            | Typical                                                     | Maximum                              | Minimum             | Typical |  |

| 2.5 V                                      | 0.0 V                                                       | 0.1 V                                | 2.4 V               | 2.5 V   |  |

| 3.3 V                                      | 0.0 V                                                       | 0.1 V                                | 3.2 V               | 3.3 V   |  |

| 5.0 V                                      | 0.0 V                                                       | 0.1 V                                | 3.2 V               | 3.3 V   |  |

| Output impedance                           | 50 Ω, nominal                                               | 50 Ω, nominal                        |                     |         |  |

| Maximum DC drive strength                  | ±16 mA at 2.5 V                                             |                                      |                     |         |  |

|                                            | ±32 mA at 3.3 V                                             | ±32 mA at 3.3 V                      |                     |         |  |

| Data channel driver enable/disable control | Per channel                                                 |                                      |                     |         |  |

| Channel power-up state                     | Software programmable (Tristate, 0, or 1 at 2.5 V or 3.3 V) |                                      |                     |         |  |

| Output protection                          | The device can indefinite                                   | ely sustain a short to any voltage b | etween 0 V and 5 V. |         |  |

# Acquisition Channels (Data and PFI <0..5> Channels)

| Specification                | Value                                            |         | Comments                                                                         |

|------------------------------|--------------------------------------------------|---------|----------------------------------------------------------------------------------|

| Acquisition voltage families | 2.5 V, 3.3 V (5 V TTL compatible)                |         | _                                                                                |

| Acquisition voltage levels   | Low Voltage Thresholds High Voltage Thresholds — |         | _                                                                                |

|                              | Maximum                                          | Minimum |                                                                                  |

| 2.5 V                        | 0.75 V                                           | 1.75 V  |                                                                                  |

| 3.3 V                        | 1.00 V                                           | 2.30 V  |                                                                                  |

| 5.0 V                        | 1.00 V                                           | 2.30 V  |                                                                                  |

| Input impedance              | High-impedance (50 kΩ to ground)                 |         | _                                                                                |

| Input protection             |                                                  |         | Diode clamps in the design may provide additional protection outside this range. |

# Timing Specifications

Sample Clock

| Specification                           | V                                                         | Value                                                                  |                                      |  |

|-----------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------|--|

| Sample clock sources                    | 1. On Board Clock (Sample Clock Timebas                   | On Board Clock (Sample Clock Timebase with divider)                    |                                      |  |

|                                         | 2. PFI <45>                                               | NI 6535/6536/6537 Help<br>for an illustration of the various clock and |                                      |  |

|                                         | 3. PXI_TRIG 7 (PXI backplane—PXI Expreonly)               | timebase sources.                                                      |                                      |  |

|                                         | 4. PXI_STAR (PXI backplane—PXI Expres                     | s only)                                                                |                                      |  |

|                                         | 5. PXIe_DSTARA (PXI backplane—PXI Ex                      | press only)                                                            |                                      |  |

| Sample clock timebase sources           | 1. 200 MHz Timebase (internal oscillator)                 |                                                                        |                                      |  |

|                                         | 2. PFI <05>                                               |                                                                        |                                      |  |

|                                         | 3. PXI_TRIG<06> (PXI backplane—PXI E Express only)        | express only) RTSI <07> (RTSI bus—PCI                                  |                                      |  |

|                                         | 4. PXIe_DSTARB (PXI backplane—PXI Ex                      | press only)                                                            |                                      |  |

| On Board Clock frequency range          | NI 6535: 48 Hz to 10 MHz Configurable to                  | 200 MHz/N; 20 ≤ N ≤ 4,194,307                                          | _                                    |  |

|                                         | NI 6536: 48 Hz to 25 MHz Configurable to                  | 200 MHz/N; 8 ≤ N ≤ 4,194,307                                           |                                      |  |

|                                         | NI 6537: 48 Hz to 50 MHz Configurable to                  | 200 MHz/N; 4 ≤ N ≤ 4,194,307                                           |                                      |  |

| Imported Sample clock frequency range   | PFI <45>                                                  | PXI_TRIG 7 (PXIe Only)                                                 | _                                    |  |

|                                         | PXIe_DSTARA (PXIe Only)                                   | RTSI 7 (PCIe Only)                                                     |                                      |  |

|                                         | NI 6535: 0 Hz to 10 MHz                                   | NI 6535: 0 Hz to 10 MHz                                                |                                      |  |

|                                         | NI 6536: 0 Hz to 25 MHz                                   | NI 6536/6537: 0 Hz to 25 MHz                                           |                                      |  |

|                                         | NI 6537: 0 Hz to 50 MHz                                   |                                                                        |                                      |  |

| Minimum detectable Sample clock pulse   | PFI <45>                                                  | PXI_TRIG 7 (PXIe Only)                                                 | Positive and negative pulse width at |  |

| width                                   | PXIe_DSTARA (PXIe Only)                                   | RTSI 7 (PCIe Only)                                                     | voltage thresholds.                  |  |

|                                         | 8 ns                                                      | 15 ns                                                                  |                                      |  |

| Imported timebase clock frequency range | PFI <05>                                                  | PXI_TRIG 7 (PXIe Only)                                                 |                                      |  |

|                                         | PXIe_DSTARB (PXIe Only)                                   | RTSI 7 (PCIe Only)                                                     |                                      |  |

|                                         | NI 6535: 0 Hz to 10 MHz                                   | NI 6535: 0 Hz to 10 MHz                                                |                                      |  |

|                                         | NI 6536: 0 Hz to 25 MHz                                   | NI 6536/6537: 0 Hz to 25 MHz                                           |                                      |  |

|                                         | NI 6537: 0 Hz to 50 MHz                                   |                                                                        |                                      |  |

| Minimum detectable imported timebase    | PFI <45>                                                  | PXI_TRIG 7 (PXIe Only)                                                 | Positive and negative pulse width at |  |

| clock pulse width                       | PXIe_DSTARB (PXIe Only)                                   | RTSI 7 (PCIe Only)                                                     | voltage thresholds.                  |  |

|                                         | 6.5 ns                                                    | 15 ns                                                                  |                                      |  |

| Exported Sample clock destinations      | Generation                                                | Acquisition                                                            | _                                    |  |

|                                         | 1. PFI 4                                                  | PFI 5                                                                  |                                      |  |

|                                         | 2. RTSI 7 (PCI Express only) PXI_TRIG7 (PXI Express only) |                                                                        |                                      |  |

|                                         | 3. PXIe_DSTARC (PXI Express only)                         |                                                                        |                                      |  |

www.ni.com

| Exported Sample clock duty cycle | Internal Sample clock or divided-down timebase: 33% to 67% Imported Sample clock: | Typical. |

|----------------------------------|-----------------------------------------------------------------------------------|----------|

|                                  | Limited by input duty cycle                                                       |          |

# Pattern Generation Timing (Data and PFI 5 Channels)

| Specification                                              | Value                                                                        |                   | Comments                                                                     |  |

|------------------------------------------------------------|------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------|--|

| Maximum data channel toggle rate                           | NI 6535: 5.0 MHz                                                             |                   | _                                                                            |  |

|                                                            | NI 6536: 12.5 MHz                                                            | II 6536: 12.5 MHz |                                                                              |  |

|                                                            | NI 6537: 25.0 MHz                                                            | I 6537: 25.0 MHz  |                                                                              |  |

| Data position modes                                        | Data Channels                                                                | PFI Channels      | Relative to Sample clock; Active edge may                                    |  |

|                                                            | Active edge, Inactive edge                                                   | Active edge       | be rising or falling.                                                        |  |

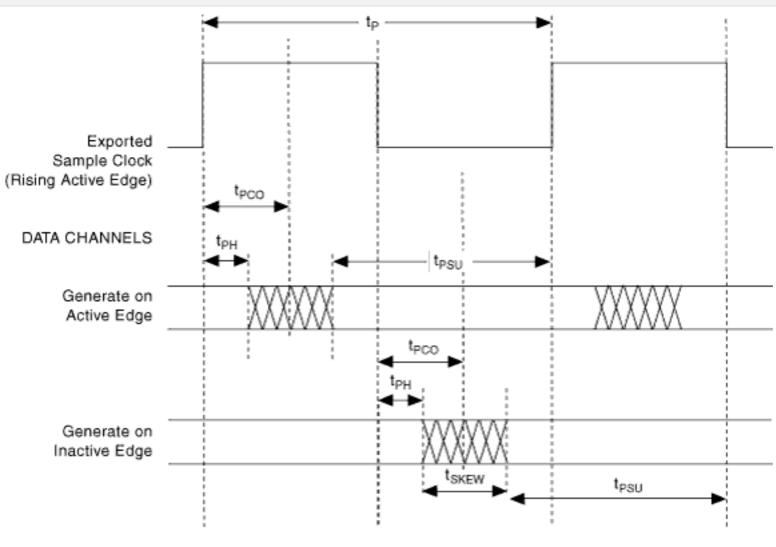

| Exported Sample Clock Offset (t <sub>PCO</sub> )           | 3.1 ns                                                                       |                   | Typical.                                                                     |  |

| Minimum provided hold time with respect to                 | PXI Express                                                                  | PCI Express       | t <sub>P</sub> is the Sample clock interval; values                          |  |

| PFI 4 (t <sub>PH</sub> )                                   | 750 ps                                                                       | 1.1 ns            | assume the sample is generated and acquired on the same clock edge; includes |  |

| Minimum provided setup time with respect to PFI 4 (t_psi_) | Sample clock interval $(t_p)$ – 5.35 ns Sample clock interval $(t_p)$ – 5 ns |                   | maximum channel-to- channel skew; valid for all data and events.             |  |

### **Provided Setup and Hold Times**

$t_P = \frac{1}{f}$  = Period of Sample Clock

$t_{\text{PH}}$  = Minimum Provided Hold Time

$t_{\text{PSU}}$  = Minimum Provided Setup Time

t<sub>PCO</sub> = Time from Rising Clock Edge to Data Transition (Provided Clock to Out Time)

t<sub>SKEW</sub> = Maximum Channel-to-Channel Skew and Clock Uncertainty

### Pattern Acquisition Timing (Data and PFI 5 Channels)

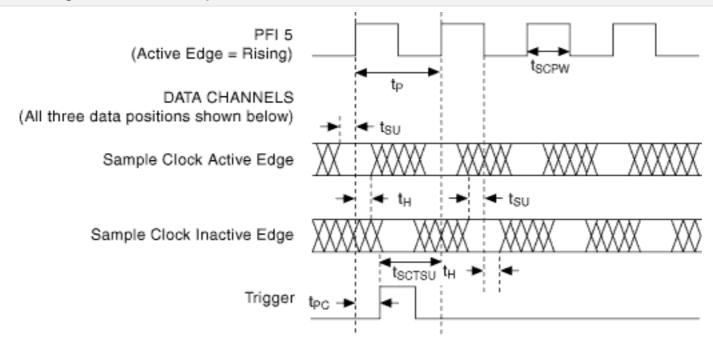

| Specification                                          | Value                                                 |                    | Comments                                                                          |

|--------------------------------------------------------|-------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------|

| Setup time with respect to PFI 5 (t <sub>SU</sub> )    | PXI Express / PCI Express Rev C <sup>*</sup> or later | PCI Express Rev B* | Maximum required; includes maximum data channel-to- channel skew; valid for       |

|                                                        | 2.8 ns                                                | 2.0 ns             | data and all triggers except the Start trigger when using the Sample Clock sample |

| Hold time with respect to PFI 5 (t <sub>H</sub> )      | PXI Express / PCI Express Rev C <sup>*</sup> or later | PCI Express Rev B* | timing type.  * Refer to assembly number sticker for                              |

|                                                        | 1.5 ns                                                | 2.0 ns             | revision information.                                                             |

| Setup time of triggers with respect to PFI 5 (t_SCTSU) |                                                       |                    | Maximum required; Sample Clock sample timing type only.                           |

| Trigger delay from PFI 5 to trigger edge (tpc)         | 2 ns                                                  |                    |                                                                                   |

www.ni.com

### Acquisition Timing Diagram Using PFI 5 as the Sample Clock

t<sub>SU</sub> = Setup Time with Respect to PFI 5

t<sub>H</sub> = Hold Time with Respect to PFI 5

$t_P = \frac{1}{f} = Sample Clock Period$

t<sub>SCPW</sub> = Minimum Detectable Sample Clock Pulse Width

t<sub>PC</sub> = Trigger Delay from PFI 5 to Trigger Edge\*

t<sub>SCTSU</sub> = Setup Time of Trigger with Respect to PFI 5\*

\*Sample Clock Sample Timing Type only.

### Handshaking

| Specification                                                  | Value                                        | Comments                   |

|----------------------------------------------------------------|----------------------------------------------|----------------------------|

| Asynchronous handshaking modes                                 | Handshake (8255) sample timing type          | 8255 emulation equivalent. |

| Synchronous handshaking modes                                  | Burst sample timing type                     | _                          |

|                                                                | 2. Pipelined Sample Clock sample timing type |                            |

| Control line polarity                                          | 1. Active high                               | _                          |

|                                                                | 2. Active low                                |                            |

| Programmable delay resolution for Handshake sample timing type | 20 ns                                        | _                          |

### **Change Detection**

www.ni.co

| Specification               | Value                                                                  | Comments                     |

|-----------------------------|------------------------------------------------------------------------|------------------------------|

| Change detection resolution | Sample clock period                                                    | _                            |

| Sources                     | P0.<07>, P1.<07>, P2.<07>, P3.<07>                                     | Per data channel selectable. |

| Valid sample position       | Active edge     Inactive edge                                          | Per data channel selectable. |

|                             | 1. Don't care 2. Rising edge 3. Falling edge 4. Rising or falling edge | Per data channel selectable. |

# **Waveform Specifications**

# Memory

| Specification                   | Value                                                      | Comments                  |

|---------------------------------|------------------------------------------------------------|---------------------------|

| Onboard memory size             | 2,048 samples (S)                                          | First-in first-out based. |

| Transfer type                   | DMA     Programmed I/O (On Demand sample timing type only) |                           |

| Generation waveform quantum     | Waveform size must be an integer multiple of 1 S.          | _                         |

| Acquisition minimum buffer size | 2 S                                                        | _                         |

# Triggers

www.ni.com

| Specification                                                                                     | Value                                                                                                              |                                                      | Comments                    |                                                                                                        |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------|

| Supported triggers (by sample                                                                     | Sample Timing Type                                                                                                 | Acquisition                                          | Generation                  | Generation operations do not                                                                           |

| timing type)                                                                                      | Sample Clock                                                                                                       | Start, Reference                                     | Start                       | support pattern match triggers.                                                                        |

|                                                                                                   | Pipelined Sample Clock                                                                                             | Pause, Start, Reference                              | Pause, Start                |                                                                                                        |

|                                                                                                   | Burst Handshake                                                                                                    | Pause (not including the pattern match type trigger) | Pause                       |                                                                                                        |

|                                                                                                   | Handshake                                                                                                          | Handshake                                            | Handshake                   |                                                                                                        |

|                                                                                                   | Change Detection                                                                                                   | Start                                                | N/A                         |                                                                                                        |

| Sources                                                                                           | 1. PFI <05> (DDC connector)                                                                                        | •                                                    | •                           | _                                                                                                      |

|                                                                                                   | 2. PXI_TRIG<06> (PXI backplar                                                                                      | ne—PXI Express only) RTSI <07>                       | (RTSI bus—PCI Express only) |                                                                                                        |

|                                                                                                   | 3. PXIe_DSTARB (PXI backplane                                                                                      | PXI Express only)                                    |                             |                                                                                                        |

|                                                                                                   | 4. Pattern match (Acquisition sess                                                                                 | sions only)                                          |                             |                                                                                                        |

|                                                                                                   | 5. Disabled (Do not wait for a trigg                                                                               | ger)                                                 |                             |                                                                                                        |

| Trigger detection                                                                                 | 1. Start Trigger (Edge detection: r                                                                                | ising or falling; Pattern match: matc                | ch or does not match)       | _                                                                                                      |

|                                                                                                   |                                                                                                                    | : high or low; Pattern match: match                  | •                           |                                                                                                        |

|                                                                                                   |                                                                                                                    | tion: rising or falling; Pattern match:              |                             |                                                                                                        |

|                                                                                                   | 4. Handshaking Trigger (Interlock                                                                                  |                                                      |                             |                                                                                                        |

|                                                                                                   |                                                                                                                    | 4. Handshaking Trigger (interlocked. high or low)    |                             |                                                                                                        |

| Destinations                                                                                      | 1. PFI <05> (DDC Connector)                                                                                        |                                                      |                             |                                                                                                        |

|                                                                                                   | 2. PXI_TRIG<07> (PXI backplar                                                                                      |                                                      |                             |                                                                                                        |

|                                                                                                   | 3. PXIe_DSTARC (PXI backplane                                                                                      | e—PXI Express only)                                  |                             |                                                                                                        |

| Delay from Pause trigger to                                                                       | Generation Acquisition                                                                                             |                                                      | Acquisition                 | Use the Data Active event during                                                                       |

| Paused state (t <sub>P2S</sub> )                                                                  | Minimum                                                                                                            | Maximum                                              |                             | generation operations to determine on a sample-by-                                                     |

|                                                                                                   | 6 sample clock cycles + 6.7 ns                                                                                     | PCI Express: 7 sample clock cycles + 15.4 ns         | Synchronous to the data     | sample basis when the NI device has entered the Paused state.                                          |

|                                                                                                   |                                                                                                                    | PXI Express: 7 sample clock cycles + 17 ns           |                             | Pause trigger only supported by Pipelined Sample Clock sample timing type.                             |

| Delay from trigger to digital data                                                                | Generation                                                                                                         |                                                      | Acquisition                 | Guaranteed by design.                                                                                  |

| output (t <sub>T2D</sub> )                                                                        | Minimum                                                                                                            | Maximum                                              |                             |                                                                                                        |

|                                                                                                   | 65 ns                                                                                                              | 1 sample clock cycle + 130 ns                        | N/A                         |                                                                                                        |

| Minimum detectable trigger pulse width $(t_{\overline{W}})$                                       | Sample Clock Sample Timing Type Triggers and Pipelined Sample Timing Type Generation Start Trigger Trigger Trigger |                                                      |                             | Maximum required pulse width to guarantee sampling by an asynchronous clock; synchronous               |

|                                                                                                   | 10 ns Sample clock period + 4 ns                                                                                   |                                                      |                             | triggers have same setup and hold requirements as data.                                                |

| Maximum required setup and hold of Sample Clock sample timing type triggers with respect to PFI 5 | Refer to the Pattern Acquisition Timing (Data and PFI 5 Channels) section of this document.                        |                                                      |                             | _                                                                                                      |

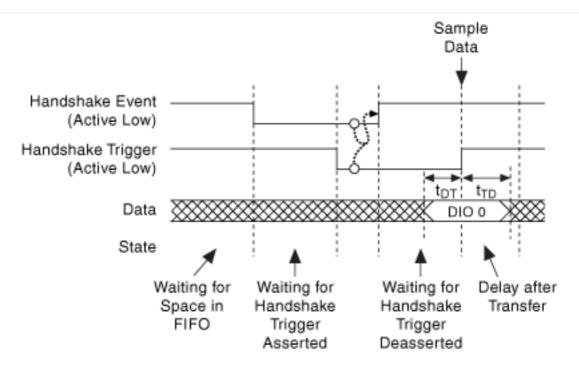

| Maximum required delay from data to Handshake trigger (t <sub>DT</sub> )                          | 5 ns                                                                                                               |                                                      |                             | Maximum required time between data valid and the Handshake trigger; Handshake sample timing type only. |

www.ni.com

| Maximum required delay from     | 50 ns | Maximum required time between    |

|---------------------------------|-------|----------------------------------|

| Handshake trigger to data (t_n) |       | the Handshake Trigger and data   |

| ID.                             |       | invalid; Handshake sample timing |

|                                 |       | type only.                       |

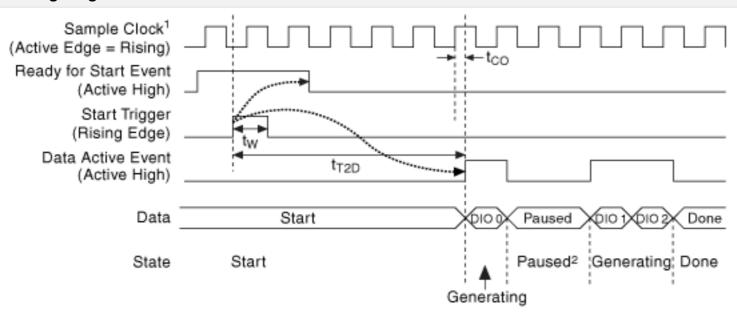

### **Pipelined Generation Timing Diagram**

<sup>&</sup>lt;sup>1</sup> Must be free-running.

t<sub>W</sub> = Minimum detectable trigger pulse width.

t<sub>CO</sub> = Exported Sample clock offset.

$t_{T2D}$  = Delay from trigger to digital data out.

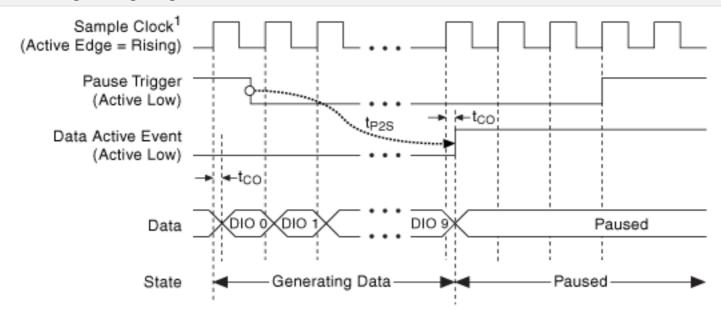

### **Pipelined Generation Handshaking Timing Diagram**

Must be free-running.

t<sub>P2S</sub> = Pause trigger to Paused state.

t<sub>CO</sub> = Exported Sample clock offset.

### Handshake (8255) Acquisition Timing Diagram

www.ni.com

<sup>&</sup>lt;sup>2</sup> Generation pauses if the DAQmx Underflow property/attribute is set to Pause Until Data Available or Pause Trigger Received.

$t_{\text{DT}}$  = Maximum required delay from data valid to trigger.  $t_{\text{TD}}$  = Maximum required delay from trigger to data invalid.

#### **Events**

| Specification                                       | Value                                                                                                                                                              |                                    |                                                                          |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------|--|

| Supported events (by sample                         | Sample Timing Type                                                                                                                                                 | Acquisition                        | Acquisition                                                              |  |

| timing type)                                        | Sample Clock                                                                                                                                                       | Ready for Start                    | Ready for Start                                                          |  |

|                                                     | Pipelined Sample Clock                                                                                                                                             | Ready for Transfer, Ready for Star | Ready for Transfer, Ready for Start                                      |  |

|                                                     | Burst Handshake                                                                                                                                                    | Ready for Transfer                 | Ready for Transfer                                                       |  |

|                                                     | Handshake                                                                                                                                                          | Handshake                          | Handshake                                                                |  |

|                                                     | Change Detection                                                                                                                                                   | Change Detection, Ready for Start  | Change Detection, Ready for Start                                        |  |

| Destinations                                        | 1. PFI <05> (DDC Connector) 2. PXI_TRIG<07> (PXI backplane—PXI Express only) RTSI <07> (RTSI bus—PCI Express only) 3. PXIe_DSTARC (PXI backplane—PXI Express only) |                                    |                                                                          |  |

| Pulse width for the exported Change Detection event | Frequency ≤ 10 MHz                                                                                                                                                 |                                    | Frequency > 10 MHz*                                                      |  |

|                                                     | 50 ns                                                                                                                                                              |                                    | 15 ns                                                                    |  |

| Delay from Change Detect to event                   | Minimum                                                                                                                                                            |                                    | Maximum                                                                  |  |

|                                                     | 90 ns                                                                                                                                                              |                                    | PCIe: 1 Sample clock cycle + 100 ns  PXIe: 1 Sample clock cycle + 105 ns |  |

### **Nonvolatile Storage**

| Specification | Value                                            | Comments |

|---------------|--------------------------------------------------|----------|

| Description   | 16 Mbit storage for firmware and power up states | _        |

| Write Cycles  | 75,000 minimum                                   | _        |

16

### Power

| Specification | Va      | lue     | Comments                          |

|---------------|---------|---------|-----------------------------------|

|               | Typical | Maximum | All data channels loaded by 5 kΩ. |

| +3.3 VDC      | 700 mA  | 750 mA  |                                   |

| +12 VDC       | 250 mA  | 300 mA  |                                   |

| Total power   | 5.1 W   | 6.1 W   |                                   |

# **Physical Specifications**

| Specification | Value                           |                                  | Comments |

|---------------|---------------------------------|----------------------------------|----------|

| Dimensions    | PXI Express                     | PCI Express                      | _        |

|               | 21.4 cm × 2.0 cm × 13.1 cm      | 18.1 cm × 2.2 cm × 12.6 cm       |          |

|               | (8.42 in. × 0.79 in.× 5.14 in.) | (7.13 in. × 0.85 in. × 4.93 in.) |          |

| Weight        | 144.58 g (5.1 oz)               | 107.7 g (3.8 oz)                 | _        |

### Software

| Specification        | Value                                                                                                                                                                                                                                                                                                                                                       |                                               | Comments |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------|

| Driver software      | NI 6535                                                                                                                                                                                                                                                                                                                                                     | NI 6536/6537                                  | _        |

|                      | NI-DAQmx driver software version 8.8 or later                                                                                                                                                                                                                                                                                                               | NI-DAQmx driver software version 8.5 or later |          |

| Application software | NI-DAQmx provides programming interfaces for the following application development environments:  • National Instruments LabVIEW 7.1.1, 8.2.1, 8.5.1, and 8.6 (LabVIEW 8.6 requires NI-DAQmx 8.8 or later)  • National Instruments LabWindows™/CVI™ 7.x or later  • Microsoft Visual Studio 6.0 or later for ANSI C  • Microsoft Visual Studio 2003 for C++ |                                               |          |

| Test Panel           | National Instruments Measurement and Automation Explorer (MAX) provides test panels with basic acquisition and generation functionality for the NI 6535/6536/6537. MAX is included on the NI-DAQmx instrument driver CD.                                                                                                                                    |                                               | _        |

### **Environment**

Note The NI 6535/6536/6537 is intended for indoor use only.

| Specification               |                                                                                 | Value                                                                                                          |   |

|-----------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---|

| Operating temperature       | PXI Express                                                                     | PCI Express                                                                                                    | _ |

|                             | 0 °C to +55 °C                                                                  | 0 °C to +45 °C                                                                                                 |   |

| Storage temperature         | –20 °C to +70 °C                                                                | -20 °C to +70 °C                                                                                               |   |

| Operating relative humidity | 10% to 90% relative humidity, noncondens                                        | 10% to 90% relative humidity, noncondensing (Meets IEC 60068-2-56)                                             |   |

| Storage relative humidity   | 5% to 95% relative humidity, noncondensi                                        | 5% to 95% relative humidity, noncondensing (Meets IEC 60068-2-56)                                              |   |

| Operating shock             | 30 g, half-sine, 11 ms pulse (Meets IEC 60 accordance with MIL PRF-28800F.)     | 30 g, half-sine, 11 ms pulse (Meets IEC 60068-2-27. Test profile developed in accordance with MIL PRF-28800F.) |   |

| Storage shock               | 50 g, half-sine, 11 ms pulse (Meets IEC 60 accordance with MIL PRF-28800F.)     | 50 g, half-sine, 11 ms pulse (Meets IEC 60068-2-27. Test profile developed in accordance with MIL PRF-28800F.) |   |

| Operating vibration         | 5 Hz to 500 Hz, 0.31 g <sub>rms</sub> (Meets IEC 6000                           | 5 Hz to 500 Hz, 0.31 g <sub>rms</sub> (Meets IEC 60068-2-64.)                                                  |   |

| Storage vibration           | 5 Hz to 500 Hz, 2.46 g <sub>rms</sub> (Meets IEC 6000 MIL PRF-28800F, Class B.) | 5 Hz to 500 Hz, 2.46 g (Meets IEC 60068-2-64. Test profile exceeds requirements of MIL PRF-28800F, Class B.)   |   |

| Altitude                    | 0 m to 2,000 m above sea level (at 25 °C a                                      | 0 m to 2,000 m above sea level (at 25 °C ambient temperature)                                                  |   |

| Pollution Degree            | II                                                                              |                                                                                                                | _ |

# Safety, Electromagnetic Compatibility, and CE Compliance

www.ni.com

| Specification                                                                                   | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Comments                                                   |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Safety                                                                                          | This product is designed to meet the requirements of the following standards of safety for electrical equipment for measurement, control, and laboratory use: • IEC 61010-1, EN 61010-1 • UL 61010-1, CSA 61010-1                                                                                                                                                                                                                                                                            |                                                            |

| Note For UL and other safety certifications, refer to the Online Product Certification section. | e product label or the                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                            |

| Electromagnetic Compatibility                                                                   | This product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:  • EN 61326 (IEC 61326): Class A emissions; Basic immunity  • EN 55011 (CISPR 11): Group 1, Class A emissions  • AS/NZS CISPR 11: Group 1, Class A emissions  • FCC 47 CFR Part 15B: Class A emissions  • ICES-001: Class A emissions  Note For the standards applied to access the EMC of this product, refer to the Online Product Certification | With use of SHC68-C68- D2 or SHC68-C68- D4 shielded cable. |

|                                                                                                 | section.  Note For EMC compliance, device <i>must</i> be operated with shielded cabling. In addition, filler panels must be installed.                                                                                                                                                                                                                                                                                                                                                       |                                                            |

| This product meets the essential requirements of applicable                                     | e European Directives as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                            |

| CE Compliance                                                                                   | 2006/95/EC; Low-Voltage Directive (safety)     2004/108/EC; Electromagnetic Compatibility Directive (EMC)                                                                                                                                                                                                                                                                                                                                                                                    |                                                            |

| Note Note                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                            |

| Refer to the Declaration of Conformity (DoC) for this produc                                    | ct for any additional regulatory compliance information. To ob<br>act line, and click the appropriate link in the Certification colur                                                                                                                                                                                                                                                                                                                                                        |                                                            |

| Environmental Management                                                                        | NI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial not only to the environment but also to NI customers.                                                                                                                                                                                                                                          |                                                            |

|                                                                                                 | For additional environmental information, refer to the NI and the Environment web page at ni.com/environment. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.                                                                                                                                                                                                              |                                                            |

| Waste Electrical and Electronic Equipment (WEEE)                                                | <b>EU Customers:</b> At the end of their life cycle, all products <i>m</i> information about WEEE recycling centers and National Ins                                                                                                                                                                                                                                                                                                                                                         |                                                            |

www.ni.com

# 电子信息产品污染控制管理办法 (中国 RoHS)

中国客户 National Instruments 符合中国电子信息产品中限制使用某些有害物质指令 (RoHS)。 关于 National Instruments 中国 RoHS 合规性信息,请登录 ni.com/environment/rohs\_china。 (For Information about China RoHS compliance, go to ni.com/environment/rohs\_china.)

Back to Top

©2010 National Instruments. All rights reserved. CompactRIO, CVI, FieldPoint, LabVIEW, Measurement Studio, National Instruments, National Instruments Alliance Partner, NI, ni.com, and SignalExpress are trademarks of National Instruments. The mark LabWindows is used under a license from Microsoft Corporation. Windows is a registered trademark of Microsoft Corporation in the United States and other countries. Other product and company names listed are trademarks or trade names of their respective companies. A National Instruments Alliance Partner is a business entity independent from National Instruments and has no agency, partnership, or joint-venture relationship with National Instruments.

## Artisan Technology Group is an independent supplier of quality pre-owned equipment

### **Gold-standard solutions**

Extend the life of your critical industrial, commercial, and military systems with our superior service and support.

### We buy equipment

Planning to upgrade your current equipment? Have surplus equipment taking up shelf space? We'll give it a new home.

#### Learn more!

Visit us at artisantg.com for more info on price quotes, drivers, technical specifications, manuals, and documentation.

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

We're here to make your life easier. How can we help you today? (217) 352-9330 | sales@artisantg.com | artisantg.com