Artest Technology Dro.

#### In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/72377-1

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

ARTISAN'

TECHNOLOGY GROUP

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales aartisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

#### **OPERATING MANUAL**

# **MODEL 6236**

Two-Channel Digital Receiver VIM-2 Module for Pentek VIM Baseboards

Pentek, Inc.

One Park Way

Upper Saddle River, NJ 07458

(201) 818–5900

http://www.pentek.com

Copyright © 2006 – 2008

Manual Part No: 800.62360 Rev: A.2 – December 1, 2008

#### **Manual Revision History**

| <u>Date</u> | Manual Rev  | <u>Comments</u>                                                                                                                                                        |

|-------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9/22/03     | Preliminary | Preliminary manual initial release                                                                                                                                     |

| 10/19/04    | Preliminary | Removed references to baseboard 'C6x processors. Updated AD6645 data sheet and board specifications. Added timing signal relationships diagram, Sect 5.5, per Kbcase . |

| 8/9/05      | A           | Release of manual, Rev A.                                                                                                                                              |

| 10/3/06     | A.1         | Updated power specifications, Sect 1.12, per KBCase 1312. Updated ERNI connector part numbers, Sect 2.4.3 & 2.4.5, per KBCase 1308.                                    |

| 12/1/08     | A.2         | Corrected GC1012B input to 12 most significant bits of 14–bit A/D output, Sect 1.4, 1.10, 1.12, & 4.2.                                                                 |

#### **Warranty**

Pentek warrants that all products manufactured by Pentek conform to published Pentek specifications and are free from defects in materials and workmanship for a period of one year from the date of delivery when used under normal operating conditions and within the service conditions for which they were furnished.

The obligation of Pentek arising from a warranty claim shall be limited to repairing or at its option, replacing without charge, any product which in Pentek's sole opinion proves to be defective within the scope of the warranty. Pentek must be notified in writing of the defect or nonconformity within the warranty period and the affected product returned to Pentek within thirty days after discovery of such defect or nonconformity.

Buyer shall prepay shipping charges, taxes, duties and insurance for products returned to Pentek for warranty service. Pentek shall pay for the return of products to buyer except for products returned from another country.

Pentek shall have no responsibility for any defect or damage caused by improper installation, unauthorized modification, misuse, neglect, inadequate maintenance, or accident, or for any product which has been repaired or altered by anyone other than Pentek or its authorized representatives.

The warranty described above is buyer's sole and exclusive remedy and no other warranty, whether written or oral, is expressed or implied. Pentek specifically disclaims fitness for a particular purpose. Under no circumstances shall Pentek be liable for any direct, indirect, special, incidental, or consequential damages, expenses, losses or delays (including loss of profits) based on contract, tort, or any other legal theory.

#### **Copyrights**

With the exception of those items listed below, the contents of this publication are copyright © 2006 – 2008, Pentek, Inc. All Rights Reserved. Contents of this publication may not be reproduced in any form without written permission.

Appendix C, AD6645 Datasheet, is the copyrighted property of Analog Devices, Inc., Norwood MA Appendix D, Graychip 1012B Datasheet, is the copyrighted property of Graychip, Inc., Palo Alto, CA Appendix E, ADM1024 Datasheet, is the copyrighted property of Analog Devices, Inc., Norwood MA

#### **Trademarks**

Pentek, GateFlow, ReadyFlow, and VIM are registered trademarks or trademarks of Pentek, Inc. Xilinx, MultiLINX, and Virtex are registered trademarks or trademarks of Xilinx, Inc.

Page Chapter 1: Introduction 1.1 General Description......9 1.2 Features ......9 1.3 1.4 Digital Receivers (Option 212)......10 1.5 1.6 1.7 Timing and Synchronization......11 1.8 1.9 1.10 Figure 1–1: Model 6236 Block Diagram......12 1.11 Figure 1-2: Model 6236 FPGA Interconnectivity......14 1.12

|     |          |                                                                                                                | Page |

|-----|----------|----------------------------------------------------------------------------------------------------------------|------|

|     |          | Chapter 2: Installation and Connections                                                                        |      |

| 2.1 | Inspect  | tion                                                                                                           | 17   |

| 2.2 | Jumpe    | r Settings                                                                                                     | 17   |

|     | Table 2  | 2–1: FPGA Configuration Data Source Jumper                                                                     | 17   |

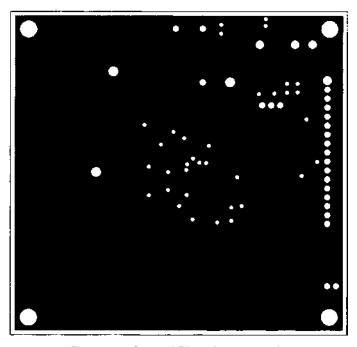

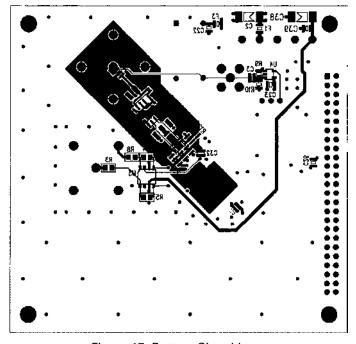

|     | Figure   | 2-1: Model 6236 PCB Assembly, Component Side                                                                   | 18   |

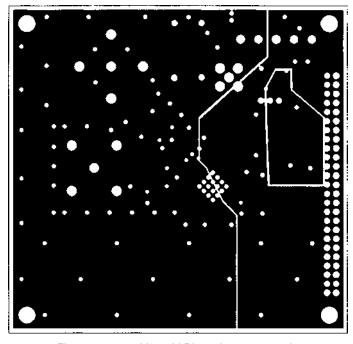

|     |          | 2-2: Model 6236 Option 102 PCB Assembly, Component Side                                                        |      |

| 2.3 | Installi | ng the Model 6236 on a VIM Baseboard                                                                           | 19   |

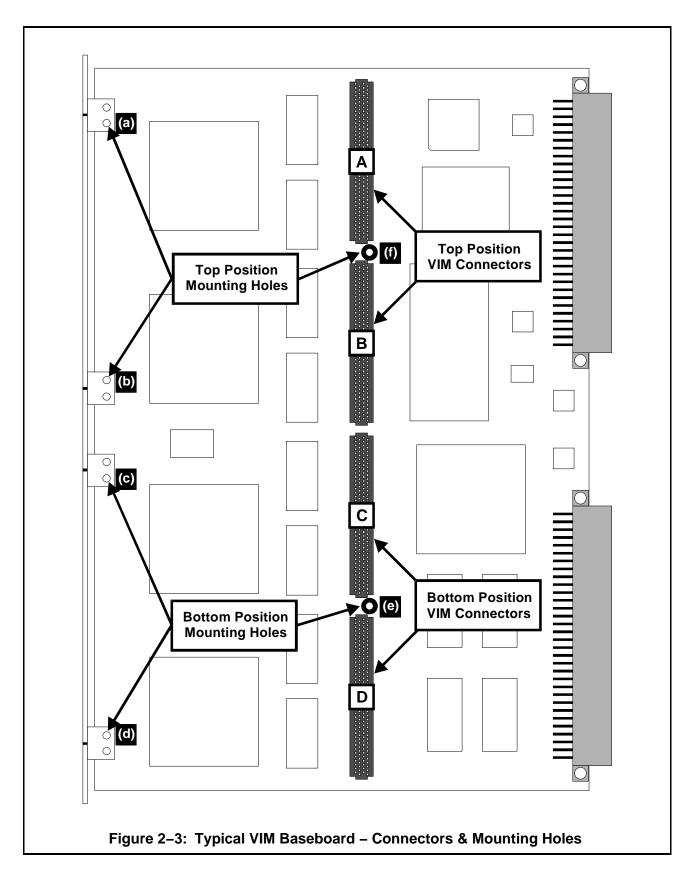

|     | Figure   | 2-3: Typical VIM Baseboard - Connectors & Mounting Holes                                                       | 20   |

|     | 2.3.1    | Installing Model 6236 without Option 102                                                                       |      |

|     |          | Figure 2–4: Model 6236 Panel Mounting and Shipping Screws                                                      | 21   |

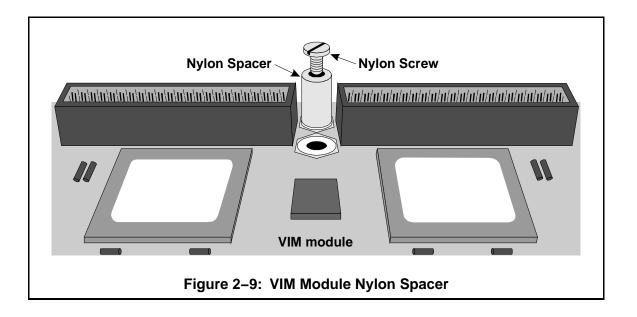

|     |          | Figure 2-5: VIM Module Nylon Spacer                                                                            |      |

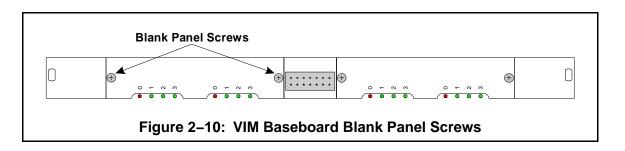

|     |          | Figure 2–6: VIM Baseboard Blank Panel Screws                                                                   |      |

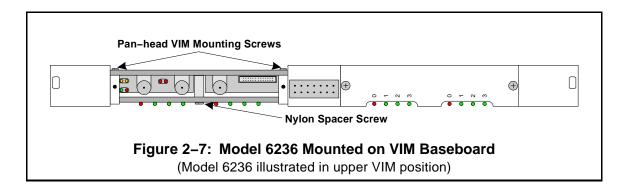

|     |          | Figure 2–7: Model 6236 Mounted on VIM Baseboard                                                                | 23   |

|     | 2.3.2    | Installing Model 6236 with Option 102                                                                          |      |

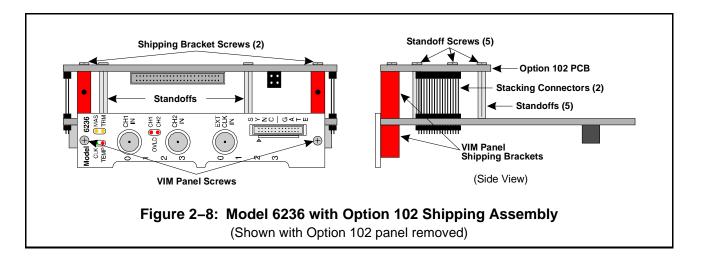

|     |          | Figure 2–8: Model 6236 with Option 102 Shipping Assembly                                                       |      |

|     |          | Figure 2–9: VIM Module Nylon Spacer                                                                            | 25   |

|     |          | Figure 2–10: VIM Baseboard Blank Panel Screws                                                                  |      |

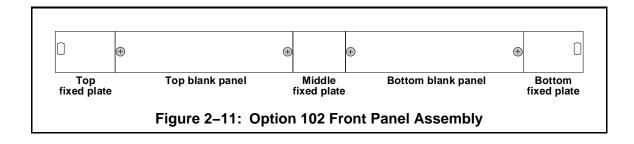

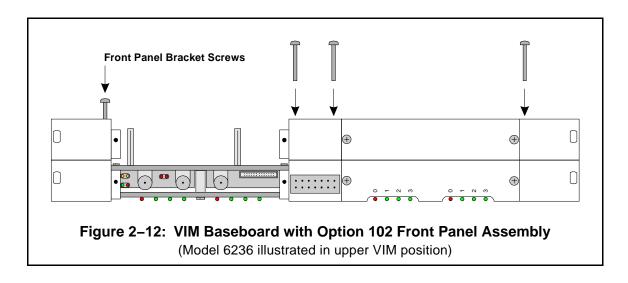

|     |          | Figure 2–11: Option 102 Front Panel Assembly                                                                   |      |

|     |          | Figure 2-12: VIM Baseboard with Option 102 Front Panel Assembly                                                |      |

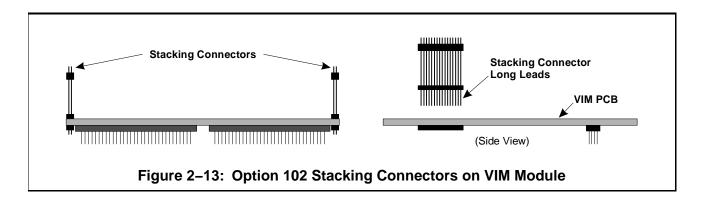

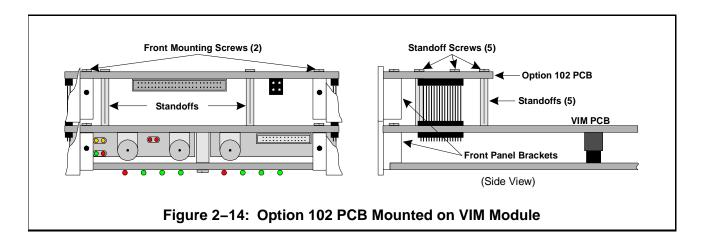

|     |          | Figure 2–13: Option 102 Stacking Connectors on VIM Module<br>Figure 2–14: Option 102 PCB Mounted on VIM Module |      |

| 2.4 | Front I  | Panel Connections                                                                                              |      |

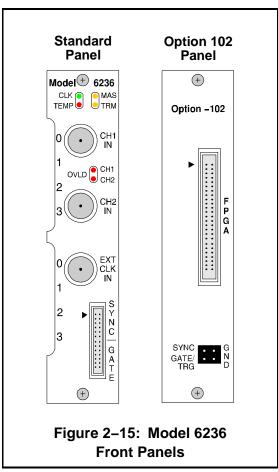

| 2.1 |          | 2–15: Model 6236 Front Panels                                                                                  |      |

|     | 2.4.1    | Analog Input Connectors                                                                                        |      |

|     | 2.4.2    | External Clock Input Connector                                                                                 |      |

|     | 2.4.3    | Sync/Gate Connector                                                                                            |      |

|     | 2.4.3    | Table 2–2: SYNC/GATE Connector Pins                                                                            |      |

|     | 2.4.4    | Sync/Gate Header (Option 102 only)                                                                             |      |

|     | 2.7.7    | Table 2–3: SYNC/GATE/TRG Header Pins                                                                           |      |

|     | 2.4.5    | FPGA Connector (Option 102 only)                                                                               |      |

|     | 2.1.0    | Table 2–4: FPGA Connector Pins                                                                                 |      |

| 2.5 | Front I  | Panel LEDs                                                                                                     |      |

| 2.0 | 2.5.1    | Clock LED                                                                                                      |      |

|     | 2.5.2    | Over Temperature LED                                                                                           |      |

|     | 2.5.3    | Master LED                                                                                                     |      |

|     | 2.5.4    | Terminate LED                                                                                                  |      |

|     | 2.5.5    | Overload LEDs                                                                                                  |      |

Page Chapter 3: Memory Maps and Register Descriptions 3.1 Model 6236 Memory Map .......33 3.2 Table 3-1: VIM Base Addresses for Models 4290 to 4295 VIM Baseboards .......33 Table 3-2: VIM Base Addresses for Model 4205 VIM Baseboards .......33 Table 3–3: Model 6236 Memory Map ......34 3.3 Table 3-4: Virtex Config Register .......35 3.3.1 WRITE ......35 3.3.2 3.3.3 PRGM ......36 3.3.4 3.3.5 3.4 3.5 Wait State Register......37 3.5.1 3.5.2 CTL REG Wn .......37 3.6 3.7 Master Control Register 39 3.7.1 3.7.2 3.7.3 3.7.4 EXT SYNC ......40 3.7.5 CLK SRC .......40 3.7.6 3.7.7 3.7.8 TERM .......40 MASTR .......41 3.7.9 Bypass Rate Divide Register ......41 3.8 Table 3-10: Bypass Rate Divide Register ......41 3.9 Table 3–11: Sync Mask Register ......42

|      |                                                                | Page                  |

|------|----------------------------------------------------------------|-----------------------|

|      | Chapter 3: Memory Maps and Register Description                | <b>1s</b> (continued) |

| 3.10 | Gate Control Register                                          | 43                    |

|      | Table 3–12: Gate Control Register                              |                       |

|      | 3.10.1 INT EDGE x                                              |                       |

|      | 3.10.2 GATE POL                                                | 44                    |

|      | 3.10.3 GATE SELn                                               | 44                    |

|      | 3.10.4 GATE DISBL                                              | 44                    |

|      | 3.10.5 GATE SRC                                                | 44                    |

|      | 3.10.6 TRIG CLEAR                                              | 44                    |

|      | 3.10.7 HOLD MODE                                               | 45                    |

|      | 3.10.8 GATE/TRIG                                               | 45                    |

|      | 3.10.9 EXT GATE                                                | 45                    |

| 3.11 | Trigger Length Register                                        | 46                    |

|      | Table 3–13: Trigger Length Register                            |                       |

| 3.12 | Channel Control Register                                       |                       |

|      | Table 3–14: Channel Control Register                           |                       |

|      | 3.12.1 RESET                                                   |                       |

|      | 3.12.2 DIV RST EN                                              |                       |

|      | 3.12.3 DAT MODEn                                               |                       |

| 3.13 | Sync/Gate Generator Register                                   |                       |

|      | Table 3–15: Sync/Gate Generator Register                       |                       |

|      | 3.13.1 FIFO GATE                                               |                       |

|      | 3.13.2 SYNC                                                    |                       |

| 3.14 | Interrupt Mask Register                                        |                       |

|      | Table 3–16: Interrupt Mask Register                            |                       |

| 3.15 | Table 3–17: Interrupt Register Bits                            | 51                    |

| 3.13 | Interrupt Flag Register                                        |                       |

| 3.16 | Table 3–18: Interrupt Flag Register  Interrupt Status Register |                       |

| 5.10 | Table 3–19: Interrupt Status Register                          |                       |

| 3.17 | Semaphore Register                                             |                       |

| 0.17 | Table 3–20: Semaphore Register                                 |                       |

| 3.18 | I/O Direction Register (Option 102 only)                       |                       |

| 0.10 | Table 3–21: I/O Direction Register                             |                       |

| 3.19 | I/O Enable Register (Option 102 only)                          | 56                    |

|      | Table 3–22: I/O Enable Register                                | 56                    |

| 3.20 | I/O Data Register (Option 102 only)                            |                       |

|      | Table 3–23: I/O Data Register                                  |                       |

| 3.21 | Graychip Registers (Option 212 only)                           |                       |

|      | Table 3-24: Graychip Registers                                 |                       |

|     |        |                                                                 | Page |

|-----|--------|-----------------------------------------------------------------|------|

|     |        | Chapter 4: Data Formatting and Routing                          |      |

| 4.1 | Overvi | ew                                                              | 59   |

| 4.2 |        | outing and Formats                                              |      |

|     | 4.2.1  | DDR Bypass Mode, Unpacked (001)                                 |      |

|     |        | Table 4-1: Output Data Format - DDR Bypass Mode, Unpacked       |      |

|     | 4.2.2  | DDR Bypass Mode, Time Packed (010)                              |      |

|     |        | Table 4-2: Output Data Format - DDR Bypass Mode, Time Packed    | 60   |

|     | 4.2.3  | DDR Bypass Mode, Channel Packed (011)                           | 61   |

|     |        | Table 4–3: Output Data Format – DDR Bypass Mode, Channel Packed |      |

|     | 4.2.4  | DDR Mode, Unpacked I/Q (100 or 101)                             |      |

|     |        | Table 4-4: Output Data Format - DDR Mode, Unpacked I/Q          |      |

|     | 4.2.5  | DDR Mode, Packed I/Q (110)                                      |      |

|     |        | Table 4–5: Output Data Format – DDR Mode, Packed I/Q            | 62   |

|     |        | Chapter 5: Timing and Synchronization                           |      |

| 5.1 | Overvi | ew                                                              | 63   |

| 5.2 | Gates. |                                                                 | 63   |

| 5.3 | Sync   |                                                                 | 63   |

| 5.4 | Clock. |                                                                 | 64   |

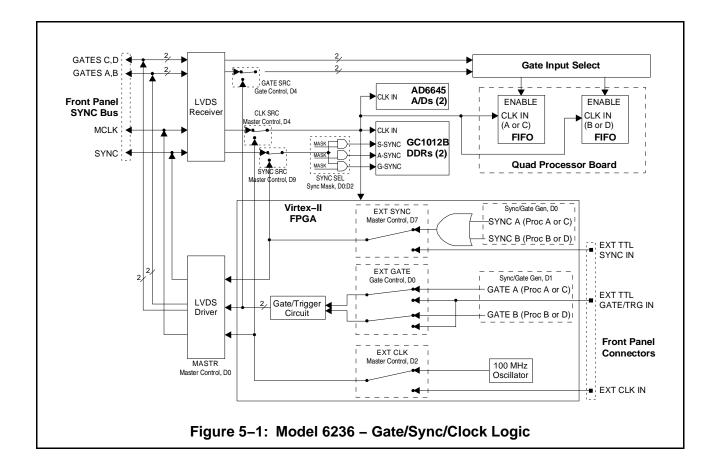

|     | Figure | 5-1: Model 6236 - Gate/Sync/Clock Logic                         | 64   |

| 5.5 | _      | ; Diagram                                                       |      |

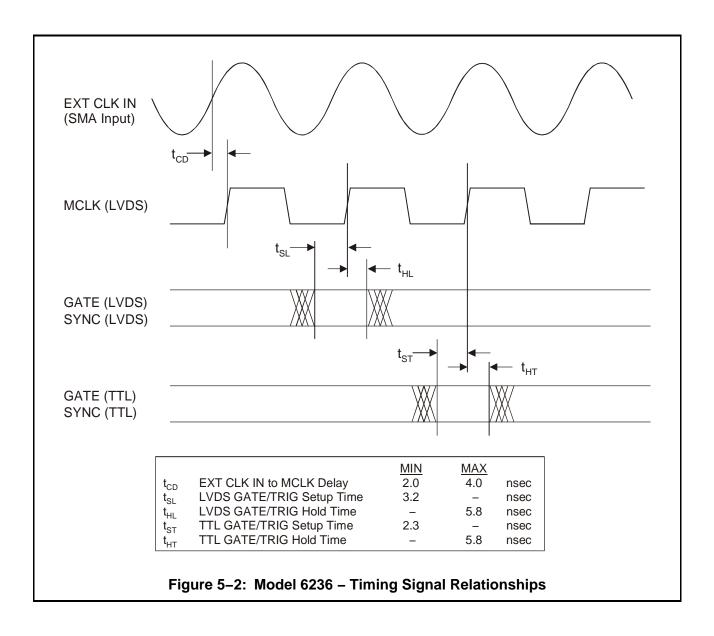

|     | Figure | 5-2: Model 6236 - Timing Signal Relationships                   | 65   |

|     |                                                            | Page |

|-----|------------------------------------------------------------|------|

|     | Appendix A: Configuration EEPROM Format                    |      |

| A.1 | Introduction                                               | A-1  |

| A.2 | EEPROM Format Example                                      |      |

|     | Table A-1: VIM ID EEPROM Register                          |      |

|     | Table A-2: EEPROM Example (Model 6236 shown)               |      |

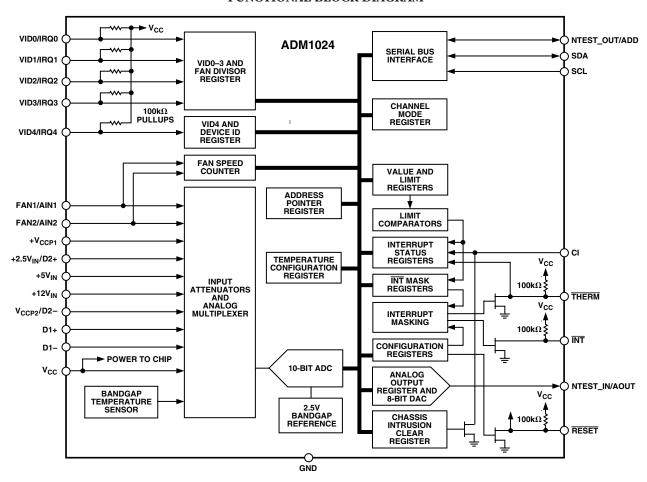

|     | Appendix B: Analog Devices ADM1024 System Hardware Monitor |      |

| B.1 | Introduction                                               | B-1  |

|     | Appendix C: Analog Devices AD6645 A/D Converter            |      |

| C.1 | Introduction                                               | C-1  |

|     | Appendix D: Graychip GC1012 Digital Receiver               |      |

| D 1 | Introduction                                               | D_1  |

# Chapter 1: Introduction

## 1.1 General Description

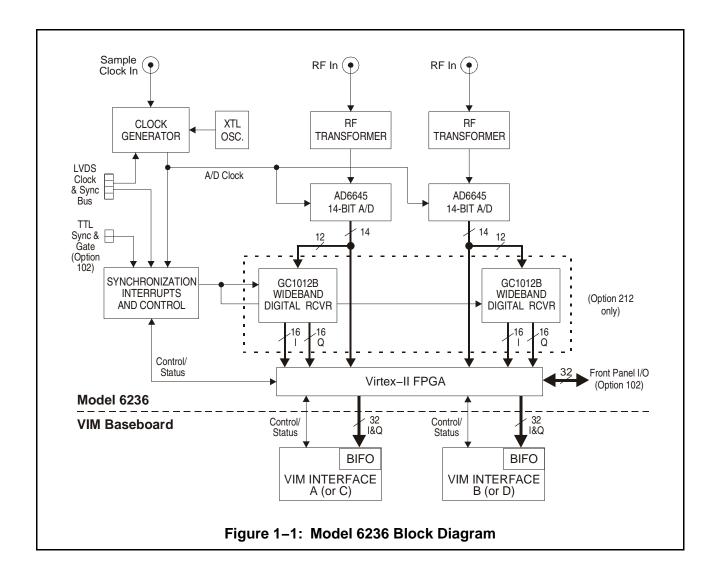

The Model 6236 is a general purpose, wideband digital receiver VIM<sup>®</sup> (Velocity Interface Mezzanine) module. This receiver features two on–board 14–bit, 105–MHz A/D converters, and has two wideband receivers to perform frequency down conversion, low–pass filtering, and decimation of the digitized input signal.

The Model 6236 VIM–2 module attaches directly to VIM–compatible baseboards, including the Pentek Models 4205, and 4290 through 4295 Quad DSP (Digital Signal Processing) boards.

#### 1.2 Features

| Two 105–MHz, 14–bit A/D converters                                              |

|---------------------------------------------------------------------------------|

| Two optional wideband digital receivers                                         |

| 300 kHz to 150 MHz input range                                                  |

| 1.25 MHz to 40 MHz output bandwidth                                             |

| Internal or external A/D sample clock to 105 MHz                                |

| Front panel timing and sync bus can synchronize multiple modules                |

| Advanced Xilinx <sup>®</sup> Virtex <sup>®</sup> –II FPGA for signal processing |

| Direct connection to two VIM baseboard BIFOs, with no shared bus bottlenecks    |

| Compliant with VIM-2 module specification                                       |

When the Model 6236 is mounted on a standard Model 4290 baseboard, data collection at the maximum sample clock rate (105 MHz) is not recommended. However, on a Model 4290 baseboard with Option 320 or 330, the 6236 will operate at the maximum sample clock rate.

## 1.3 Analog/Digital Conversion

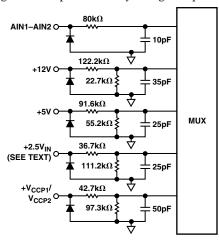

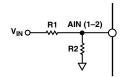

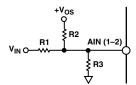

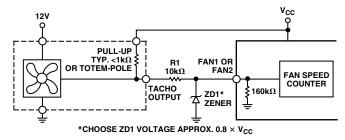

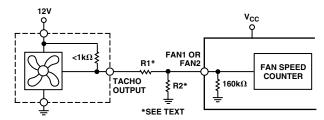

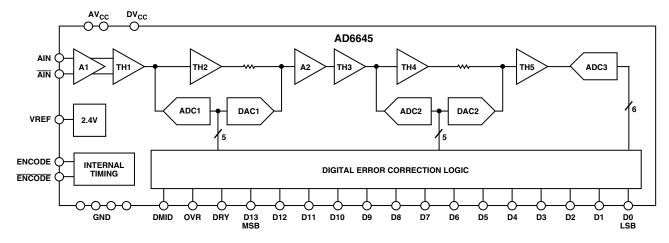

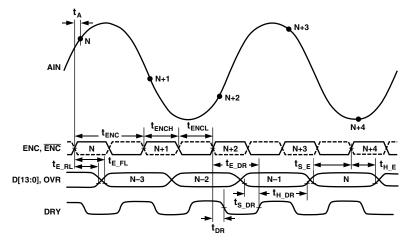

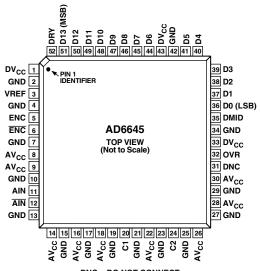

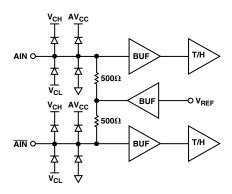

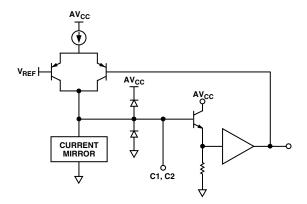

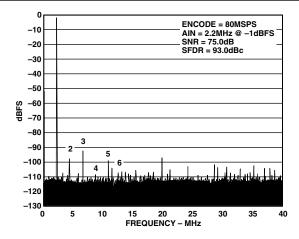

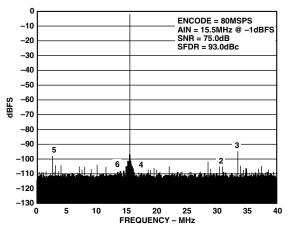

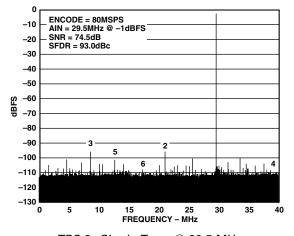

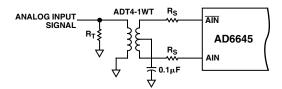

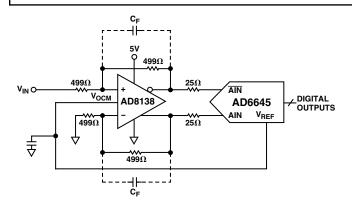

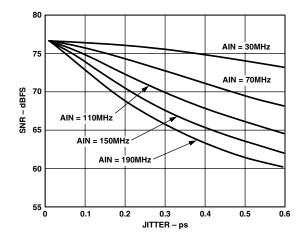

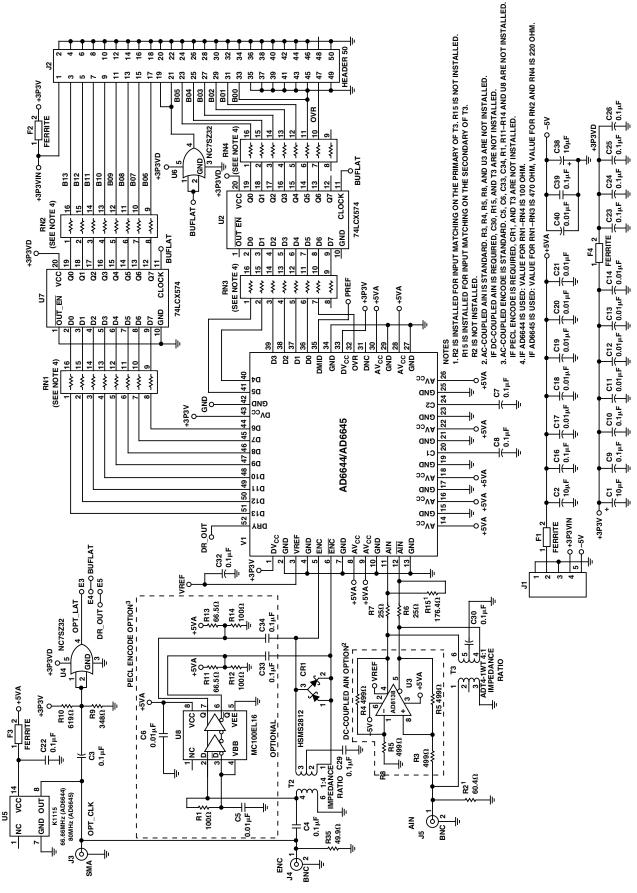

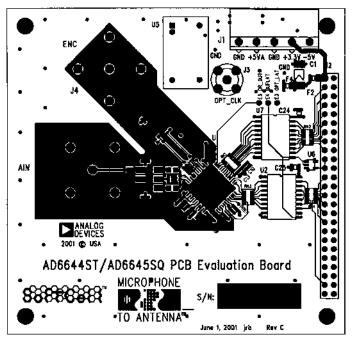

The Model 6236 accepts two analog RF inputs on front panel SMA connectors in the range of 300 kHz to 150 MHz. Each of the two inputs is transformer coupled, and then digitized by an AD6645 14–bit, 105–MHz A/D converter. The A/D converter clock can be driven from an internal 100–MHz crystal oscillator, from an external sample clock supplied through a front panel SMA connector, or from the front panel sync bus.

## 1.4 Digital Receivers (Option 212)

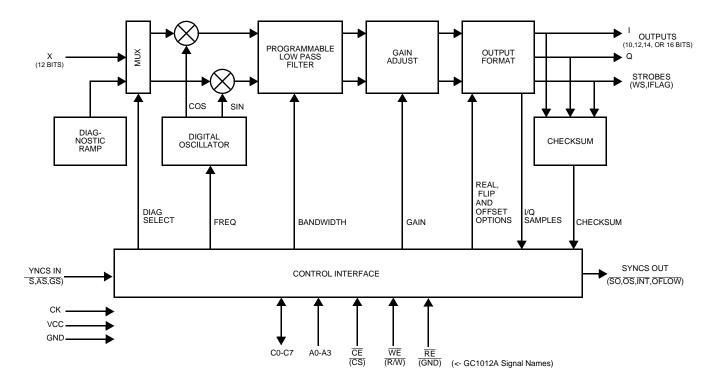

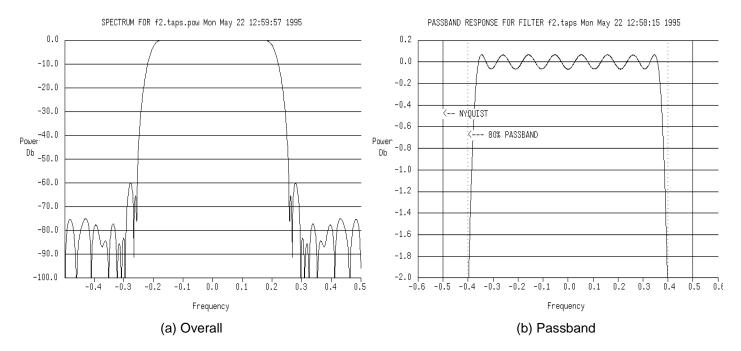

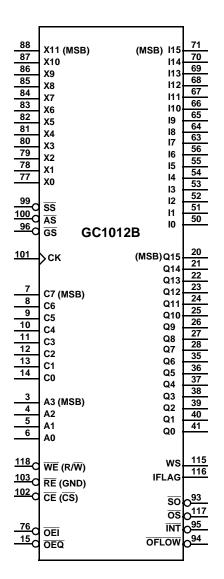

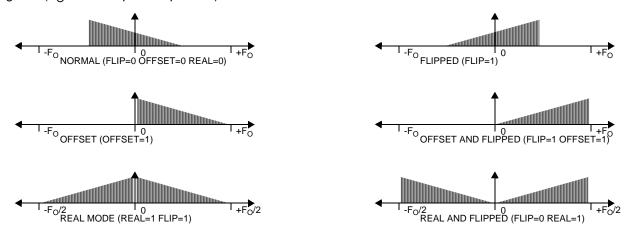

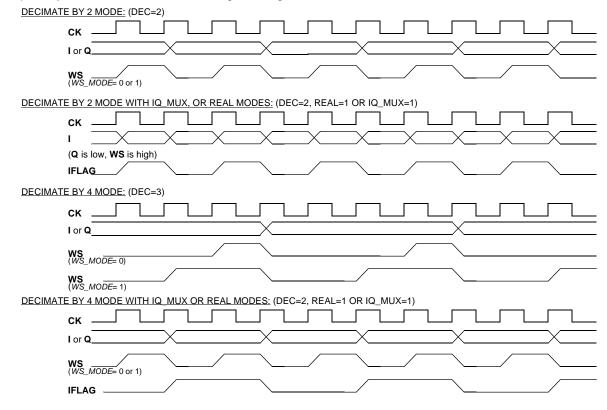

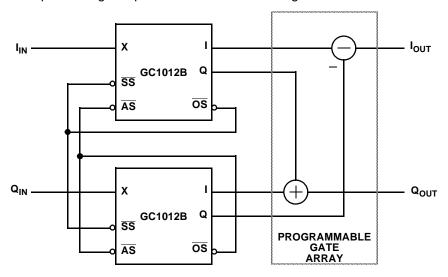

Model 6236 Option 212 adds two Graychip GC1012B wideband digital receiver (DDR) chips. Each GC1012B accepts the 12 most significant bits of each digitized sample from its associated A/D converter. For an input sampling clock of 100 MHz, each receiver is capable of tuning throughout the DC to 50 MHz range, with output bandwidths ranging from 1.25 MHz to 40 MHz. Each optional DDR may be bypassed.

## 1.5 Digital Interfaces

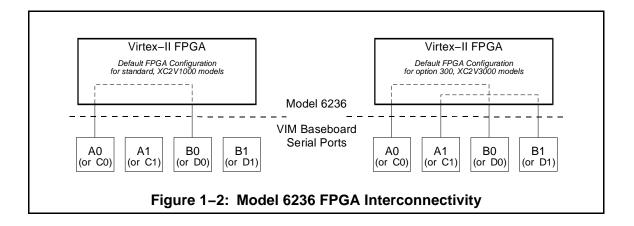

The AD6645 digital outputs are connected directly to an FPGA (field programmable gate array), where data is formatted for delivery across the VIM interface to the 32–bit Bi–FIFOs on the VIM baseboard. With Option 212, each GC1012B delivers real or complex 16–bit parallel data streams to the FPGA.

The Model 6236 contains one Xilinx Virtex–II XC2V1000 FPGA. (The Xilinx Model XC2V3000 is optionally available.) The FPGA is factory programmed to implement the standard data formatting, clocking, and control functions specified in this document.

The FPGA can be re–programmed from a processor on the VIM baseboard. Pentek has an available GateFlow<sup>™</sup> FPGA Design Kit that provides resources for the user to modify the programmable logic functions for the Virtex–II FPGA. This allows the user to implement his own algorithms for special timing requirements and for pre–processing of AD6645 or GC1012B output data before sending it to the baseboard VIM BIFOs. Pentek offers this capability as a separate development package, Model 4953 – Option 236. Contact Pentek at (201) 818–5900 for details about this package.

Refer to Section 1.11, FPGA Configuration, for additional information about the gate array configurations.

#### 1.6 VIM Interface

The FPGA outputs are connected directly through the VIM interface to the 32-bit synchronous Bi-FIFOs on the VIM baseboard, where data is buffered for efficient block transfers to the processors. Baseboard processors can control all programmable registers on the optional GC1012B's as well as control and initiate sync bus functions.

## 1.7 Timing and Synchronization

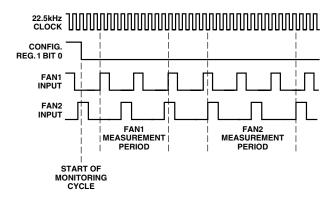

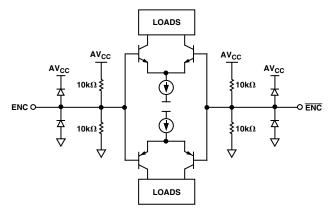

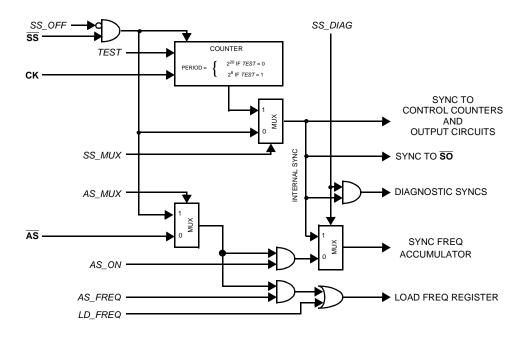

The front panel LVDS (low–voltage differential signal) Sync Bus includes sample clock, sync, and gate signals. It allows one Model 6236 to act as a bus master, driving the sample clock out to a front panel flat cable using LVDS differential signaling. The sync line on the bus allows synchronization of the local oscillator phase, frequency switch–ing, decimating filter phase, and BIFO data collection on multiple 6236s. Up to seven slave 6236s can then be driven from the master, supporting synchronous sampling and sync functions across all connected modules. The sync source is connected to the LVDS bus through the FPGA, so that it can be routed to the GC1012B's S–sync (system sync), A–sync (accumulator sync), and G–sync (gain sync) lines under software control. Gates are used to enable writes to the VIM baseboard BIFOs.

A VIM baseboard processor can access all control and status registers to control synchronization, gating, triggering, and clocking modes. Baseboard processors can generate sync, gate, and trigger signals for distribution across the LVDS Sync Bus.

In addition to the LVDS Sync Bus signals, the Model 6236 accepts an external sample clock supplied through a front panel SMA connector, and two optional TTL input timing signals, one for external sync and the other external gating or triggering.

Refer to Chapter 5, Timing and Synchronization, for additional information about the use and programming of gate and sync signals.

## 1.8 Interrupts

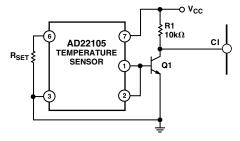

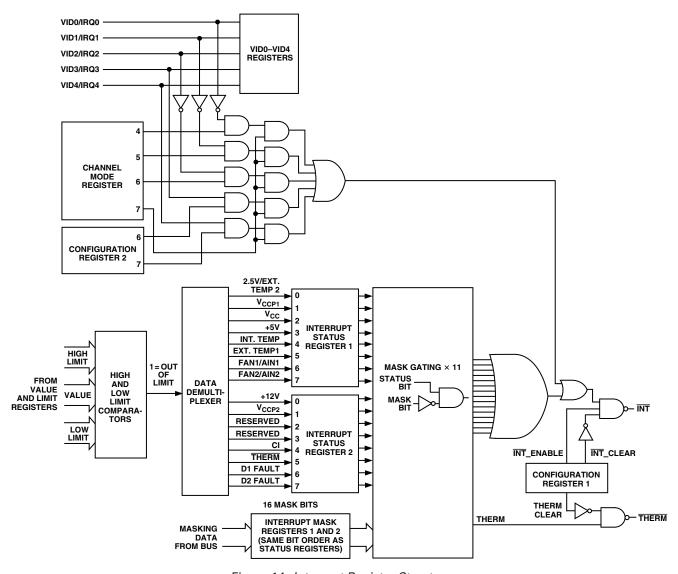

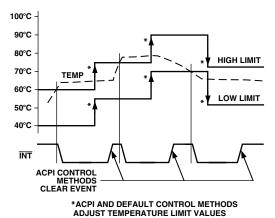

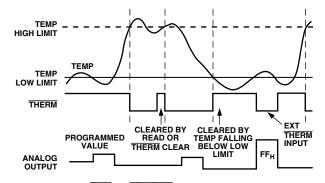

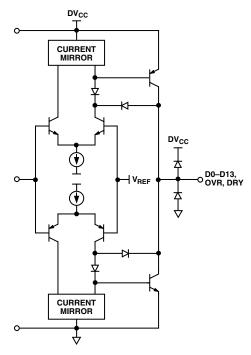

The Model 6236 has several maskable interrupt sources. Interrupts may be generated by the A/D converter overload outputs, DDR overflow, transitions on the gate or sync signals, clock loss, or a programmable over–temperature on one of three sensors or a faulty power supply voltage.

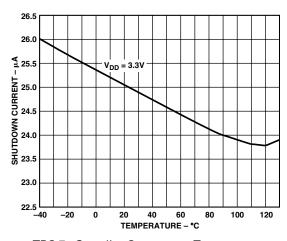

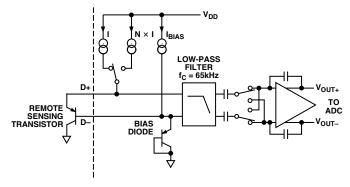

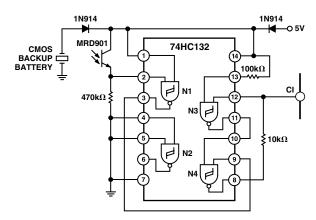

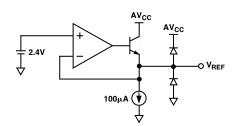

The board's programmable Voltage/Temperature Monitor, an ADM1024, provides constant monitoring of critical voltages and temperatures on the PCB. If the voltage or temperature fall outside of the set limits, an interrupt can be generated.

# 1.9 Board Support Software

Pentek's ReadyFlow<sup>®</sup> Board Support Libraries allow high–level programming to speed development tasks. Refer to the ReadyFlow board support software documentation for the Model 6236 (Pentek part #801.62360) for further description of these capabilities.

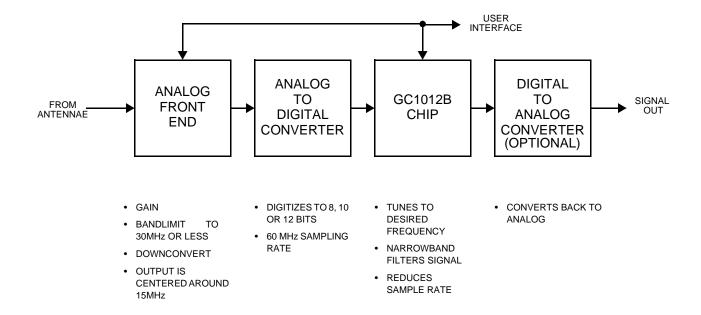

#### 1.10 Block Diagram

The following is a simplified block diagram of the Model 6236 digital receiver, connected to a VIM baseboard.

There are two processor channels on the Model 6236, one for each baseboard VIM interface. These are identified as **A** and **B** if your VIM module is installed on the upper VIM position of the baseboard, or **C** and **D** if your VIM module is installed on the lower VIM position of the baseboard. Each processor channel is associated with (and controls) one RF analog input and one VIM baseboard BIFO (plus one GC1012B with Option 212).

#### 1.11 FPGA Configuration

The standard FPGA on the Model 6236 is the Xilinx Virtex–II XC2V1000; the Xilinx Virtex–II XC2V3000 is available as Option 300. The baseline functionality of the Model 6236 consumes approximately 18% of the XC2V1000 or 6% of the XC2V3000.

The Model 6236 is shipped with a default set of logic functions for this FPGA, on a JTAG-programmable serial EEPROM. Upon power-up, this set of default functions is loaded into the FPGA. The FPGA can be configured in several different ways:

- The default method is serial configuration load from the configuration EEPROM. This is the power up mode of the board. Configuration reload may also be forced at any time by a baseboard processor (see Section 3.3).

- The second method, to facilitate development and debugging, is by serial download to the FPGA using a Xilinx Parallel III or MultiLINX<sup>TM</sup> cable. This method will replace the factory–programmed configuration that loads at power up from the EEPROM, but is volatile and will exist only until the power is turned off.

- The third method is JTAG programming the FPGA using a Xilinx Parallel III or MultiLINX<sup>™</sup> cable. This method will replace the factory–programmed configuration that loads at power up from the EEPROM, but does not overwrite the EEPROM. This method is volatile and will exist only until the power is turned off.

- The fourth method is byte—wide upload to the FPGA from a baseboard processor. This is done by the processor writing the configuration data to the FPGA configuration data register (see Section 3.4). For the XC2V1000, about 468 kBytes of FLASH memory on the baseboard is required to hold the FPGA configuration; for the XC2V3000, about 1.2 MBytes is required. This method is also volatile; that is, the new configuration will exist only until the power is turned off.

- The last method is to reconfigure the EEPROM via the JTAG interface with a Xilinx cable, then power—up the board with the new configuration. This overwrites the default configuration by reprogramming the EEPROM. After turning power off, the FPGA will power up with this new configuration instead of the default configuration the Model 6236 was shipped with.

**NOTE:** This method will permanently overwrite the default configuration supplied by Pentek. The default configuration is supplied with the available FPGA Design Kit so that it can be restored if necessary.

Pentek has an available GateFlow<sup>™</sup> FPGA Design Kit for the Model 6236 that provides resources for the user to modify the programmable logic functions for the Virtex–II FPGA. This allows the user to implement his own algorithms for special timing requirements and for pre–processing of AD6645 or GC1012B output data. Pentek offers this capability as a separate development package, Model 4953 – Option 236. Contact Pentek at (201) 818–5900 for details about this package.

## **1.11 FPGA Configuration** (continued)

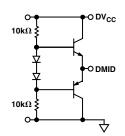

When the Model 6236 is attached to a Pentek VIM baseboard, the standard XC2V1000 FPGA, or the optional XC2V3000 FPGA, provides serial port connectivity as shown in the following illustration.

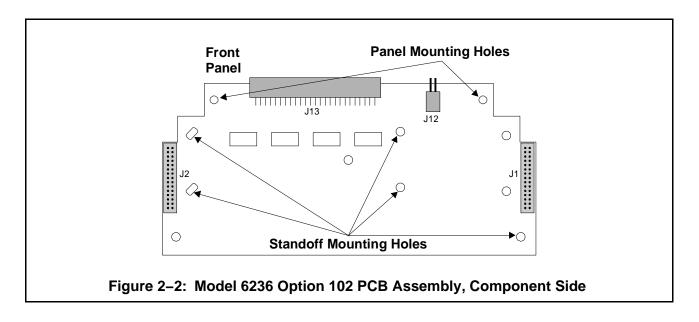

Option 102 for the Model 6236 provides an FPGA I/O connector on an additional front panel located in the adjacent VMEbus slot (see Section 2.4). The FPGA I/O pins are split into two groups of 16 pins each, with one group going to each of the two baseboard VIM interfaces. The user can configure these FPGA I/O pins as either inputs or outputs (see Section 3.18), on either the XC2V1000 or the XC2V3000 models. The quickswitches and 25–ohm series resistors provide some over–voltage and short protection to the FPGA I/O pins.

For convenience, Option 102 also provides a 4–pin header connection, on the additional front panel, for TTL Sync/Gate inputs.

#### 1.12 Specifications

**Front Panel Connectors**

**Analog Inputs:** Two female SMA connectors (one per A/D converter)

Sample Clock Input: One female SMA connector

**Sync/Gate Bus:** One 26–pin connector, with four gates, one sync, and one

clock input/output LVDS signals, plus one sync and

one gate input TTL signals

**Option 102 Panel Connectors:**

TTL Sync/Gate: One 4-pin header, with one sync and one gate TTL inputs

**FPGA Inputs/Outputs:** One 50–pin connector

FPGA Input/Output: 32 pins (16 pins for each baseboard VIM interface)

Max. Load per I/O pin: 20 mA (These pins are connected through IDT Quick

Switch P/N QS32245)

**Analog Signal Inputs**

**Quantity:** Two, via front panel SMA connectors

**Input Type:** Single–ended, non–inverting

**Coupling:** AC **Input Impedance:**  $50\Omega$

Full Scale Input: +4 dBm, absolute maximum +15 dBm

**Input Bandwidth:** 300 kHz to 150 MHz

**Analog Input Transformers**

**Quantity:** Two (enclosed in a shielded cover)

**Type:** ADT4–5WT (Mini–Circuits)

3 dB Passband: 300 kHz to 500 MHz

**Input Return Loss:** 8.72 dB min., 31.13 dB max.

Bypass: None

Analog/Digital Converters

**Quantity:** Two (enclosed in a shielded cover)

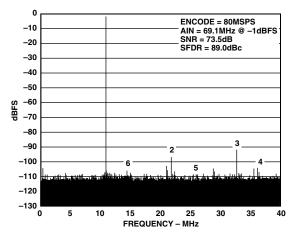

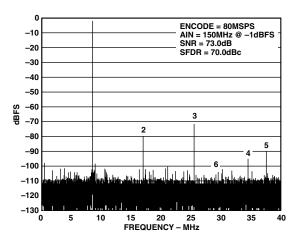

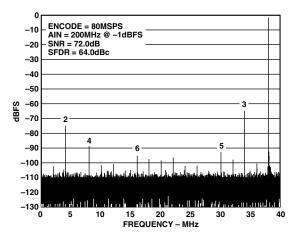

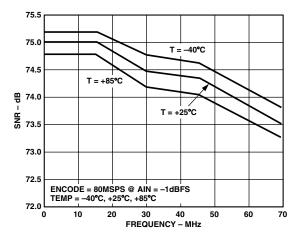

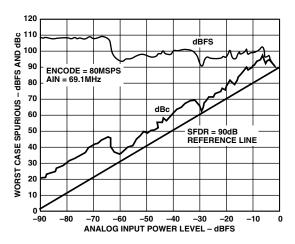

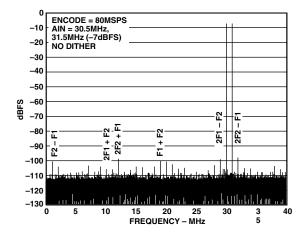

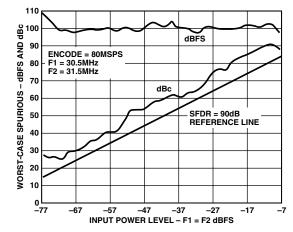

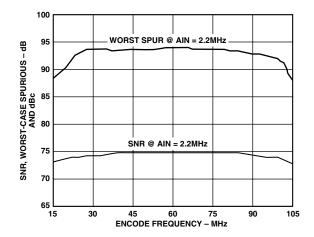

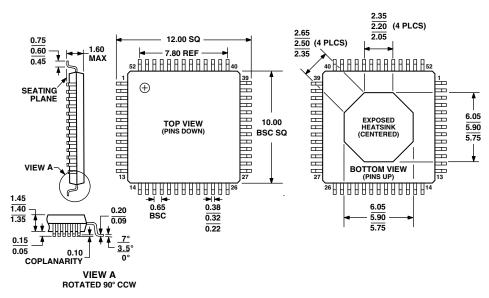

**Device:** Analog Devices AD6645 (see Appendix C)

Sampling Rate: 30 MHz to 105 MHz

**Resolution:** 14 bits

**Coupling:** Transformer coupled

Clock Source: Onboard crystal oscillator, external clock, or LVDS clock

Internal Clock

**Frequency:** 100–MHz crystal oscillator, better than 100 ppm accuracy

**External Clock Input**

**Type:** Sine Wave **Voltage Range:** 0 to 10 dBm

Frequency: 30 MHz to 105 MHz Impedance:  $50\Omega$ , AC coupled

#### **1.12 Specifications** (continued)

<u>Gates</u>

Quantity: Two, one per VIM baseboard BIFO; each baseboard VIM

interface can create its own gate

**Gate Sources:** Front panel LVDS Sync Bus (four) gate inputs, TTL Gate/

Trigger input, or (two) programmable registers

**Polarity:** External gate input has programmable polarity

Gate Disable: Each gate can be disabled by a baseboard processor; when

disabled, VIM BIFO writes default to enabled

**Triggering:** Each gate can be programmed as a trigger, programmable

trigger length up to 16,383 VIM BIFO writes

<u>Digital Receivers</u> (Option 212 only)

Quantity: Two receiver chips

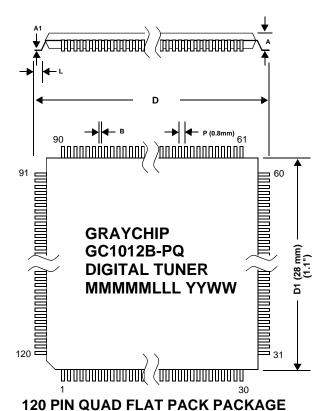

**Device:** Graychip GC1012B (see Appendix D)

**Decimation:** 2 to 64

**Data Source:** 12 most significant bits from associated A/D output

**Clock Source:** A/D clock

Sync: Maskable inside each GC1012B chip

(All receiver channels directed to the same VIM BIFO

must be synced at the GC1012B output)

Output: 32 bits parallel complex, 16-bit I, 16-bit Q; Parallel real also

available, 16-bit I, 16-bit I

**Bypass Mode:** Data from A/D converters can be written directly into the

FPGA (bypassing GC1012B's) at a sample rate equal to the A/D clock decimated by any value from 1 to 4096

Field-Programmable Gate Array

**Device:** Standard: Xilinx Virtex–II XC2V1000

Option 300: Xilinx Virtex-II XC2V3000

**Programming:** Factory programmed by Pentek (see Section 1.11)

<u>Power</u>

For XC2V1000 FPGA w/average use: 12.5 W (610 mA @ +12V, 1.04A @ 5V)

For XC2V1000 FPGA w/heavy use: 15 W (estimated) 17.5 W (estimated)

(Note: Estimated at 100MHz; FPGA power consumption varies based on usage)

**Physical**

Dimensions

VIM-2 Module

Height:

114.3 mm (4.5 in.)

Depth:

82.5 mm (3.25 in.)

Width:

20.3 mm (0.80 in.)

Weight:

130.4 grams (4.6 oz)

**Environmental**

**Operating Temperature:**  $0^{\circ}$  to  $50^{\circ}$ C **Storage Temperature:**  $-20^{\circ}$  to  $90^{\circ}$ C

**Relative Humidity:** 95% non–condensing

**VME Rack Exhaust Temp:** 0° to 50°C

# Chapter 2: Installation and Connections

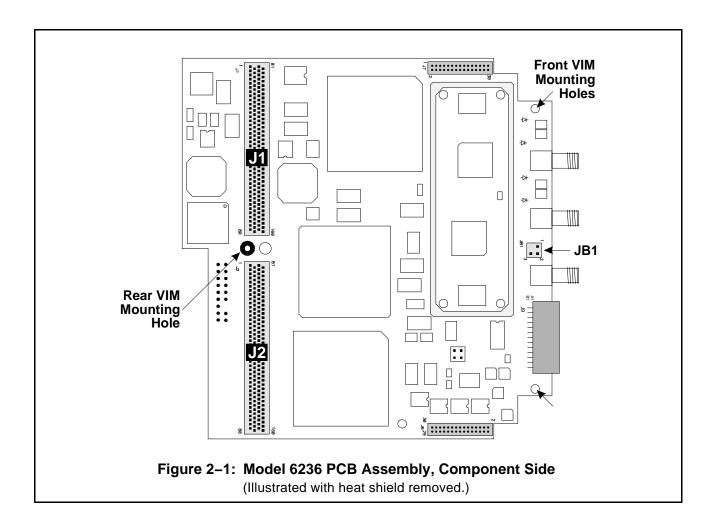

#### 2.1 Inspection

After unpacking, inspect the unit carefully for possible damage to connectors or components. If any damage is discovered, contact Pentek immediately at (201) 818–5900. Please save the original shipping container and packing material in case reshipment is required. The component side of the PCB is illustrated in Figure 2–1 on the next page.

# 2.2 **Jumper Settings**

There is only one jumper on the Model 6236 module that can be set by the user.

The user should not change jumpers that are not identified in this chapter—all other jumpers are reserved for factory test and setup purposes only.

Jumper **JB1** selects the source of the Virtex FPGA configuration data download. The FPGA can select its configuration data either from an on–board Serial EEPROM or from a serial download (using a Xilinx cable), depending on the setting of this jumper. Refer to Virtex Config Register, Section 3.3, for further information on reconfiguring the Virtex FPGA.

Table 2–1 shows the jumper settings for this FPGA configuration data source jumper. This jumper block has three pins. Note the location of pin 1 of the jumper block, which is identified on the PCB (see Figure 2–1 on the next page).

| Table 2–1: FPGA Configuration Data Source Jumper |                     |                                |  |  |  |  |  |

|--------------------------------------------------|---------------------|--------------------------------|--|--|--|--|--|

| 4                                                | Jumper JB1 Position | FPGA Data Source               |  |  |  |  |  |

| 1 = 2                                            | 1 – 2               | Serial Download (Xilinx cable) |  |  |  |  |  |

| <b>a</b> 3                                       | Removed, or 2 – 3 * | On-board Serial EEPROM         |  |  |  |  |  |

|                                                  | * Factory De        | efault Setting                 |  |  |  |  |  |

# **2.2 Jumper Settings** (continued)

### 2.3 Installing the Model 6236 on a VIM Baseboard

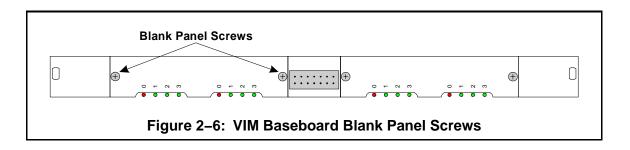

This section provides instructions for installing the Model 6236 VIM–2 module on a VIM–compatible baseboard. Pentek's VIM baseboards ship with two blank panel inserts and four VIM interface connectors where you can install VIM modules such as the Model 6236. See Figure 2–3, on the next page, for illustration of a typical Pentek VIM baseboard.

Perform all assembly steps at an antistatic workstation.

#### Tools required for all procedures:

- #1 Phillips screwdriver

- Flat-blade screwdriver (blade width 5/16-inch or less)

The Model 6236 is shipped in different configurations. The installation instructions vary according to the configuration you receive from Pentek, as follows:

☐ If you have ordered a Model 6236 **without** Option 102, you have received a single VIM module that you must mount on your existing VIM baseboard.

Refer to Section 2.3.1 for the instructions for this configuration.

☐ If you have ordered a Model 6236 with Option 102, you have received an assembly of a Model 6236 PCB and an Option 102 PCB, plus a front panel assembly. You must disassemble these components to mount them onto your existing VIM baseboard.

Refer to Section 2.3.2 for the instructions for this configuration.

**NOTE:** Be sure to follow all instructions in the order presented.

All required mounting hardware and front panels are included in your shipment.

#### 2.3.1 Installing Model 6236 without Option 102

This section provides instructions for installing the Model 6236 VIM–2 (without Option 102) on your existing VIM baseboard.

The Model 6236 module is shipped as an assembled unit and must be disassembled for installation on your VIM baseboard.

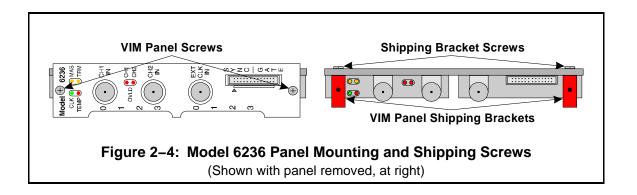

1) Remove the front panel from the Model 6236 VIM–2 module by removing the two countersunk Phillips screws from the panel (see figure below).

- 2) Remove the (red) shipping brackets that hold the front panel to the VIM-2 module by removing the pan-head Phillips shipping bracket screws from the solder side of the Model 6236 PCB (see figure above). Set these screws aside, as they are used to secure the VIM module to the VIM baseboard.

- (The shipping brackets may be discarded, or saved to store the panel back on the VIM module if it is removed from the VIM baseboard.)

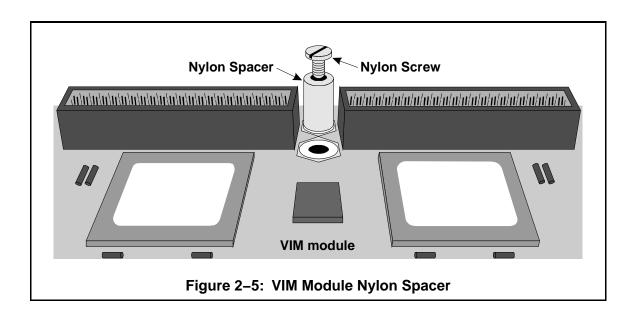

- 3) A nylon spacer is installed on the component side of the Model 6236 PCB, between the VIM connectors (see Figure 2–5 on the following page). Remove the nylon screw that is threaded into the top of the spacer from the component side. Set this screw aside, as it is used to secure the VIM module to the VIM baseboard.

#### 2.3.1 Installing Model 6236 without Option 102 (continued)

The nylon spacer must be installed in the hole at the REAR of the VIM connectors, farthest from the front panel (as illustrated above and indicated in Figure 2–1 on page 18).

If the spacer is installed in the front hole, reposition it by removing the nylon screw on the solder side of the module and threading it back into the spacer through the rear hole.

4) Remove one blank panel insert from your VIM baseboard, at the VIM position you wish to install the Model 6236 module, by removing the two countersunk Phillips screws from the panel insert (see figure below).

#### 2.3.1 Installing Model 6236 without Option 102 (continued)

- 5) With the VIM baseboard's component side (the side with the VIM connectors) facing up, align the two VIM connectors on the Model 6236 VIM–2 module (**J1** and **J2**) with two VIM connectors on the baseboard—the Model 6236 VIM–2 module may be installed in either the top or bottom mezzanine position on the VIM baseboard. See Figure 2–1 for location of the Model 6236 VIM connectors, and see Figure 2–3 for location of the VIM connectors on a typical VIM baseboard.

- 6) **GENTLY but firmly**, press down on the VIM module opposite the connectors to fully seat the module's connectors into the baseboard. If you meet with significant resistance, check the connector alignment.

**NOTE:** Misalignment can cause bent pins or break connector housings, so **NEVER APPLY EXCESSIVE FORCE**.

7) After seating the connectors, secure the front of the VIM module to the VIM baseboard by screwing two short pan-head Phillips screws through the mounting holes in the front of the VIM module (see figure below and Figure 2–1), into the threaded holes in baseboard's panel brackets (indicated at positions (a) and (b), or (c) and (d) on Figure 2–3).

- 8) Turn the assembly over, such that the VIM module is on the work surface and the solder side of the VIM baseboard is facing up. Secure the baseboard to the nylon spacer on the VIM module, using the nylon screw removed earlier (see figure above), through the rear mounting hole on the baseboard (indicated at position (e) or (f) on Figure 2–3).

- 9) Attach the Model 6236 VIM module's front panel to the baseboard, by screwing the countersunk Phillips screws through the holes of the VIM panel, into the threaded holes in the baseboard's front panel brackets.

The Model 6236 installation is complete.

#### 2.3.2 Installing Model 6236 with Option 102

The Model 6236 with Option 102 is shipped as an assembled unit and must be disassembled for installation. A separate Option 102 front panel assembly is also provided.

1) Remove both front panels from the Model 6236 VIM–2 module and the Option 102 module by removing the two countersunk Phillips screws from each panel (see figure below).

- 2) Remove the (red) shipping brackets that hold the front panels to both modules by removing the pan-head Phillips shipping bracket screws from the solder side of the Option 102 PCB (see figure above).

- (The shipping brackets may be discarded, or saved to store the panels if they are removed from the VIM baseboard.)

- 3) Remove and set aside the five pan-head Phillips standoff screws from the top of the Option 102 board (see figure above).

- 4) **CAREFULLY**, remove the Option 102 board from the stacking connectors (see figure above), taking care to not bend the pins.

- 5) **GENTLY**, remove and set aside both stacking connectors from the Model 6236 PCB. Do not remove the five (black) metal standoffs from this PCB.

Be careful when removing the stacking connectors, as they are fragile and can easily be damaged.

#### 2.3.2 Installing Model 6236 with Option 102 (continued)

6) A nylon spacer is installed on the component side of the Model 6236 PCB, between the VIM connectors. Remove and set aside the nylon screw that is threaded into the top of the spacer (see figure below).

The nylon spacer must be installed in the hole at the REAR of the VIM connectors, farthest from the front panel (as shown in the figure above). If the spacer is installed in the front hole, reposition it using the nylon screw on the solder side of the module.

7) Remove one blank panel insert from your VIM baseboard, at the VIM position you wish to install the Model 6236 module, by removing the two countersunk Phillips screws from that panel insert (see figure below).

## 2.3.2 Installing Model 6236 with Option 102 (continued)

- 8) With the VIM baseboard's component side (the side with the VIM connectors) facing up, align the two VIM connectors on the Model 6236 VIM–2 module (**J1** and **J2**) with two VIM connectors on the baseboard—the Model 6236 VIM–2 module may be installed in either the top or bottom mezzanine position on the VIM baseboard. See Figure 2–1 for location of the Model 6236 VIM connectors, and see Figure 2–3 for location of the VIM connectors on a typical VIM baseboard.

- 9) **GENTLY but firmly**, press down on the VIM module opposite the connectors to fully seat the VIM module's connectors into the baseboard. If you meet with significant resistance, check the connector alignment.

**NOTE:** Misalignment can cause bent pins or break connector housings, so **NEVER APPLY EXCESSIVE FORCE**.

- 10) After seating the connectors, secure the front of the VIM module to the VIM baseboard by screwing two short pan-head Phillips screws through the mounting holes at the front of the VIM module into the threaded holes in the baseboard's panel brackets (indicated at positions (a) and (b), or (c) and (d) on Figure 2–3).

- 11) Turn the assembly over, such that the VIM module is on the work surface and the solder side of the VIM baseboard is facing up. Secure the baseboard to the nylon spacer on the VIM module, using the nylon screw removed earlier, through the rear mounting hole on the baseboard (indicated at position (e) or (f) on Figure 2–3).

- 12) Remove one top or bottom blank panel insert from the Option 102 front panel assembly provided (see illustration below), depending on the VIM position in which the Model 6236 module was installed in the above steps. The remaining fixed plates and blank panel will be installed onto the baseboard front panel in the following steps.

#### 2.3.2 Installing Model 6236 with Option 102 (continued)

13) Install the Option 102 front panel assembly (which is in two pieces depending on which blank panel you removed in the prior step) onto the VIM baseboard front panel using the four long pan-head Phillips screws supplied (see figure below).

14) **CAREFULLY**, insert the two stacking connectors into the solder side of the Model 6236 PCB. Note that the stacking connector's longer leads must be inserted through holes on the solder side of the PCB (see figure below).

Be careful when installing the stacking connectors, as they are fragile and can easily be damaged.

#### 2.3.2 Installing Model 6236 with Option 102 (continued)

15) Align the Option 102 PCB connectors **J1** and **J2** with the two stacking connectors on the VIM module. **GENTLY but firmly**, press down on the areas of the board opposite the connectors to fully seat the board's connectors into the VIM module.

NOTE: Misalignment can cause bent pins or break connector housings, so NEVER APPLY EXCESSIVE FORCE.

16) After seating the connectors, secure the front of the Option 102 PCB to the baseboard by screwing two short pan—head Phillips screws through the holes near the front of the PCB into the threaded holes in the Option 102 front panel assembly's panel brackets (see figure below).

- 17) Screw the five pan-head Phillips standoff screws removed from the PCB earlier through the solder side of the Option 102 PCB into the VIM module standoffs (see figure above).

- 18) Attach the Model 6236 and Option 102 front panels to the assembly, by screwing the countersunk Phillips panel screws through the holes in each VIM panel into the corresponding threaded holes in the front panel brackets.

The Model 6236 installation is complete.

#### 2.4 Front Panel Connections

The Model 6236 standard configuration provides a single front panel—a second front panel is provided with Option 102, mounted on an adjacent VMEbus board. Both of these front panels are illustrated in the figure at the right.

The standard panel includes three coaxial SMA input connectors labeled **CH1**, **CH2**, and **EXT CLK IN**, and a 26-pin Sync bus connector labeled **SYNC/GATE**. The optional second panel provides a 4-pin **SYNC/GATE/TRG** input connector, and a 50-pin **FPGA** I/O connector. These connectors are described in the following subsections.

#### 2.4.1 Analog Input Connectors

The Model 6236 standard front panel has two threaded, coaxial SMA connectors for analog signal inputs (labeled **CH1 IN** and **CH2 IN**), one for each A/D input channel.

The analog input signal must be within the range of 1 V<sub>p-p</sub>

(4 dBm). Each input drives an RF transformer with approximately 50  $\Omega$  input impedance. This device amplifies the amplitude of the input signal by a factor of one.

# 2.4.2 External Clock Input Connector

The Model 6236 standard panel has a threaded, coaxial SMA connector, labeled **EXT CLK IN**, for input of an external clock. The external clock signal must be a sine signal of 01 to 10 dBm.

This input clock can be used as the reference signal to derive the sample clock signal for the A/D converters and DDRs. This input is enabled using bit D2, EXT CLK, in the Master Control Register (see Section 3.7.7).

#### **2.4** Front Panel Connections (continued)

#### 2.4.3 Sync/Gate Connector

The 26–pin **SYNC/GATE** connector provides input/output for six low–voltage differential signal (LVDS) pairs: four gates, one sync, and one clock. When the Model 6236 is a sync bus Master, these pins output the sync bus signals to other 6236 slave units. When the 6236 is a sync bus Slave, these pins input the signals from a bus Master. Two TTL Gate/Sync inputs are also provided. The mating 26–pin connector is Pentek part # 353.02607 (ERNI # 214346). The following table shows the connector pinouts.

| Table 2–2: SYNC/GATE Connector Pins |     |                          |     |         |  |

|-------------------------------------|-----|--------------------------|-----|---------|--|

| Signal                              | Pin |                          | Pin | Signal  |  |

| TTL GATE                            | B1  |                          | A1  | GND     |  |

| TTL SYNC                            | B2  |                          | A2  | GND     |  |

| GATE D-                             | В3  | B1 ▶ • • A1<br>B2 • • A2 | А3  | GATE D+ |  |

| GND                                 | B4  | B3 • • A3                | A4  | GND     |  |

| GATE C-                             | B5  | B4                       | A5  | GATE C+ |  |

| GND                                 | B6  | B6 • • A6                | A6  | GND     |  |

| GATE B-                             | B7  | B7 • • A7                | A7  | GATE B+ |  |

| GND                                 | B8  | B8                       | A8  | GND     |  |

| GATE A-                             | B9  | B10 • • A10              | A9  | GATE A+ |  |

| GND                                 | B10 | B11                      | A10 | GND     |  |

| SYNC-                               | B11 | B13 • • A13              | A11 | SYNC+   |  |

| GND                                 | B12 |                          | A12 | GND     |  |

| CLK-                                | B13 |                          | A13 | CLK+    |  |

## 2.4.4 Sync/Gate Header (Option 102 only)

The optional 4–pin **SYNC/GATE/TRG** connector provides a second set of connections for TTL Sync/Gate inputs. These are wired to the same TTL SYNC and TTL GATE signals as pins B1 and B2 of the **SYNC/GATE** connector, above. The mating 2–pin connector housing (use two for both signals) is Pentek part # 353.00201 (Berg # 65039–035) or equivalent. This connector housing uses discrete 0.025" square socket pins, Pentek part # 354.00104 (Berg # 48254–000). The following table shows the connector pinouts.

| Table 2-3: SYNC/GATE/TRG Header Pins |     |         |     |        |  |

|--------------------------------------|-----|---------|-----|--------|--|

| Signal                               | Pin |         | Pin | Signal |  |

| TTL SYNC                             | 1   | 1 2     | 2   | GND    |  |

| TTL GATE/TRG                         | 3   | 3 • • 4 | 4   | GND    |  |

## **2.4** Front Panel Connections (continued)

# 2.4.5 FPGA Connector (Option 102 only)

The optional 50-pin **FPGA** connector provides a 32-pin FPGA input/out-put data path. These pins correspond to bits D0 through D15 of the I/O Data Register (see Section 3.20). The mating connector is Pentek part # 353.05006 (ERNI part # 214347). The following table shows the pinouts of this connector, and illustrates the connector pin configuration.

| Table 2–4: FPGA Connector Pins |     |                   |   |   |            |     |             |

|--------------------------------|-----|-------------------|---|---|------------|-----|-------------|

| Description                    | Pin |                   |   |   |            | Pin | Signal      |

| GND                            | B1  |                   |   |   |            | A1  | GND         |

| FPGA I/O 31                    | B2  |                   |   |   |            | A2  | FPGA I/O 30 |

| FPGA I/O 29                    | В3  |                   |   |   |            | A3  | FPGA I/O 28 |

| GND                            | B4  | [                 |   |   |            | A4  | GND         |

| FPGA I/O 27                    | B5  | B1 <b>▶</b><br>B2 | • | • | A1<br>A2   | A5  | FPGA I/O 26 |

| FPGA I/O 25                    | В6  | В3                | • | • | А3         | A6  | FPGA I/O 24 |

| GND                            | B7  | B4<br>B5          | • | • | A4<br>A5   | A7  | GND         |

| FPGA I/O 23                    | B8  | B6                | • | • | A6         | A8  | FPGA I/O 22 |

| FPGA I/O 21                    | В9  | B7<br>B8          | • | • | A7<br>A8   | A9  | FPGA I/O 20 |

| GND                            | B10 | В9                | • | • | A0<br>A9   | A10 | GND         |

| FPGA I/O 19                    | B11 | B10               | • | • | A10        | A11 | FPGA I/O 18 |

| FPGA I/O 17                    | B12 | B11<br>B12        |   | • | A11<br>A12 | A12 | FPGA I/O 16 |

| N/C (Spare)                    | B13 | B13               | • | • | A13        | A13 | N/C (Spare) |

| GND                            | B14 | B14<br>B25        | • | • | A14<br>A15 | A14 | GND         |

| FPGA I/O 15                    | B15 | B16               | • | • | A16        | A15 | FPGA I/O 14 |

| FPGA I/O 13                    | B16 | B17<br>B18        | • | • | A17<br>A18 | A16 | FPGA I/O 12 |

| GND                            | B17 | B19               | • | • | A19        | A17 | GND         |

| FPGA I/O 11                    | B18 | B20<br>B21        | • | • | A20<br>A21 | A18 | FPGA I/O 10 |

| FPGA I/O 9                     | B19 | B21<br>B22        | • | • | A21<br>A22 | A19 | FPGA I/O 8  |

| GND                            | B20 | B23               | • | • | A23        | A20 | GND         |

| FPGA I/O 7                     | B21 | B24<br>B25        | • | • | A24<br>A25 | A21 | FPGA I/O 6  |

| FPGA I/O 5                     | B22 |                   |   |   |            | A22 | FPGA I/O 4  |

| GND                            | B23 |                   |   |   |            | A23 | GND         |

| FPGA I/O 3                     | B24 |                   |   |   |            | A24 | FPGA I/O 2  |

| FPGA I/O 1                     | B25 |                   |   |   |            | A25 | FPGA I/O 0  |

#### 2.5 Front Panel LEDs

The Model 6236 front panel has six LED indicators, as shown in Figure 2–15, page 29.

#### 2.5.1 Clock LED

The green **CLK** LED is illuminated when a clock signal is detected. If this LED is not illuminated, then no clock signal has been detected and no data from this stream can be processed.

#### 2.5.2 Over Temperature LED

There are several temperature/voltage sensors on the Model 6236 PCB. The sensor thresholds are set by a VIM baseboard processor (see Hardware Monitor Port Register, Section 3.6). When an over–temperature or over–voltage condition is indicated, the red **TEMP** LED is illuminated on the front panel. In addition, an over–temperature/voltage interrupt is available to any baseboard processor (see Table 3–17, page 51).

NOTE: You must set up the sensors' Hardware Monitor Port following power on of a Model 4290/4291 VIM baseboard (see Hardware Monitor Port Register, Section 3.6). ReadyFlow board support software for the Model 6236 is provided for this purpose.

#### 2.5.3 Master LED

The yellow **MAS** LED is illuminated when this Model 6236 is the sync bus Master (MASTR bit D00 = 1, Master Control Register, Section 3.7.9). The bus Master generates all sync/gate/clock signals on the sync bus.

#### 2.5.4 Terminate LED

When this Model 6236 is the last (or only) Slave unit on the sync bus, you must enable bus termination (TERM bit D01, Master Control Register, (see Section 3.7.8). Enabling bus termination illuminates the yellow **TRM** LED.

#### 2.5.5 Overload LEDs

There are two red overload LEDs, labeled **OVLD CH1** and **OVLD CH2**. Each LED is an indicator for the A/D overload detection function in each of the AD6645 A/D converters. When an overload indication is set by the AD6645, the associated OVLD LED is illuminated. In addition, an OVLD interrupt may be generated from each A/D overload indication to the VIM baseboard processors (see Section 3.14).

# Chapter 3: Memory Maps and Register Descriptions

#### 3.1 Overview

This chapter describes processor access to the Model 6236 from the VIM baseboard. Memory maps to VIM module resources are given from the baseboard processor's viewpoint, and details are provided describing the use of each resource.

# 3.2 Model 6236 Memory Map

The two tables below provide base addresses of the Model 6236 control and status registers for each type of Pentek VIM Baseboard. Use the applicable base address from these tables as the VIM registers base address ('VIMReg\_base') in the following sections.

**For a Pentek Model 4290 through 4295 VIM baseboard**, use the VIM registers base addresses in Table 3–1, below. These baseboards have four processor nodes, one for each VIM Interface, and each node processor uses the same VIM base address to access the associated VIM module.

| Table 3-1: VIM Base Addresses for Models 4290 to 4295 VIM Baseboards |                                          |  |  |  |

|----------------------------------------------------------------------|------------------------------------------|--|--|--|

| VIM Baseboard                                                        | VIM Registers Base Address (VIMReg_base) |  |  |  |

| Model 4290 or 4291                                                   | 0x0032 0000                              |  |  |  |

| Model 4292 or 4293                                                   | 0x0202 0000                              |  |  |  |

| Model 4294 or 4295                                                   | 0x1D02 0000                              |  |  |  |

**For a Pentek Model 4205 VIM baseboard**, use the VIM registers base addresses in Table 3–2, below. The Model 4205 has a single baseboard processor, which uses a separate base address for each VIM Interface (emulating four processors). In addition, on this baseboard the VIM module registers can be accessed from the VMEbus.

| Table 3–2: VIM Base Addresses for Model 4205 VIM Baseboards |                                          |                           |  |  |  |

|-------------------------------------------------------------|------------------------------------------|---------------------------|--|--|--|

| VIM Site                                                    | VIM Registers Base Address (VIMReg_base) |                           |  |  |  |

|                                                             | MPC7455                                  | VMEbus A32 Slave *        |  |  |  |

| VIM A                                                       | 0x4082 0000                              | A32VME_base + 0x00B2 0000 |  |  |  |

| VIM B                                                       | 0x4086 0000                              | A32VME_base + 0x00B6 0000 |  |  |  |

| VIM C                                                       | 0x408A 0000                              | A32VME_base + 0x00BA 0000 |  |  |  |

| VIM D                                                       | 0x408E 0000                              | A32VME_base + 0x00BE 0000 |  |  |  |

<sup>\*</sup> Offsets relative to the base address 'A32VME\_base' set on the Model 4205 baseboard (refer to the Model 4205 Operating Manual for these settings)

#### 3.2 Model 6236 Memory Map (continued)

The following table provides a memory map for the Model 6236 32–bit control and status registers. All register addresses are expressed as offsets from the VIM registers base address for the applicable VIM baseboard—see Table 3–1 or Table 3–2 on the prior page for the VIM registers base address ('VIMReg\_base') for your VIM baseboard. The sections following the table provide detailed information about each register.

| Table 3–3: Model 6236 Memory Map                         |                                           |        |              |  |  |  |  |  |  |

|----------------------------------------------------------|-------------------------------------------|--------|--------------|--|--|--|--|--|--|

| Address Offset*                                          | Register Description                      | Access | Information  |  |  |  |  |  |  |

| VIMReg_base+0x0000                                       | ID EEPROM Readout                         | R.O.   | Appendix A   |  |  |  |  |  |  |

| VIMReg_base+0x0004                                       | Virtex Config (Proc. A or C only)         | R/W    | Section 3.3  |  |  |  |  |  |  |

| VIMReg_base+0x0008                                       | Virtex Config Data (Proc. A or C only)    | W.O.   | Section 3.4  |  |  |  |  |  |  |

| VIMReg_base+0x000C                                       | Wait States (Proc. A or C only)           | R/W    | Section 3.5  |  |  |  |  |  |  |

| VIMReg_base+0x0010                                       | Hardware Monitor Port (Proc. A or C only) | R/W    | Section 3.6  |  |  |  |  |  |  |

| VIMReg_base+0x0014 - 0x001C                              | Not Used                                  | _      | -            |  |  |  |  |  |  |

| VIMReg_base+0x0020                                       | Master Control (Proc. A or C only)        | R/W    | Section 3.7  |  |  |  |  |  |  |

| VIMReg_base+0x0024                                       | eg_base+0x0024 Bypass Rate Divide         |        | Section 3.8  |  |  |  |  |  |  |

| VIMReg_base+0x0028                                       | Sync Mask                                 | R/W    | Section 3.9  |  |  |  |  |  |  |

| VIMReg_base+0x002C                                       | Not Used                                  | _      | -            |  |  |  |  |  |  |

| VIMReg_base+0x0030                                       | Gate Control                              | R/W    | Section 3.10 |  |  |  |  |  |  |

| VIMReg_base+0x0034                                       | Trigger Length                            | R/W    | Section 3.11 |  |  |  |  |  |  |

| VIMReg_base+0x0038                                       | Channel Control                           | R/W    | Section 3.12 |  |  |  |  |  |  |

| VIMReg_base+0x003C                                       | Sync/Gate Generator                       | R/W    | Section 3.13 |  |  |  |  |  |  |

| VIMReg_base+0x0040                                       | Not Used                                  | _      | -            |  |  |  |  |  |  |

| VIMReg_base+0x0044                                       | Interrupt Mask                            | R/W    | Section 3.14 |  |  |  |  |  |  |

| VIMReg_base+0x0048                                       | Interrupt Flag                            | R/Clr  | Section 3.15 |  |  |  |  |  |  |

| VIMReg_base+0x004C                                       | Interrupt Status                          | R.O.   | Section 3.16 |  |  |  |  |  |  |

| VIMReg_base+0x0050                                       | Semaphore                                 | R/W    | Section 3.17 |  |  |  |  |  |  |

| VIMReg_base+0x0054 - 0x005C                              | Not Used                                  | _      | _            |  |  |  |  |  |  |

| VIMReg_base+0x0060                                       | I/O Direction (Option 102 only)           | R/W    | Section 3.18 |  |  |  |  |  |  |

| VIMReg_base+0x0064                                       | I/O Enable (Option 102 only)              | R/W    | Section 3.19 |  |  |  |  |  |  |

| VIMReg_base+0x0068                                       | I/O Data (Option 102 only)                | R/W    | Section 3.20 |  |  |  |  |  |  |

| VIMReg_base+0x006C - 0x00FC                              | Not Used                                  | _      | _            |  |  |  |  |  |  |

| VIMReg_base+0x0100 - 0x013F                              | Graychip Registers (Option 212 only)      | R/W    | Section 3.21 |  |  |  |  |  |  |

| * VIMReg_base = see Table 3-1 or Table 3-2 on prior page |                                           |        |              |  |  |  |  |  |  |

## 3.3 Virtex Config Register

The Virtex Config Register can be used to reconfigure/reprogram the Virtex FPGA. The bits in this register allow you to read and set the status of the FPGA configuration cycle, and to control uploading the configuration from a baseboard processor. This register is accessible only to Processor A on the VIM baseboard (or Processor C for a Model 6236 installed in the bottom VIM position on the baseboard).

Refer to Section 1.11, FPGA Configuration, for additional information about configuring the Virtex FPGA.

The following table shows the contents of the Virtex Config Register. The subsections following the table provide descriptions of the bits in this register.

| Table 3-4: Virtex Config Register  R/W @ VIMReg_base+0x0004 (Proc A or C only)           |                           |                          |                           |                                  |                                  |                              |                           |  |  |

|------------------------------------------------------------------------------------------|---------------------------|--------------------------|---------------------------|----------------------------------|----------------------------------|------------------------------|---------------------------|--|--|

|                                                                                          | D31 – D06                 | D05                      | D04                       | D03*                             | D02*                             | D01                          | D00                       |  |  |

| Bit Name                                                                                 | Not used                  | WRITE                    | Not used                  | INIT                             | DONE                             | PRGM                         | LD SRC                    |  |  |

| Function                                                                                 | Write zeros,<br>Mask read | 0 = Disable<br>1 = Write | Write zeros,<br>Mask read | 0 = Configuring<br>1 = Completed | 0 = Configuring<br>1 = Completed | 0 = Disable<br>1 = Reprogram | 0 = Onboard<br>1 = Upload |  |  |

| * These bits are Read Only All bits default to the logic '0' state at power on and reset |                           |                          |                           |                                  |                                  |                              |                           |  |  |

**3.3.1 WRITE** Bit D05

This bit sets the write access of the Virtex Config Data Register, described in Section 3.4. When you set this bit to logic '1', you can write configuration data to the FPGA. To write data with the Virtex Config Data Register, you must also enable configuration upload (LD SRC bit D00 = 1, Section 3.3.5). Clear the bit to logic '0' (its default state) to disable configuration data from being accepted by the FPGA.

**3.3.2 INIT** Bit D03

This read—only bit indicates the status of the FPGA's 'INIT' pin. At initial—ization of a configuration cycle this bit goes to logic '0', then logic '1'. It will remain at logic '0' if an error in configuration data is detected. When read as logic '1', initialization is done.

**3.3.3 DONE** Bit D02

This read—only bit indicates the status of the FPGA's 'DONE' pin. When read as logic '0', the FPGA is in the configuration cycle. When read as logic '1', the FPGA has completed configuration.

# 3.3 Virtex Config Register (continued)

**3.3.4 PRGM** Bit D01

The FPGA begins a configuration reprogramming cycle after you transition this bit from logic '0', to logic '1', to logic '0', when in the Serial EEPROM or processor upload modes (see LD SRC, below). It has no effect in the serial download mode, as the Xilinx cable has control in that mode.

**3.3.5 LD SRC** Bit D00

This bit selects the source of the FPGA configuration data. When you clear this bit to logic '0' (its default state), the Virtex selects its configuration data from the on–board Serial EEPROM or from a serial download (depending on the setting of the configuration data source jumper on the 6236 module PCB, see Section 2.2). When you set this bit to logic '1', the FPGA is in processor upload mode, and you can upload the configuration using the Virtex Config Data Register, as described in Section 3.4.

# 3.4 Virtex Config Data Register

The Virtex Config Data Register writes configuration data to the Virtex FPGA. The write access is set by the WRITE bit in the Virtex Config Register (Section 3.3.1). When the LD SRC bit in the Virtex Config Register (Section 3.3.5) is set to '1', the FPGA configuration data can be uploaded, one byte at a time, using the Virtex Config Data Register. The Virtex Config Data Register is accessible only to Processor A (or Processor C for a Model 6236 installed in the bottom VIM position on the baseboard).

The following table shows the contents of this register.

| Table 3–5: Virtex Config Data Register W.O. @ VIMReg_base+0x0008 (Proc A or C only) |                                                                        |                                                           |    |    |    |    |    |    |    |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------|----|----|----|----|----|----|----|--|

|                                                                                     | D31 – D08                                                              | D31 – D08   D07   D06   D05   D04   D03   D02   D01   D00 |    |    |    |    |    |    |    |  |

| Bit Name                                                                            | Not used                                                               | D7                                                        | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

| Function                                                                            | Write zeros                                                            | Vrite zeros Eight bits (one byte) of configuration data   |    |    |    |    |    |    |    |  |

|                                                                                     | When reset, including power–up, the state of this register is unknown. |                                                           |    |    |    |    |    |    |    |  |

Refer to Section 1.11, FPGA Configuration, for additional information about configuring the Virtex FPGA.

## 3.5 Wait State Register

With the possibility of DBCLKs above 50 MHz, programmable wait states are provided to guarantee adequate access time. These wait states are user–programmable, using the Wait States Register. The Wait States Register is accessible only to Processor A on the VIM baseboard (or Processor C for a Model 6236 installed in the bottom VIM position on the baseboard).

The following table shows the contents of the Wait State Register. The paragraphs following the table provide descriptions of the fields in this register.

| Table 3-6: Wait States Register  R/W @ VIMReg_base+0x000C (Proc A or C only) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                |             |            |           |                                |     |               |  |

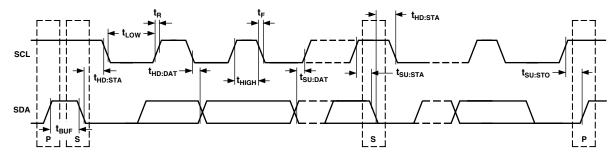

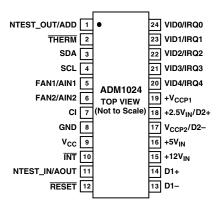

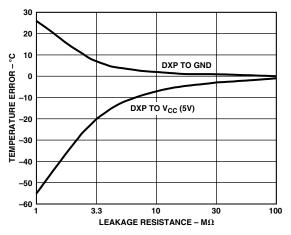

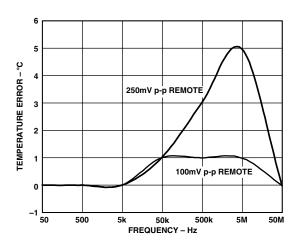

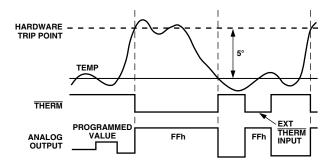

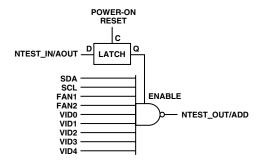

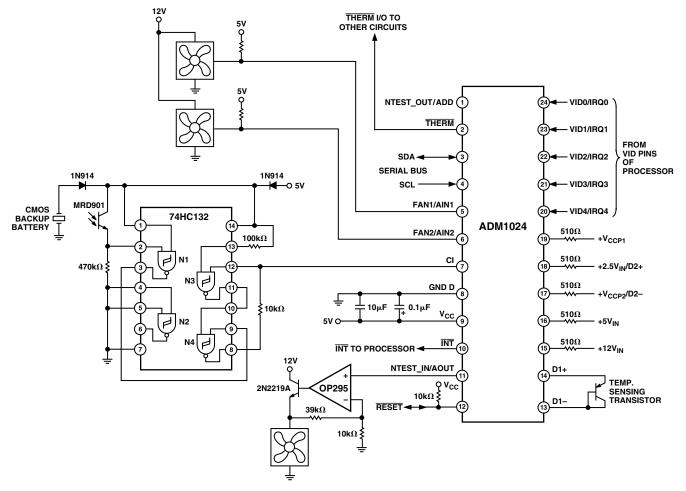

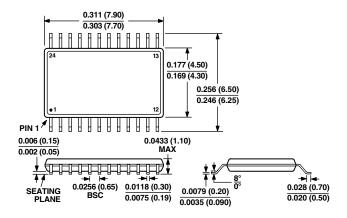

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------|-------------|------------|-----------|--------------------------------|-----|---------------|--|