In Stock

**Used and in Excellent Condition**

Open Web Page

https://www.artisantg.com/94655-1

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

In stock / Ready-to-ship

Critical and expedited services

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# ZT 8825 and ZT 88CT25 Expanded\Extended Memory Systems

#### HARDWARE MANUAL

For ZT 8825 and ZT 88CT25 REVISION A.4

Reorder Part Number ZT M8825 April 29, 1993

1050 Southwood Drive San Luis Obispo, CA 93401 USA FAX (805) 541-5088 Telephone (805) 541-0488

#### ZIATECH WARRANTY

Ziatech Hardware: Within two years of shipping date, Ziatech will repair or replace products which prove to be defective in materials and/or workmanship, provided they are promptly returned to Ziatech at customer's expense and have not been repaired, altered, or damaged by non-Ziatech personnel. Service after warranty is available at a predesignated service charge. Batteries are not covered by this warranty. No other warranty is expressed or implied.

**Ziatech Software:** Within 90 days of shipping date, Ziatech will replace software (PROM or diskette) should it prove defective.

**Products not manufactured by Ziatech:** Limited to the warranty provided by the original manufacturer.

**Notice:** Contact Ziatech for a Return Materials Authorization (RMA) number before returning any product to Ziatech for repair.

**Life Support Policy:** Ziatech products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Ziatech Corporation. As used herein:

- Life support devices or systems are devices or systems that support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### ©1998 Ziatech Corporation

Portions copyright 1987 Lotus Development Corporation, Intel Corporation, Microsoft Corporation. Used by permission.

#### **CUSTOMER SUPPORT**

If you have a technical question, please call Ziatech's Customer Support Service at the following number:

Corporate Headquarters: (805) 541-0488 (805) 541-5088 (FAX)

You can also use a modem to leave a message on the 24 hour Ziatech Bulletin Board Service (BBS) by calling (805) 541-8218. The BBS will provide you with current Ziatech product revision and upgrade information.

If you have a sales question, please contact your local Ziatech Sales Representative.

#### **PREFACE**

This manual discusses hardware and systems level topics for the ZT 8825 and ZT 88CT25 extended byte-wide memory systems. All references in this manual to the ZT 8825 include the ZT 88CT25 unless otherwise indicated. The ZT 8825 Software Support Package manual addresses software support issues.

The following organizational outline describes the focus of each chapter in this manual. Section headings enclosed in boxes indicate the location of a labeled tab for quick access to the appropriate information.

#### I. INTRODUCTION

**Chapter 1, "Introduction,"** contains a brief overview of the ZT 8825. It includes a product definition and a listing of product features.

#### I. GETTING STARTED

**Chapter 2, "Getting Started,"** summarizes the information essential to getting your ZT 8825 up and running. You can refer to subsequent chapters for further explanation of the material covered in "Getting Started."

#### III. USER'S REFERENCE

**Chapter 3, "Theory Of Operation,"** presents a more detailed look at the way the ZT 8825 functions. Some topics covered in this chapter include I/O addressing, memory addressing, memory mapping, and extended memory mode.

**Chapter 4, "Application Examples,"** includes specific examples of the ZT 8825 in operation, including code to implement these applications. Examples include initializing the ZT 8825 as continuous memory and as extended memory.

**Chapter 5, "Configurable Options,"** details the various jumperselectable options on the ZT 8825.

#### IV. APPENDICES

**Appendix A, "Jumper Configurations,"** lists the ZT 8825 jumpers in numerical order and describes the function of each. This appendix also indicates the factory default configuration and includes a figure that shows the location of each jumper.

**Appendix B, "Specifications,"** includes electrical, mechanical, and environmental specifications for the ZT 8825.

**Appendix C, "Hardware Quick Reference,"** supplies a centralized location for frequently referenced tables and illustrations.

**Appendix D, "Customer Support,"** offers a product revision history, the Ziatech warranty, and the necessary information should you need to return your ZT 8825 for repair.

**Appendix E, "Glossary,"** lists definitions for acronyms and important terms used in the manual.

# **CONTENTS**

| I.  | INTRODUCTION              |      |

|-----|---------------------------|------|

| Ch  | napter 1. INTRODUCTION    | 1-1  |

| ΟV  | /ERVIEW                   | 1-1  |

|     | ODUCT DESCRIPTION         |      |

|     | ATURES OF THE ZT 8825     |      |

| II. | GETTING STARTED           |      |

| Ch  | apter 2. GETTING STARTED  | 2-1  |

| ΟV  | /ERVIEW                   | 2-1  |

| UN  | NPACKING                  | 2-2  |

| WF  | HAT'S IN THE BOX          | 2-2  |

| SY  | STEM REQUIREMENTS         | 2-3  |

|     | Backplane Recommendations | 2-4  |

|     | Processor Compatibility   | 2-4  |

| SO  | OCKET ASSIGNMENTS         | 2-5  |

| WF  | RITE PROTECT              | 2-5  |

| ME  | EMORY SPEED REQUIREMENTS  | 2-6  |

| ВО  | OARD CONFIGURATIONS       | 2-7  |

| СН  | IIP SIZE SELECTION        | 2-10 |

| СН  | IIP TYPE SELECTION        | 2-14 |

| I/O | ADDRESSING                | 2-16 |

#### **Contents**

III. USER'S REFERENCE

**Chapter 4. APPLICATION EXAMPLES**

**Chapter 5. CONFIGURABLE OPTIONS**

| Chapter 3. THEORY OF OPERATION  | 3-1    |

|---------------------------------|--------|

| OVERVIEW                        | 3-2    |

| MEMORY CHIP TYPE                |        |

| MEMORY CHIP SIZE                |        |

| WAIT STATES                     |        |

| WRITE PROTECTION                | 3-6    |

| BATTERY BACKUP                  | 3-7    |

| I/O ADDRESSING                  | . 3-10 |

| MEMORY ADDRESSING               | . 3-13 |

| 20-bit Memory Addressing        | 3-13   |

| 24-bit Memory Addressing        | 3-13   |

| MEMORY MAPPING                  |        |

| Paging                          | 3-14   |

| Map Registers                   | 3-15   |

| Configuration Register          | . 3-17 |

| Setting the Map Register        | 3-18   |

| Absolute Address Mode           | . 3-19 |

| EXTENDED MEMORY MODE            | . 3-20 |

| Setting the 24-bit Map Register | 3-20   |

|                                 |        |

INITIALIZING ZT 8825 AS CONTINUOUS MEMORY . . . . . . . 4-1 EXAMPLE PROGRAMS USING EMS . . . . . . . . . . . . 4-7

OVERVIEW ...... 5-2 MEMORY CHIP TYPE SELECTION ...... 5-3 MEMORY CHIP SIZE SELECTION ...... 5-6 BATTERY BACKUP SELECTION ..... 5-9

4-1

| I/O BASE ADDRESS SELECTION                                                                                                                                                                                                                   |                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| IV. APPENDICES                                                                                                                                                                                                                               |                                                      |

| Appendix A. JUMPER CONFIGURATIONS                                                                                                                                                                                                            | A-1                                                  |

| OVERVIEW JUMPER DESCRIPTIONS USER JUMPER CONFIGURATION SWITCH CONFIGURATION                                                                                                                                                                  | A-2<br>A-5                                           |

| Appendix B. SPECIFICATIONS                                                                                                                                                                                                                   | B-1                                                  |

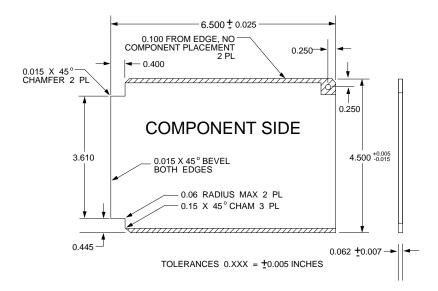

| ELECTRICAL SPECIFICATIONS  ZT 8825 Power Requirements  ZT 88CT25 Power Requirements  STD Load Characteristics  ENVIRONMENTAL SPECIFICATIONS  Operating Temperature  Storage Temperature  MECHANICAL SPECIFICATIONS  Card Dimensions & Weight | B-1<br>B-2<br>B-2<br>B-4<br>B-4<br>B-4               |

| Appendix C. HARDWARE QUICK REFERENCE                                                                                                                                                                                                         | C-1                                                  |

| JUMPER DESCRIPTIONS                                                                                                                                                                                                                          | C-2<br>C-5                                           |

| Appendix D. CUSTOMER SUPPORT                                                                                                                                                                                                                 | D-1                                                  |

| ZT 8825 REVISION HISTORY Revision 0.1 Revision A - June 7, 1988 Revision A.1 - January 1, 1989 Revision A.2 - July 6, 1989 Revision A.3 - January 30, 1991 Revision A.4 - September 23, 1991 TECHNICAL ASSISTANCE RELIABILITY WARRANTY       | D-1<br>D-2<br>D-2<br>D-2<br>D-2<br>D-4<br>D-4<br>D-5 |

| RETURNING FOR SERVICE                                                                                                                                                                                                                        | D-6                                                  |

| Contents             |     |

|----------------------|-----|

| Appendix E. GLOSSARY | E-1 |

| V. INDEX             |     |

| Index                | i   |

# **TABLES**

| Table 2–1 | ZT 8825 Basic Access Time Requirements      | . 2-6  |

|-----------|---------------------------------------------|--------|

| Table 2–2 | Chip Size Selection.                        | 2-12   |

| Table 2–3 | Valid Chip Combinations                     | 2-13   |

| Table 2–4 | Chip Type Jumper Configurations             | 2-15   |

| Table 2–5 | ZT 8825 I/O Registers                       | 2-16   |

| Table 2–6 | Default I/O Address Assignments             | 2-17   |

| Table 3–1 | Chip Size Combinations                      | 3-5    |

| Table 3–2 | Est. Battery Life @ Max. Standby Current    | 3-7    |

| Table 3–3 | Default I/O Address Assignments             | 3-10   |

| Table 3–4 | ZT 8825 I/O Registers.                      | . 3-11 |

| Table 5–1 | Signal Choices on Each Socket.              | 5-3    |

| Table 5–2 | Jumper Selection of Socket Signals          | . 5-4  |

| Table 5–3 | Chip Type Jumper Configurations             | . 5-5  |

| Table 5–4 | Switch Settings for All Possible Chip Sizes | 5-7    |

| Table 5–5 | ZT 8825 Basic Access Time Requirements      |        |

| Table 5–6 | Jumper Settings for Battery Backup          | 5-9    |

| Table 5–7 | Jumpers for I/O Base Address Decoding       | 5-11   |

| Table A–1 | ZT 8825 Jumper Descriptions.                | . A-2  |

| Table A–2 | Switch Settings for All Possible Chip Sizes | . A-5  |

| Table B-1 | ZT 8825 STD Bus Loading                     | . B-3  |

| Table B–2 | ZT 8825 Rev. A.4 Material List              | . B-6  |

| Table C–1 | ZT 8825 Jumper Descriptions.                |        |

| Table C–2 | Jumpers for I/O Base Address Decoding       | . C-5  |

| Table C–3 | Chip Type Jumper Configurations             | . C-6  |

| Table C-4 | Switch Settings for All Possible Chip Sizes | C-7    |

# **ILLUSTRATIONS**

| Figure 2–1 | Factory Default Jumper Configuration  | 2-8  |

|------------|---------------------------------------|------|

| Figure 2–2 | Example Setting for 24-bit Addressing | 2-9  |

| Figure 2–3 | Memory Chip Orientation.              | 2-11 |

| Figure 3–1 | Functional Block Diagram              | 3-2  |

| Figure 3–2 | Logical to Physical Address Mapping   | 3-15 |

| Figure 3–3 | Map Register                          | 3-16 |

| Figure 3–4 | Configuration Register                | 3-17 |

| Figure A–1 | Customer Jumper Configuration         | A-6  |

| Figure B–1 | ZT 8825 Card Dimensions               | B-5  |

|            |                                       |      |

### Chapter 1

### **INTRODUCTION**

| Contents                | Page |

|-------------------------|------|

| OVERVIEW                |      |

| PRODUCT DESCRIPTION     | 1-2  |

| FEATURES OF THE ZT 8825 | 1-4  |

### **OVERVIEW**

This chapter briefly introduces some key features and some possible applications for the ZT 8825. Unless specifically called out, all references to ZT 8825 also refer to the CMOS extended temperature version ZT 88CT25.

### PRODUCT DESCRIPTION

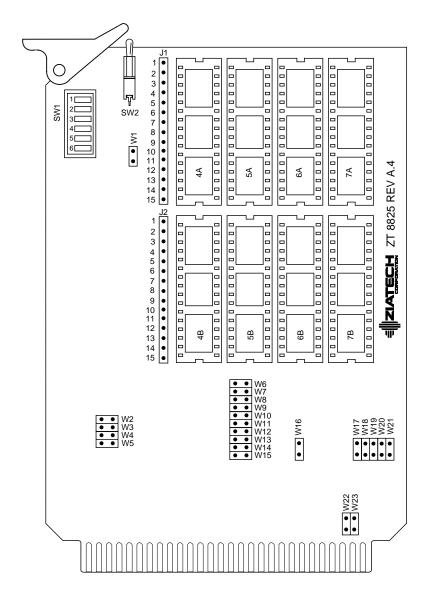

The ZT 8825, a member of Ziatech's growing STD-80 Series product line, is a state-of-the-art memory board that accommodates 28- and 32-pin byte-wide memory chips. The board is divided into two rows of four memory chip sockets. Device type can be configured for each row of four sockets individually. Address decoding can be configured separately for each 16 Kbytes of memory. This provides an extremely flexible board that can accommodate the memory requirements of nearly any system.

The ZT 8825 can be used with several different processors in many modes of operation:

- 1. Normal Memory: The ZT 8825 memory can be mapped in 16 Kbyte blocks to anywhere in the 1 Mbyte address space of the *STD-80 Series Bus Specification*.

- 2. Extended Memory: For processors like the Intel 80286 (protected mode) and 80386 or the Motorola 680XX family, the ZT 8825 provides memory that can be mapped in 16 Kbyte blocks at any address, including those above the 1 Mbyte limit. The board supports 24-bit addressing if the CPU meets the *STD-80 Series Bus Specification*.

- 3. Expanded Memory: The ZT 8825 hardware supports the Lotus-Intel-Microsoft Expanded Memory Specification (EMS), Versions 3.2 & 4.0 and the AST Enhanced Expanded Memory Specification (EEMS), Version 3.2. These specifications allow access to additional memory outside of the normal 1 Mbyte address space of the processor or DOS. The Ziatech ZT 8825 Software Support Package provides many of the DOS subroutines required for the above specifications. See the ZT 8825 Software Support Package manual for more information.

- 4. RAM or PROM disk: The ZT 8825 can be organized as a disk using the software provided with the product. DOS can work with these pseudo-disks in the same manner as with regular disks.

Devices that can be used in the ZT 8825 include: EPROMs (for example, 27128, 27256, 27512, 27010, 27020, 27040, up to 1 Mbyte chips), 5V-only EEPROMs (for example, 28C256, 28C010), and static RAMs (for example, HM62256, HM628128). The maximum amount of memory on a ZT 8825 is limited to 2 Mbytes. There are also some limitations to the combinations of chip sizes that can be used (see page 3-5).

The STD-80 Series 20-bit memory address protocol is used for memory addressing. The board will also accept 24-bit addressing. The on-board registers use 8- or 16-bit I/O addresses. The ZT 8825 configured with 120 ns memories operates without wait states when used with an 8 MHz processor board such as the ZT 8809. The ZT 8825 configured with 250 ns memories operates without wait states when used with a 5 MHz CPU board. An optional wait state is user-selectable, allowing the use of slower memory devices (see page 3-6).

An example of the versatility of the ZT 8825 is that EPROM can be used on one half of the ZT 8825 and RAM on the other half. This arrangement will provide the total memory requirements for many STD systems. The ZT 8825 is effectively two byte-wide boards in one. See Chapter 4 for details on additional application examples.

#### FEATURES OF THE ZT 8825

- Direct 20-bit or 24-bit addressing (compatible with the *STD-80 Series Bus Specification*)

- Each 16 Kbyte block is independently addressable

- Two sets (four sockets each) of 32-pin JEDEC sockets

- Various combinations of RAM (32K-2M) and EPROM (16K-2M)

- Optional wait state for slow device types

- Selectable hardware and software write protect to aid debugging

- No wait states needed at 5 or 8 MHz with fast memory chips

- Supports EMS versions 3.2 and 4.0 as well as EEMS version 3.2

- Supports 5V-only Flash EPROMS

- 2 Mbyte maximum on-board storage

- Optional 1 Amp-hour battery backup

- Burned in and tested

- TTL-compatible

- The CMOS version ZT 88CT25 operates at substantially lower power (0.5 W typical as compared to 2.5 W typical for the ZT 8825)

- The ZT 88CT25 operates over a temperature range of -40° to +85°C

#### Chapter 2

### **GETTING STARTED**

| Contents                  | Page |

|---------------------------|------|

| OVERVIEW                  | 2-1  |

| UNPACKING                 | 2-2  |

| WHAT'S IN THE BOX         | 2-2  |

| SYSTEM REQUIREMENTS       | 2-3  |

| Backplane Recommendations |      |

| Processor Compatibility   | 2-4  |

| SOCKET ASSIGNMENTS        |      |

| WRITE PROTECT             | 2-5  |

| MEMORY SPEED REQUIREMENTS | 2-6  |

| BOARD CONFIGURATIONS      | 2-7  |

| CHIP SIZE SELECTION       | 2-10 |

| CHIP TYPE SELECTION       | 2-14 |

| I/O ADDRESSING            | 2-16 |

### **OVERVIEW**

This chapter is intended for users who require only a brief summary of information essential to getting their systems up and running. Other users should refer back to this chapter after familiarizing themselves with the more detailed information found in subsequent chapters. Unless explicitly noted, all references to ZT 8825 in this manual also refer to the CMOS version ZT 88CT25.

#### **UNPACKING**

Upon receipt of the shipping carton, check for any damage to its contents. Normally, the contents will survive considerable abuse since the packing is designed to protect against typical shipping and handling stresses. However, if the board is damaged or fails to function, notify the carrier and Ziatech to arrange for insurance settlement. Retain the shipping carton and packing material for the carrier's inspection. Under no circumstances should a board or cable be returned to Ziatech without a Return Material Authorization (RMA) Number (see page D-6).

#### WHAT'S IN THE BOX

When the package is opened, you should find:

- 1. The ZT 8825 Operator's Manual and the ZT 8825 Software Support Package manual (in a binder).

- 2. One ZT 8825 or ZT 88CT25 PC Board.

- 3. Anti-static packing material.

- 4. One software driver diskette.

Attach the sticker found with the manual onto the spine of the binder for easy identification. Be sure to save the anti-static packing material for storing or shipping the ZT 8825.

#### **WARNING!**

Like all equipment utilizing CMOS devices, the ZT 8825 must be protected from static discharge. Never remove or install any of the socketed parts except at a static-free work station.

#### SYSTEM REQUIREMENTS

The ZT 8825 is designed to be physically compatible with card cages manufactured to meet the STD-80 Series Specification and should normally be mounted in one.

The board requires +5 V DC ±5% @ 0.67 A maximum, not including any memory chips. A typical fully-populated EPROM board requires approximately 1.17 A maximum. Maximum continuous power dissipation in this configuration is 6.0 W. A typical fully-populated SRAM board requires approximately 0.77 A maximum.

The ambient temperature must be maintained between  $0^{\circ}$  and  $+65^{\circ}$  Celsius to avoid improper operation and possible damage to the ZT 8825. The ZT 88CT25 operates in an ambient temperature range of  $-40^{\circ}$  to  $+80^{\circ}$ C. The relative humidity should be less than 95% at  $40^{\circ}$  C, non-condensing.

Vertical mounting is recommended in convective cooling systems not equipped with a fan. However, most systems require a fan for reliable operation. Horizontal mounting is not recommended unless forced air cooling of at least 30 cubic ft./min. is provided.

If a standard STD bus card cage is not used, refer to the figure on page B-5 for dimensions. Be sure to allow enough clearance for good convective or forced cooling.

#### **Getting Started**

#### **Backplane Recommendations**

Ziatech recommends the use of a multilayer backplane for good power distribution and noise suppression. The ZT 32 series of card cages and backplanes work well in STD-80 and STD 32 systems.

#### **Processor Compatibility**

The ZT 8825 is designed for STD-80 Series systems. It can be used with other microprocessors only if they meet the STD-80 Series multiplexed memory addressing and timing specifications.

#### **SOCKET ASSIGNMENTS**

Memory chip socket Row A includes sockets 4A, 5A, 6A, and 7A. Memory chip socket Row B includes sockets 4B, 5B, 6B, and 7B. Socket 4A/B is always in the lowest address range of the row when using Ziatech initialization software, and socket 7A/B is always the highest.

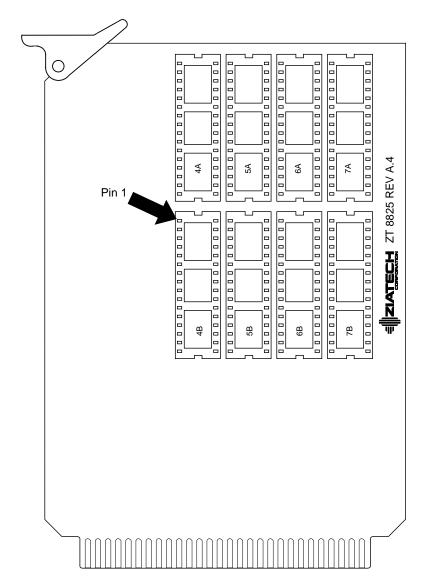

28-pin memory chips must be inserted with socket pins 1, 2, 31 and 32 empty. When looking at the ZT 8825 circuit board with the component side facing you and the edge connector at the bottom, 28-pin chips should be installed in the bottom-most section of the socket.

#### WRITE PROTECT

When debugging programs in RAM, there is a tendency for certain programming errors to cause undesired writes to RAM. The ZT 8825 has a write-protect switch (SW2) that can be used to prevent writes to any of the memory chips installed on the board. This switch is located near the outside edge of the board for easy access. The switch is positioned up away from the board for write enable, down toward the board for write protect.

The RAM may also be software write-protected by setting bit 3 of the Configuration Register to logic 0. Bit 3 is logic 0 at power-on or reset time. Both SW2 and bit 3 must be enabled to allow writing to the RAM. If either is in protect mode, the RAM will be protected.

## **MEMORY SPEED REQUIREMENTS**

Table 2-1 shows the basic chip access time requirements for static RAMs (SRAMs), EPROMs or EEPROMs. See page 3-6 for more information about wait states.

Table 2-1 ZT 8825 Basic Access Time Requirements.

| 0 WAIT STATES |               |              | 1 WAIT STATE   |               |               |     |     |                |

|---------------|---------------|--------------|----------------|---------------|---------------|-----|-----|----------------|

| TIMING        | ZT 8<br>5 MHz | 825<br>8 MHz | ZT 88<br>5 MHz | CT25<br>8 MHz | ZT 8<br>5 MHz |     |     | 8CT25<br>8 MHz |

|               |               |              |                |               |               |     |     |                |

| Tce           | 290           | 120          | 255            | 80            | 490           | 240 | 455 | 205            |

| Taa           | 315           | 140          | 295            | 130           | 515           | 265 | 495 | 255            |

| Toe           | 190           | 80           | 190            | 80            | 390           | 205 | 390 | 205            |

| Twp           | 160           | 95           | 135            | 70            | 360           | 220 | 335 | 195            |

| Tdw           | 250           | 130          | 250            | 130           | 550           | 255 | 450 | 255            |

|               |               |              |                |               |               |     |     |                |

#### **BOARD CONFIGURATIONS**

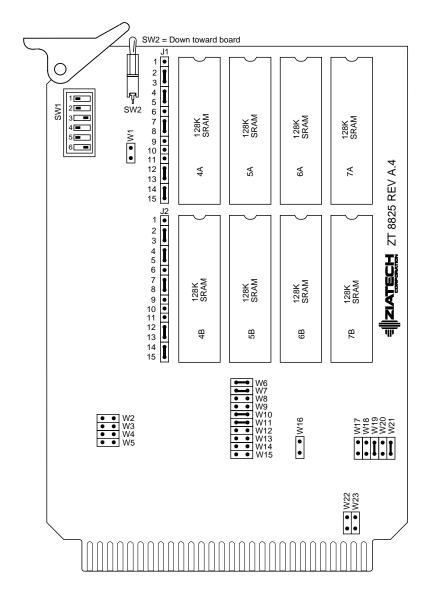

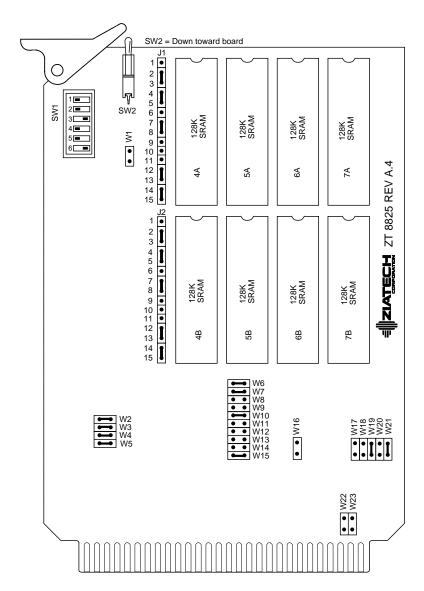

The ZT 8825 incorporates several jumpers that can be set to select different board configurations. The default configuration includes 20-bit memory addressing, 16-bit I/O port addressing, 0 wait states on all memory accesses, no battery backup, high IOEXP for access to registers, and is configured for 128K SRAM chips in both rows. If the default configuration (shown in Figure 2-1 on page 2-8) meets your needs, you do not need to change any jumpers. An example configuration that substitutes 24-bit addressing but is otherwise set for the default options appears in Figure 2-2 on page 2-9.

Each configurable option is covered in detail in Chapter 5, "Configurable Options," to assist you to correctly set your board for non-default operation. Appendix A, "Jumper Configurations," outlines the function of each jumper.

**Note**: Even if you have purchased RAMs, EPROMs, a battery, or other memory devices from Ziatech, your ZT 8825 will still have the default jumper settings and must be reconfigured as appropriate for the type and speed of the memory chips you install.

We recommend that you document your configuration on the blank layout provided in Appendix A on page A-6. This will allow you to easily restore the configuration if it is changed for any reason.

Figure 2–1. Factory Default Jumper Configuration.

Figure 2–2. Example Setting for 24-bit Addressing.

### **CHIP SIZE SELECTION**

Six-segment switch SW1 must be set according to the size of memory chips installed. Segments 6, 5, and 4 correspond to Row B chip size while segments 3, 2, and 1 correspond to Row A. See Table 2-2 on page 2-12 and Table 2-3 on page 2-13 for allowable settings.

#### **WARNING!**

Memory chips **must** be properly oriented to avoid damage. Pin 1 must be installed in the upper left hand corner of the socket, as indicated in Figure 2-3. Note that some hybrid chips contain labeling oriented differently from what you might expect. Some chips have half moons on both ends. Because of this, extra care should be taken to identify pin 1.

Figure 2–3. Memory Chip Orientation.

### **Getting Started**

Table 2-2 Chip Size Selection.

| Size | Switch section† 321 (or 654) |

|------|------------------------------|

| 16K  | 000                          |

| 32K  | 001                          |

| 64K  | 010                          |

| 128K | 011                          |

| 256K | 100                          |

| 512K | 101                          |

| 1M   | 110                          |

| 512K | special - two chips in row A |

|      |                              |

$<sup>\</sup>dagger$  Switch section setting of 0 = ON, 1 = OFF.

Table 2-3 Valid Chip Combinations.

| Size | ROW A | SW 321 | Size | ROW B | SW 654 |

|------|-------|--------|------|-------|--------|

|      |       |        |      |       |        |

| 16K  | †     | 000    | 16K  | †     | 000    |

| 32K  | †     | 001    | 32K  | †     | 001    |

| 64K  | †     | 010    | 32K  | †     | 001    |

| 64K  | †     | 010    | 64K  | †     | 010    |

| 128K | †     | 011    | 32K  | †     | 001    |

| 128K | †     | 011    | 128K | †     | 011    |

| 256K | †     | 100    | 128K | †     | 011    |

| 256K | †     | 100    | 256K | †     | 100    |

| 512K | †     | 101    |      |       | XXX    |

| 1M   | **    | 110    |      |       | XXX    |

| 512K | *     | 111    | 256K | †     | 100    |

| 512K | *     | 111    | 512K | *     | 101    |

<sup>\* 2</sup> chips (sockets 4 and 5) max; e.g., use Row A for RAM and Row B for PROM.

Notes: Any empty sockets must be accounted for by the software when it accesses the physical pages represented by the empty sockets.

Switch setting of 0 = ON, 1 = OFF. XXX = Don't care; switch bits not used.

<sup>\*\* 2</sup> chips (sockets 4 and 5) only, due to 2 Mbyte board limit.

<sup>† 1, 2, 3,</sup> or 4 chips per row are acceptable.

### **CHIP TYPE SELECTION**

All chips in each row must be of the same size and type. Jumper sets J1 and J2 define the configuration for memory chip Rows A and B, respectively. The configurations shown in Table 2-4 cover all chip types known at publication time.

Table 2-4 Chip Type Jumper Configurations.

| Chip Type                                             | J1 or J2 Pin #                        |

|-------------------------------------------------------|---------------------------------------|

|                                                       | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1   |

| 16 Kbyte EPROM                                        | 0-0 0 0 0 0-0 0-0 0 0 0-0 0-0         |

| 32 Kbyte EPROM                                        | 0 0-0 0 0 0-0 0-0 0 0 0-0 0-0         |

| 64 Kbyte EPROM                                        | 0 0-0 0 0-0 0 0-0 0 0 0-0 0-0         |

| 128 Kbyte EPROM*                                      | 0 0-0 0 0-0 0 0-0 0 0-0               |

| 256 Kbyte EPROM                                       | 0 0-0 0 0-0 0 0 0-0 0 0-0             |

| 512 Kbyte EPROM                                       | 0 0-0 0 0-0 0 0-0 0 0-0 0-0           |

| 1 Mbyte EPROM                                         | 0 0-0 0 0-0 0 0 0-0 0 0-0             |

| 32 Kbyte SRAM                                         | 0-0 0-0 0 0 0-0 0 0-0 0-0 0           |

| 128 Kbyte SRAM                                        | 0-0 0-0 0 0 0 0-0 0 0-0 0             |

| 256 Kbyte SRAM                                        | · · · · · · · · · · · · · · · · · · · |

| 512 Kbyte SRAM                                        | 0-0 0-0 0 0 0 0-0 0-0 0               |

| 32 Kbyte, 28-Pin Flash EPROM†<br>TI 29F256, AT 29C256 | 600000000000000                       |

| 32 Kbyte, 32-Pin Flash EPROM†<br>AT 29C257            | 6000000000000000                      |

| 128 Kbyte, 32-Pin Flash EPROM†<br>AT 29C010           | 6000000000000000                      |

Note:  $\circ$ — $\circ$  indicates a jumper is installed between those two posts.

<sup>\*</sup> The jumper configuration shown is for Intel and AMD 128K x 8 EPROMS only. For all other I28K x 8 manufacturers, please remove the jumpers between pins 1-2 and 3-4. Wire-wrap pin J to pin 8 and pin 4 to pin 9. This applies +5V to EPROM pins 1 and 31 (Vpp and /pgm) to meet non-Intel/AMD requirements.

$<sup>\</sup>dagger$  Flash EPROMs require special software routines for programming. See ZT 8825 Software Support Package documentation.

### **I/O ADDRESSING**

The ZT 8825 has four I/O registers that are used to configure the board (see Table 2-5. These registers require jumpers to set the base I/O address (see Table 2-6 on page 2-17). The default base address is 0EE68h.

Table 2-5 ZT 8825 I/O Registers.

| Base+ | Default | Description                                                 |

|-------|---------|-------------------------------------------------------------|

| 000   | EE68h   | Low order six bits of map register address (write only)     |

| 001   | EE69h   | High order four bits of map register address (write only)   |

| 010   | EE6Ah   | Data to/from map register previously addressed (read/write) |

| 011   | EE6Bh   | Configuration register (write only, reset to 0 at power-on) |

Table 2-6 Default I/O Address Assignments.

| Address<br>Line | Default<br>Condition  | Default<br>Base Address<br>(Binary) | Default<br>Base Address<br>(Hexadecimal) |

|-----------------|-----------------------|-------------------------------------|------------------------------------------|

| A15             | W14 out               | 1                                   | E                                        |

| A14             | W13 out               | 1                                   |                                          |

| A13             | W12 out               | 1                                   |                                          |

| A12             | W11 in                | 0                                   |                                          |

| A11             | 1 hardwired           | 1                                   | Е                                        |

| A10             | 1 hardwired           | 1                                   |                                          |

| A9              | 1 hardwired           | 1                                   |                                          |

| A8<br>A7        | 0 hardwired<br>W10 in | 0                                   |                                          |

| A6              | W9 out                | 1                                   | 6                                        |

| A5              | W8 out                | 1                                   |                                          |

| A4              | W7 in                 | 0                                   |                                          |

| A3              | 1 hardwired           | 1                                   | 8                                        |

| A2              | -                     | 0                                   |                                          |

| A1              | -                     | 0                                   |                                          |

| A0              | -                     | Ő                                   |                                          |

## III. USER'S REFERENCE

| THEORY OF OPERATION  | 3-  |

|----------------------|-----|

| APPLICATION EXAMPLES | 4-1 |

| CONFIGURABLE OPTIONS | 5-  |

## Chapter 3

## THEORY OF OPERATION

| Contents P:                     | age  |

|---------------------------------|------|

| OVERVIEW                        | 3-2  |

| MEMORY CHIP TYPE                | 3-4  |

| MEMORY CHIP SIZE                | 3-4  |

| WAIT STATES                     | 3-6  |

| WRITE PROTECTION                | 3-6  |

|                                 |      |

| I/O ADDRESSING                  |      |

| MEMORY ADDRESSING               |      |

| 20-bit Memory Addressing        | 3-13 |

| 24-bit Memory Addressing        |      |

| MEMORY MAPPING                  |      |

| Paging                          | 3-14 |

|                                 | 3-15 |

| Configuration Register          | 3-17 |

| Setting the Map Register        |      |

| Absolute Address Mode           |      |

| EXTENDED MEMORY MODE            |      |

| Setting the 24-bit Map Register |      |

### **OVERVIEW**

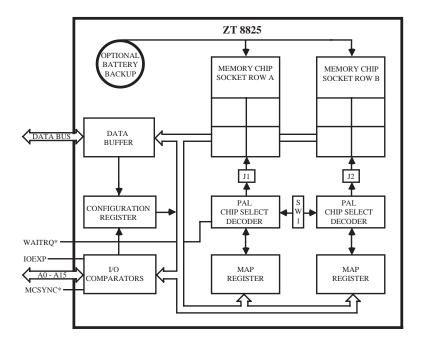

This chapter presents a high-level look at the way the ZT 8825 functions. It is designed to help you become more familiar with the board. Figure 3-1 illustrates the functional relationship between the key components on the board. Refer to Figure 3-1 as you read this chapter.

Figure 3–1. Functional Block Diagram.

The ZT 8825 is a state-of-the-art STD bus compatible memory board that accommodates most popular byte-wide memory chips. It is electrically, physically, and logically compatible with the STD bus as defined by the *STD-80 Series Bus Specification*. In addition, the CMOS version ZT 88CT25 is TTL compatible. Unless specifically noted, all references to ZT 8825 in this manual refer also to ZT 88CT25.

There are eight memory chip sockets on the ZT 8825. These sockets are divided into two rows of four. Each row can be independently configured for memory chip type (for example, EPROM, EEPROM, static RAM).

The ZT 8825 uses the STD-80 Series 20-bit memory address protocol. It can also accommodate 24-bit addressing. The user sees the board as many separate 16 Kbyte memory boards. In addition to implementing the normal 1 Mbyte STD-80 Series address space, the ZT 8825 allows access to Extended Memory address space up to 16 Mbytes. Also implemented are the *Lotus-Intel-Microsoft Expanded Memory Specification* (EMS), Versions 3.2 and 4.0, and the *AST Enhanced Expanded Memory Specification* (EEMS), Version 3.2, allowing access to up to 2 Mbytes of memory on the board. Multiple boards may be used to achieve up to 32 Mbytes of memory.

#### **MEMORY CHIP TYPE**

The ZT 8825 accepts JEDEC-compatible byte-wide memory devices of either 28 or 32 pins. All chips in each row of four must be of the same type (for example, all static RAM in Row A, all EPROM in Row B) and the same size (all 64K in Row A, all 32K in Row B).

Each row can be selected to be ROM, EPROM, EEPROM, or Flash or static RAM. Jumper set J1 selects the chip type for Row A and jumper set J2 selects the chip type for Row B. See page 5-3 for more information on configuring the board for memory chip type.

## **MEMORY CHIP SIZE**

Switch 1 is a six-segment switch that provides a signal to a preprogrammed PAL indicating the chip size used in each row. This allows the PAL to decode the appropriate address bits for the chips used. Switch 1 segments 6, 5, and 4 select the chip size for Row B while switch 1 segments 3, 2, and 1 select the chip size for Row A. Table 3-1 shows the allowable chip size combinations for Row A and Row B along with the corresponding settings for switch 1. Refer to page 5-6 for more information on configuring your board for memory chip size.

Table 3-1 Chip Size Combinations.

| Row A                                                                                  |                                       | Row B                                            | Switch 1<br>654321                                                                                      |

|----------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 16K<br>32K<br>64K<br>64K<br>128K<br>128K<br>256K<br>256K<br>512K<br>1M<br>512K<br>512K | †<br>†<br>†<br>†<br>†<br>†<br>**<br>* | 32K<br>32K<br>64K<br>32K<br>128K<br>128K<br>256K | † 000000 † 001001 † 001010 † 010010 † 010011 † 011011 † 011100 † 100100 xxx101 xxx110 † 100111 * 100111 |

<sup>\* 2</sup> chips (sockets 4 and 5) max; e.g., use Row A for RAM and Row B for PROM.

Notes: Any empty sockets must be accounted for by the software when it accesses the physical pages represented by the empty sockets.

Switch setting of 0 = ON, 1 = OFF. XXX = Don't care; switch bits not used.

<sup>\*\* 2</sup> chips (sockets 4 and 5) only, due to 2 Mbyte board limit.

<sup>† 1, 2, 3,</sup> or 4 chips per row are acceptable.

### **WAIT STATES**

You may select either zero wait states or one wait state for the board. If one wait state is selected, the ZT 8825 requests a wait state only for 16 Kbyte blocks of memory that you have programmed as enabled. All chips on the board must use the same number of wait states; the slowest chip, therefore, determines the speed of the board.

Generally speaking, devices with a maximum access time of 120 ns will work on the ZT 8825 with no wait states when used with an 8 MHz STD-80 Series CPU board, such as the Ziatech ZT 8809. For 5 MHz STD-80 Series CPUs (for example, with a ZT 8808), access times of 290 ns or less will need no wait states.

For no wait states, the ZT 88CT25 requires devices of < 250 ns for 5 MHz STD-80 Series CPUs and  $\le 80$  ns for 8 MHz STD-80 Series CPUs. Note that when a ZT 88CT25 is used with a ZT 8817 or any other CPU that requires WAITRQ\* to be asserted by mid T2, the CPU *must* insert the wait state. The ZT 88CT25 wait state generator will not be fast enough at 8 MHz to meet the ZT 8817 requirement. Access time requirements are listed in the table on page 5-8. Consult your CPU board manual to answer any questions.

#### WRITE PROTECTION

The ZT 8825 has a write-protect switch (SW2) to assist in program debugging. When this toggle switch is positioned down (default) toward the board, the write signal is inhibited, preventing loss of data should a program run wild. This switch is located at the top of the board for easy access.

Write protection can also be controlled through software by manipulating bit 3 of the Configuration Register. Setting bit 3 to a logical 0 will inhibit writing to the memory (refer to Figure 3-4 on page 3-17). This bit is reset to zero at power-on time and by a system reset. SW2 must be enabled *and* Configuration Register bit 3 must be a logical 1 to write to the memory.

## **BATTERY BACKUP**

An optional battery backup is available as an on-board 1 Amp-hour lithium battery. Either or both of the rows of four sockets may be battery backed. The lithium battery has a long shelf life and will provide years of backup for low power static RAMs (SRAMs) such as the Hitachi HM62256LP-15SL. For even longer back-up, use all-CMOS SRAMs such as Toshiba TC55256 PL-12, NEC  $\mu\text{PD}44256\text{-}12L$  or Sony CXK58255P-12L which have a 1  $\mu\text{A}$  data retention current. See Table 3-2 for the estimated life of batteries used with the ZT 8825 with various SRAM chips installed.

Table 3-2

Est. Battery Life @ Max. Standby Current.

| CHIPS<br>INSTALLED | CURRENT<br>DEMAND<br>Max. | ESTIMATED BATTERY LIFE (HOURS)   |

|--------------------|---------------------------|----------------------------------|

|                    | (μΑ)                      | $0^{\circ}$ C to $+65^{\circ}$ C |

| Eight 200 μA SRAMs | 1640                      | 610                              |

| Eight 50 μA SRAMs  | 440                       | 2,273                            |

| Eight 10 μA SRAMs  | 120                       | 8,333                            |

| Eight 1 µA SRAMs   | 48                        | 20,833                           |

**Note:** It is highly unlikely that the worst case given in Table 3-2 will ever occur. Typical ZT 8825s with 512K of SRAM draw less than  $5 \mu A$  at  $+25^{\circ}$  C, which corresponds to more than 10 years (shelf life limited).

Convert the number of hours given in Table 3-2 to days, months, or years based on the number of hours that the main power supply is off (the battery is the source of power) per day, month, or year.

#### **Theory of Operation**

For example, a board with eight 10  $\mu A$  RAMs installed is used (powered-on) 8 hours per day, 5 days per week at +25°C. In this example, the battery acts as the power supply for the board for different amounts of time on weekdays than on weekends (16 hrs/day on weekdays, 24 hrs/day on weekends). Therefore, an average daily rate must first be calculated. Each week has:

Since the battery is not in use 40 hrs/week, the weekly rate of battery use is:

$$(168-40) \text{ hrs/week} = 128 \text{ hrs/week}$$

which gives a daily rate of:

$$\frac{128 \text{ hrs/week}}{7 \text{ days/week}} = 18.29 \text{ hrs/day}$$

This rate can be used to calculate the estimated battery life in days, weeks, months, or years, as illustrated below.

The estimated battery life in days is:

$$\frac{8333 \text{ hrs}}{18.29 \text{ hrs/day}} = 455.6 \text{ days}$$

in weeks:

$$\frac{8333 \text{ hrs}}{18.29 \text{ hrs/day x 7 days/week}} = 65.1 \text{ weeks}$$

in months:

$$\frac{8333 \text{ hrs}}{18.29 \text{ hrs/day x } 30 \text{ days/month}} = 15.2 \text{ months}$$

in years:

$$\frac{8333 \text{ hrs}}{18.29 \text{ hrs/day x } 365 \text{ days/year}} = 1.25 \text{ years}$$

Again, the actual battery life is likely to be much greater than this worst case estimate.

The ZT 8825 supplies a DCLOW signal for use with the on-board battery backup. DCLOW is asserted when the 5 V supply is below 4.50 V. The ZT 8825 uses this signal to disable any glitching on the write line or chip selects to the memory chips. This signal may optionally assert DCLOW\* (STD bus pin 6, Jumper W22 IN) and/or PBRESET\* (STD bus pin 48, Jumper W23 IN) on the backplane.

Refer to page 5-9 for more information on configuring your board for battery backup.

# **I/O ADDRESSING**

An I/O address is chosen for the ZT 8825 to distinguish it from any other I/O board that exists on the STD bus. If more than one ZT 8825 is used in a system, each must have a unique address.

In addition, the two least significant bits (LSBs) of the I/O address define the location of the Map Registers and Configuration Register used on the ZT 8825 during implementation of EMS. See page 3-14 for more information about EMS and the ZT 8825 Software Support Package manual for EMS programming considerations.

Table 3-3 Default I/O Address Assignments.

| Address              | Default                                     | Default      | Default |

|----------------------|---------------------------------------------|--------------|---------|

| Line                 | Condition                                   | Base Address | (HEX)   |

| A15                  | W14 out                                     | 1            | Е       |

| A14                  | W13 out                                     | 1            |         |

| A13                  | W12 out                                     | 1            |         |

| A12                  | W11 in                                      | 0            |         |

| A11                  | 1 hardwired                                 | 1            | E       |

| A10                  | 1 hardwired                                 | 1            |         |

| A9                   | 1 hardwired                                 | 1            |         |

| A8                   | 0 hardwired                                 | 0            |         |

| A7<br>A6<br>A5<br>A4 | W10 in 0<br>W9 out 1<br>W8 out 1<br>W7 in 0 |              | 6       |

| A3                   | 1 hardwired                                 | 1            | 8       |

| A2                   | -                                           | 0            |         |

| A1                   | -                                           | 0            |         |

| A0                   | -                                           | 0            |         |

The I/O base address for the board may be placed at one of 256 locations in the 64 Kbyte I/O address space of the STD-80 Series bus. The base address can be defined by either 8 or 16 bits (removing Jumper W6 restricts it to 8 bits).

Address lines A15-A0 supply the 16 bits of I/O address to the ZT 8825 (see Table 3-3). A15-A12 are jumper configurable. A11-A8 are hardwired to 1110b. A7-A4 are jumper configurable. A3 is hardwired to a logical 1. A2 is not decoded. A1-A0 define the four unique addresses (000b, 001b, 010b, and 011b) used on the ZT 8825 (see Table 3-4).

**Note:** Since A2 is not decoded, four addresses (100b, 101b, 110b, and 111b) are redundantly mapped and should not be used.

Table 3-4 ZT 8825 I/O Registers.

| Base+ | Default | Description                                                 |

|-------|---------|-------------------------------------------------------------|

| 000   | EE68h   | Low order six bits of Map Register address (write only)     |

| 001   | EE69h   | High order four bits of Map Register address (write only)   |

| 010   | EE6Ah   | Data to/from Map Register previously addressed (read/write) |

| 011   | EE6Bh   | Configuration Register (write only, reset to 0 at power-on) |

#### **Theory of Operation**

Address lines A15-A12 and A7-A4 are tied to Jumpers W14-W11 and W10-W7, respectively. Since the hardware restricts address lines A11-A8 to the value 1110b (Eh) and A7-A4 to the value 1000b (8h), this limits the choice of base addresses to XEY8h, where X and Y may be chosen by Jumpers W14-W11 and W10-W7, respectively. The default base address is 1110111001101XXXb or 0EE68h. See page 5-10 for more information on configuring I/O addresses.

The base address is decoded by two 8-bit comparators. IOEXP (Input/Output Expansion signal) is included in the decode of the I/O address. Its polarity is determined by W15 (default is high). The output of the base address comparator enables a preprogrammed PAL that provides a chip select for each read or write register on the board.

## **MEMORY ADDRESSING**

The ZT 8825 is designed to operate with the STD-80 Series multiplexed memory address scheme. Therefore, while address bits A0-A15 have their own dedicated backplane pins, A16-A23 are multiplexed onto the data bus pins during T1 of a memory access. The MCSYNC\* (machine cycle sync) signal is used to latch the addresses on the ZT 8825. The MEMEX (memory expansion) signal is not used by the ZT 8825.

## 20-bit Memory Addressing

The default memory addressing configuration (Jumpers W2-W5 out) is for 20-bit addressing. On-board pull-down resistors on the internal addressing lines A20-A23 make the Map Registers believe that these upper four address bits are zeros. That is, the 1 Mbyte address space is at the bottom of the 16 Mbyte Extended Memory address space. 20-bit addressing allows for 64 Map Registers (see page 3-15 for more information on Map Registers).

#### 24-bit Memory Addressing

Even though the ZT 8825 was designed to work explicitly with the multiplexed 20-bit memory address scheme of the *STD-80 Series Bus Specification*, it will work with a 24-bit address STD bus (for example, 80286 or similar processors). 24-bit addressing allows for 1,024 Map Registers or 16 Mbytes of address space. Memory between 1 Mbyte and 16 Mbytes is known as Extended Memory. Install Jumpers W2-5 to configure the ZT 8825 for 24 bit addressing.

For more information on configuring your board for memory addressing, refer to page 5-12.

## **MEMORY MAPPING**

This section describes memory mapping for EMS and non-EMS applications. The ZT 8825 supports the *Lotus-Intel-Microsoft Expanded Memory Specification* (EMS), Versions 3.2 and 4.0. It also satisfies the *AST Enhanced Expanded Memory Specification* (EEMS), Version 3.2. The ZT 8825 software drivers implement a subset of those specifications. The EMS Version 3.2 is a subset of the EEMS capabilities. The ZT 8825 can also be set in an "absolute address mode" for easy startup in small systems. True 24-bit address memory anywhere in the 16 Mbyte Extended Memory space is also supported.

## **Paging**

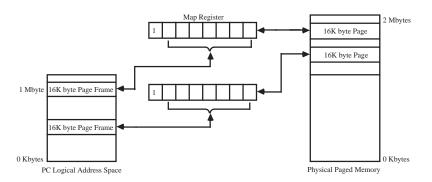

The memory resident on the ZT 8825 can be located outside the normal memory map of the PC when the ZT 8825 is used as an expanded memory board. Using a technique called "paging", the CPU can access 16 Kbyte blocks of physical memory called "pages" through 16 Kbyte blocks of logical memory called "page frames" (see Figure 3-2). Each page frame's logical address points to a page's physical address in expanded memory. That page of memory is then mapped in and out of the page frame space. This mapping may be changed dynamically by your software as required.

Figure 3–2. Logical to Physical Address Mapping.

## **Map Registers**

Each page frame in the logical address space has an associated Map Register on the ZT 8825. 64 Map Registers are used in 20-bit address systems. 1,024 Map Registers are available in 24-bit address systems. In addition, a complete alternate set of Map Registers can be loaded at the same time as the primary set and switched in under software control (see "Setting the Map Register" on page 3-18). The physical registers are composed of two 4K x 4 SRAMs with 35 ns access times. Memory address bits A14-A19 (A14-A23 for 24-bit systems) form the index number of the Map Register for each 16K block.

#### **Theory of Operation**

Each 8-bit wide Map Register points to a 16 Kbyte physical page of memory that is to occupy the page frame currently associated with the Map Register. The most significant bit (MSB) of each register is used as an enable bit for the page frame (see Figure 3-3). If the enable bit is a logical 0, the board does not supply physical memory for that particular 16 Kbyte page frame. If the enable bit is a logical 1, the remaining 7 bits become the index number of that 16 Kbyte page. Once this index number is assigned to the page, the page frame is free to associate with another page.

In this manner, more than 1 Mbyte of physical memory can be mapped into the 1 Mbyte logical memory space. Since 7 bits can point to 128 pages of 16 Kbytes each, the maximum on-board memory is limited to 2 Mbytes (16K x 128). Other ZT 8825s may be used to provide additional pages of memory if the chip size limits the memory to less than 2 Mbytes on one board, or if more than 2 Mbytes is required.

Figure 3–3. Map Register.

#### **Configuration Register**

The Configuration Register allows software control of several board parameters associated with memory mapping. Figure 3-4 illustrates the Configuration Register bits that affect these parameters. The following is a description of the purpose of each Configuration Register bit:

- Bit 0 Map Enable bit. Setting bit 0 to logical 1 turns on the board's mapping functions. Bit 0 must be set to logical 0 when changing the Map Registers.

- Bit 1 Absolute Address Disable bit. Use Bit 1 to choose between an "absolute address mode" (see page 3-19) and addressing modes using the mapping function. Set bit 1 to logical 0 to select absolute address mode.

- Bit 2 Map Write Enable bit. Set bit 2 to logical 0 to protect the Map Register data from being overwritten. Bit 2 must be set to logical 1 to load the Map Registers.

- **Bit 3** RAM Write Enable bit. Use bit 3 to control write protection of RAM (see page 3-6) in software. Set bit 3 to logical 0 to protect RAM from being altered.

- Bits 4 6 Undefined.

- Bit 7 Alternate Map Register Enable bit. Set bit 7 to logical 1 to enable access to a complete alternate set of Map Registers.

| 7                                             | 6 | 5 | 4 | 3                             | 2                             | 1                                     | 0                    |

|-----------------------------------------------|---|---|---|-------------------------------|-------------------------------|---------------------------------------|----------------------|

| Alternate<br>Map<br>Register<br>Enable<br>bit |   |   |   | RAM<br>Write<br>Enable<br>bit | Map<br>Write<br>Enable<br>bit | Absolute<br>Address<br>Disable<br>bit | Map<br>Enable<br>bit |

Figure 3–4. Configuration Register.

## **Setting the Map Register**

Follow these steps to load the Map Register:

- 1. Disable the board by setting the Configuration Register Map Enable bit (bit 0) to logical 0.

- 2. Set the Configuration Register Map Write Enable bit (bit 2) to logical 1.

- 3. Set the Configuration Register Alternate Map bit (bit 7) to:

- a) logical 0 to load the primary Map Register set.

- b) logical 1 to load the Alternate Map Register set.

- 4. Put the upper four bits of the Map Register index number into the Map High Address Register. This register must be set to 0000 for 20-bit address systems and need not be changed once initially loaded (see page 3-20 for 24-bit addressing).

- Put the lower six bits of the Map Register index number into the Map Low Address Register. Typically, the lowest index number will be entered and will then be incremented by software for each successive Map Register number.

- 6. Write the data to the Map Register (bit 8 = logical 1 to enable the Map Register, bits 7-0 = page number).

- 7. When all 64 (or 1,024) Map Registers have been loaded, reset the Configuration Register Map Write Enable bit (bit 2) to logical 0 to protect the registers from further changes.

- 8. Disable Absolute Addressing by setting Configuration Register bit 1 to logical 1.

- 9. Set the Configuration Register Alternate Map Register bit (bit 7) to:

- a) logical 0 to access the Primary Map Register set.

- b) logical 1 to access the Alternate Map Register set.

- 10. Normally, the Configuration Register RAM Write Enable bit (bit 3) will be set to logical 0 at this time.

- 11. Enable the board by setting the Configuration Register Map Enable bit (bit 0) to logical 1.

#### **Absolute Address Mode**

For ease of start-up in simple systems, the ZT 8825 can be configured to come up at power-on or reset time in an "absolute address mode." To enable absolute address mode:

- 1. Install Jumper W1.

- 2. Set Configuration Register bit 1 to logical 0.

- 3. Set Configuration Register bit 3 to logical 1.

The board behaves in this mode as though its memory is a linear block starting at address 0 and continuing to the upper limit of memory on the board.

This is useful for small systems where the ZT 8825 is the only RAM board or in systems where it is used for RAM disks and for lower memory. Only one ZT 8825 in a system can use absolute address mode.

The ZT 8825 cannot be used in absolute address mode in DOS systems because the ZT 8825 powers up with its RAM write protected.

Non-DOS systems with boot ROMs can disable ZT 8825 write protection while executing custom code. To do this, the ROM code must output 08h to I/O location base+3 (default EE68h).

Absolute address mode can be turned off in software by setting the Configuration Register bit 1 to logical 1 after programming the Map Registers as described above. It may be permanently disabled by removing Jumper W1.

## **EXTENDED MEMORY MODE**

The ZT 8825 can be used as normal memory anywhere in the 16 Mbyte address space by using 24-bit addressing. Memory is mapped in 16 Kbyte blocks, allowing it to be distributed over 16 Mbytes of address space.

## **Setting the 24-bit Map Register**

To set the Map Register for 24-bit addressing, after installing Jumpers W2-W5:

- 1. Disable the board by setting the Configuration Register Map Enable bit (bit 0) to logical 0.

- 2. Set the Configuration Register Map Write Enable bit (bit 2) to logical 1.

- 3. Set the Configuration Register Alternate Map bit (bit 7) to:

- a) logical 0 to load the primary Map Register set.

- b) logical 1 to load the Alternate Map Register set.

- 4. Set the Map High Register to 0000.

- 5. Set the Map Low Register to 000000.

- 6. Allow software to increment the Map Low Register index number by one for each successive Map Register number until the Map Low Register has been filled (64 increments).

- 7. Allow software to increment the Map High Register by one and then reset the Map Low Register to 000000.

- 8. Repeat steps 6 and 7 until both low and high registers have filled (16 times).

- 9. When all 1,024 Map Registers have been loaded, reset the Configuration Register Map Write Enable bit (bit 2) to logical 0 to protect the map data.

- 10. Set the Configuration Register Alternate Map Register bit (bit 7) to:

- a) logical 0 to access the Primary Map Register set.

- b) logical 1 to access the Alternate Map Register set.

- 11. Enable the board by setting Configuration Register bit 0 to logical 1.

## Chapter 4

# **APPLICATION EXAMPLES**

| Contents                                  | Page |

|-------------------------------------------|------|

| OVERVIEW                                  | 4-1  |

| INITIALIZING ZT 8825 AS CONTINUOUS MEMORY | 4-1  |

| Assembly Language Setup                   |      |

| Microsoft C Setup                         |      |

| EXAMPLE PROGRAMS USING EMS                |      |

| Example 1                                 | 4-7  |

| Example 2                                 | 4-12 |

| Example 3                                 |      |

| Example 4                                 | 4-23 |

# **OVERVIEW**

This chapter includes specific examples of the ZT 8825 in operation.

# INITIALIZING ZT 8825 AS CONTINUOUS MEMORY

The examples in this section demonstrate initialization of the ZT 8825 as a linear memory board.

## **Assembly Language Setup**

The following example is written in Assembly language. The ZT 8825 is loaded with 8 x 32K RAM. The 20-bit memory address starts at 8000:000 (segment 8000 or 512K).

```

; MEMORY EQUATES

START_MAP EQU 20H

SIZE EQU 16

;=SEGMENT 8000H SHIFTED RIGHT 10 TIMES

;16 X 16K = 256K

;8825 I/O ADDRESSES

LO_ADDR EQU 0EE68H

HI_ADDR

EQU

HI_ADDR EQU 0EE69H

DATA EQU 0EE6AH

CONFIG EQU 0EE6BH

; CONFIG REGISTER EQUATES

ALT_REG EQU 80H

VALID

EQU

80H

; VALID PAGE

EN_MAP_WR EQU 0EH

EN_BOARD EQU OBH

MOV DX, CONFIG

MOV

AL, EN_MAP_WR

; ENABLE WRITES TO MAP REGISTER

OUT

DX, AL

DX, HI_ADDR

MOV

MOM

AL, 0

DX, AL

AL, 0

CX, 64

AH, 0

;SELECT LOWER 64 MAP REGISTERS

OUT

MOV

;START AT REGISTER 0

MOV

;CLEAR ALL 64 MAP REGISTERS

MOV

;NOT VALID PAGE

CLEAR_LOOP:

MOV

DX, LO_ADDR

OUT

DX, AL

;SELECT NEXT MAP REGISTER

XCHG

AH, AL

DX, DATA

MOV

;CLEAR IT TO 0

OUT

DX, AL

XCHG AH, AL

INC

LOOP

CLEAR_LOOP

MOV

CX, SIZE

VOM

AL, START_MAP

MOV

AH, VALID

INIT_LOOP:

MOV DX, LO_ADDR

OUT

DX, AL

;SELECT WINDOW

MOV

DX, DATA

XCHG AH, AL

OUT

DX, AL

;ENABLE PAGE

XCHG AH, AL

INC

; INCREMENT WINDOW NUMBER

```

| INC   | AH        | ; INCREMENT PAGE NUMBER |

|-------|-----------|-------------------------|

| T.OOD | TNTT LOOP | : CFT.FCT NEYT DACE     |

MOV DX, CONFIG MOV AL, EN\_BOARD

OUT DX, AL ;TURN ON BOARD

#### **Microsoft C Setup**

```

/***********************

Ziatech 8825 Setup Utility

Copyright Ziatech Corp. 1988

^{\star} Setup is a simple configuration utility for the ZT 8825. Its

* only purpose is to allow you to map the ZT 8825 into a single

* contiguous memory space in an STD DOS system. It is implemen-

* ted using Microsoft C compiler Version 4.0. Any questions or

^{\star} comments should be directed to Ziatech Technical Support at

* (805) 541-0488.

#include <stdio.h>

"BETA v0.1"

#define VERSION

#define DEFAULT_IO_ADDR

0x0ee68

0x08000

#define DEFAULT_BASE_SEG

#define DEFAULT_PAGES

16

#define REG_LO_ADDR

Ω

#define REG_HI_ADDR

1

#define REG_DATA

#define REG_CONFIG

{\tt \#define\ CONFIG\_ENABLE\_MAPPING\ 0x01}

#define CONFIG_NO_ABS_ADDR

#define CONFIG_MAP_WRITE_ENABLE 0x04

#define CONFIG_RAM_WRITE_ENABLE 0x08

#define CONFIG SELECT ALT REGS 0x80

#define MAP_PAGE_ENABLE

0x80

char Copyright[50] =

"Copyright Ziatech Corp. 1988 All Rights Reserved\0";

main(argc,argv)

int argc;

char *argv[];

unsigned int ioaddr, baseaddr, pages;

printf("\n Ziatech ZT8825 Setup Utility  \s\n\s\n\n",

VERSION, Copyright);

if (argc != 4) {

getargs(&ioaddr, &baseaddr, &pages);

} else {

sscanf(argv[1],"%x",&ioaddr);

sscanf(argv[2], "%x", &baseaddr);

sscanf(argv[3], "%d", &pages);

```

```

printf("\nMapping ZT8825 at %x to %x:0 for %d pages (%dK).\n",

ioaddr,baseaddr,pages,(pages*16));

clear(ioaddr);

setup(ioaddr,baseaddr,pages);

***********************

clear: zeros all mapping registers on the specified ZT8825.

clear(ioaddr)

unsigned int ioaddr;

int i;

outp( (ioaddr + REG_CONFIG), CONFIG_MAP_WRITE_ENABLE);

outp( (ioaddr+REG_HI_ADDR), 0);

for (i=0; i<64; i++) {

outp( (ioaddr+REG_LO_ADDR), i);

outp( (ioaddr+REG_DATA), 0);

setup: maps the ZT8825 as per the requested configuration.

setup(ioaddr,baseaddr,pages)

unsigned int ioaddr, baseaddr, pages;

int basemap, i;

basemap = (baseaddr >> 10);

outp( (ioaddr + REG_CONFIG), CONFIG_MAP_WRITE_ENABLE );

outp( (ioaddr + REG_HI_ADDR), 0);

for (i = 0; i < pages; i++) {

outp( (ioaddr + REG_LO_ADDR), (basemap + i) );

outp( (ioaddr + REG_DATA), (MAP_PAGE_ENABLE + i) );

outp( (ioaddr + REG_CONFIG), (CONFIG_ENABLE_MAPPING |

CONFIG_NO_ABS_ADDR | CONFIG_RAM_WRITE_ENABLE) );

getargs(ioaddr, baseaddr, pages)

unsigned int *ioaddr, *baseaddr, *pages;

char ch,Input[30];

printf("\nI/O address of 8825 (in hex) [%x] : ",DEFAULT_IO_ADDR);

gets(Input);

if (strlen(Input) == 0) {

*ioaddr = DEFAULT_IO_ADDR;

} else {

sscanf(Input, "%x", ioaddr);

```

## **EXAMPLE PROGRAMS USING EMS**

These example programs have been included in this manual as a convenient quick reference for EMS users. Further information on EMS can be found in the ZT 8825 Software Support Package manual.

#### Example 1

The following program was written using the Microsoft C compiler Version 3.0. EMM function calls are made with the int86 function found in the dos.h library. Use the following command line to create an executable program:

#### msc program,,program;

```

#include <dos.h>

#define GET_UNALLOC_PAGE_COUNT 0x42 /* EMM get unallocated */

/* page count */

/* function number */

#define ALLOCATE_PAGES 0x43 /* EMM allocate pages */

/* function number */

0x44 /* EMM map pages

/* function numbe

#define MAP PAGES

/* function number */

#define DEALLOCATE_PAGES 0x45 /* EMM deallocate pages */

/* function number */

8  /* Length of a device

/* name string */

#define DEVICE_NAME_LENGTH 8

1

#define TRUE

#define FALSE

union REGS input_regs, output_regs;

struct SREGS segment_regs;

int pf_addr;

/* ----- */

/* Routine to convert a segment:offset pair to a far ptr.

char *build_ptr(segment,offset)

unsigned int segment; unsigned int offset;

```

```

{

ptr = (char *) (((unsigned long)segment << 16) + offset);</pre>

return (ptr);

/* Function which determines whether EMM device driver is installed. */

char emm_installed()

{

char *EMM_device_name = "EMMXXXXX0";

char *int_67_device_name_ptr;

/* AH = DOS get interrupt vector function.

input_regs.h.ah = 0x35;

/* AL = EMM interrupt vector number.

input_regs.h.al = EMM_INT;

intdosx (&input_regs, &output_regs, &segment_regs);

/* ----- */

/* Upon return ES:OAh points to location where device name */

/* should be.

int_67_device_name_ptr = build_ptr(segment_regs.es,0xA);

/* Compare memory with EMM device name.

if (memcmp(EMM_device_name, int_67_device_name_ptr,

DEVICE_NAME_LENGTH) == 0)

return (TRUE);

return (FALSE);

/* ----- */

/\star Function which determines if there are enough unallocated expanded \star/

char enough_unallocated_pages (pages_needed)

int pages_needed;

input_regs.h.ah = GET_UNALLOCATED_PAGE_COUNT;

int86 (EMM_INT, &input_regs, &output_regs);

if (output_regs.h.ah! = 0 || pages_needed > output_regs.x.bx)

return (FALSE);

else

return (TRUE);

```

```

/* Routine which allocates expanded memory pages and passes

/* back to the main EMM handle.

/* ----- */

char allocate_expanded_memory_pages (pages_needed, emm_handle_ptr)

pages_needed;

unsigned int *emm_handle_ptr;

{

input_regs.h.ah = ALLOCATE_PAGES;

input_regs.x.bx = pages_needed;

int86 (EMM_INT, &input_regs, &output_regs);

if (output_regs.h.ah ==0) {

*emm_handle_ptr = output_regs.x.dx;

return (TRUE);

else

return (FALSE);

}

/* Routine to map a logical page to a physical page.

char map_expanded_memory_pages (emm_handle, physical_page, logical_page)

unsigned int emm_handle;

int physical_page;

logical_page;

int

{

input_regs.h.ah = MAP_PAGES;

input_regs.h.al = physical_page;

input_regs.x.bx = logical_page;

input_regs.x.dx = emm_handle;

int86 (EMM_INT, &input_regs, &output_regs);

if (output_regs.h.ah == 0)

return (TRUE);

return (FALSE);

char get_page_frame_address (pf_ptr)

char **pf_ptr;

{

input_regs.h.ah = GET_PAGE_FRAME;

int86 (EMM_INT, &input_regs, &output_regs);

return (FALSE);

else

*pf_ptr = build_ptr(output_regs.x.bx,0);

return (TRUE);

```

```

/* Routine to release all expanded memory pages allocated by an EMM */

/* handle.

/* ------ */

char deallocate_expanded_memory_pages (emm_handle)

unsigned int

{

input_regs.h.ah = DEALLOCATE_PAGES;

input_regs.x.dx = emm_handle;

int86 (EMM_INT, &input_regs, &output_regs);

if (output_regs.h.ah == 0)

return (TRUE);

return (FALSE);

}

main() {

unsigned int emm_handle;

char *pf_addr;

int pages_needed;

int physical_page;

int logical_page;

int

index;

/* Determine if EMM is installed.

/* ----- */

if (!emm_installed())

exit (1);

/* Determine if enough expanded memory pages exist for */

/* application.

pages_needed = 1;

if (!enough_unallocated_pages (pages_needed))

exit (1);

/* Allocate expanded memory pages.

if (!allocate_expanded_memory_pages (pages_needed, &emm_handle))

exit (1);

/* ----- */

/* Map in the required pages.

physical_page = 0;

logical_page = 0;

if (!map_expanded_memory_pages (emm_handle, physical_page,

logical_page))

exit (1);

```

#### Example 2

The following program is an example of how to use the basic EMM functions with Turbo Pascal. The program performs the following steps:

- 1. Makes sure that the EMM has been installed

- 2. Displays the EMM version number

- 3. Determines whether there are enough pages of memory for the test program

- 4. Displays the total number of pages present in the system and the number of pages available for use

- 5. Requests the desired number of pages from the EMM

- 6. Maps a logical page into one of the logical memory page frames

- 7. Displays the base address of this EMM memory page frame

- 8. Performs a simple read/write test on the EMM memory

- 9. Returns the EMM memory back to the EMM

- 10. Exits

All the calls are structured for the result or error code of the EMM function performed to be returned as an integer. If the error code is not zero, an error has occurred. A simple error procedure is then called and the program terminates.

```

Type

ST3 = string[3];

ST80 = string[80];

ST5 = string[5];

Registers = record

case integer of

1: (AX,BX,CX,DX,BP,SI,DI,DS,ES,FLAGS: Integer);

2: (AL,AH,BL,BH,CL,DL,DH : Byte);

end;

Const

EMM_INT

= $67;

= $21;

DOS Int

GET_PAGE_FRAME

= $41;

```

```

GET_UNALLOCATED_PAGE_COUNT= $42;

ALLOCATE_PAGES = $43;

MAP_PAGES = $44;

= $45;

= $46;

DEALLOCATE_PAGES

GET VERSION

STATUS_OK

= 0;

{ Assume the application needs one EMM page.

APPLICATION_PAGE_COUNT = 1;

Var

Regs: Registers;

Emm_Handle,

Page_Frame_Base_Address,

Pages_Needed,

Physical_Page,

Logical_Page,

Offset,

Error_Code,

Pages_EMM_Available,

Total_EMM_Pages,

Available_EMM_Pages: Integer;

Version_Number,

Pages_Number_String: ST3;

Verify: Boolean;

The function Hex_String converts an integer into a four

{ character hexadecimal number (string) with leading zeros.

Function Hex_String (Number: Integer): ST5;

Function Hex_Char (Number: Integer): Char;

Begin

If Number < 10 then

Hex_Char := Char (Number+48)

Hex_Char := Char (Number+55);

end; { Function Hex_Char}

Var

S: ST5;

Begin

S := '';

S := Hex_Char ((Number shr 1) div 2048);

Number:=(((Number shr 1) mod 2048) shl 1)+(Number and 1);

S := S+Hex_Char (Number div 256);

Number := Number mod 256;

S := S+Hex_Char (Number div 16);

Number := Number mod 16;

S := S+Hex_Char (Number);

Hex_String := S+'h';

end; { Function Hex_String}

```

```

The function Emm_Installed checks to see if the

EMM is loaded in memory. It does this by looking

for the string 'EMMXXXXO', which should be located

at 10 bytes from the beginning of the code segment

the EMM interrupt, 67h, points to.

Function Emm_Installed: Boolean;

Var

Emm Device Name

: string[8];

Int_67_Device_Name : string[8];

Position

: integer;

Regs

: registers;

Begin

Int_67_Device_Name := '';

Emm_Device_Name := 'EMMXXXX0';

with regs do

Begin

Get the code segment interrupt 67h points to

the EMM interrupt by using DOS function 35h.

{ (get interrupt vector)

AH := $35;

AL := EMM_INT;

Intr (DOS_int,Regs);

The ES pseudo-register contains the segment

address pointed to by interrupt 67h. Create an

eight character string from the eight successive

bytes at address ES:$000A (10 bytes from ES).

_____

For Position := 0 to 7 do

Int_67_Device_Name :=

Int_67_Device_Name+Chr (mem[ES:Position+$0A]);

Emm Installed := True;

If the string is the EMM manager signature,

'EMMXXXX0', then EMM is installed and ready

for use. If not, then EMM is not present.

If Int_67_Device_Name <> Emm_Device_Name

then Emm_Installed := False;

end; { with Regs do}

end; { Function Emm_Installed }

This function returns the total number of EMM pages

present in the system, and the number of {\tt EMM} pages

that are available.

Function EMM_Pages_Available

(Var Total_EMM_Pages, Pages_Available: Integer): Integer;

Var

Regs: Registers;

Begin

with Regs do

Begin

```

```

Get the number of currently unallocated pages and

the total number of pages in the system from EMM.

Load pseudo-registers prior to invoking EMM.

AH = get unallocated page count function.

AH := Get_Unallocated_Page_Count;

intr (EMM_INT, Regs);

Unload the pseudo-registers after invoking EMM.

BX = currently unallocated pages

{\tt DX} = total pages in the system

AH = status

Pages_Available := BX;

Total_EMM_Pages := DX;

EMM_Pages_Available := AH;

end;

end; { EMM_Pages_Available }

This function requests the specified number of pages

from the EMM.

Function Allocate_Expanded_Memory_Pages

(Pages_Needed: Integer; Var Handle: Integer): Integer;

Regs: Registers;

Begin

with Regs do

Begin

Allocate the specified number of pages from EMM.

Load pseudo-registers prior to invoking EMM.

AH = allocate pages function.

BX = number of pages to allocate.

AH := Allocate_Pages;

BX := Pages_Needed;

intr (EMM_INT,Regs);

Unload the pseudo-registers after invoking EMM.

DX = EMM handle

AH = status

Handle := DX;

Allocate_Expanded_Memory_Pages := AH;

end;

end; { Function Allocate_Expanded_Memory_Pages}

This function maps a logical page allocated by the

Allocate_Expanded_Memory_Pages function into one of

the four physical pages.

Function Map_Expanded_Memory_Pages

(Handle, Logical_Page, Physical_Page: Integer): Integer;

```

```

Var

Regs: Registers;

Begin

with Regs do

Begin

Map a logical page at physical page 0.

Load pseudo-registers prior to invoking EMM.

AH = map page function

DX = handle

BX = logical page number

AL = physical page number

AH := Map_Pages;

DX := Handle;

BX := Logical_Page;

AL := Physical_Page;

Intr (EMM_INT, Regs);