## Synergy Microsystems VGM5 **VME Module**

In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/72809-2

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

- Critical and expedited services

- In stock / Ready-to-ship

- We buy your excess, underutilized, and idle equipment

- Full-service, independent repair center

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

VMEbus Dual G3/G4

PowerPC Single Board Computer

User Guide

Revision 5.1

October 12, 2004

Curtiss-Wright Controls Embedded Computing 9605 Scranton Road, Suite 700 San Diego, CA 92121-1773 (858) 452-0020 • (858) 452-0060 (FAX) www.cwembedded.com

#### VGM5 User Guide

Copyright © 2004 Synergy Microsystems, Inc.

This manual is copyrighted under Title 17 US Code of the United States Copyright Law. All rights are reserved by Synergy Microsystems, Inc. This document may not, in whole or in part, be copied, photocopied, reproduced, translated, scanned, or reduced to any electronic medium or readable form without the express written consent of Synergy Microsystems, Inc.

This document contains material of a proprietary nature to Synergy Microsystems, Inc. All manufacturing, use, and sales rights pertaining to this product are expressly reserved. Distribution of this material does not convey any license or title under any patent or copyright. It is submitted in strict confidence to provide technical information for purchasers of this product or for those considering the purchase of the product. Each recipient, by accepting this document, agrees that its contents will not be disclosed in any manner or any person except to serve this purpose.

Synergy Microsystems, Inc. reserves the right to make changes to the specifications and contents in this document without prior notification. If in doubt, users are urged to consult Synergy to determine whether any such changes have been made.

Synergy products are not intended for use in life support systems or other applications where a failure of the product could result in injury or loss of life. Customers using or selling this product in systems or applications serving such a function do so at their own risk and agree to fully indemnify Synergy Microsystems, Inc. for any and all damages arising from improper use.

This product and associated manuals are sold "AS IS" without implied warranty as to their merchantability or fitness for any particular use. In no event shall Synergy Microsystems, Inc. or anyone involved in the creation, production, or delivery of this product be liable for any direct, incidental, or consequential damages, such as, but not limited to, loss of anticipated profits, benefits, use, or to data resulting from the use of this product or associated manuals or arising out of any breach of warranty. In states that do not allow the exclusion or limitation of direct, incidental, or consequential damages, this limitation may not apply.

Synergy<sup>™</sup>, VGM5<sup>™</sup>, VGM Series<sup>™</sup>, V30 Series<sup>™</sup>, V20 Series<sup>™</sup>, EZ-bus<sup>™</sup> and P0•PCI<sup>™</sup> are trademarks of Synergy Microsystems, Inc. VMEbus Technology logo is a trademark of VITA.

Synergy wishes to acknowledge that the names of products and companies mentioned in this manual are trademarks of their respective manufacturers.

PRINTED IN THE USA

# Table of contents

| Manual revision summary                                    | i   |

|------------------------------------------------------------|-----|

| Section 1. Overview                                        | 1   |

| VGM5 features                                              |     |

| VGM5 physical configuration                                |     |

| Functional block diagram                                   |     |

| Feature summary                                            |     |

| Manual conventions                                         |     |

| Typographical conventions                                  |     |

| Notes chapter                                              |     |

| Bit numbering conventions                                  |     |

| Web page address                                           |     |

| Manual comments                                            |     |

| Section 2. Getting Started                                 |     |

| Minimum system requirements                                |     |

| Front panel                                                |     |

| 8-bit user switch                                          |     |

| Toggle switches                                            |     |

| LEDs                                                       |     |

| Lamp test feature                                          |     |

| Setting up the VGM5 hardware                               |     |

| Default configurationInstalling jumpers                    | 23  |

| Setting the slot number manually                           | 23  |

| Installing a monitor PROM                                  | 20  |

| Installing the RGSx memory module                          |     |

| Installing/upgrading the RGSx memory module                |     |

| Memory module securing screws                              | 38  |

| Installing PMC cards                                       | 39  |

| VGM5 PMC connectors                                        |     |

| Adding additional PMC cards with the PEX3 expansion board  |     |

| Installing a PMC card                                      |     |

| Installing the P0 overlay                                  |     |

| Installation notes                                         |     |

| Bus grant signal problems with Hybricon VME64x backplanes  | 5 · |

| Section 3. Basic Bus Descriptions                          | 53  |

| PowerPC bus                                                |     |

| VME64 bus                                                  | 57  |

| Overview                                                   |     |

| VGM5 VMEbus implementation                                 |     |

| PCI bus                                                    |     |

| Introduction                                               |     |

| PMC cards                                                  |     |

| PCI implementation details                                 |     |

| PCI configuration                                          |     |

| Endian issues, byte swapping<br>PCI standards organization |     |

| SCSI bus                                                   |     |

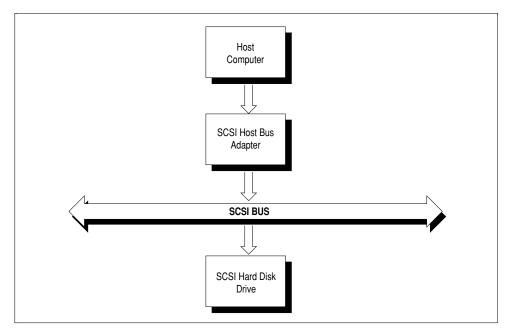

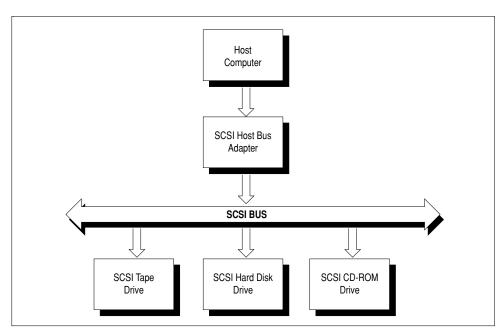

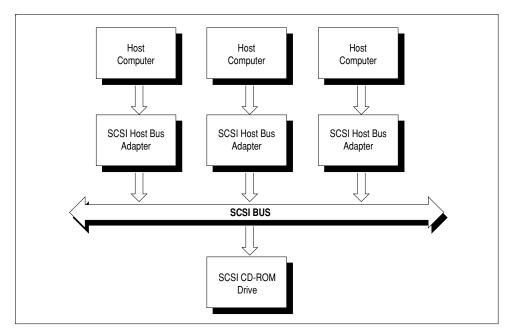

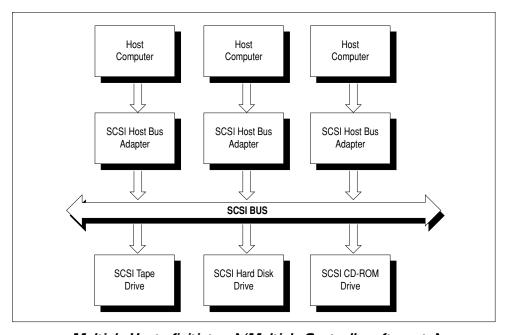

| Overview                                                   |     |

| History                                                    |     |

| SCSI specifications and publications                       |     |

| Device connections                                         |     |

| Electrical connections                                     |     |

| Physical topology                                          |     |

| Pus terminations                                           | 7   |

| Bus communication control                            |    |

|------------------------------------------------------|----|

| Data transfer options                                | 75 |

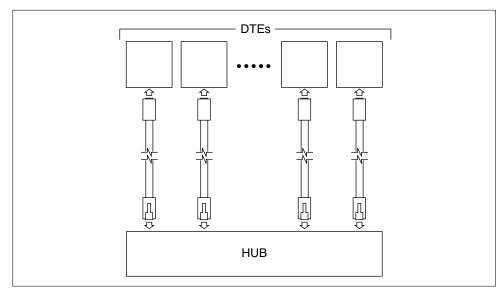

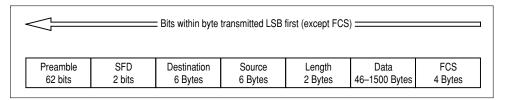

| Fast Ethernet interface                              |    |

| Ethernet network connections                         |    |

| Data transmission                                    |    |

| Ethernet ID or physical address                      |    |

| Avoiding bus contention — CSMA/CD                    |    |

| Interchange signals                                  |    |

| LED indicators                                       | 82 |

| Section 4. Programming the PowerPC                   | 83 |

| PowerPC architecture                                 |    |

| Introduction                                         |    |

| Further information                                  |    |

| Architecture models                                  |    |

| Register set                                         |    |

| Instruction set overview                             |    |

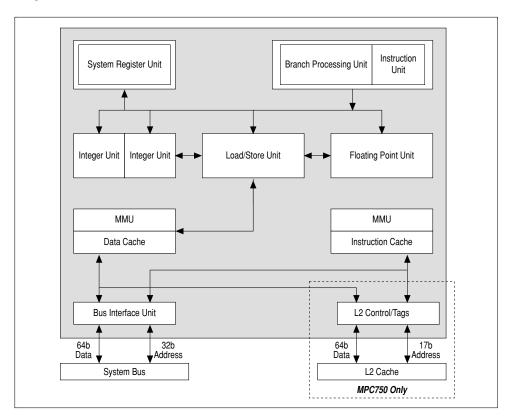

| PowerPC 750 G3 processor                             |    |

| Superscalar microprocessor                           |    |

| Power management                                     |    |

| Cache and MMU support                                |    |

| Bus interface                                        |    |

| MPC750-specific registers                            |    |

| PowerPC G4 processor                                 |    |

| Summary of differences, 750 vs. 7400 Processor       | 9  |

| 7410 G4 Processor                                    |    |

| MPC106 PCI bridge/memory controller                  |    |

| General description                                  |    |

| PowerPC processor interface                          |    |

| Secondary (L2) cache interface                       |    |

| Memory interface                                     |    |

| PCI bus interface                                    |    |

| Power management functions                           |    |

| Programming the MPC106                               |    |

| MPC106 registers                                     |    |

| Address maps                                         |    |

| Configuration registers                              |    |

| Power management configuration registers             |    |

| Error handling registers                             |    |

| Memory interface registers                           |    |

| Processor interface configuration registers          |    |

| Alternate OS-Visible parameters registers            |    |

| Emulation support configuration registers            |    |

| External configuration registers                     |    |

| Programming notes, MPC106                            |    |

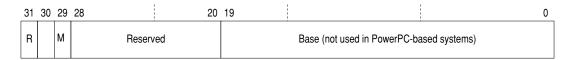

| Setting PCI device base address                      |    |

| Write posting to ROM Space                           |    |

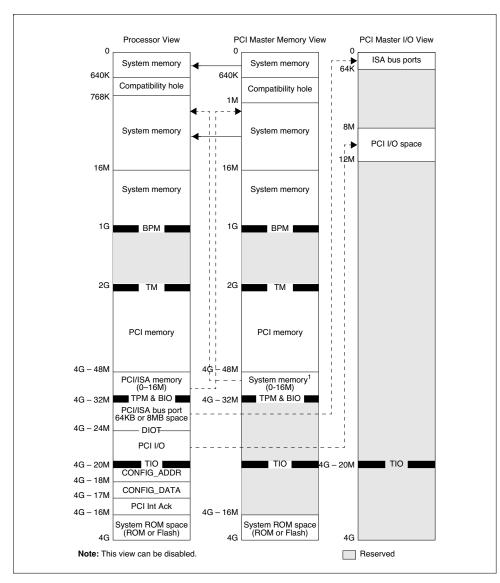

| Address map                                          |    |

| CHRP address map                                     |    |

| PCI configuration and address                        |    |

| VGM5 address map                                     |    |

| Address space descriptions                           |    |

| Processor Memory Space                               |    |

| PCI Memory space                                     |    |

| PCI I/O space                                        |    |

| VME master space                                     |    |

| VME slave space                                      |    |

| Onboard registers                                    |    |

| Board information registers                          |    |

| Board type and revision register, 0xFFEF_FE00 (RO)   |    |

| Special mod and ECO level register, 0xFFEF_FE08 (RO) |    |

| Board family and feature register, 0xFFEF_FE10 (RO)                                                                 |       |

|---------------------------------------------------------------------------------------------------------------------|-------|

| L2 cache register, 0xFFEF_FE30 (RO)                                                                                 |       |

| Memory register, 0xFFEF_FE38 (RO)                                                                                   | 126   |

| Secondary PCI Slot register, 0xFFEF_FE48 (RO)                                                                       |       |

| VME64 Slot register, 0xFFEF_FF30 (RO)                                                                               |       |

| Status registers<br>Eight-bit user switch register, 0xFFEF_FD00 (RO)                                                |       |

| Board status register, 0xFFEF_FE18 (RO)                                                                             |       |

| CPU status register, 0xFFEF_FE20 (RO)                                                                               | 129   |

| Control/Mode registers                                                                                              |       |

| CPU Timebase register, 0xFFEF_FE28 (RW)                                                                             | 131   |

| Flash ROM register, 0xFFEF_FE40 (RW)                                                                                | 132   |

| Flash Window register, 0xFFEF_FE50 (WO)                                                                             | 133   |

| PO•PCI™ interrupt assert/pending register, 0xFFEF_FE68 (RW)                                                         |       |

| User LED registers, 0xFFEF_FE80, 0xFFEF_FE88, 0xFFEF_FE90, 0xFFEF_FE98, 0                                           |       |

| Oxffef_fea8, Oxffef_feb0, Oxffef_feb8 (RW)                                                                          | 134   |

| PowerPC-VME64 Slave Mask register, 0xFFEF_FF00 (RW)                                                                 |       |

| PowerPC-VME64 Slave Address register, 0xFFEF_FF08 (RW)                                                              |       |

| VME64 Broadcast Slave Address register, 0xFFEF_FF10 (RW)<br>PowerPC-VME64 Master Address register, 0xFFEF_FF18 (RW) |       |

| PowerPC-VME64 Mode register, 0xFFEF_FF20 (RW)                                                                       |       |

| PowerPC-VME64 RMW register, 0xFFEF_FF28 (RW)                                                                        |       |

| VME64 SysReset register, 0xFFEF_FF38 (RW)                                                                           |       |

| Backside L2 cache controller                                                                                        |       |

| How to use the backside L2 cache                                                                                    |       |

| Mailboxes                                                                                                           |       |

| Programming notes, Mailbox                                                                                          | 143   |

| Handling mailbox writes                                                                                             | 143   |

| Asynchronous serial interface                                                                                       | 145   |

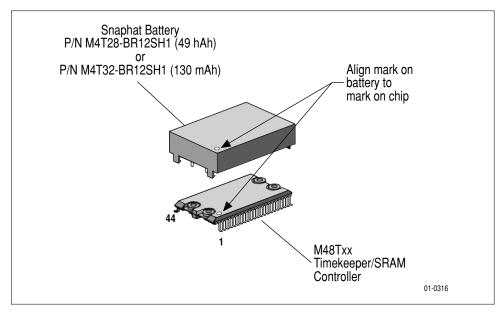

| Clock calendar                                                                                                      |       |

| Non-volatile 128K x 8 SRAM                                                                                          |       |

| NVRAM space allocationReplacing the battery                                                                         |       |

| Boot Flash ROM/DIP EPROM                                                                                            |       |

| Boot options                                                                                                        |       |

| DIP EPROM use                                                                                                       |       |

| EPROM type configuration                                                                                            |       |

| Boot Flash use                                                                                                      |       |

| Block organization                                                                                                  |       |

| Writing and erasing                                                                                                 |       |

| Additional write protection of Boot Flash                                                                           | 164   |

| Additional Flash memory information                                                                                 | 164   |

| User Flash memory                                                                                                   |       |

| Introduction                                                                                                        |       |

| Block organizationBank selection                                                                                    |       |

| Writing and erasing                                                                                                 |       |

| Additional information                                                                                              |       |

|                                                                                                                     |       |

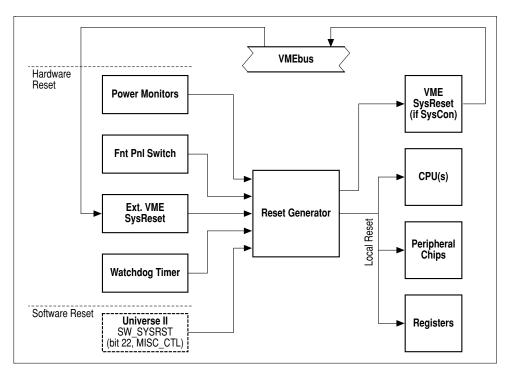

| Section 5. Reset                                                                                                    | 169   |

| Reset information                                                                                                   | 171   |

| General description                                                                                                 | 171   |

| PCI reset                                                                                                           | 172   |

| Hard reset sources                                                                                                  |       |

| Power monitor                                                                                                       |       |

| Front panel reset switch                                                                                            |       |

| External VME SysReset                                                                                               |       |

| Watchdog timer                                                                                                      |       |

| Universe II software reset                                                                                          |       |

| JUIL 16356                                                                                                          | 1 / 4 |

| Section 6. MPIC Interrupt Controller               | 177 |

|----------------------------------------------------|-----|

| General description                                |     |

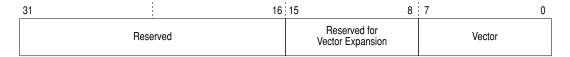

| MPIC registers                                     |     |

| MPIC base address                                  |     |

| Global registers                                   |     |

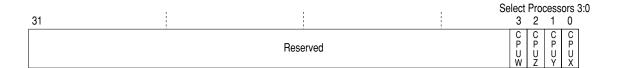

| Feature reporting register                         |     |

| Global configuration registers                     |     |

| Vendor identification register                     |     |

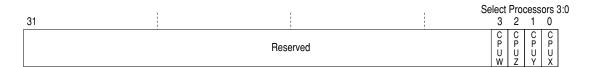

| Processor init register                            |     |

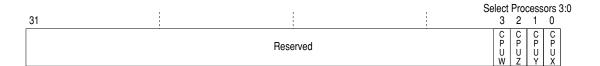

| IPI vector/priority registers                      |     |

| Spurious vector register                           |     |

| Global Timer registers                             |     |

| Interrupt source configuration registers           |     |

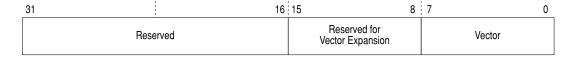

| Interrupt Source Vector/Priority registers         | 190 |

| Interrupt Source Destination register              | 191 |

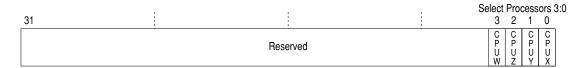

| Per processor registers                            |     |

| Interprocessor Interrupt Dispatch registers        |     |

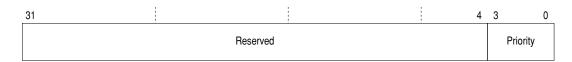

| Current Task Priority register                     |     |

| Interrupt Acknowledge registers                    |     |

| End-of-interrupt registers                         |     |

| Watchdog timer                                     |     |

| Example watchdog timer code                        |     |

|                                                    |     |

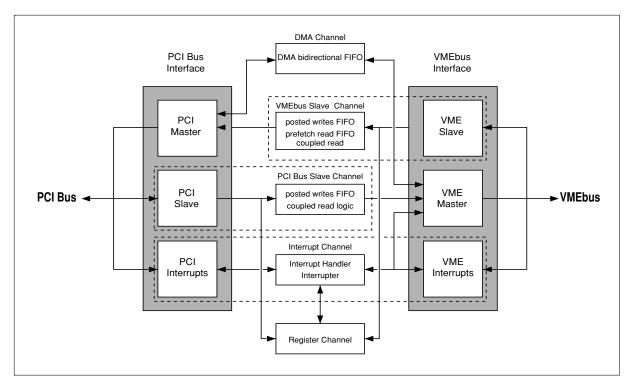

| Section 7. PCI-VME64 Bridge (Universe II)          | 199 |

| Introduction to Universe II                        | 201 |

| Universe II register reference                     |     |

| Overview                                           |     |

| Register access                                    | 205 |

| Universe II base address                           |     |

| Register map                                       |     |

| Improving VME performance                          |     |

| Universe II specific (U2SPEC) register             |     |

| U2SPEC adjustable VME timing parameters            |     |

| U2SPEC register bit assignments                    |     |

| BLT speedup bit                                    |     |

| PowerPC-VME64 Mode register, FFEF_FF20 (RW)        |     |

| Programming notes, Universe II                     |     |

| Writing to non-existent VME locations              |     |

| Slave image programming                            | 215 |

|                                                    |     |

| Section 8. Direct PowerPC-to-VME64 Interface       | 217 |

| Using the VGM5 direct VME interface                | 219 |

| Master direct VME interface                        |     |

| Direct VMEbus address map                          |     |

| Master Mode                                        |     |

| Master Address Translation                         |     |

| Programming notes, Master direct VME interface     | 225 |

| Improving performance, master direct VME interface | 225 |

| Slave direct VME interface                         |     |

| Read-Modify-Write (RMW)                            |     |

| General description                                |     |

| Slave RMW operations                               |     |

| Master RMW operations                              |     |

| Section 9. SCSI/Ethernet Controller       | 237 |

|-------------------------------------------|-----|

| General description                       | 239 |

| SYM53C885 registers                       |     |

| SCSI registers                            | 242 |

| PCI configuration                         | 242 |

| Operating registers                       | 243 |

| Ethernet registers                        | 245 |

| PCI configuration                         | 245 |

| Operating registers                       | 246 |

| Programming notes, SYM53C885              |     |

| SCSI prematurely surrendering PCI bus     | 249 |

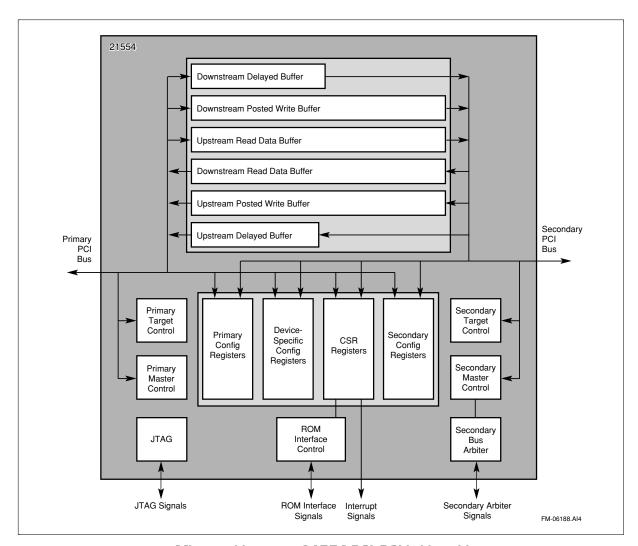

| Section 10. PCI-PCI Bridge Interface      | 251 |

| General description                       | 253 |

| Registers                                 | 255 |

| Configuration                             | 257 |

| Introduction                              | 257 |

| PCI configuration                         |     |

| P0 • PCI™ configuration                   |     |

| Software support, P0 • PCI™               | 259 |

| Section 11. Warranties & Service          | 261 |

| Warranty terms & options                  | 263 |

| Customer service                          |     |

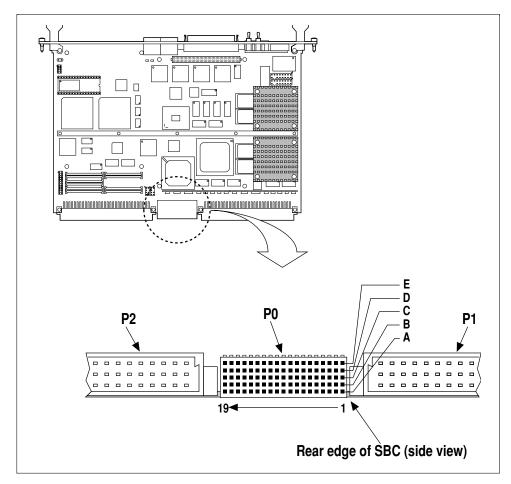

| Appendix A, Connectors & Cables           | 267 |

| VMEbus connectors (P1 & P2)               |     |

| PMC connectors (P11-P15)                  |     |

| P0 • PCI <sup>TM</sup> bus connector (P0) |     |

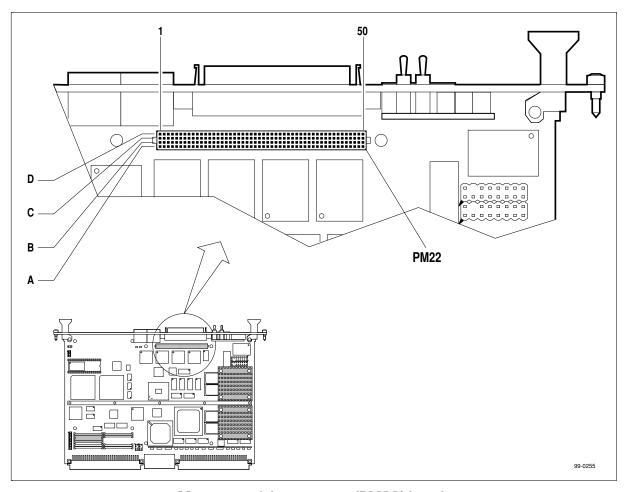

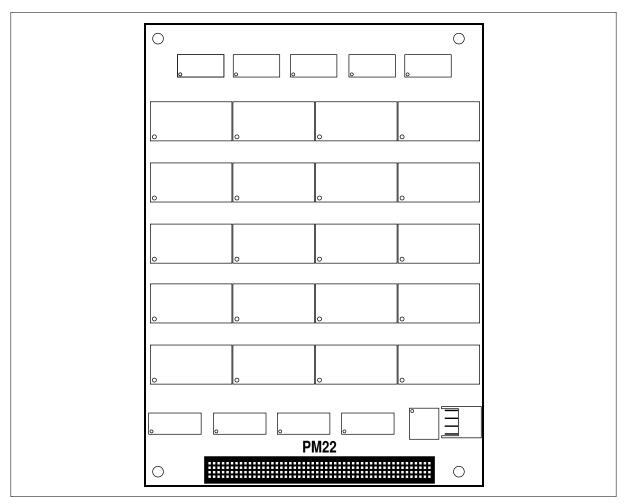

| Memory module connector (PM22)            |     |

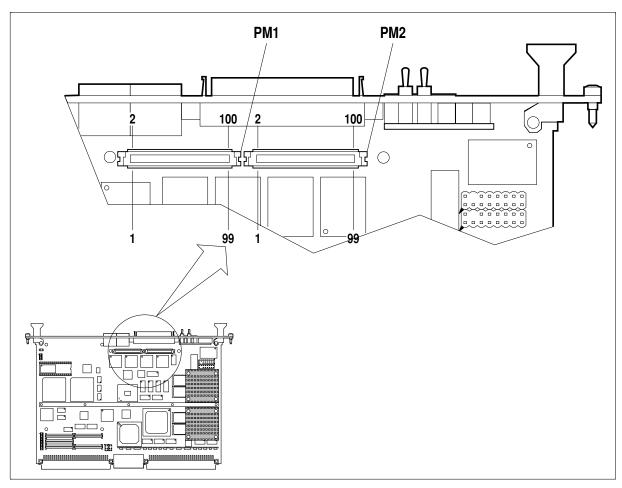

| Memory module connectors (PM1 & PM2)      |     |

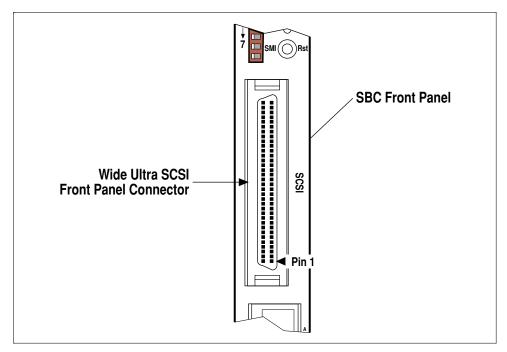

| Wide Ultra SCSI connector (P264/P262)     |     |

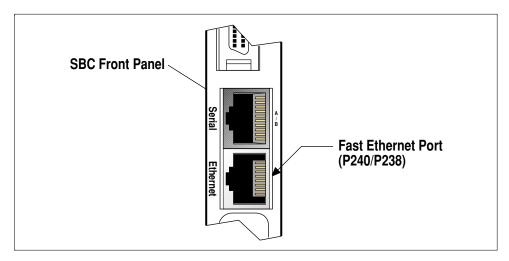

| Fast Ethernet connector (P240/P238)       |     |

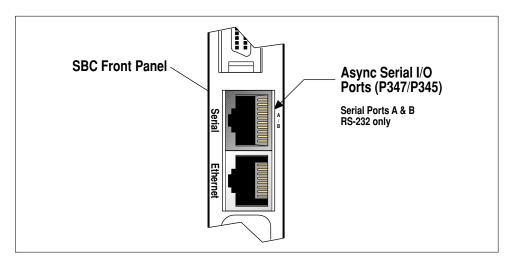

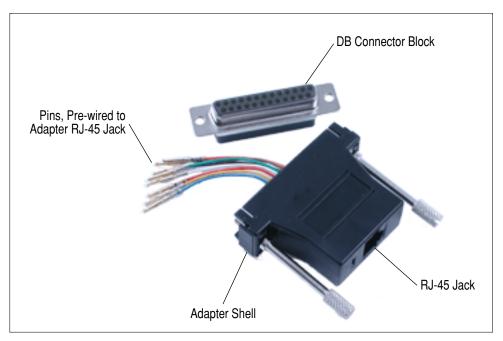

| Asynchronous serial connector (P347/P345) |     |

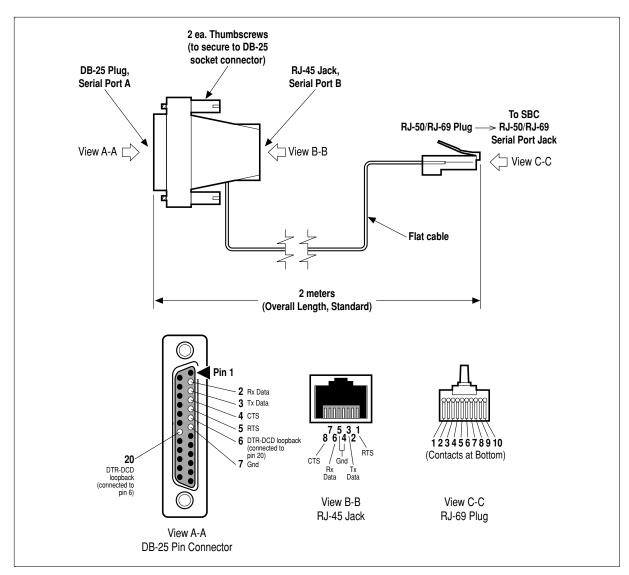

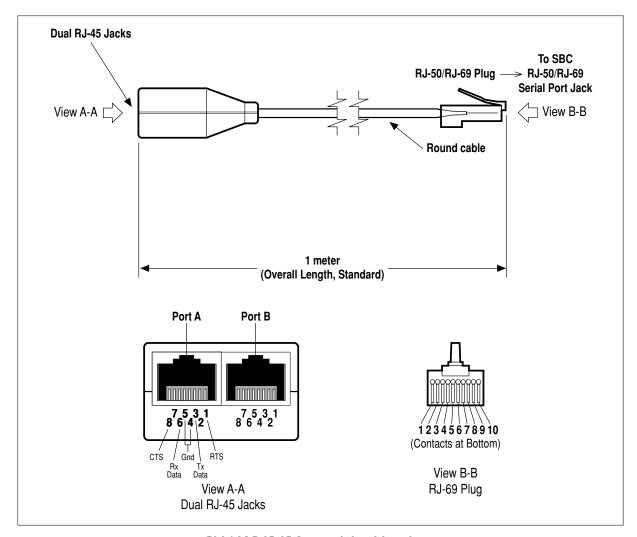

| Serial I/O cabling options                |     |

| Using only Serial Port A                  |     |

| Appendix B, Specifications                | 305 |

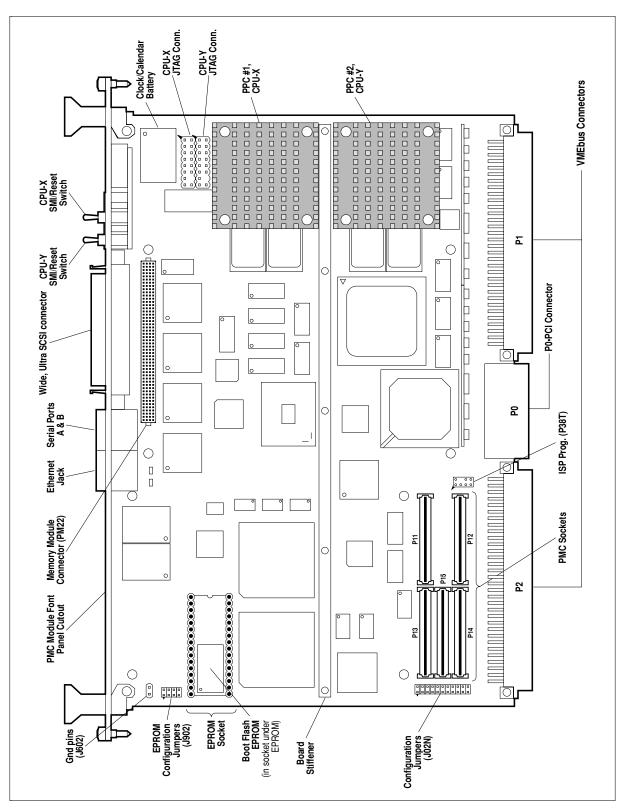

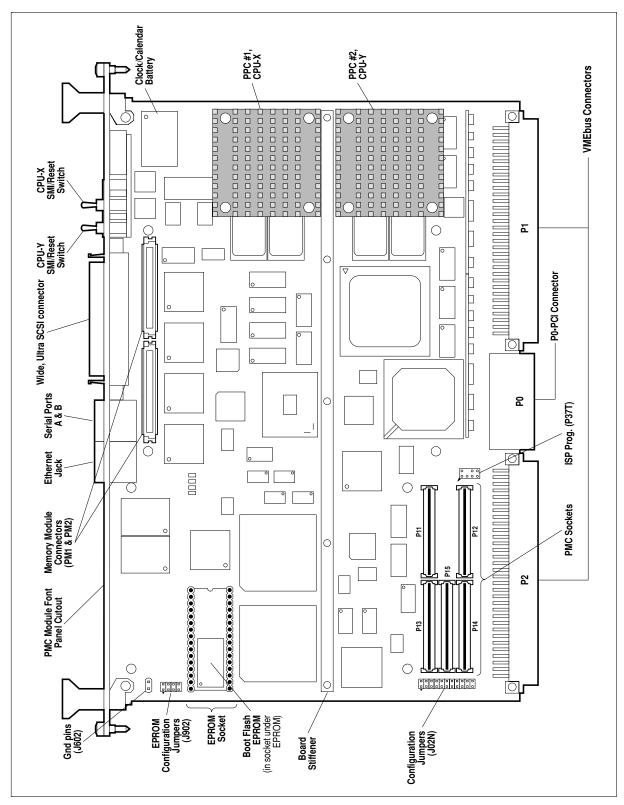

| Board layout                              |     |

| Appendix C. Roard revision summary        | 311 |

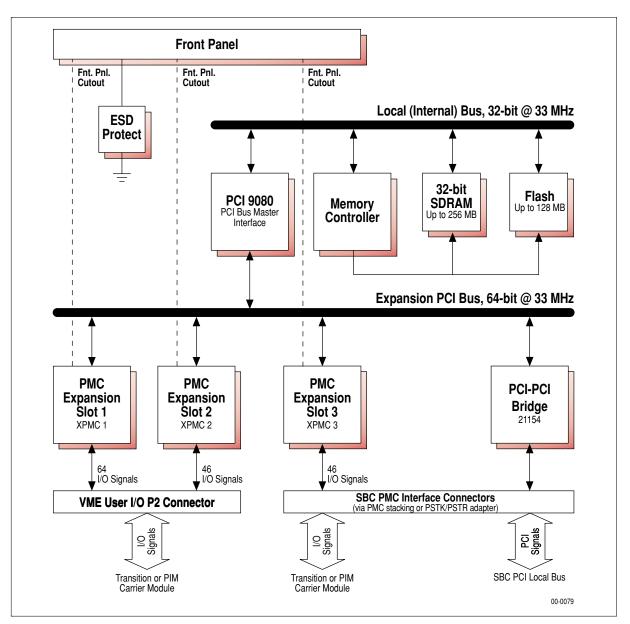

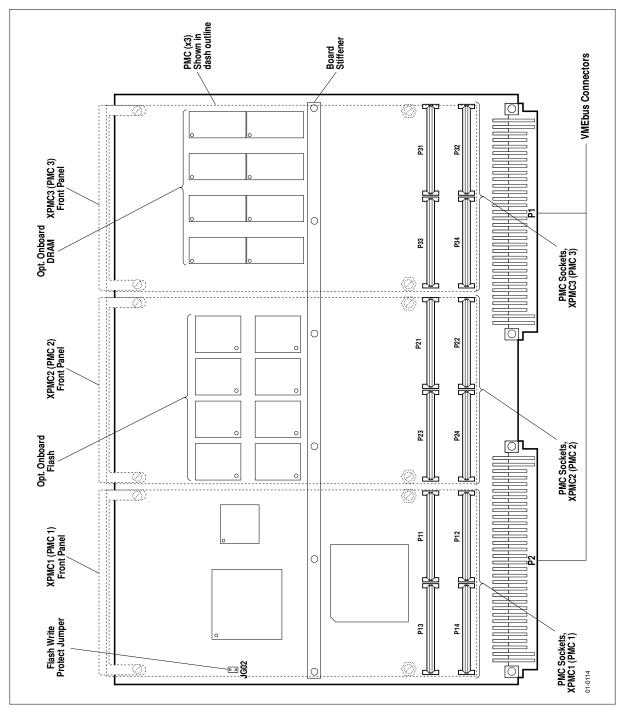

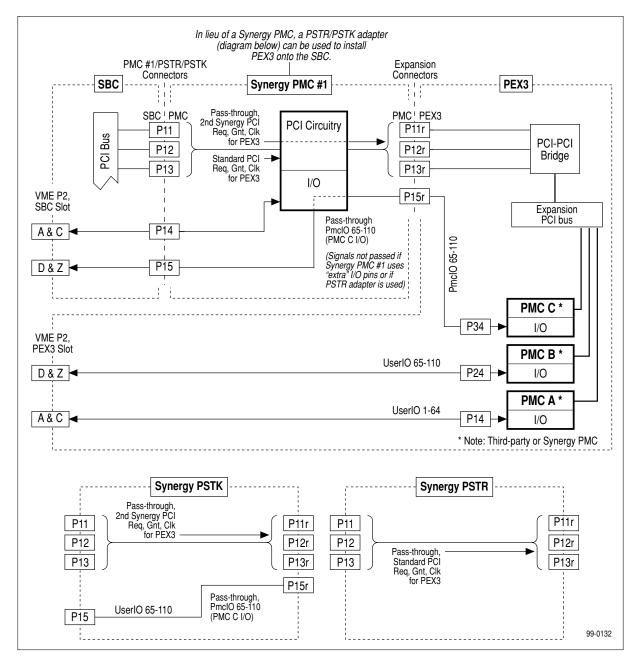

| ndix D, PEX3 PMC expansion option                 | 313 |

|---------------------------------------------------|-----|

| Features                                          |     |

| Block diagram                                     |     |

| Board layout                                      |     |

| Front panel layout                                |     |

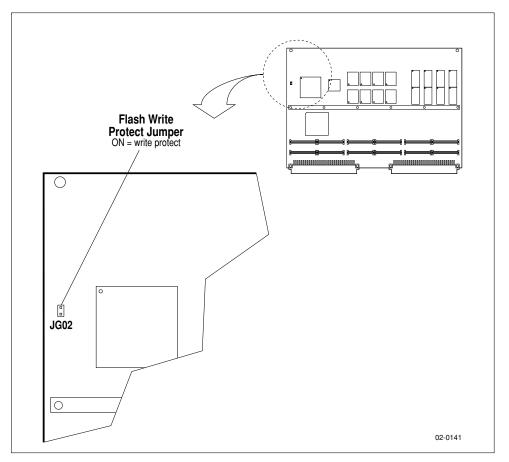

| Configuration                                     |     |

| Flash write protect                               |     |

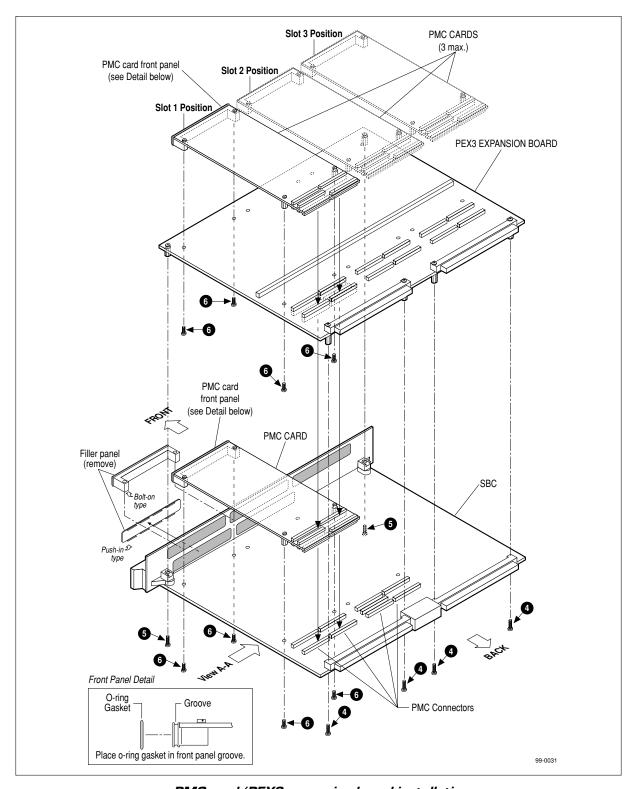

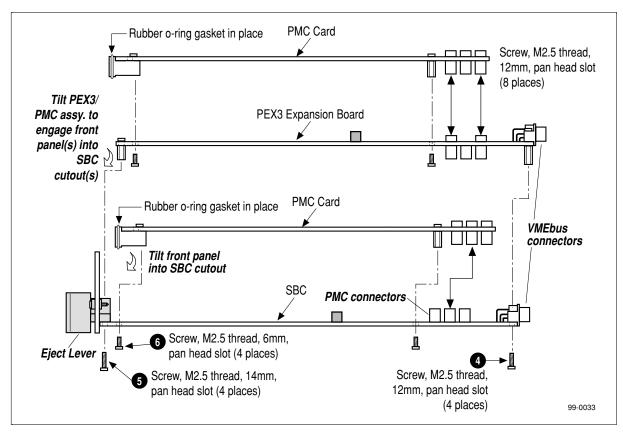

| Installation                                      |     |

| Installing PMC cards                              |     |

| PSTK/PSTR adapters                                | 318 |

| PMC stacking and P2 I/O routing                   |     |

| PMC P2 I/O restriction                            |     |

| Operation                                         |     |

| Address map                                       | 324 |

| PMC PCI interrupts                                |     |

| PCI Type 0 configuration and address              |     |

| PCI configuration                                 |     |

| PCI 9080 basic set up                             |     |

| Registers                                         |     |

| Board type register, 0xC000_0000 (RO)             | 328 |

| Revision and ECO level register, 0xC000_0004 (RO) |     |

| Flash configuration register, 0xC000_0008 (RO)    |     |

| DRAM configuration register, 0xC000_000C (RO)     |     |

| Using PEX3 memory                                 |     |

| PEX3 connector pinouts                            |     |

| VMEbus connectors (P1 & P2)                       | 332 |

| PMC connectors                                    |     |

| ry                                                | 339 |

|                                                   | 349 |

# Manual revision summary

| Revision level | Revision date | Section          | Affected chapter/description                                                                                                                                             |  |

|----------------|---------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.0a           | 11/24/98      |                  | 1st preliminary release                                                                                                                                                  |  |

| 1.0b           | 5/20/99       |                  | 2nd preliminary release                                                                                                                                                  |  |

| 1.0c           | 10/15/99      |                  | pre-GA release                                                                                                                                                           |  |

| 1.0d           | 11/16/99      |                  | 2nd pre-GA release                                                                                                                                                       |  |

| 1.0            | 3/21/00       |                  | GA Release                                                                                                                                                               |  |

| 2.0            | 1/5/00        | All              | Cleaned up various items as required.                                                                                                                                    |  |

|                |               | Section 4        | Onboard registers/Added register for P0•PCI Interrupt.                                                                                                                   |  |

|                |               | Appendix C       | Added VGM5 Rev. G to revision summary.                                                                                                                                   |  |

| 3.0            | 4/27/01       | All              | Cleaned up various items as required.                                                                                                                                    |  |

|                |               | Section 2/App. B | Updated Power Specification.                                                                                                                                             |  |

|                |               | Section 7        | Added Slave image programming caveat.                                                                                                                                    |  |

|                |               | Appendix D       | Deleted P0•PCI references. Added PEX3 board layout drawing.                                                                                                              |  |

| 3.1            | 6/6/01        | All              | Cleaned up various items as required.                                                                                                                                    |  |

|                |               | Section 3        | Revised PCI bus discussion.                                                                                                                                              |  |

|                |               | Section 4        | Revised address map information.                                                                                                                                         |  |

| 3.2            | 10/5/01       | All              | Cleaned up various items as required.                                                                                                                                    |  |

|                |               | Section 2        | Installing the P0 overlay/Removed all references to passive overlay models.                                                                                              |  |

|                |               | Section 4        | Non-volatile 128K x 8 SRAM/Revised drawing to show how mark on battery and mark on chip are aligned. Pointed to board layout drawing in Appendix B for battery location. |  |

|                |               | Appendix C       | Removed VGM5 Rev. G from revision summary.                                                                                                                               |  |

|                |               | Appendix D       | Added clarification on PEX3 PCI interrupt scheme. Added Device Number info to PEX3 Type 0 configuration table.                                                           |  |

| 4.0            | 5/17/02       | All              | Cleaned up various items as required.                                                                                                                                    |  |

|                |               | Section 2        | Installing PMC cards/All PEX3 info moved to Appendix D.                                                                                                                  |  |

|                |               | Section 4        | <b>User Flash memory</b> /Corrected address ranges listed in User Flash bank selection table.                                                                            |  |

|                |               |                  | Mailbox/Added "Programming Notes" chapter describing recommended handling of mailbox writes.                                                                             |  |

|                |               | Appendix D       | Revised and cleaned up. Consolidated PEX3 info in this Appendix.                                                                                                         |  |

#### Manual revision summary

| Revision level | Revision date | Section    | Affected chapter/description                                                                                                                                                     |

|----------------|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.0            | 3/28/03       | All        | Cleaned up various items as required.                                                                                                                                            |

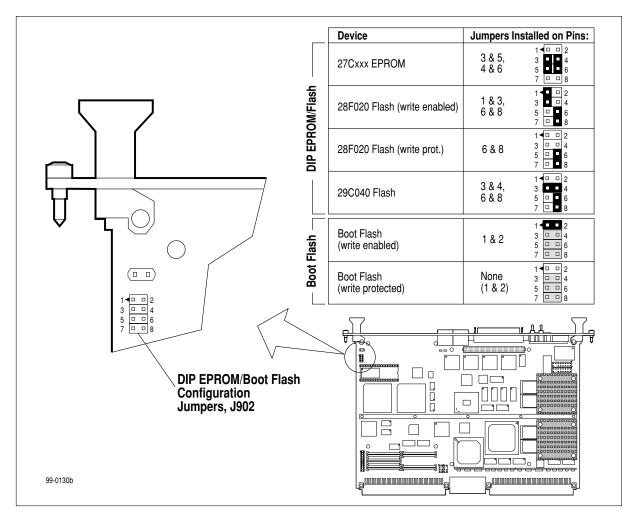

|                |               | Section 2  | Installing a monitor PROM/Revised J902 configuration jumper diagram to include Boot Flash Write Protect jumper function (see next item below).                                   |

|                |               | Section 4  | Boot Flash ROM/DIP EPROM/Added info describing J902 jumper settings for Boot Flash Write Enable/Disable (applicable only to boards that incorporate ECO specifying this change). |

|                |               | Appendix D | Revised PCI 9080 basic setup info. Added info on VxWorks BSP PEX3 driver. Put back PSTK stacking adapter info. Revised PMC connector pin assignments.                            |

| 5.1            | 10/12/04      | All        | Cleaned up various items as required.                                                                                                                                            |

# 1 Overview

This section introduces the VGM5 single board computer.

- VGM5 features

- Manual conventions

## VGM5 features

Synergy Microsystems' VGM Series is a family of 6U-sized VMEbus Single Board Computers (SBCs) designed from the ground up to run dual PowerPC microprocessors from IBM/Motorola. The VGM Series architecture is optimized for Real-time VME applications. All VGM Series SBCs are provided with a PCI bus mezzanine card slot for easy I/O expansion.

The VGM5 SBC is based on dual G3/G4 PowerPC microprocessors running at up to 400+ MHz. A performance-boosting backside L2 cache (1 MB for G3, 2 MB for G4) running at or near CPU core frequency is standard. An upgradeable DRAM module provides up to 512 MB of high performance SDRAM memory. SCSI, Ethernet, PMC slots, up to 64 MB 8-bit User Flash and 128 KB NVRAM give the VGM5 the flexibility to meet almost any requirement.

The VGM Series architecture supports VME Real-time multi-processor computing. Real-time VME support includes true VME Read-Modify-Write cycle support, a direct low latency PowerPC to VMEbus interface, hot-insertion/extraction support, and VME64x support with up to 110 pins of P2 I/O. Additional support is provided for Open Firmware and Symmetric Multiprocessor.

Multiprocessing support includes: dual CPUs with shared high bandwidth DRAM memory, a private mailbox for each CPU, and the OpenPIC<sup>TM</sup> interrupt controller.

VGM5 single board computer

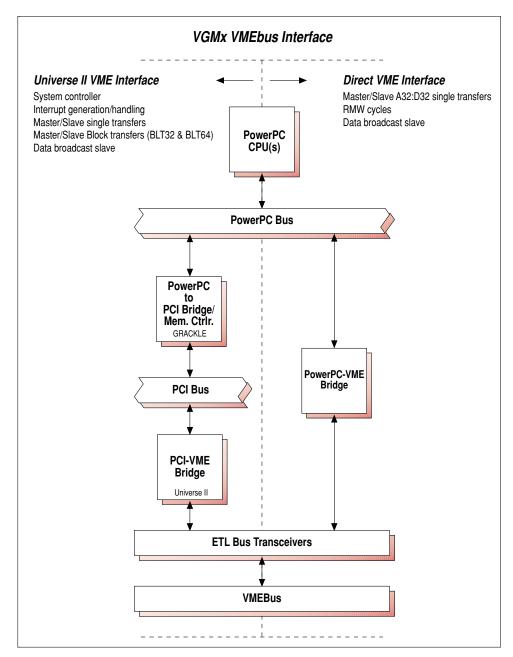

The VMEbus may be accessed either via the PowerPC to VME bridge (direct VME interface) or via the more traditional PCI to VME bridge (Universe II interface). Support for 64-bit VME (VME64) and autosystem controller is included. Special hardware supports the translation of PowerPC semaphore instructions to/from VME Read-Modify-Write cycles. This feature fixes a basic PowerPC to VME incompatibility, and allows multiprocessing with a mix of PowerPC and 68xxx based CPU boards.

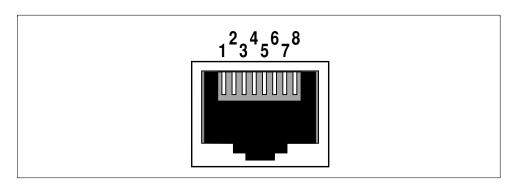

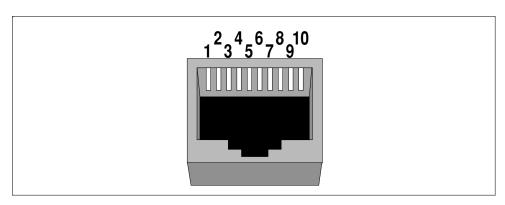

Onboard peripherals include an optional Wide Ultra SCSI (8/16-bit wide) interface, Fast Ethernet (10Base-T/100Base-TX) RJ-45 interface, two RS-232D serial ports, and a real-time clock/calendar with four digits for the year.

An industry-standard PMC slot provides optional daughterboard I/O connection to the PCI bus. The optional PEX3 PMC expansion board provides up to 3 additional PMC slots. The VGM5 also provides Synergy Microsystems' P0•PCI<sup>TM</sup> interface which is a secondary PCI bus accessed through the P0 connector. P0•PCI<sup>TM</sup> provides support for board-to-board communications and additional PCI I/O expansion.

A full line of system **monitor**, **kernel**, and **operating system** software/ firmware is also available from Synergy and leading developers.

## VGM5 physical configuration

VGM5 has onboard connectors for:

- Modular memory card

- PMC I/O card and/or PMC carrier board expansion via PEX3

- P0 PCI™ interface via P0 connector

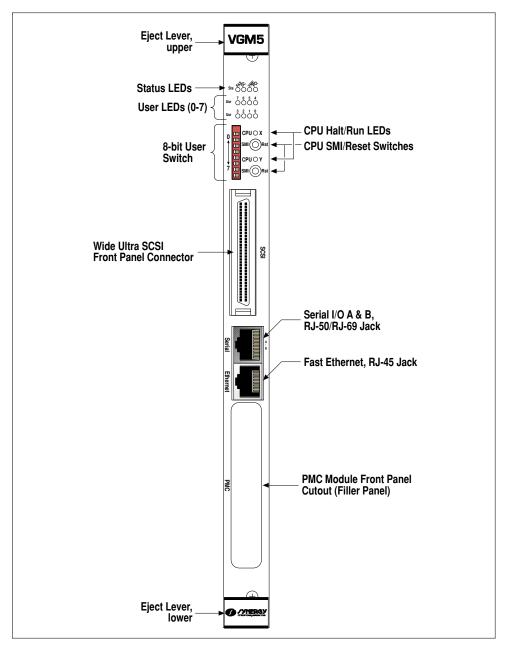

#### VGM5's front panel includes:

- Modular RJ-45 jack for Fast Ethernet

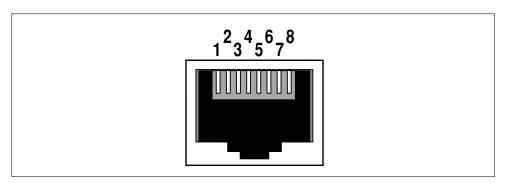

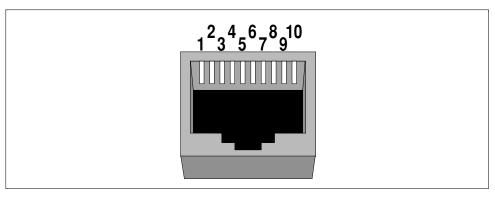

- Modular RJ-69 jack for dual serial ports (A and B)

- SMI & reset switch for each processor

- 8 user LEDs

- 8 status LEDs (count includes 2 ea. dual-color LEDs)

- Software-readable 8-bit DIP switch

- Optional 68-pin Wide Ultra SCSI connector (single-ended)

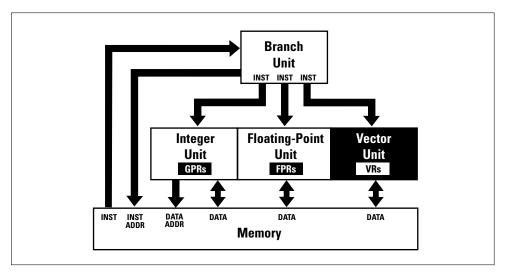

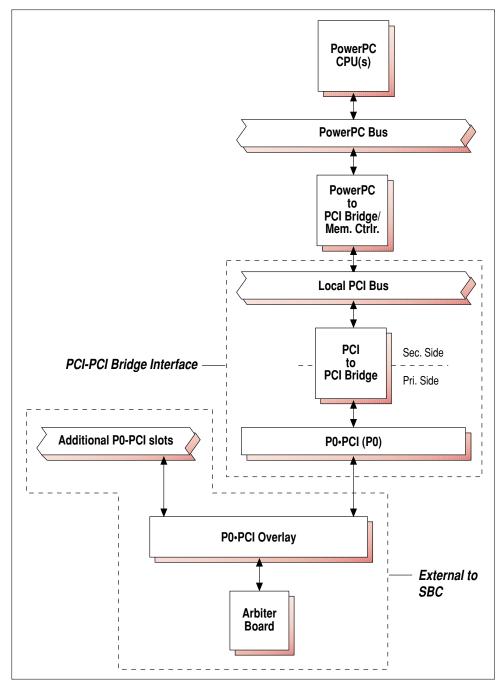

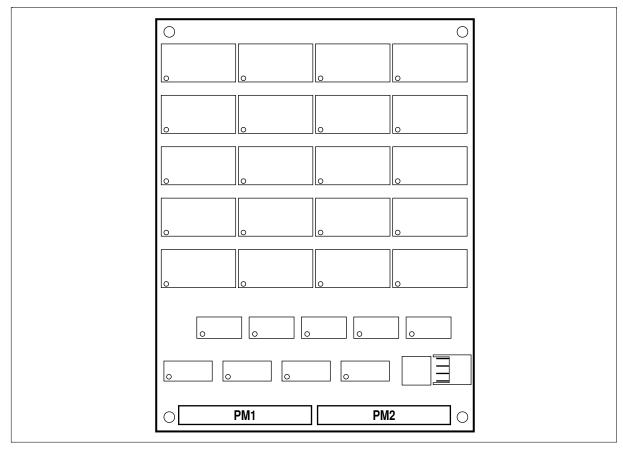

## Functional block diagram

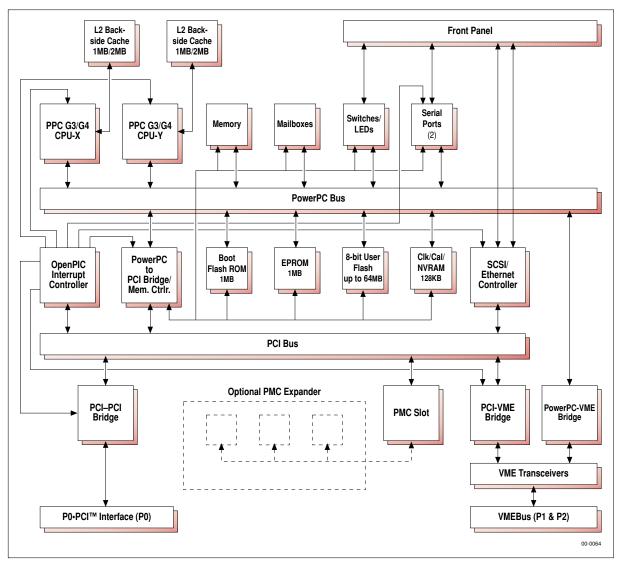

The figure below shows the functional block diagram for the VGM5 SBC.

VGM5 functional block diagram

#### Feature summary

VGM5 provides the following list of powerful features and functions:

- SMP compliant

- Synergy's PowerPC to VME bridge (direct VME interface) for low latency VME access and true VME Read-Modify-Write cycle support

- PCI to VME64 bridge (with auto-system controller) rated at 50 MB/sec

- OpenPIC<sup>™</sup> compliant any interrupt source can be routed to any CPU at any priority

- Four 32-bit counters can be read at any time as well as generate interrupts

- Single or dual G3/G4 PowerPC processor(s)

- Backside L2 cache, 1 MB (G3) or 2 MB (G4)

- 16-512 MB of high performance SDRAM supporting parity (32-512 MB, Rev. E or higher boards)

- 1 MB of system boot Flash loadable via a 32-pin JEDEC socket

- 4/8/16/32/64 MB 8-bit wide User Flash memory

- 128 KB of NVRAM

- Real time clock/calendar (4-digit year)

- RTC/NVRAM backed up by battery or capacitor option (for high altitude applications)

- Two RS-232D serial ports up to 115.2Kbps

- Two 8-bit CPU mailboxes

- PO•PCI™ sub-bus interface goes beyond VMEbus bandwidth limitations by providing an aggregate 266 MB/sec (theoretical maximum) transfer rate for up to 8 boards (4 pair) in a system

- Fast-20 SCSI (8/16-bit wide) option

- Fast Ethernet 10Base-T/100Base-TX

- PMC compliant slot

- Optional 6U expansion board provides up to 3 more PMC slots

- Geographical addressing support

- Twelve status LEDs (8 front panel, 4 on board), eight userprogrammable LEDs, an 8-bit software-readable switch, two CPU reset/interrupt switches

Section 1: Overview VGM5 features

## Manual conventions

#### Typographical conventions

This manual observes the following typographical conventions:

- The term **VGM Series** is used in conjunction with information that applies to **ALL** models of the board series. When differences among models exist, specific model numbers are used to describe any special features.

- 2 In diagrams and descriptions in this manual, signal names followed by a backslash (\) are active low.

#### Notes chapter

Within this manual, a **notes chapter** is provided in select sections. Some or all of the following notes chapters (or sections) may be found in this manual:

- Programming notes deals with programming issues

- Installation notes deals with installation issues

- Operating notes deals with operating/usage issues

Refer to this special information for any notes or caveats for the device or topic under discussion.

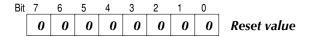

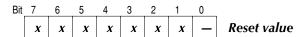

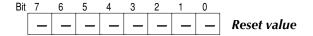

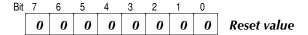

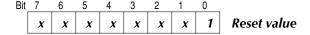

#### Bit numbering conventions

To avoid confusion, be aware that there are two bit numbering conventions.

The PowerPC architecture was invented by IBM, who number their bits with 0 on the left (most-significant bit or MSB) and 31 on the right (least-significant bit or LSB). This zero-on-the-left numbering convention is reflected in both IBM's and Motorola's PowerPC documentation.

PCI bus and VMEbus both number the bits with 0 on the right (LSB) and 31 on the left (MSB). This zero-on-the-right numbering convention is used in the bit descriptions contained in this manual.

#### Bit numbering conventions

| Binary bits of data (example) | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

|-------------------------------|---|---|---|---|---|---|---|---|

| Zero-on-the-right             | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Zero-on-the-left              | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

### Web page address

Note that any web page address (URL) is subject to change without notice. If the listed web page address in the manual doesn't work, do a site search or use your favorite search engine to find the information you need. Over time, some information may no longer be posted online. In this case, contact the manufacturer directly using the contact information usually provided in the home page.

#### Manual comments

Synergy invites your comments or corrections to this manual. Email comments/corrections to:

doc@synergymicro.com

# 2 Getting Started

This section provides configuration, setup and general information for the VGM5 SBC.

- Minimum system requirements

- Front panel

- Setting up the VGM5 hardware

- Installing a monitor PROM

- Installing the RGSx memory module

- Installing PMC cards

- Installing the P0 overlay

- Installation notes

# Minimum system requirements

The following system components are required to install and test VGM5 boards:

- **6**U VMEbus-compatible card cage with VME64x-compatible P1 and P2 backplanes installed (with P0 connector) A card cage with forced air cooling is required:

- minimum, 300 LFM (@sea level)

- recommended, 400 LFM (@sea level)

Note the recommended airflow rating in linear ft./min. This is the rate of air flowing over the component side of the SBC in its chassis and not the air moved through the chassis (CFM rating). LFM can be measured using a hand-held anemometer such as the Kestrel 1000 Pocket Wind Meter by Nielsen-Kellerman (www.nkelectronics.com).

VGM5 boards feature state-of-the-art, high-speed, transfers across the VMEbus that in some cases may approach the maximum VME specifications for transfer speeds. To support these transfers, the underlying connectors, circuitry, and printed circuit boards used in the VME card cage must be constructed of high-quality materials that are fully compliant with VME specifications.

For example, VME card cages containing 10-layer, PCB boards are normally required to support high-speed VME transfers. Older style card cages containing 6-layer boards may have some difficulty conducting these signals without generating excessive noise.

Pin row **B** of the P2 backplane is defined by VMEbus specifications and is bussed across the entire backplane. Pin rows **A** and **C** are user configured and, if connected at all, are normally connected to adjacent slots via wirewrap or special cables.

Because the P2 and P0 pinout may vary between backplanes or even slots in the same backplane, DO NOT INSTALL the VGM5 into a system slot whose backplane is not compatible with the VGM5's P2 and P0 pinout. Failure to observe this warning can cause the complete destruction of many on-board components and also voids the product warranty.

The VGM5 pinout meets standard VME specifications for row **B**, but rows **A** and **C** (and for 5-row boards, the majority of pins on row **D** and half the pins on row **Z**) will vary according to the PMC card installed. Synergy PMC card pinouts are shown in the associated manual. If no PMC card is present, P2 backplane rows **A** and **C** (and **D** & **Z**) are defined as **no-connects**.

For a complete list of the VGM5 P2 assignments, see the **P2 connector pinouts** table in Appendix A, page 271.

• Power supply \_ VGM5 boards (with 256 MB memory module and no PMC installed) typically require the following power supply voltage levels:

| Dual G3/466 MHz | +5.0V +/-5%, 5.8A typical @ 5.00V (29W).<br>±12V ±5%, 50 mA for -12V, 150 mA for +12V |

|-----------------|---------------------------------------------------------------------------------------|

|                 | 112V 13%, 30 IIIA 101 - 12V, 130 IIIA 101 + 12V                                       |

| Dual G4/466 MHz | +5.0V +/-5%, 7.8A typical @ 5.00V (39W).                                              |

|                 | ±12V ±5%, 50 mA for -12V, 150 mA for +12V                                             |

Ensure that the power supply is capable of meeting the above requirements plus the requirements of any additional boards in the system. An extra 20% margin of current capacity should be factored in for safety.

- One modular serial I/O cable or dual-port adapter cable (for Ser. Port B) The serial ports on VGM5 boards share a 10-pin modular RJ-69 connector. A regular 8-pin RJ-45 cable can be used to access Serial Port A. Dual-port adapter cables, available from Synergy, allow access to Serial Port B. Refer to Serial I/O cabling options in Appendix A, page 299, for more information.

- RS-232 compatible video display terminal or a PC with a COM port and terminal emulator software

Section 2: Getting Started

Minimum system requirements

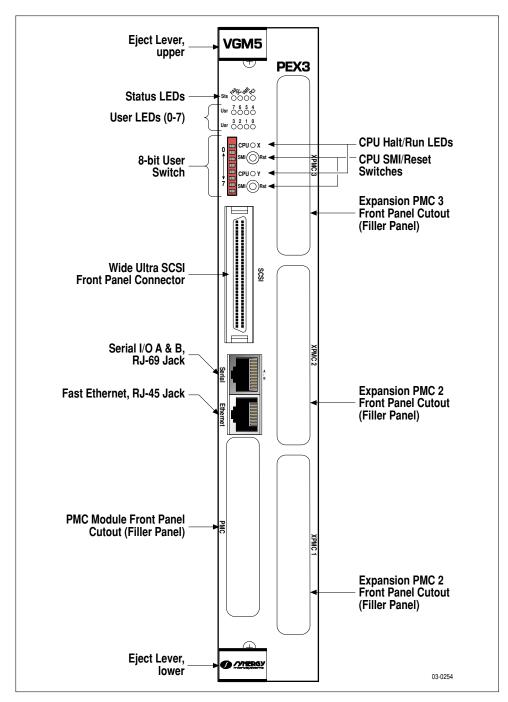

# Front panel

The drawing below shows the layout of the connectors, controls, and indicators on the VGM5 front panel.

VGM5 front panel

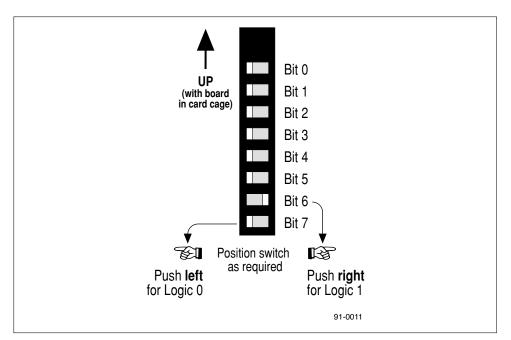

#### 8-bit user switch

The eight position switch on the VGM5 front panel provides an 8-bit software-readable switch.

Readable switches can be very useful in target applications where applications programs can read the switch to discover what their function should be, the nature of their peripherals, etc.

The CPU reads the switch setting by performing a byte-wide read from the 8-bit User Switch register at memory location **0xFFEF\_FD00**. The figure below shows the register bits corresponding to each of the eight switch positions.

8-bit user switch polarity

Numbering may appear on the switch component itself that conflicts with the numbering shown above. Ignore all numbering schemes except what is shown above and on the *Quick Reference Card*.

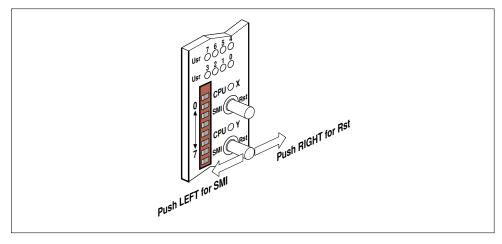

#### Toggle switches

VGM5 boards have a RESET and SMI switch for each CPU:

#### RESET

Asserts either a **CPU** or **board-level** RESET as described in the figure and text below:

Pushing a switch to the **right** asserts a CPU-level RESET to the corresponding CPU. The **CPU-X** (top) switch asserts a reset to the CPU on single CPU models and to **CPU-X** on the dual CPU models. The **CPU-Y** switch (bottom) asserts a reset to CPU-Y which has an effect only on dual CPU models.

Pushing **both** switches to the right at the same time asserts a board-level reset on all VGM Series models:

- Resets the CPU(s).

- Resets all on-board components that have such a function and clears all on-board control registers.

- Asserts a VME RESET if the board is serving as the System Controller.

**SMI**

Pushing a switch to the **left** asserts an SMI interrupt to the respective CPU.

Pushing the bottom switch to the left has **no effect** on single processor boards.

Close-up of RESET and SMI switches

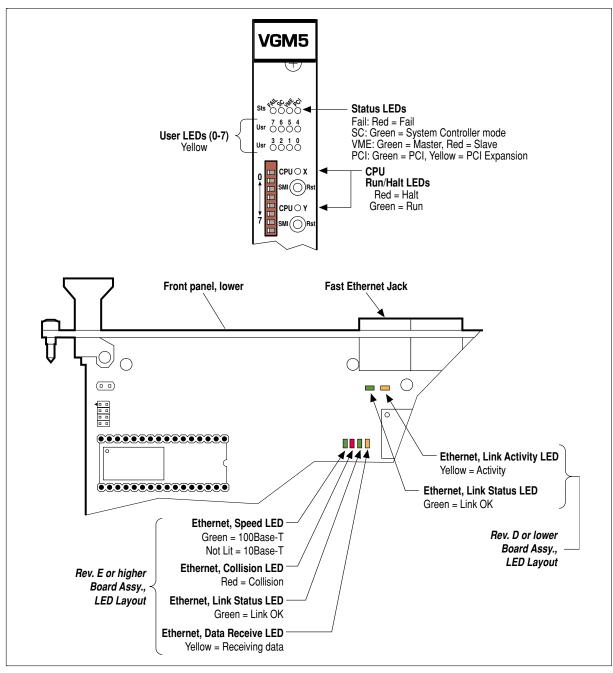

#### **LEDs**

Shown below are the VGM5 front panel and onboard LEDs which provide a quick indication of board activity. The following describes the LED functions.

VGM5 LEDs

#### The eight **User** LEDs indicate **application events**:

0 - 7

Software-programmable LEDs are controlled by the User LED registers. They indicate the current **operating mode** of the board as defined by the software currently running.

For more information on the registers that control these LEDs, refer to the *User LED registers* discussion in Section 4, page 134.

#### The **Status** LEDs indicate various status items:

| LED Label | Indication                                                                                                                                                                                 |                                                        |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|

| FAIL      | Red                                                                                                                                                                                        |                                                        |  |

|           | When on, indicates a condition that caused the CPU to reset (VMEbus SysRst\ line or the front panel RESET toggle).                                                                         |                                                        |  |

|           | During normal operation, the system b shortly after RESET.                                                                                                                                 | oot software clears this condition                     |  |

| SC        | Gr                                                                                                                                                                                         | een                                                    |  |

|           | When on, indicates System Controller                                                                                                                                                       | function assumed by board.                             |  |

| VME       | Dual-color LED, VMEbus Activity                                                                                                                                                            |                                                        |  |

|           | Green (VME Master)                                                                                                                                                                         | Red (VME Slave)                                        |  |

|           | Flickers green in response to VME Master activity. When the VMEbus interface is idle, the VME LED lights up green on the last release-on-request (ROR) VMEbus master to have used the bus. | Flickers red in response to VME Slave activity.        |  |

| PCI       | Dual-color LED, PCI Bus Activity                                                                                                                                                           |                                                        |  |

|           | Green (PCI Bus)                                                                                                                                                                            | Yellow (PCI Expansion)                                 |  |

|           | Flickers green in response to PCI bus activity.                                                                                                                                            | Flickers yellow in response to PCI expansion activity. |  |

The **CPU** LEDs indicate the **run status** of CPU-X and CPU-Y:

| LED Label | Indication                                                                                                                                                                                       |                                 |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|

| CPU X     | Dual-color LED, CPU-X Run Status                                                                                                                                                                 |                                 |  |  |

|           | Green (Run)                                                                                                                                                                                      | Red (Halt)                      |  |  |

|           | Flickers green in response to<br>PowerPC bus activity by CPU-X. If<br>not on, indicates CPU is not<br>executing bus cycles as it executes<br>instructions in cache or waits for an<br>interrupt. | Lights red when CPU has halted. |  |  |

| CPU Y     | Dual-color LED, CPU-Y Run Status (non-functional for single CPU boards)                                                                                                                          |                                 |  |  |

|           | Green (Run)                                                                                                                                                                                      | Red (Halt)                      |  |  |

|           | Flickers green in response to<br>PowerPC bus activity by CPU-Y. If<br>not on, indicates CPU is not<br>executing bus cycles as it executes<br>instructions in cache or waits for an<br>interrupt. | Lights red when CPU has halted. |  |  |

The two LEDs on the VGM5 motherboard, Revision D or lower, indicate Ethernet port status as follows:

| Green  | <b>Link OK</b> — lit when 10Base-T/100Base-TX cable is properly plugged into a functioning Ethernet network and onboard software has initialized the Ethernet interface.                                                                                                                                               |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Yellow | <b>Link Activity</b> — flickers whenever data is being received or transmitted. If the VGM5 is connected to a repeater-type hub instead of a switch-type hub, this LED may still flicker even when the VGM5 is not transferring data since packets sent over the network to other nodes will also be sent to the VGM5. |

For VGM5 board assembly Revision E or higher, four LEDs indicate Ethernet port status as follows:

**Green** Speed — lit when operating as 100Base-TX. LED is

OFF when operating as 10Base-T.

**Red** Collision – lit whenever the VGM5 produces a

collision (VGM5 transmits at same time as packet data is being received). When collisions occur, retries are automatically performed as part of the

Ethernet protocol.

**Green** Link OK – lit when 10Base-T/100Base-TX cable is

properly plugged into a functioning Ethernet network and onboard software has initialized the

Ethernet interface.

**Yellow** Receive Data – flickers whenever data is being

received. If the VGM5 is connected to a repeatertype hub instead of a switch-type hub, this LED may still flicker even when the VGM5 is not the intended destination since packets sent over the network to other nodes will also be sent to the

VGM5.

#### Lamp test feature

During board level reset, all LEDs are illuminated to provide a lamp test. You can confirm proper operation of the LED indicators as you do a board level reset by observing the LEDs and pushing **both** CPU toggle switches to the right. Hold switches in this position and wait 2 seconds for LED illumination.

Section 2: Getting Started

Front panel

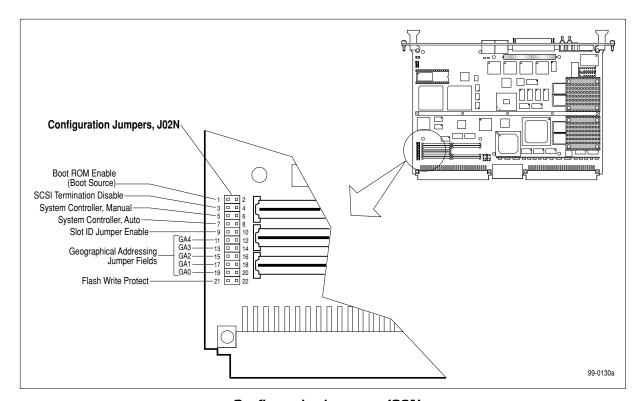

# Setting up the VGM5 hardware

This chapter describes the general hardware configuration of VGM5 boards. This configuration is done via jumpers on jumper block **J02N**.

Additional jumpers are provided on jumper block **J902** for EPROM configuration. Refer to the next chapter on *Installing a monitor PROM* (page 29) for details on EPROM configuration.

### Default configuration

The table shown below lists the default hardware configuration for the VGM5 board before the installation of any jumpers on **J02N**.

#### Default hardware conditions

| Jumpers (presumes no jumper installed)           | Default  |

|--------------------------------------------------|----------|

| J02N — Boot ROM Enable                           | Disabled |

| <ul><li>— SCSI Termination</li></ul>             | Enabled  |

| <ul> <li>Force VME System Controller</li> </ul>  | Disabled |

| <ul> <li>VME64 Auto System Controller</li> </ul> | Enabled  |

| <ul> <li>User Defined Slot Number</li> </ul>     | None     |

| <ul> <li>Flash Write Protect</li> </ul>          | Disabled |

#### Installing jumpers

No jumpers need to be set for most applications. However, the **J02N** user configuration jumpers let you change the default conditions listed in the table above if necessary. Note that the jumper shunts used are of the smaller 2 mm size and not the larger .100" size commonly found on older SBCs. The jumpers are summarized below.

- Verify that the board has a monitor EPROM and memory module installed.

- Verify/install shunt at J02N 1 & 2 to boot from DIP EPROM.

- Install a shunt at JO2N 3 & 4 to unterminate the SCSI bus.

- Install a shunt at J02N 5 & 6 to force VME System Controller.

- Install shunt at J02N 7 & 8 to disable Auto System Controller function.

- Install a shunt at J02N 9-20 for manual slot number configuration.

- Install a shunt at JO2N 21 & 22 for global Flash write protection.

The drawing below shows the location and pinout of jumper block **J02N**.

Configuration jumpers, JO2N

#### Jumper JO2N functions

| Jumper Pins | Function                                                                                                                                                                                                                                   | For more info, see Section,<br>Chapter                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 1 & 2       | Boot ROM Enable: When installed, the board will boot from the DIP EPROM instead of Boot Flash ROM.                                                                                                                                         | Section 4, Boot Flash ROM/DIP<br>EPROM (page 159)                                             |

| 3 & 4       | SCSI Termination Disable: When installed, the on-board SCSI termination is disabled                                                                                                                                                        | Section 3, SCSI bus (page74)                                                                  |

| 5 & 6       | VME System Controller: When installed, the on-board VME system controller function is active regardless of the VME64 auto-system controller function or the actual VME slot in which the board is installed.                               | Section 3, VME64 bus (page 58)                                                                |

| 7 & 8       | VME64 Auto-System Controller Disable:<br>When installed, the on-board auto-system<br>controller function is disabled.                                                                                                                      |                                                                                               |

| 9 & 10      | User Defined Slot Number: When installed, indicates that the slot number has been set by the user installing jumpers in positions 6-10. When not installed, the slot number is determined from the geographical address pins on VME64x P1. | See text below.                                                                               |

| 11 & 12     | Jumper for GA4, slot number                                                                                                                                                                                                                |                                                                                               |

| 13 & 14     | Jumper for GA3, slot number                                                                                                                                                                                                                | See Table Below                                                                               |

| 15 & 16     | Jumper for GA2, slot number                                                                                                                                                                                                                | For Jumper Settings                                                                           |

| 17 & 18     | Jumper for GA1, slot number                                                                                                                                                                                                                |                                                                                               |

| 19 & 20     | Jumper for GA0, slot number                                                                                                                                                                                                                |                                                                                               |

| 21 & 22     | Flash Write Protect: When installed, all<br>Flash (Boot Flash, User Flash, DIP Flash<br>EPROM) is protected from writes.                                                                                                                   | Section 4, Boot Flash ROM/DIP<br>EPROM (page 159); Section 4, User<br>Flash memory (page 165) |

## Setting the slot number manually

On a VME64x backplane (5-row connectors), a board can automatically sense which slot it is plugged into by reading special pins on P1. These geographical address pins are encoded on the backplane. Boards that can read these pins present the geographical address in the VME64 Slot register. These boards also check the geographically addressing parity and signal its validity in the same register.

In some cases the VGM5 will not be able to read these pins because the board is configured with 3-row VME connectors or it may be plugged into an old VME64 backplane (3-row connectors). For these situations, jumpers on J02N (pins 9–22) are provided to set the board's slot number manually.

To set a slot number, install jumpers over the appropriate pair of pins as shown with a bullet (●) in the table below. Pins with no jumper installed are shown with a dash (—). This is a binary encoded scheme with pins 11 & 12 MSB and pins 19 & 20 LSB.

Install the User Defined Slot Number jumper (pins 9 & 10) to let hardware/software read the user defined slot number from the VME64 Slot register. The value in this register is set by the 5 slot number jumpers.

Note that user defined slot number jumpers must not be used if both the board and backplane have 5-row connectors.

JO2N jumper settings for slot number selection

| Slot No. | Pins 11 &12<br>(GA4) | Pins 13 & 14<br>(GA3) | Pins 15 & 16<br>(GA2) | Pins 17 & 18<br>(GA1) | Pins 19 & 20<br>(GA0) |

|----------|----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 1        | _                    | _                     | _                     | _                     | •                     |

| 2        | _                    | _                     | _                     | •                     | _                     |

| 3        | _                    | _                     | _                     | •                     | •                     |

| 4        | _                    | _                     | •                     | _                     | _                     |

| 5        | _                    | _                     | •                     | _                     | •                     |

| 6        | _                    | _                     | •                     | •                     | _                     |

| 7        | _                    | _                     | •                     | •                     | •                     |

| 8        | _                    | •                     | _                     | _                     | _                     |

| 9        | _                    | •                     | _                     | _                     | •                     |

| 10       | _                    | •                     | _                     | •                     | _                     |

| 11       | _                    | •                     | _                     | •                     | •                     |

| 12       | _                    | •                     | •                     | _                     | _                     |

| 13       | _                    | •                     | •                     | _                     | •                     |

| 14       | _                    | •                     | •                     | •                     | _                     |

| 15       | _                    | •                     | •                     | •                     | •                     |

| 16       | •                    | _                     | _                     | _                     | _                     |

| 17       | •                    | _                     | _                     | _                     | •                     |

| 18       | •                    | _                     | _                     | •                     | _                     |

| 19       | •                    | _                     | _                     | •                     | •                     |

| 20       | •                    | _                     | •                     |                       | _                     |

| 21       | •                    | _                     | •                     | _                     | •                     |

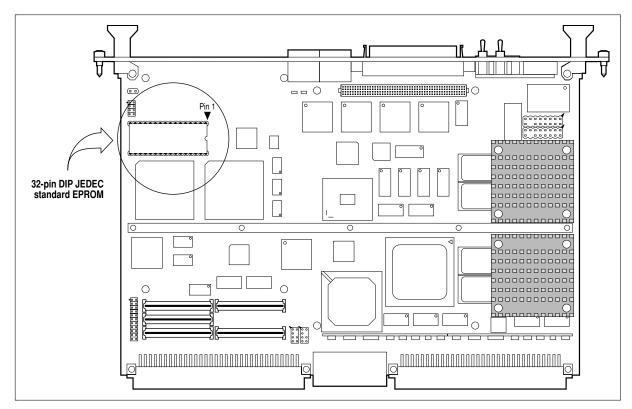

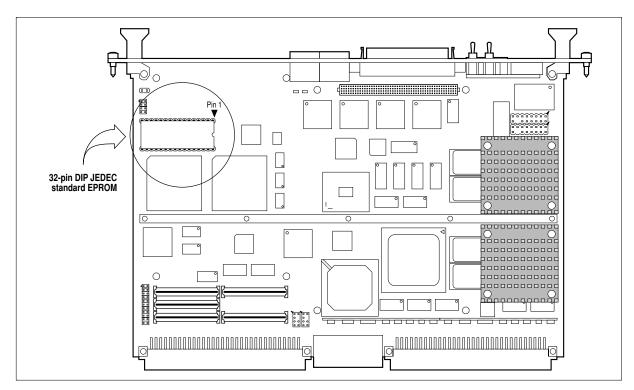

## Installing a monitor PROM

The VGM5 comes with one, 32-pin, 8-bit, monitor DIP EPROM socket that accepts any of the following devices<sup>†</sup>:

- 27C010 1 Mbit (128KB) DIP EPROM

- 27C020 2 Mbit (256KB) DIP EPROM

- 27C040 4 Mbit (512KB) DIP EPROM

- 28F020 2 Mbit (256KB) Flash DIP EPROM

- 29C040 4 Mbit (512KB) Flash DIP EPROM

Some boards ship from the factory with the appropriate monitor PROM already installed. However, a new or updated PROM is easily added or changed in the field.

The paragraphs below describe a field installation of a new DIP EPROM and all of the potential configuration changes you may need to make to the VGM5 CPU board as a result.

If the desired monitor PROM is already present on the VGM5 board or if the monitor ROM is programmed into Boot Flash (e.g. VxWorks), proceed to the next chapter in this section.

<sup>†</sup> TI brand EPROMs cannot be used. Their requirement for Vcc on unused pins prevents a TI PROM from being used in a general purpose socket. EPROMs from other manufacturers such as Intel, AMD, etc. work without problem.

## Materials

To complete this procedure, you will need the following materials:

- The desired monitor firmware PROM

- A 32-pin, 0.6" wide DIP extractor tool to remove the current PROM (if necessary)

- The manual for the software product on the new EPROM

## Procedural steps

To install a monitor EPROM, complete the following procedure:

• Verify proper operation of the motherboard (if replacing an existing monitor PROM) — Before attempting to install a new EPROM on an existing board, ensure that the motherboard (and any attached mezzanine cards) are operating properly.

VGM5 DIP EPROM socket location

**Power-down and remove the SBC from the card cage** — Power-down the system and remove the VGM5 CPU board from the card cage.

Synergy SBCs contain static-sensitive devices. Make sure you are properly grounded (by putting on a ground-strap, touching a system ground such as a metallic chassis or case, etc.) before removing and handling the board. Use an ESD-protected workstation for module removal and installation work.

**Solution Locate the current monitor PROM or DIP socket on the CPU board and remove the current monitor PROM** (if necessary) — The figure on the previous page shows the location of the DIP EPROM socket on the VGM5 board.

Use a chip extraction tool to remove the DIP EPROM from the socket to avoid damaging parts underneath.

- Install the DIP EPROM Install the DIP EPROM in the socket. The VGM5 EPROM socket accepts 32-pin DIP EPROM devices. The figure above shows the orientation of the DIP EPROM after proper installation (note orientation of notch end).

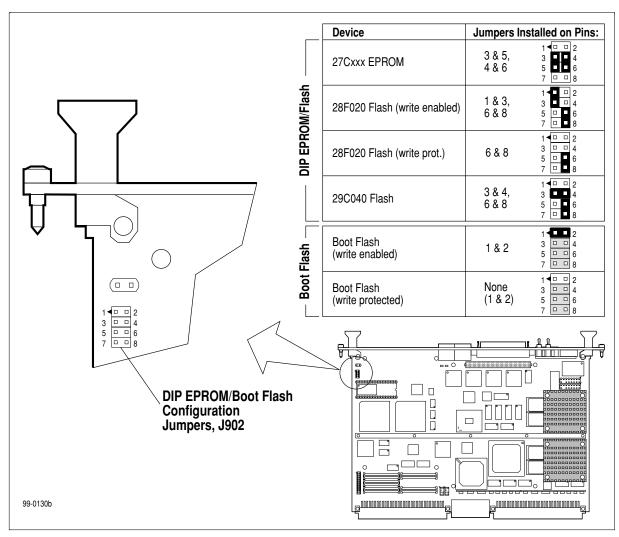

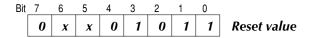

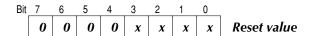

- **Install DIP EPROM configuration jumpers (J902)** Place jumpers on **J902** to configure the board for the device used in the DIP EPROM socket as shown in the drawing below.

Some VGM5 boards include an ECO that adds a Boot Flash write protect function to the J902 jumper block, pins 1 and 2. Refer to the *Additional write protection of Boot Flash* discussion in Section 4 (page 164) for more information on this jumper.

DIP EPROM/Boot Flash configuration jumpers, J902

# Installing the RGSx memory module

VGM5 boards provide all on-board DRAM on upgradable memory modules. Modules are available with the following amounts of DRAM:

RGS1 memory module:

- 16 MB

- 32 MB

- 64 MB

RGS2/RGS3 memory module:

- **9** 32 MB

- 64 MB

- 128 MB

- 256 MB

- 512 MB

Rev. E VGM5 boards and higher use the RGS3 memory module. Rev. D and lower VGM5 boards use the RGS1/RGS2 memory module.

Normally, all VGM5 boards ship from the factory with a memory module installed. The modular design of the VGM5 DRAM interface, however, allows for easy DRAM upgrades in the field.

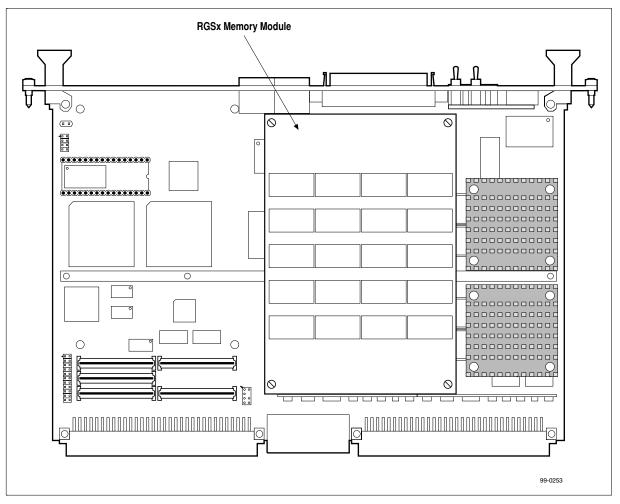

The drawing below shows the location of the RGSx memory module on the motherboard.

RGSx memory module location

This chapter describes field installation of an RGSx memory module.

If the desired RGSx module is already present on the VGM5 board, proceed to the next chapter in this section.

# Installing/upgrading the RGSx memory module

Perform the following steps to install or upgrade an RGSx memory module.

- Verify proper operation of motherboard (if replacing an existing RGSx memory module) Before attempting to install a new RGSx memory module on a working CPU motherboard, consider checking that the motherboard (and any attached PMC cards) are operating properly.

- **Power-down and remove SBC from card cage** Power-down the system and remove the VGM5 CPU board from the card cage.

Synergy SBCs contain static-sensitive devices. Make sure you are properly grounded (by putting on a ground-strap, touching a system ground such as a metallic chassis or case, etc.) before removing and handling the board. Use an ESD-protected workstation for module removal and installation work.

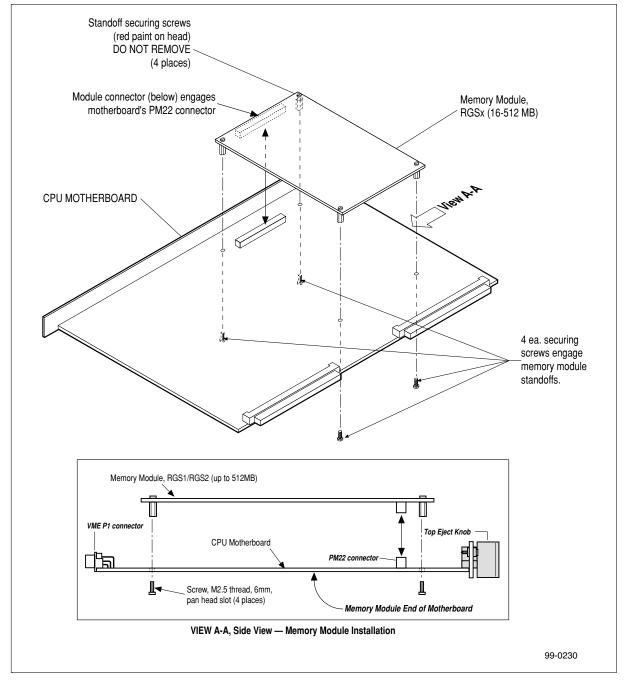

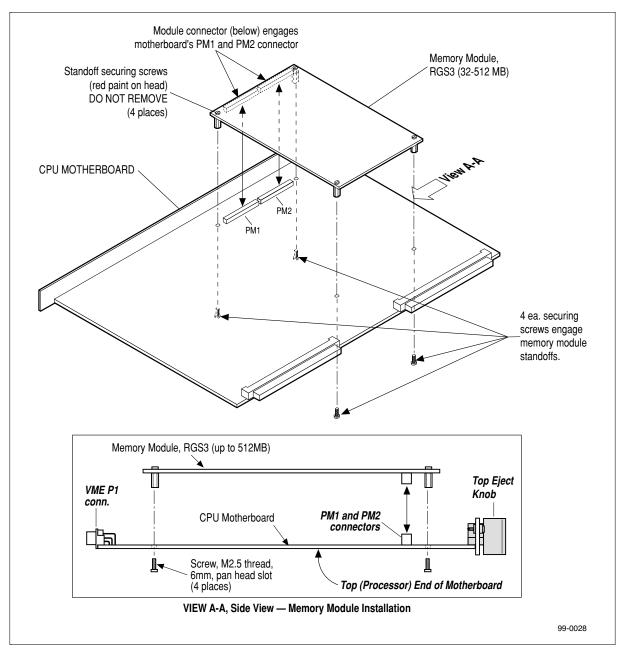

- **8** Remove existing RGSx memory module from CPU motherboard (if you are replacing refer to RGSx module installation drawing below for assembly details):

- a. Place VGM5/RGSx assembly face-down, that is with large circuit board (motherboard) on top, on a flat surface of an ESD-protected workstation.

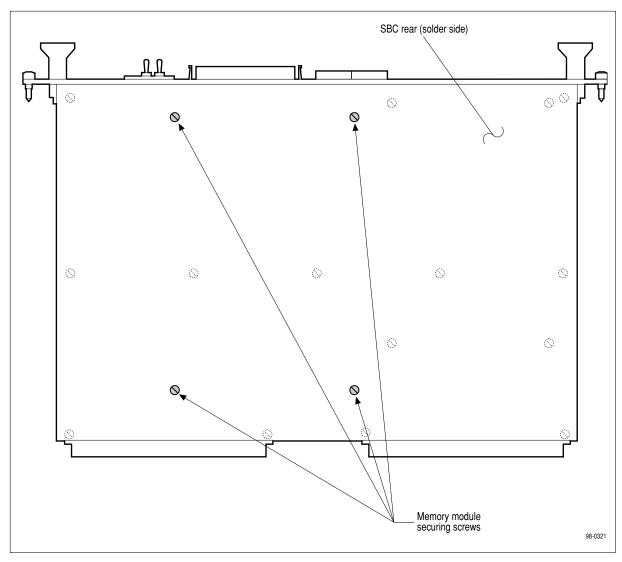

- b. Remove four M2.5 slot-head screws from rear (solder) side of VGM5 motherboard. See *Location, memory module securing screws* drawing below.

- c. Turn VGM5/RGSx assembly over.

- d. Grasp RGSx sides at connector end (toward SBC front panel) and gently pull up until the connector comes loose (rocking back and forth may help).

- Install RGSx module on motherboard Installation of RGSx memory module is reverse of removal. Refer to RGSx module installation drawing below for assembly details.

The SBC memory module connector is fragile. To avoid connector damage, make sure that module connector is properly aligned with SBC connector before fully seating module.

RGS1/RGS2 module installation

RGS3 module installation

## Memory module securing screws

To aid in installation, the location of the memory module securing screws on the VGM5 is shown in the drawing below.

Location, memory module securing screws

# Installing PMC cards

VGM5's I/O expansion is provided by PMC (PCI Mezzanine Card) cards.

This chapter describes PMC card installation.

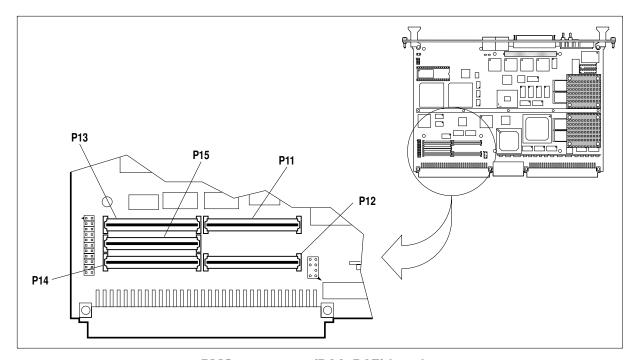

## VGM5 PMC connectors

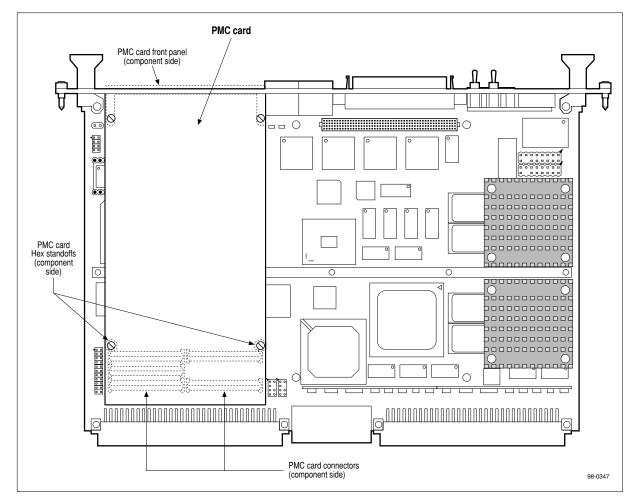

The VGM5 comes with PMC connectors for direct installation of one PMC card. The drawing below shows the location of a PMC card on the VGM5 board.

PMC location (top view)

## Adding additional PMC cards with the PEX3 expansion board

The PEX3 PMC expansion option provides VGM5 with up to 3 additional PMC slots plus additional SDRAM and Flash memory. Refer to Appendix D (page 313) for complete PEX3 information

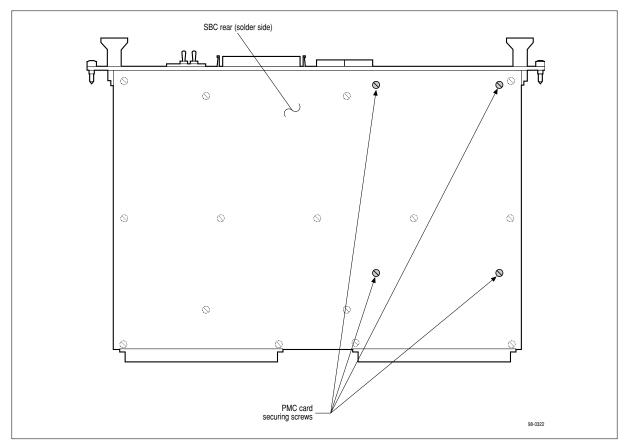

## PMC card securing screws

To aid in installation, the location of the PMC card securing screws on the VGM5 is shown in the drawing below.

Location, PMC card securing screws

## Installing a PMC card

Perform the following steps to install a PMC card.

The VGM5 PMC slot accepts 5V VI/O or 5V-tolerant PMCs only.

• Power-down and remove SBC from card cage — Power-down the system and remove the VGM5 SBC from the card cage.

Synergy SBCs contain static-sensitive devices. Make sure you are properly grounded (by putting on a ground-strap, touching a system ground such as a metallic chassis or case, etc.) before removing and handling the board. Use an ESD-protected workstation for module removal and installation work.

- **Remove PMC filler panel from SBC front panel** The filler panel will be one of two types. The first type simply snaps in place remove by pushing from the inside. The second type is an actual blank PMC front panel remove 2 ea. 6 mm M2.5 slot head securing screws from solder side of board to remove (see PMC card securing screws location drawing above).

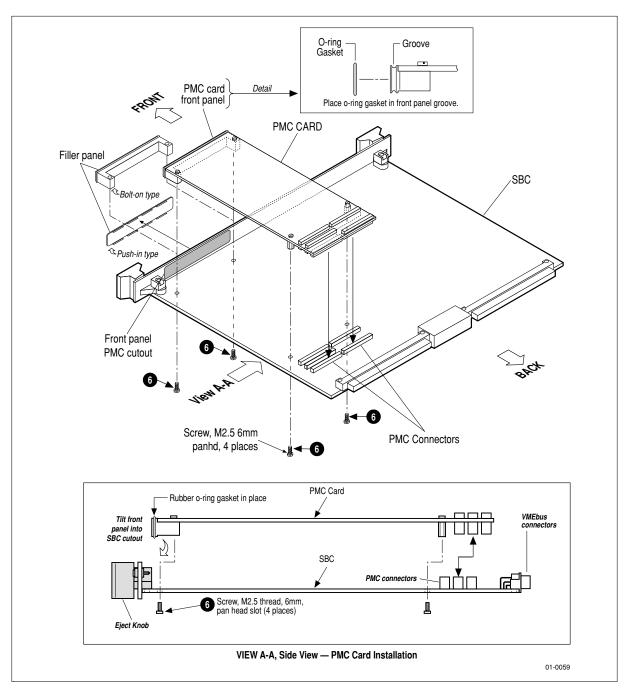

- **Install PMC card onto SBC** (refer to drawing below for assembly details):

- a. Place VGM5 assembly face-up on a flat surface of an ESD-protected workstation.

- b. If not already on, install PMC card's front panel O-ring gasket (included with PMC card) by slipping gasket into groove around front panel.

- c. Grasp PMC at sides: with card front panel towards SBC front panel from rear, tilt PMC front panel into SBC front panel cutout and engage front panel O-ring gasket with chamfer in SBC panel cutout. With PMC front panel in place, place card over SBC connectors. Ensure both PMC and SBC connectors are aligned then press down over PMC connector area to fully engage SBC connectors.

- d. Turn VGM5 assembly over.

- e. Install four 6 mm M2.5 slot-head screws (item 6, typically supplied with PMC) from rear (solder) side of VGM5 motherboard. Two screws engage the standoffs on the PMC card. The other two screws engage the threaded holes in the PMC card front panel. See *Location*, *PMC* card securing screws drawing earlier in this chapter.

Removal is reverse of installation.

#### Single PMC installation - Required hardware

| Item<br>locator | Quantity in assy | Synergy part number | Item<br>description                                                                                                             |  |

|-----------------|------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 6               | 4                | Fas/SwM25FP6SS      | Screw, M2.5 thread, pan head, phillips, 6 mm long, stainless steel (or use whatever screw fastener is supplied in PMC card kit) |  |

PMC card installation

Section 2: Getting Started

Installing PMC cards

# Installing the PO overlay

The P0 overlay is used to interconnect boards within the same cardcage via Synergy's  $P0 \cdot PCI^{\text{TM}}$  interface. Refer to the **PCI-PCI Bridge Interface** chapter (page 253) for a description of the interface.

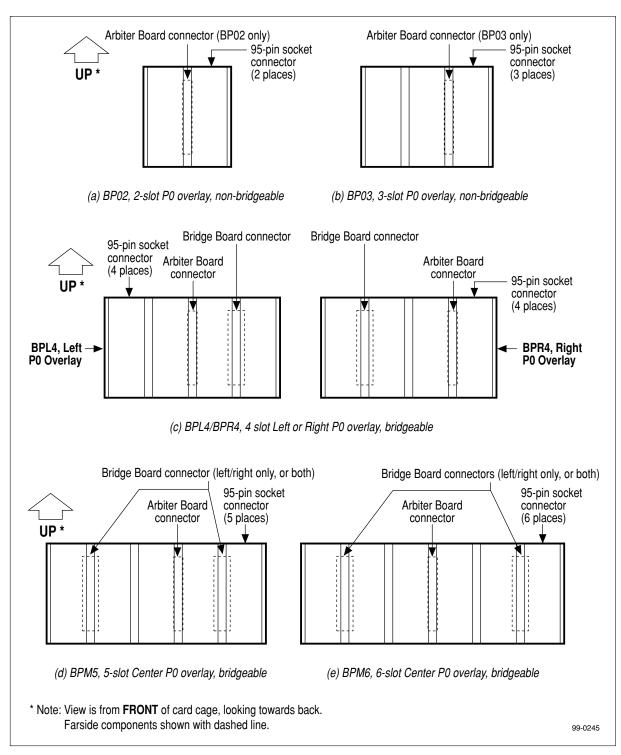

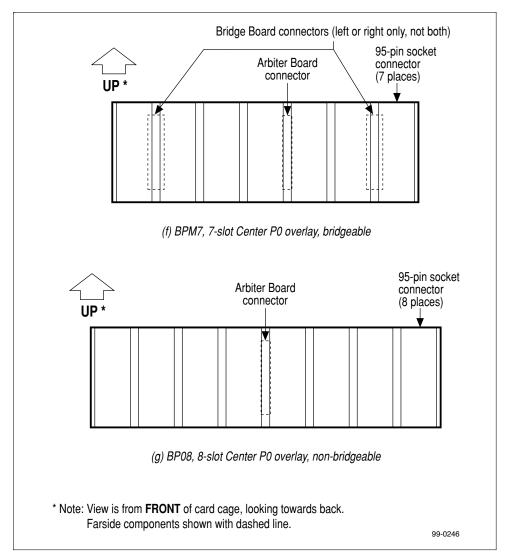

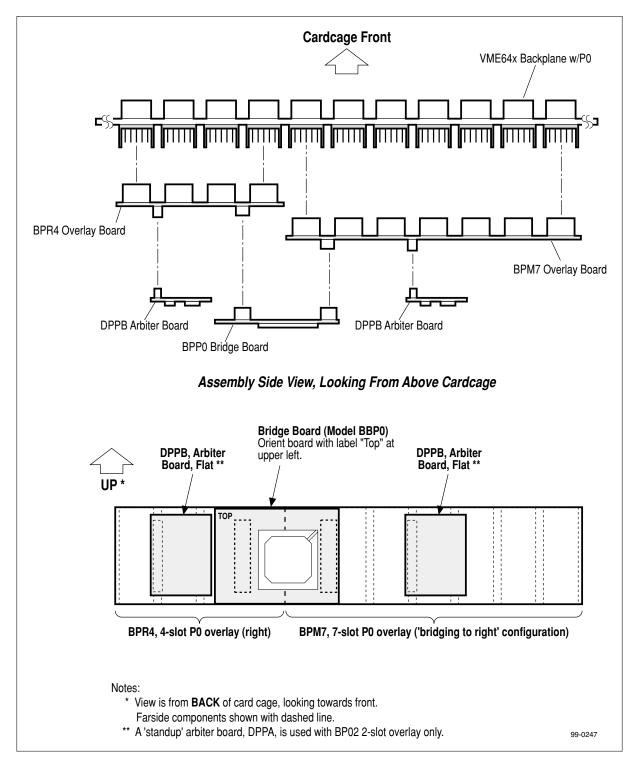

The P0 overlay board comes in left, right, and center configurations of varying slot capacities. Each overlay uses a small, plug-in arbiter board. Some overlay models allow joining with another overlay section via a bridge board. The table below lists the P0 overlay components for use with the  $P0 \cdot PCI^{\mathsf{TM}}$  interface.

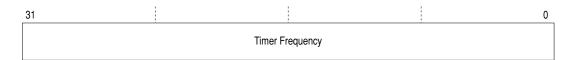

#### PO overlay components