## Themis TSVME-110-4 VME Single Board Computer

In Stock

**New From Surplus Stock**

Open Web Page

https://www.artisantg.com/61030-31

After Technology Drog

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# **TEMEX TELECOM**

# **TSVME 110**

# Carte CPU 68000 Multifonctions

# **MANUEL D'UTILISATION**

TSVME110

**Carte CPU 68000 Multifonctions**

85124-A0

# **SOMMAIRE**

| 1 - MISE EN ROUTE                                                                                                           | • | SOMMAIRE                                                                                                  | 1        |

|-----------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------|----------|

| 1.2 - Mise sous tension                                                                                                     |   | I - MISE EN ROUTE                                                                                         | 4        |

| 2.1 - Présentation                                                                                                          |   | 1.1 - Inspection du matériel reçu                                                                         | 4        |

| 2.2 - Description de la carte                                                                                               | • | II - INTRODUCTION                                                                                         | 6        |

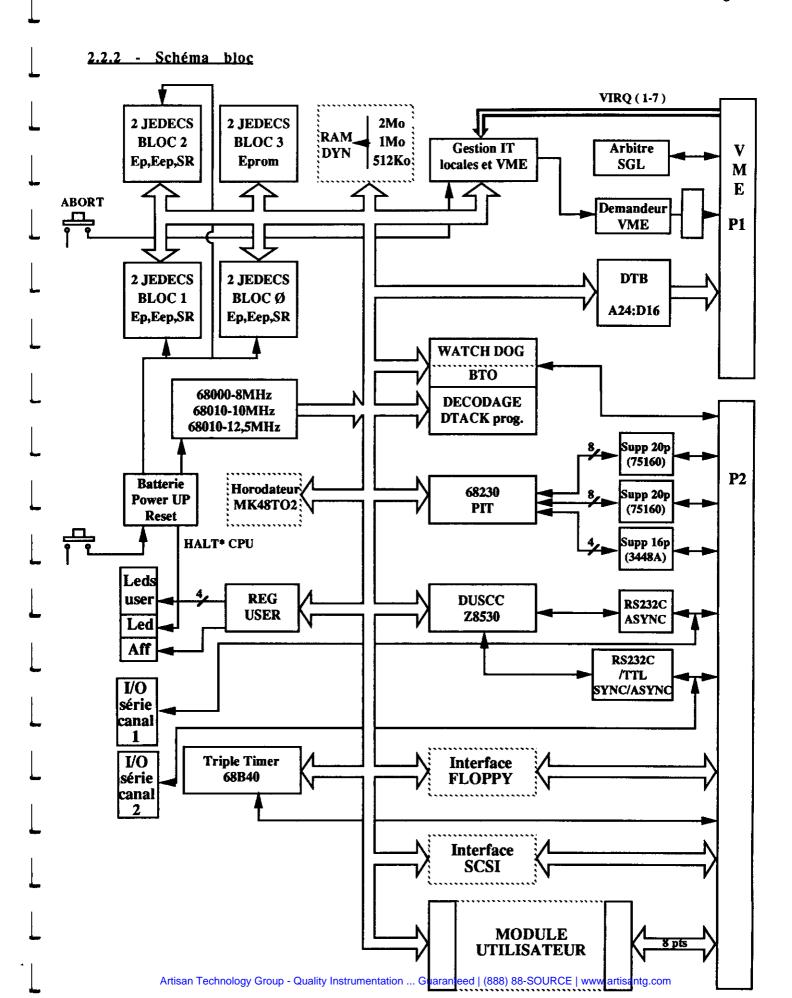

| 2.2.2 - Schéma Bloc                                                                                                         | - | 2.1 - Présentation                                                                                        | 6        |

| 3.1 - Espace d'adressage - Différentes configurations 20 3.2 - Supports Jedecs 32 broches                                   | - | 2.2.2 - Schéma Bloc                                                                                       | 13<br>14 |

| 3.2 - Supports Jedecs 32 broches                                                                                            | _ | III - DESCRIPTION TECHNIQUE                                                                               | 20       |

| 3.2.1 - Adressage des 4 blocs de supports Jedecs                                                                            | - | 3.1 - Espace d'adressage - Différentes configurations                                                     | 20       |

| 3.2.2 - Configuration Jedec de chaque bloc de supports 28 3.2.3 - Définition du temps d'accès des 4 blocs de support Jedecs |   | 3.2 - Supports Jedecs 32 broches                                                                          | 23       |

| 3.2.4 - Sauvegarde batterie                                                                                                 | - | 3.2.2 - Configuration Jedec de chaque bloc de supports 3.2.3 - Définition du temps d'accès des 4 blocs de | 28       |

| 3.4 - Gestion des interruptions                                                                                             |   |                                                                                                           |          |

| 3.4.1 - Requêtes d'interruption du bus VME                                                                                  | - | 3.3 - Options Ram dynamique                                                                               | 33       |

| 3.4.2 - Requêtes d'interruptions locales                                                                                    |   | 3.4 - Gestion des interruptions                                                                           | 34       |

| 3.5.1 - Registres intégrés au dispositif de contrôle de la carte                                                            | - | 3.4.1 - Requêtes d'interruption du bus VME                                                                | 34<br>34 |

| de la carte                                                                                                                 | - | 3.5 - Registres de commande et status                                                                     | 36       |

| 3.5.3 - Registre de relance de chien de garde                                                                               | - | de la carte                                                                                               |          |

|                                                                                                                             | - | 3.5.3 - Registre de relance de chien de garde                                                             | 42<br>43 |

| 3 Atisan Technologiporous totality Astransation Guaranteed   (888) 88-SOURCE   www.artisantg.com5                           | - | 3.6 - Dispositifs de contrôle de la carte TSVME110                                                        | 44       |

|                                                                                                                             | - | 3 - Artisan Technology Orsus t defalited Astronamenton Guaranteed   (888) 88-SQURCE   www.artisantg.c     | 415      |

|      | 3.6.3 - Gestion et Contrôle de SYSFAIL* et ACFAIL* 4 3.6.4 - Dispositif de chien de garde | 48<br>49             |

|------|-------------------------------------------------------------------------------------------|----------------------|

|      | 3.7 - Interface du bus VME                                                                | 52                   |

|      | 3.7.1 - Module de transfert des données (DTB)                                             | 53<br>54             |

|      | 3.8 - Périphériques                                                                       | 56                   |

|      | 3.8.1 - Timer                                                                             | 60<br>75<br>79<br>83 |

|      | 3.9 - Interface module utilisateur                                                        | 90                   |

|      | 3.9.1 - Contrôle du module utilisateur par la carte TSVME110                              |                      |

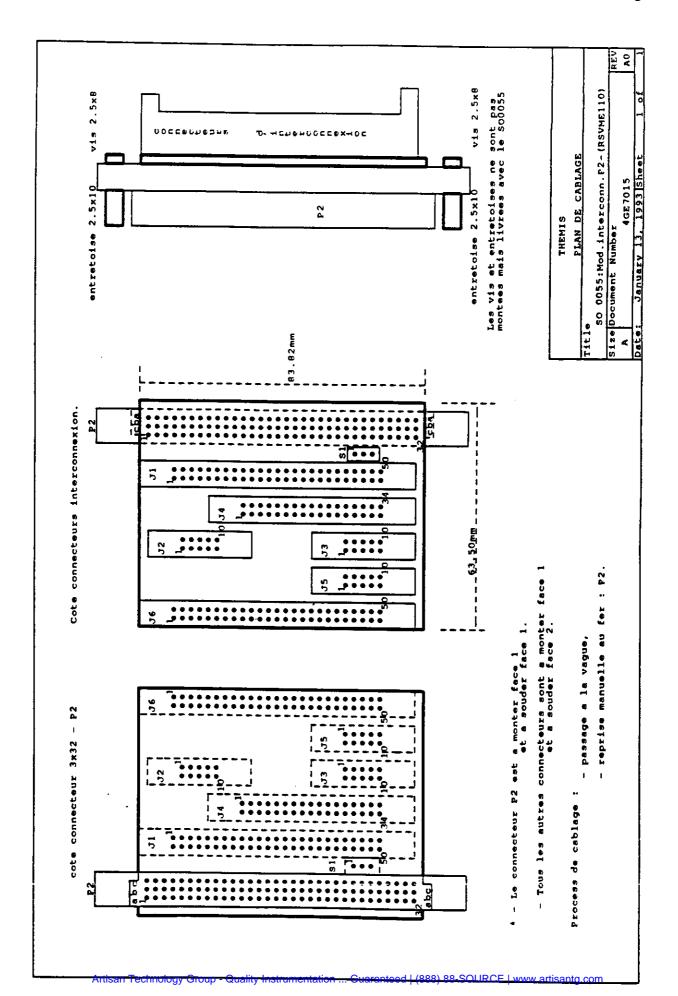

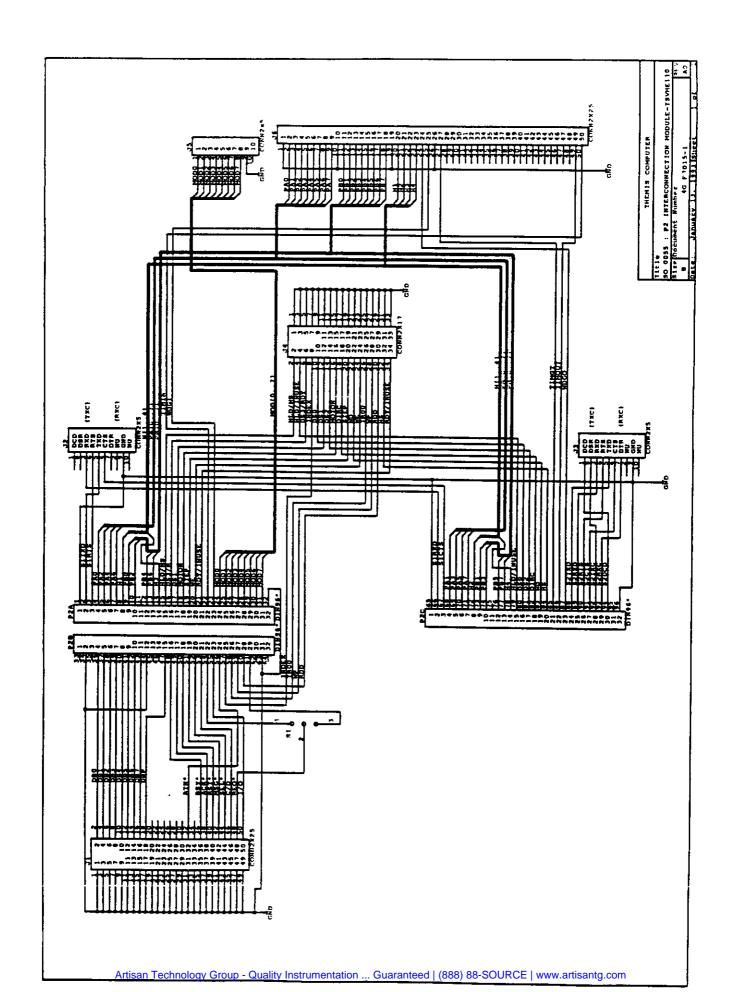

|      | 3.10 - Connecteurs P1 et P2                                                               | 96                   |

| ıv - | SUPPORT LOGICIEL1                                                                         | 02                   |

|      | 4.1 - Moniteur d'aide à la mise au point et autotest1                                     | 02                   |

|      | 4.1.1 - Introduction                                                                      | 04<br>06             |

|      | 4.2 - Fonctions logicielles TSVME1101                                                     | 11                   |

|      | ANNEXES DU SUPPORT LOGICIEL1                                                              | 14                   |

#### **FIGURES**

|   | Fig.<br>Fig. | 2.2  | - | Emplacement des connecteurs  Emplacement des gouttes de soudure -  Face soudure  Emplacement des sélecteurs et gouttes de soudure - Face composants | 18 |

|---|--------------|------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | Fig.<br>Fig. |      | - | Espace d'adressage                                                                                                                                  | 24 |

|   | Fig.         |      | - | Adressage des 4 blocs de Jedecs                                                                                                                     | 27 |

|   | Fig.         |      | _ | Configurations possibles sur SW11, 10 et 9                                                                                                          | 25 |

|   | Fig.         |      | _ | Configurations des interruptions locales                                                                                                            | 15 |

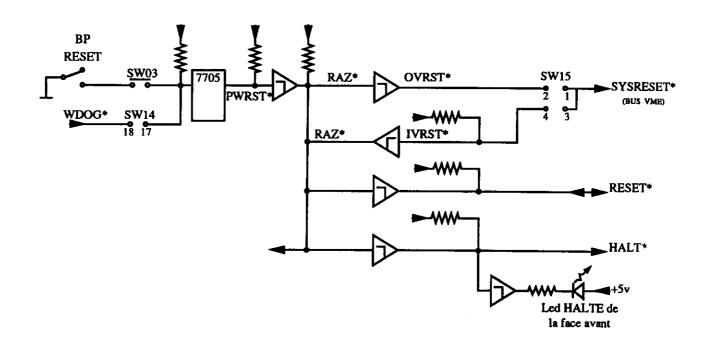

| • | Fig.         |      |   | Synoptique du dispositif de Reset<br>Synoptique de gestion et contrôle de                                                                           | 40 |

|   | Fig.         |      |   | SYSFAIL* et ACFAIL*                                                                                                                                 | 48 |

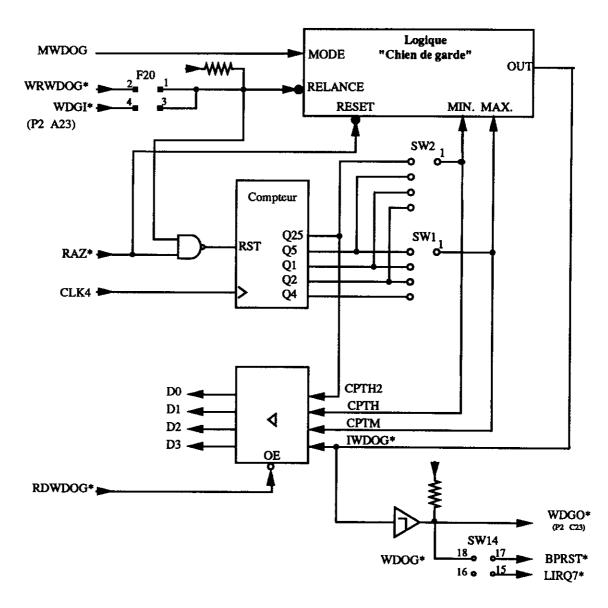

|   | Fig.         | 3.8  | _ | Synoptique du dispositif de chien de garde                                                                                                          | 49 |

| • |              |      |   | Synoptique d'implantation du 68B40                                                                                                                  |    |

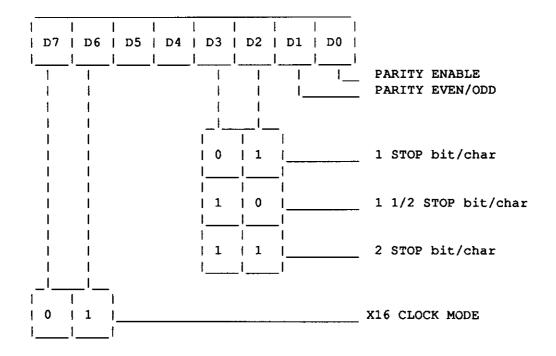

|   | Fig.         | 3.10 | - | Synoptique des E/S série                                                                                                                            | 61 |

|   | Fig.         | 3.11 | _ | Configuration du canal 1                                                                                                                            | 61 |

| • | Fig.         | 3.12 | - | Configuration du canal 2                                                                                                                            | 62 |

|   |              |      |   | Synoptique des ports parallèles                                                                                                                     |    |

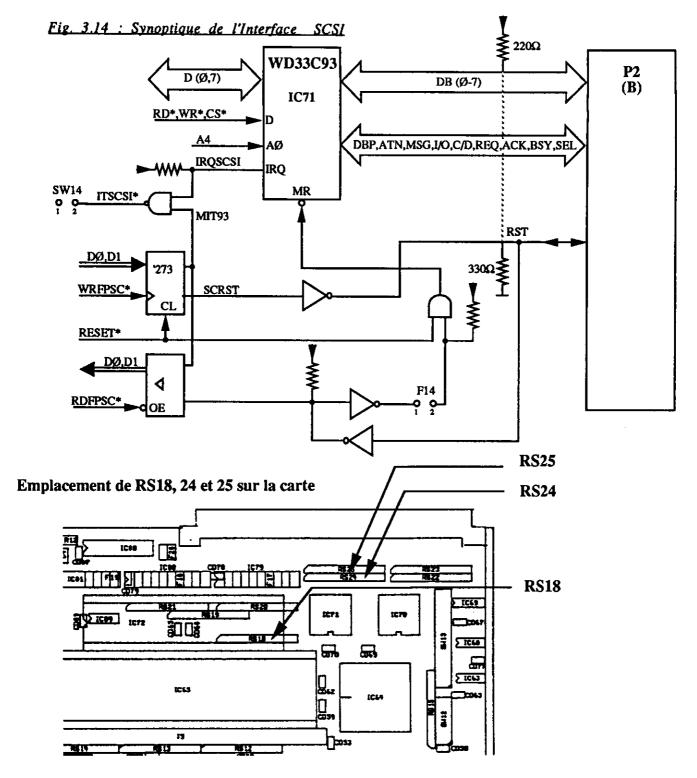

|   |              |      |   | Synoptique de l'Interface SCSI                                                                                                                      |    |

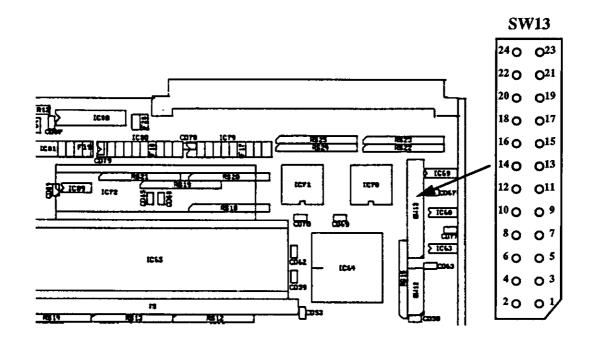

| • |              |      |   | Brochage du sélecteur SW13                                                                                                                          | 85 |

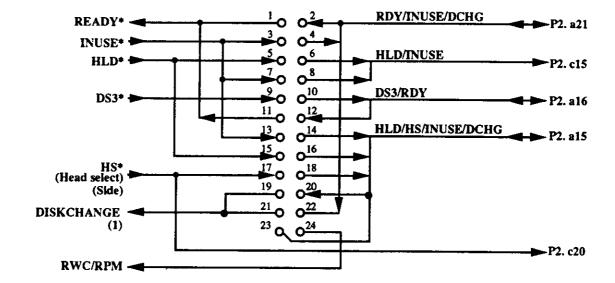

|   | Fig.         | 3.16 |   | Affectation de broches du connecteur des unités de disques souples des différents                                                                   | 07 |

| • | Fia          | 2 17 |   | Constructeurs Brochage du Connecteur P1                                                                                                             |    |

|   |              |      |   | Brochage du connecteur P2                                                                                                                           |    |

|   | rig.         | 2.10 | _ | broomage an connecteur rz                                                                                                                           | 20 |

#### I - MISE EN ROUTE

#### 1.1 - INSPECTION DU MATERIEL RECU

- Vérifier que l'emballage n'a subi aucun dommage au cours du transport.

- Ouvrir l'emballage et vérifier que tous les éléments cités dans la 'Fiche Inventaire Produit' sont présents.

- Il est recommandé de conserver l'emballage pour stocker la carte ou pour faciliter l'envoi de la carte dans le cas d'un service ultérieur.

- Dès que la carte est reçue et déballée, vérifier que le circuit imprimé, la face avant, les connecteurs, modules et composants n'ont reçu aucun dommage.

#### 1.2 - MISE SOUS TENSION

- Les liaisons série sont configurées en usine, mode asynchrone.

- Canal 1 en liaison console

- Canal 2 en liaison 'système'. (pour modifier voir § 3.8.2)

- L'utilisateur doit configurer les cartes en fonction de son application :

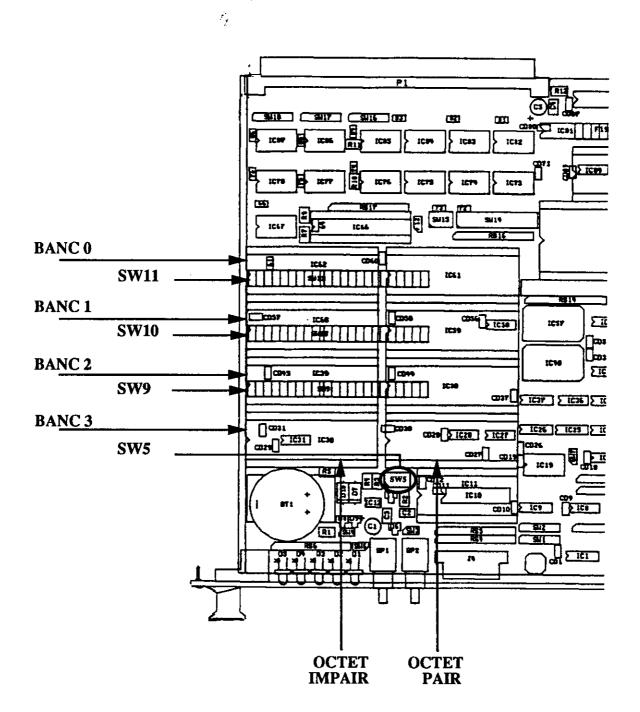

- (1) Blocs de supports Jedecs : Type de composants (cf § 3.2)

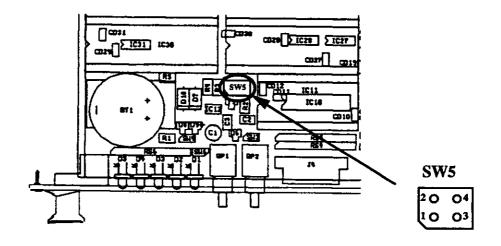

SW5 Bloc 3 Eproms

SW9 Bloc 2 SRAM/EEPROM/EPROM

SW10 Bloc 1 SRAM/EEPROM/EPROM

SW11 Bloc 0 SRAM/EEPROM/EPROM

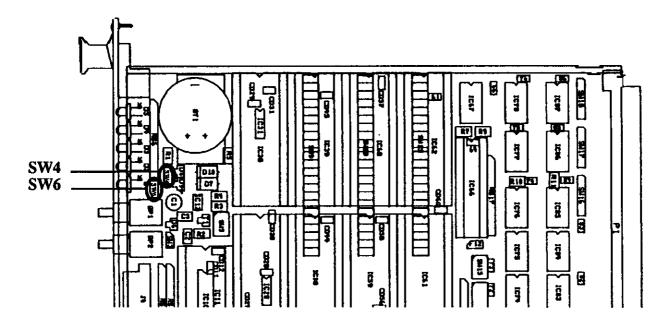

SW6 Sauvegarde batterie.

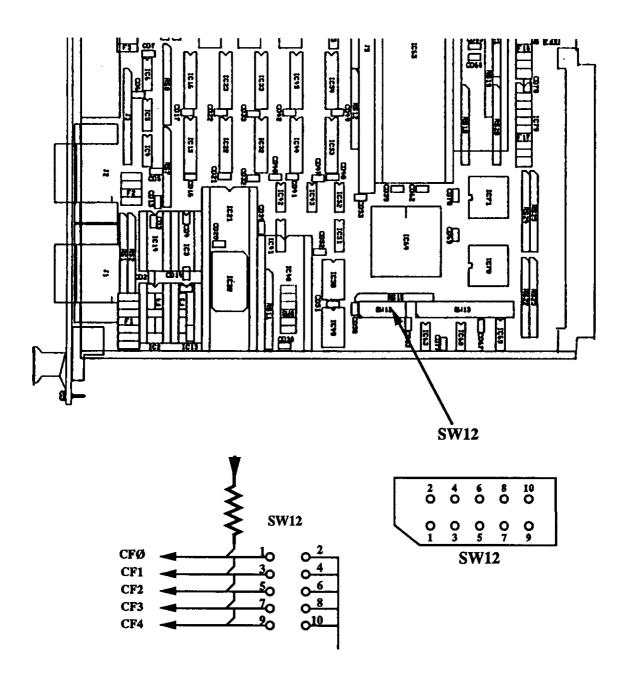

- (2) Configuration mémoire-SW12 (cf § 31, 3.2 et 3.3)

Jedecs/Ram dynamique

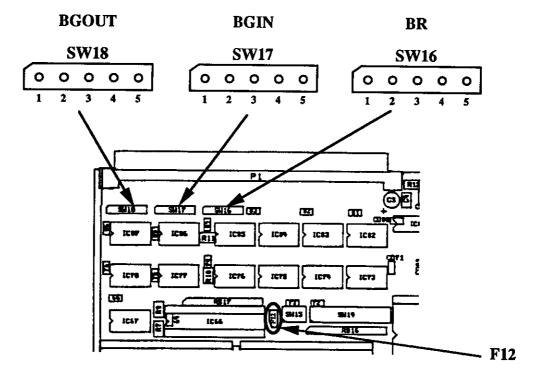

- (3) Arbitre/demandeur VME-F12 (cf § 3.7)

- (4) Niveau demandeur chaînage arbitrage-SW16, 17, 18 (cf § 3.7)

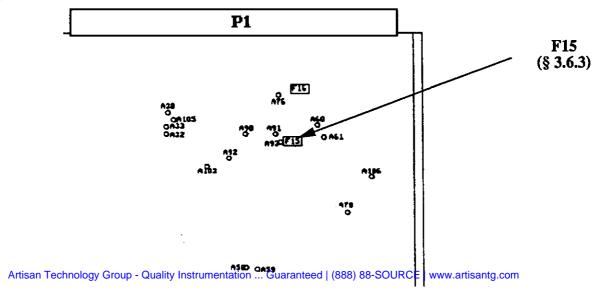

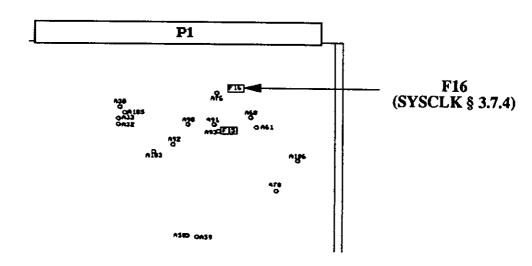

- (5) SYSCLK, RESET\*, SYSFAIL\* du bus VME

F16, SW15, F15

Validation du Bouton poussoir Reset-SW3

(cf § 3.6/1/3)

(§ 3.7)

(§ 3.6.1)

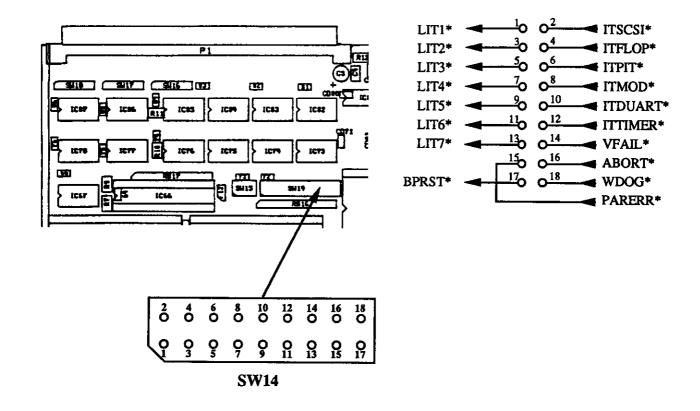

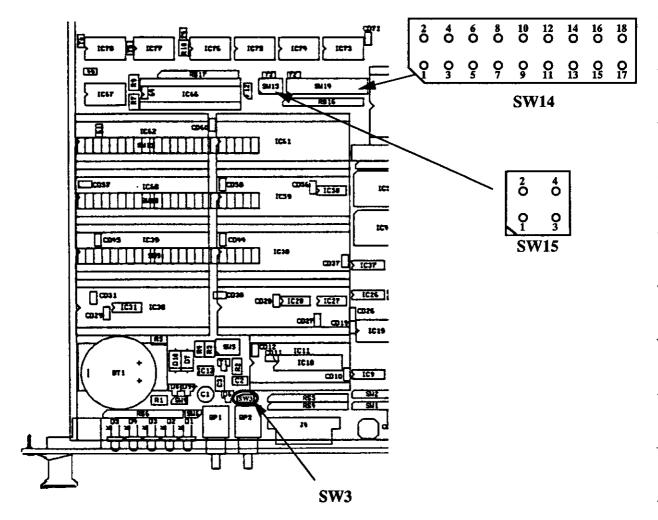

- (6) Sélection des niveaux utilisés pour les it locales et actions du chien de garde SW14 (§ 3.4, 3.6.4)

- (7) Configuration du chien de garde : entrée de relance durées - F20, SW1 et SW2 (§ 3.6.4)

- (8) Configuration des périphériques :

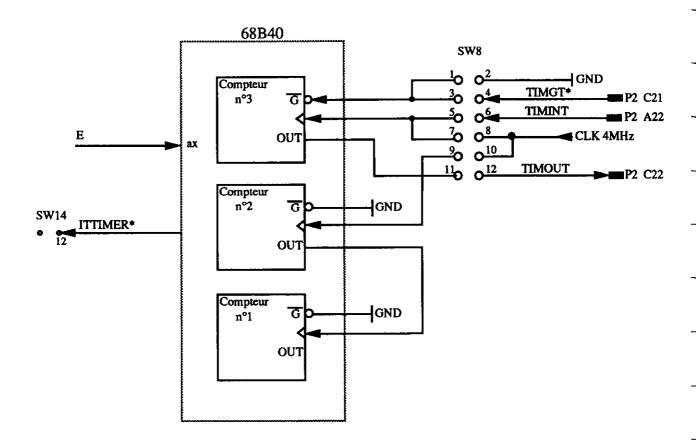

- Timer compteur 3 et entrée du compteur 2 SW8 (§ 3.8.1)

- Entrées/sorties parallèles

(§ 3.8.3)

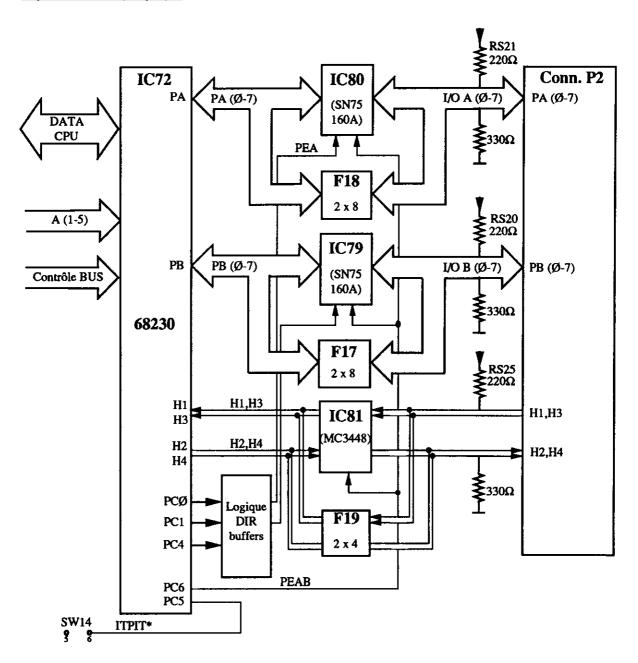

- Sans buffers la carte est configurée en liaison directe 68230 - P2 : liaisons F17, F18 et F19 présentes

- Avec buffers les liaisons sur F17, F18 et F19 sont absentes et les composants SN75160 sont montés en IC79, IC80 et MC3448A, en IC81

- Option FLoppy SCSI:

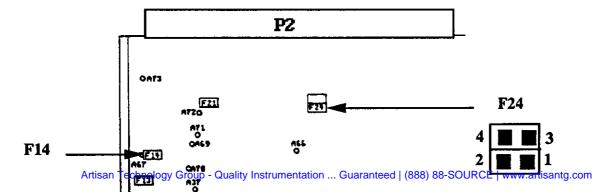

| - | Entrée Reset du bus SCSI active sur le | (§ 3.8.4) |

|---|----------------------------------------|-----------|

|   | contrôleur ou non F14                  |           |

| - Configuration P2/SO0055 | (§ 3.8.4.4) |

|---------------------------|-------------|

| F24 - SW1 du SO0055       | (§ 3.8.12)  |

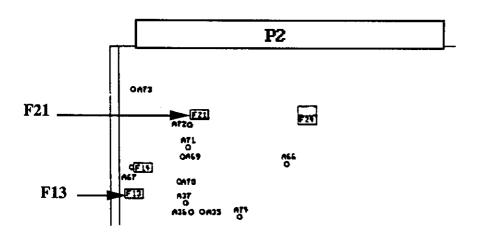

- Configuration interface floppy utilisation DISK CHANGE, polarité DRV SW13, F13 et F21. (§ 3.8.5)

- Insérer la carte dans un châssis hors tension, en s'assurant que les signaux chaînés du bus VME (IACKIN\*, OUT\*, BGxIN\*, OUT\*) sont bien chaînés jusqu'à la place occupée par la carte TSVME110.

#### II - INTRODUCTION

#### 2.1 - PRESENTATION

La carte TSVME110 se présente comme une carte CPU 16 bits multifonctions au bus VME. Dans sa version de base, elle fournit les fonctions suivantes :

- Accès en maître sur le bus VME.

- Port parallèle 16 bits bi-directionnel.

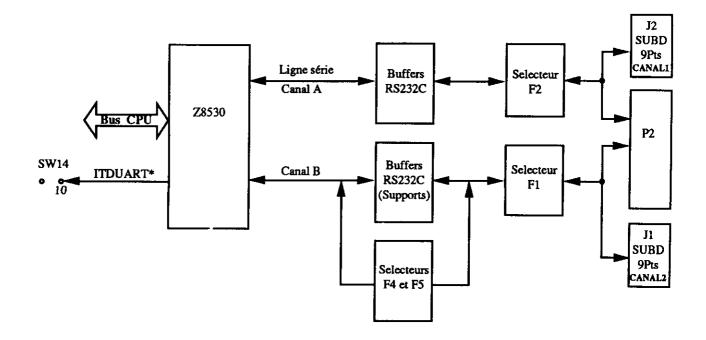

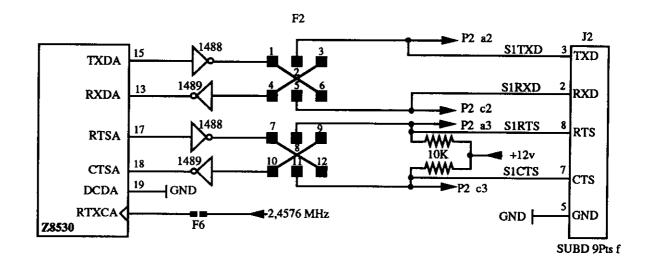

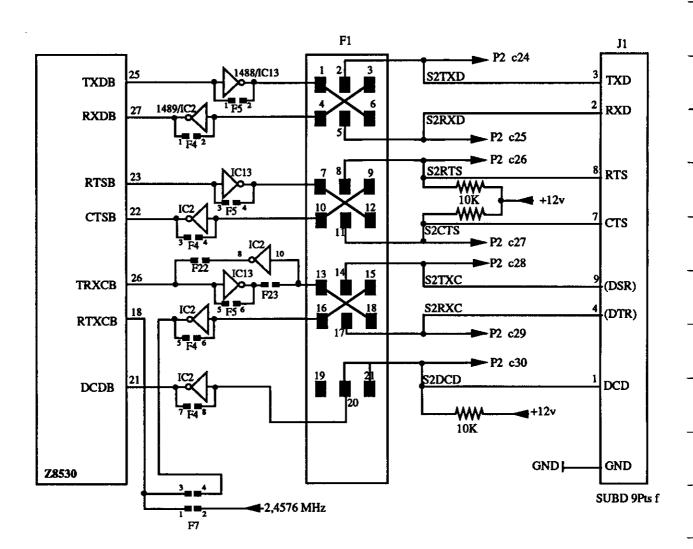

- 2 lignes série dont une synchrone ou asynchrone.

- Fonction chien de garde.

- 3 timers programmables.

- 4 blocs de 2 supports jedecs 32 broches.

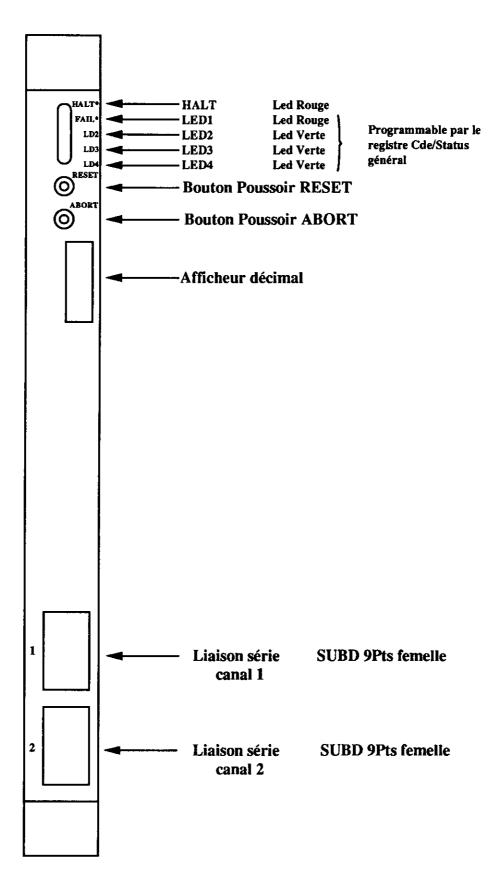

- 5 Leds et afficheur décimal en face avant.

- Une première option permet d'ajouter sur la carte un contrôleur SCSI et un contrôleur floppy.

- Une seconde série d'options augmente la capacité de mémoire de la carte avec 512 K, 1M ou 2Moctets de ram dynamique.

- La connectique est prévue pour permettre l'adjonction d'un module utilisateur.

- Il existe différentes références commerciales de la carte TSVME110. La liste et les configurations de ces références sont données à la page suivante.

| FONCTION             | TSVME110-1                 | TSVME110-2                 | TSVME110-3                 | TSVME110-4                 | TSVME110-5                 |

|----------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| CPU                  | 68000-8MHz                 | 68010-10MHz                | 68010-12.5MHz              | 68010-12.5MHz              | 68010-12.5MHz              |

| Bloc Jedec 0         | 64 Koctets<br>SRAM 100ns   | 64 Koctets<br>SRAM 100ns   | 64 Koctets<br>SRAM 80 ns   | Libre                      | 64 Koctets<br>SRAM 80ns    |

| Bloc Jedec 1         | Libre                      | Libre                      | Libre                      | Libre                      | 64 Koctets<br>SRAM 80ns    |

| Bloc Jedec 2         | Libre                      | Libre                      | Libre                      | Libre                      | Libre                      |

| Bloc Jedec 3         | EPROMS Vbug<br>LP5282,5283 | EPROMS Vbug<br>LP5288,5289 | EPROMS Vbug<br>LP5340,5341 | EPROMS Vbug<br>LP5336,5337 | EPROMS Vbug<br>LP5338,5339 |

| RAM<br>DYNAMIQUE     | NON                        | 1Moctets                   | 1 Moctets                  | 512Koctets                 | 2Moctets                   |

| Liaisons série       | RS232C                     | RS232C                     | RS232C                     | RS232C                     | RS232C                     |

| E/S parallèles       | Divers 75160,<br>MC3448A   |

| Contrôleur SCSI      | NON                        | OUI                        | OUI                        | NON                        | OUI                        |

| Contrôleur<br>Floppy | NON                        | OUI                        | OUI                        | NON                        | OUI                        |

| Horodateur           | OUI                        | OUI                        | OUI                        | OUI                        | OUI                        |

### 2.2 - DESCRIPTION DE LA CARTE

## 2.2.1 - Caractéristiques

| Fonction                  | SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| UNITE CENTRALE            |                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| MICROPROCESSEUR           | 68000 à 8 MHz<br>Option 68010 10 MHz ou 12,5 MHz                                                                                                                                                                                                                                                                                                                       |  |  |  |

| MEMOIRE                   |                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| RAM, EEPROM, EPROM        | 4 blocs de 2 supports Jedecs 32 broches dont : 3 blocs de 2 supports Jedecs 32 broches configurables par goutte de soudure                                                                                                                                                                                                                                             |  |  |  |

| Option RAM DYNAMIQUE      | 1 bloc de 2 supports Jedecs 32 broches dédié Eproms Tous ces blocs sont montés en bus 16 bits de données Les Temps d'accès maximum des composants sont programmables:  CPU 68000 68010 68010 8MHz 10MHz 12.5MHz Ram, Eeprom 0wst 50ns 100ns 80ns 1 wst 300ns 200ns 150ns Eprom 0wst 250ns 200ns 150ns 1 wst 400ns 300ns 250ns 512 Koctets, 1 Moctets ou 2 Moctets avec |  |  |  |

|                           | contrôle de parité - 1 wait state max. hors rafraîchissement                                                                                                                                                                                                                                                                                                           |  |  |  |

| GESTION DES INTERRUPTIONS |                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                           | Gestion des 7 niveaux VME et 7 niveaux locaux                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                           | Interruptions masquables par logiciel                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                           | Sélection des niveaux des interruptions locales                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                           | Toutes les interruptions locales sont auto-<br>vectorisées                                                                                                                                                                                                                                                                                                             |  |  |  |

| ГОИСТІОН               | SPECIFICATIONS                                                                                                             |  |  |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CHIEN DE GARDE         | CHIEN DE GARDE                                                                                                             |  |  |  |  |

|                        | - Compteur pouvant être relancé soit par<br>un signal de P2, soit par accès logiciel<br>interne                            |  |  |  |  |

|                        | - Sortie du chien de garde accessible sur P2<br>et pouvant provoquer soit une inter-<br>ruption, soit un reset de la carte |  |  |  |  |

|                        | - 2 modes de déclenchement :                                                                                               |  |  |  |  |

|                        | <ol> <li>pas de relance du comptage pendant<br/>un temps max.</li> </ol>                                                   |  |  |  |  |

|                        | 2. idem 1 + relance pendant un délai<br>inférieur à temps max/2                                                            |  |  |  |  |

|                        | - Temps max sélectable par wrapping : 0,25, 0,5, 1 ou 2 s.                                                                 |  |  |  |  |

| MODULE DE SURVEILLANCE |                                                                                                                            |  |  |  |  |

|                        | Bus time out désélectable par logiciel                                                                                     |  |  |  |  |

| FONCTION                   | SPECIFICATIONS                                                                                                                                                     |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PERIPHERIQUES LOCAUX       |                                                                                                                                                                    |

| Liaisons série             | 1 liaison asynchrone RS232C                                                                                                                                        |

|                            | 1 liaison synchrone / asynchrone, RS232C ou TTL contrôleur Z8530                                                                                                   |

|                            | Liaisons disponibles en face avant connecteurs 9 points et sur P2                                                                                                  |

| Timer                      | 3 timers programmables et cascadables 68B40 un timer accessible sur P2                                                                                             |

| Entrées/sorties parallèles | - 2 ports 8 bits et 4 signaux de contrôle du<br>PIT 68230                                                                                                          |

|                            | - sortie directe sur P2 ou interface bidirec-<br>tionnelle avec drivers 75160 et MC3948A                                                                           |

| Option : Contrôleur SCSI   | Bus SCSI sur P2.ANSI SCSI X3T9.2<br>Contrôleur WD33C93<br>Résistances de terminaison sur la carte                                                                  |

| Option : Contrôleur floppy | Interface "Floppy disk" sur P2<br>Contrôleur WD37C65                                                                                                               |

|                            | - jusqu'à 4 floppy ou microfloppydisk (TM)                                                                                                                         |

|                            | - 125, 250, et 500 Kbits/sec en vitesse de transfert des données                                                                                                   |

| Module utilisateur         | L'utilisateur peut développer un module spécifique à monter sur la carte TSVME110                                                                                  |

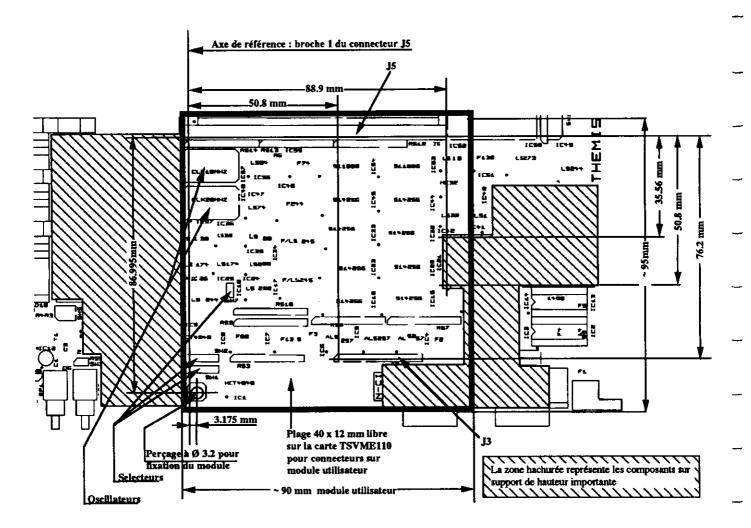

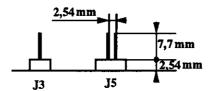

|                            | <ul> <li>le connecteur J5 2x35 pts fournit le bus du<br/>CPU local (Adr, données, contrôle) les<br/>horloges, un CSMOD* et une ligne<br/>d'interruption</li> </ul> |

|                            | - le connecteur J3 12 pts permet de se relier<br>à 8 points du connecteur P2 et fournit les<br>alimentations + et -12V                                             |

| FONCTION                   | SPECIFICATIONS                                                                                                                                                                                      |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTERFACE VME              |                                                                                                                                                                                                     |

| Compatibilité              | ANSI/IEEE STD1014 - 1987                                                                                                                                                                            |

| Type de carte              | Maître                                                                                                                                                                                              |

| Arbitre VME                | 1 niveau<br>Sélectable par goutte de soudure                                                                                                                                                        |

| Demandeur VME              | Type "Release on Request" (ROR)<br>Niveau sélectable par wrapping                                                                                                                                   |

| Transferts de données      | A24:D08 (EO) Lecture/Ecriture RMW A24:D16 Lecture/Ecriture                                                                                                                                          |

| Module de surveillance     | Bus Time Out désélectable par logiciel                                                                                                                                                              |

| Contrôleur d'interruptions | Gestion des 7 niveaux VME                                                                                                                                                                           |

| Horloge système            | Génération de SYSCLK, désélectable                                                                                                                                                                  |

| Reset système              | Génération ou réception de SYSRESET* désélectables                                                                                                                                                  |

| Défaut système             | Génération par logiciel de sysfail*<br>réception désélectable (par goutte de<br>soudure) de sysfail*                                                                                                |

| Défaut secteur             | Réception de ACFAIL*                                                                                                                                                                                |

| Connecteurs VME utilisés   | P1                                                                                                                                                                                                  |

|                            | Les 3 rangées de P2 sont utilisées pour les interfaces des périphériques locaux.                                                                                                                    |

|                            | La carte TSVME110 avec les options contrôleurs SCSI et floppy ne peut pas être montée dans un rack VME à un emplacement comportant sur P2 un fond de panier pour l'extension du bus VME en 32 bits. |

| Fonction                                                | SPECIFICATIONS                                                                                                  |  |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| FACE AVANT                                              |                                                                                                                 |  |  |  |

| LEDS Afficheur Boutons poussoirs Connecteurs SUBD 9 pts | HALT, FAIL et 3 Leds utilisateur Décimal 7 segments + point. Reset, Abort 2 connecteurs pour les liaisons série |  |  |  |

| ENVIRONNEMENT ELECTRIQUE                                |                                                                                                                 |  |  |  |

| ALIMENTATIONS                                           | +5Vdc -2,5% +5%<br>+12Vdc -3% +5%<br>-12Vdc -3% +5%                                                             |  |  |  |

| CONSOMMATIONS                                           | +5V 3,5A Max. avec DRAM, FLOPPY, SCSI<br>+12V 50mA Max.<br>-12V 50mA Max.                                       |  |  |  |

| ENVIRONNEMENT CLIMATIQUE                                |                                                                                                                 |  |  |  |

| TEMPERATURE: - Fonctionnement - Stockage                | 0 à 60° C<br>- 40 à +85° C                                                                                      |  |  |  |

| HUMIDITE RELATIVE                                       | 0 à 95 % sans condensation.                                                                                     |  |  |  |

| CARACTERISTIQUES MECANIQUES                             |                                                                                                                 |  |  |  |

| FORMAT                                                  | Double Europe 160 X 233,3 mm (6,29 x 9,18 inches)                                                               |  |  |  |

| EPAISSEUR                                               | un emplacement VME                                                                                              |  |  |  |

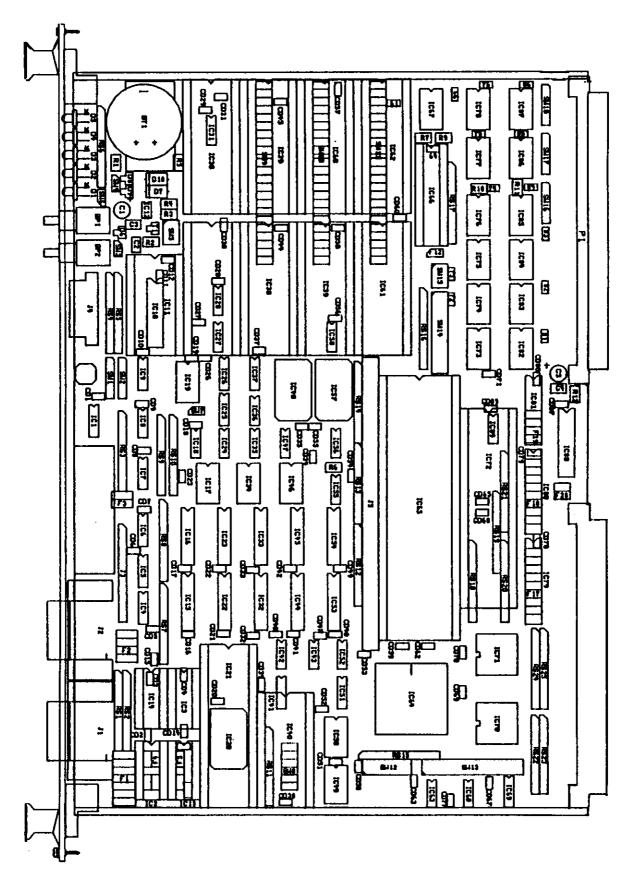

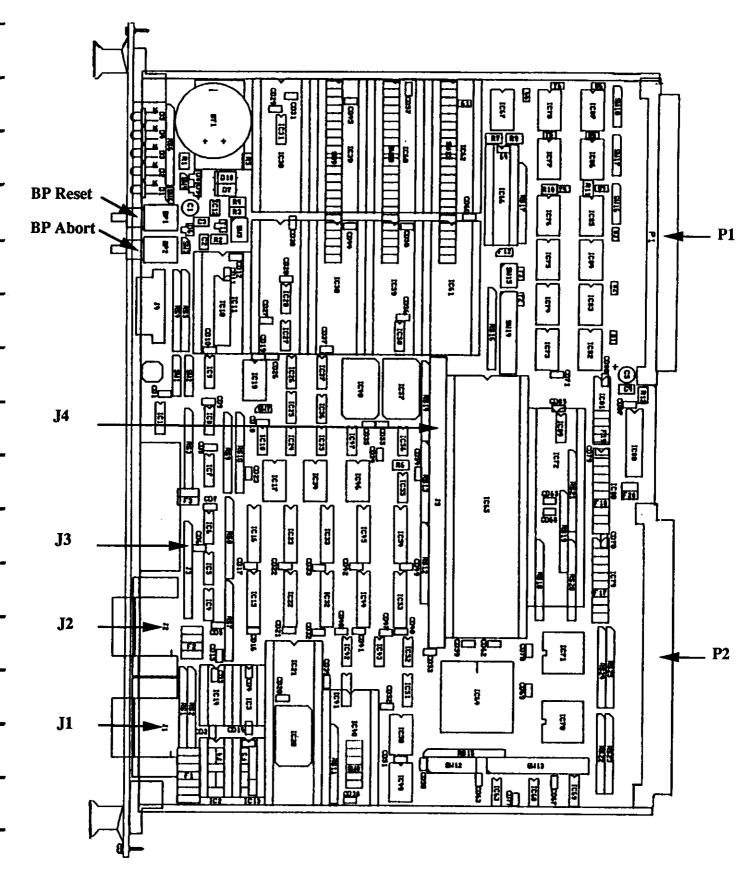

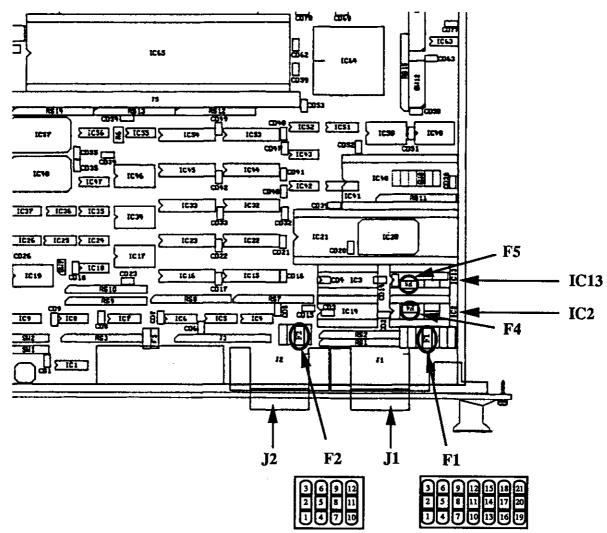

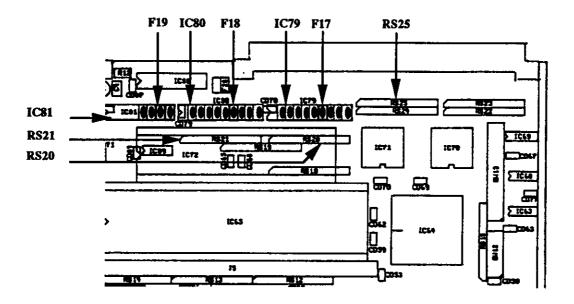

#### 2.2.3 - Plan d'implantation

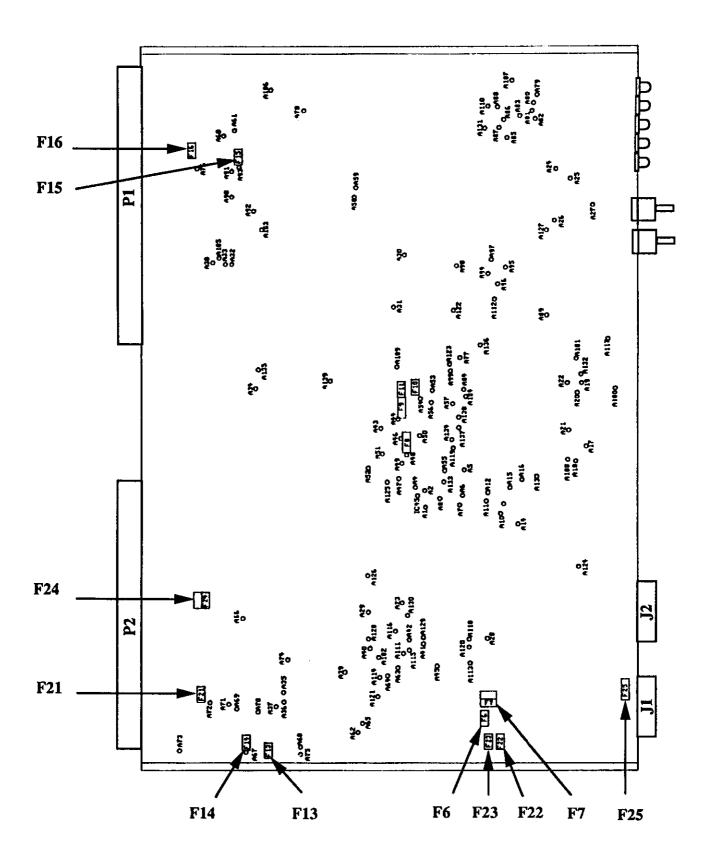

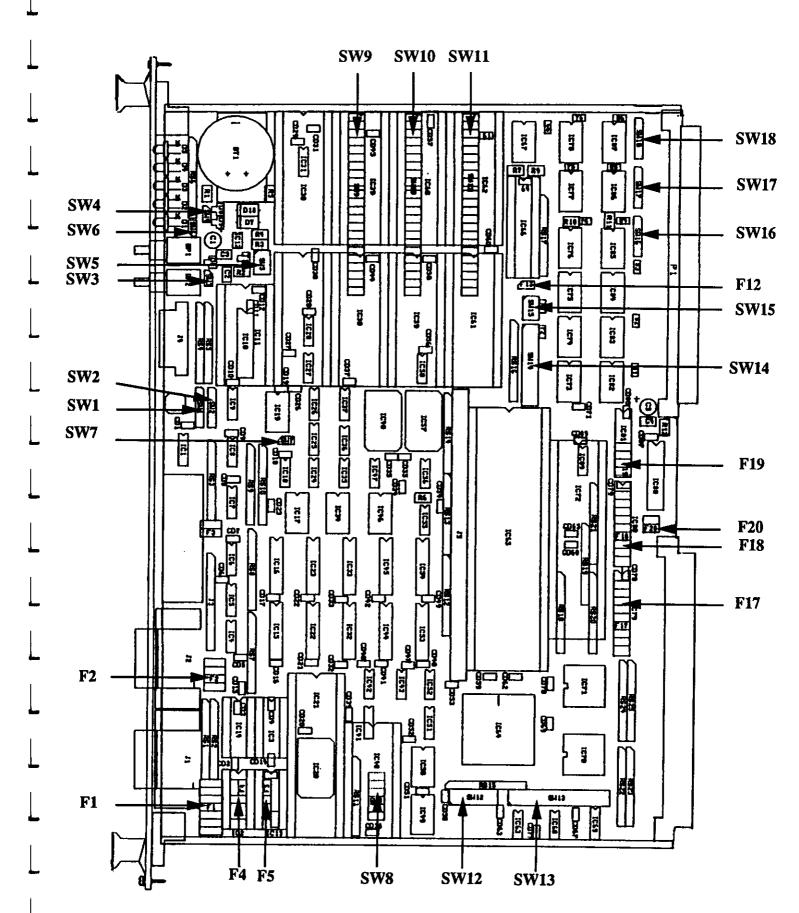

#### 2.2.4 - Connecteurs et sélecteurs

#### CONNECTEURS

| Repère | Utilisation                                                  | Remarques                                                                                                                                      | Paragra<br>phe                                                    |

|--------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| J1     | Liaison série Canal 2<br>RS232C/TTL.<br>Synchrone/Asynchrone | SubD 9 pts femelle                                                                                                                             | 3.8.2                                                             |

| J2     | Liaison série Canal 1<br>RS232C Asynchrone                   | SubD 9 pts femelle                                                                                                                             | 3.8.2                                                             |

| J3     | Connecteur module utilisateur                                | 1x 12 pts. I/O vers P2                                                                                                                         | 3.9.2                                                             |

| J5     | Connecteur module utilisateur                                | 2x 25 pts. Bus CPU + Contrôle                                                                                                                  | 3.9.2                                                             |

| P1     | Connecteur bus VME                                           |                                                                                                                                                | 3.7                                                               |

| P2     | Connecteur I/O périphériques                                 | Liaisons série Canal 1, Canal 2<br>E/S parallèles<br>Timer<br>Chien de garde<br>Bus SCSI<br>Interface floppy<br>Module utilisateur<br>Ensemble | 3.8.2<br>3.8.3<br>3.8.1<br>3.6.4<br>3.8.4<br>3.8.5<br>3.9<br>3.10 |

#### **SELECTEURS**

| Repère | Utilisation                                              | Remarques                      | Paragra<br>phe      |

|--------|----------------------------------------------------------|--------------------------------|---------------------|

| SW1,2  | Sélection délai Chien de garde                           |                                | 3.6.4               |

| SW3    | Validation BP Reset*                                     | Cavalier                       | 3.6                 |

| SW4    | Batterie/pile                                            | Valide charge batterie         | 3.2.4               |

| SW5    | Configuration bloc Jedecs 3                              | Eproms                         | 3.2.2.2             |

| SW6    | Validation sauvegarde batterie                           |                                | 3.2.4               |

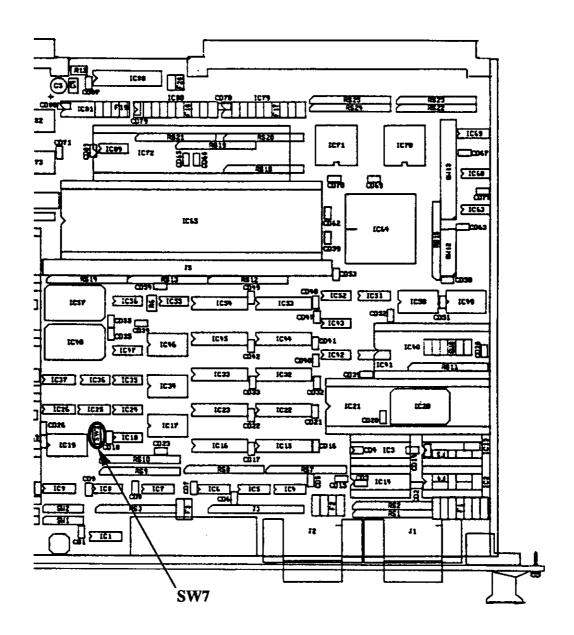

| SW7    | Mode autotest                                            |                                | 3.5.2               |

| SW8    | Configuration Timer 3                                    |                                | 3.8.1               |

| SW9    | Configuration bloc Jedecs 2                              | Blocs Ram statique Eeprom,     |                     |

| SW10   | Configuration bloc Jedecs 1                              | Eprom                          |                     |

| SW11   | Configuration bloc Jedecs 0                              |                                | 3.2.2.1             |

| SW12   | Configuration mémoire                                    |                                | 3.1                 |

| SW13   | Configuration interface Floppy                           |                                | 3.2 et 3.3<br>3.8.5 |

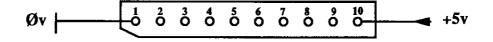

| SW14   | Sélection niveaux IT locales<br>et action chien de garde | 2x9pts - Cavaliers ou wrapping | 3.4<br>3.6.4        |

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

| Repère               | Utilisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Remarques          | Para<br>graphe |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|

| SW15                 | Reset VME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    | 3.6.1          |

| SW16<br>SW17<br>SW18 | \ > Choix du niveau de requête et / d'arbitrage du bus VME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    | 3.7.2          |

| F1                   | Configuration liaison série Canal 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | modem/terminal     | 3.8.2          |

| F2                   | Configuration Liaison série canal 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | modem/terminal     | 3.8.2          |

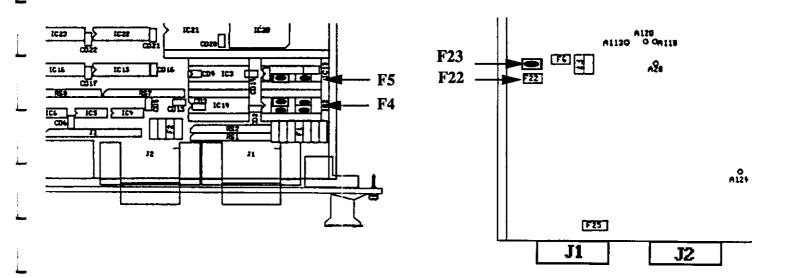

| F4,F5                | RS232C/TTL liaison série Canal 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    | 3.8.2          |

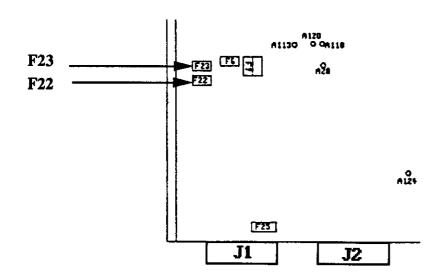

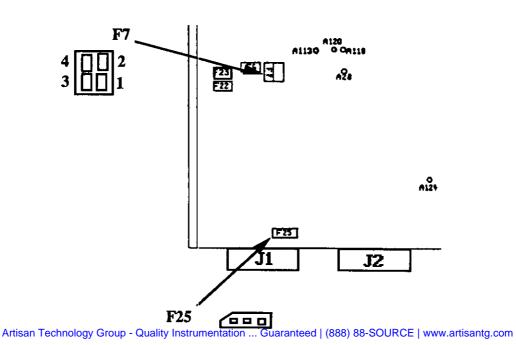

| F7                   | Sélection Horloge duart Canal 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    | 3.8.2          |

| F12                  | Arbitre/demandeur VME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    | 3.7.2          |

| F13                  | Validation "DISK Change"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    | 3.8.5          |

| F14                  | Entrée Reset bus SCSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    | 3.8.4          |

| F15                  | Validation Réception SYSFAIL*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    | 3.6.3          |

| F16                  | Validation SYSCLK sur le VME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    | 3.7.4          |

| F17<br>F18<br>F19    | > I/O Parallèles<br>/ Buffers ou sortie directe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    | 3.8.3          |

| F20                  | Sélection Relance Chien de garde                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    | 3.6.4          |

| F21                  | Sélection DRV (0/1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.8.5.3        |

| F22<br>F23           | Configuration du signal S2TXC     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     /     / |                    | 3.8.2.1        |

| F24                  | Configuration SCSI REQ sur P2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    | 3.8.4.4        |

| F25                  | Configuration de mise à la masse des capôts des connecteurs des E/S série                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    | 3.8.2          |