In Stock

**Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/65243-2

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

ARTISAN'

TECHNOLOGY GROUP

Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

- Critical and expedited services

- In stock / Ready-to-ship

- We buy your excess, underutilized, and idle equipment

- Full-service, independent repair center

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# Intel<sup>®</sup> NetStructure<sup>™</sup> ZT 5550 High Availability Processor Board

Hardware User Manual

#### **Revision History**

| Revision<br>Date | Revision History                                  |

|------------------|---------------------------------------------------|

| 12/17/01         | ZT 5550 Revision D release. Global format update. |

Copyright © 2001, Intel Corporation. All rights reserved.

Intel Corporation 5200 N.E. Elam Young Parkway Hillsboro, OR 97124-6497

Intel Corporation assumes no responsibility for errors or omissions in this document. Nor does Intel make any commitment to update the information contained herein.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel, Pentium, and NetStructure are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other brands and names may be claimed as the property of others.

12/17/2001

## **Contents**

| Tables                                 | 8  |

|----------------------------------------|----|

| Figures                                | 9  |

| Manual Organization                    | 10 |

| 1. Introduction                        | 12 |

| Product Definition                     | 12 |

| Features                               | 15 |

| Functional Blocks                      | 16 |

| High Availability                      | 16 |

| CompactPCI Bus Interface               | 17 |

| Rear-Panel I/O                         | 17 |

| Dual CompactPCI System Slot Interfaces | 18 |

| Intel Pentium III Processor            | 18 |

| I/O Expansion Connector                | 19 |

| SMBus (Alarming Functions)             | 19 |

| AGP Mezzanine                          | 19 |

| PCI Mezzanine                          | 20 |

| Dual Ethernet Interfaces               | 20 |

| Memory and I/O Addressing              | 20 |

| Serial I/O                             | 21 |

| Interrupts                             | 21 |

| Counter/Timers                         | 22 |

| DMA                                    | 22 |

| Real-Time Clock                        | 23 |

| Power Ramp Circuitry                   | 23 |

| Reset                                  | 23 |

| Two-Stage Watchdog Timer               | 24 |

| Universal Serial Bus (USB)             | 24 |

| Enhanced IDE Controller                | 24 |

| Floppy Controller                      | 24 |

| Keyboard Controller                    | 25 |

| Mouse                                  | 25 |

| Speaker Interface                      | 25 |

| LED Indicators                         | 25 |

| Software                               | 27 |

| 2. Getting Started                                                 | 28 |

|--------------------------------------------------------------------|----|

| Unpacking                                                          | 28 |

| System Requirements                                                | 28 |

| Connectivity                                                       | 28 |

| Electrical and Environmental Requirements                          | 29 |

| Switches and Cuttable Traces                                       | 29 |

| Memory Configuration                                               | 29 |

| I/O Configuration                                                  | 30 |

| Programming the LEDs                                               | 32 |

| Video Interface Selection                                          | 33 |

| Removing Mezzanine Boards                                          | 33 |

| BIOS Configuration Overview                                        | 33 |

| Console Redirection                                                | 34 |

| Identifying Media Options                                          | 35 |

| 3. Configuration                                                   | 36 |

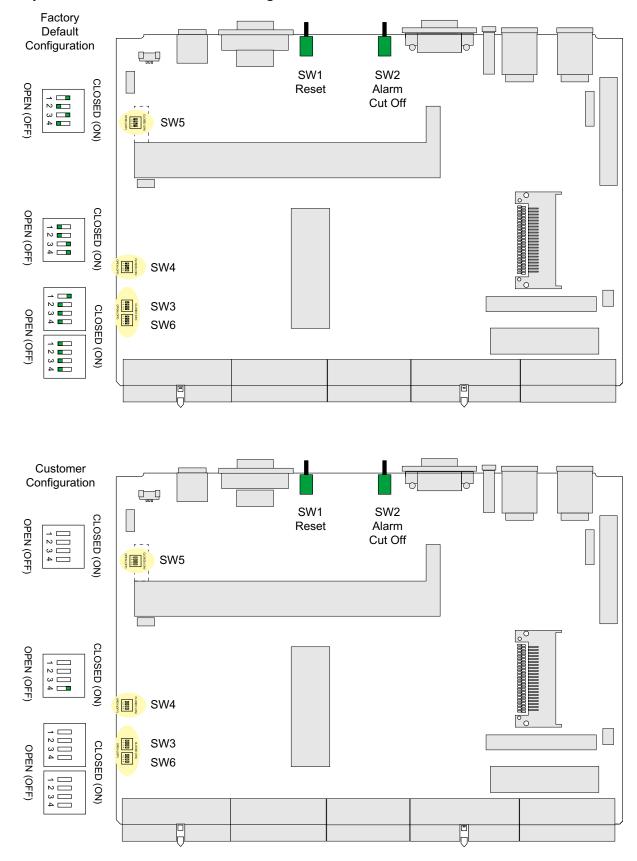

| Switch Options and Locations                                       | 36 |

| Switch Descriptions                                                | 38 |

| SW1 (Reset)                                                        | 38 |

| SW2 (Alarm Cut Off)                                                | 38 |

| SW3-1, -2 (CMOS Clear/Battery Backup)                              | 38 |

| SW3-3 (SRAM Battery Backup)                                        | 38 |

| SW3-4 (Soft Reset Mode Select)                                     | 39 |

| SW4-1, -2 (Ethernet Channel/Port Select)                           | 40 |

| SW4-3 (Configuration Mode Preset)                                  | 40 |

| SW4-4 (Reserved)                                                   | 40 |

| SW5-1 (BIOS Recovery)                                              | 41 |

| SW5-2 (Port 80 Test Mode)                                          | 41 |

| SW5-3 (IDE Master/Slave Selection)                                 | 41 |

| SW5-4 (Flash Write-Protect)                                        | 42 |

| SW6-1 (Console Redirection)                                        | 42 |

| SW6-2, -3, -4 (Software Configuration)                             | 42 |

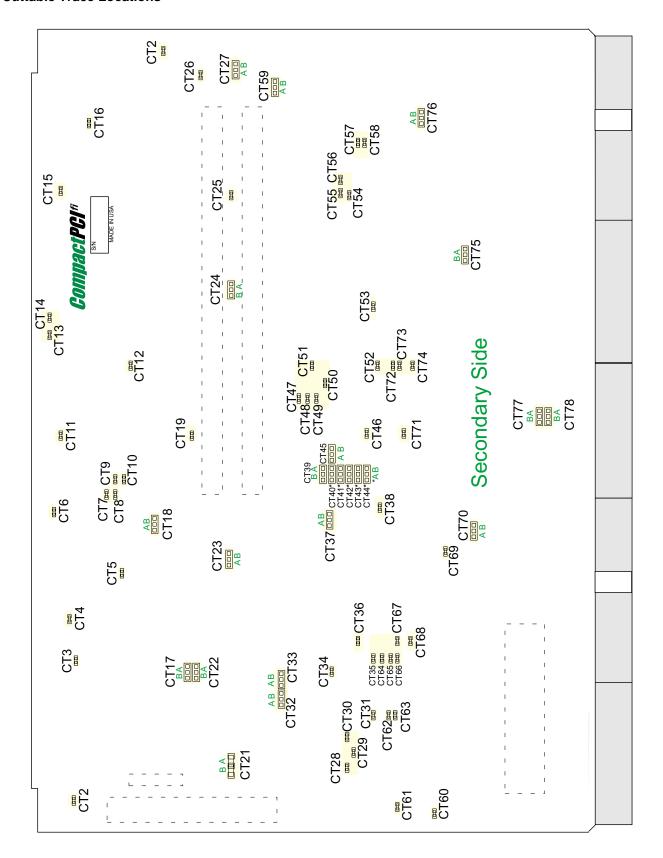

| Cuttable Trace Options and Locations                               | 43 |

| Cuttable Trace Descriptions                                        | 45 |

| CT2-4, CT6, CT11, CT13-15, CT20 (Connect Chassis GND to Logic GND) | 45 |

| CT7-CT10 (Reserved)                                                | 45 |

| CT12 (Floppy DRATE0 to MSEN0)                                      | 45 |

| CT27 (FAN Voltage Selection)                                       | 46 |

| CT79 (CompactFlash Socket Voltage Select) | 46 |

|-------------------------------------------|----|

| 4. High Availability                      | 47 |

| Core Technology Approach                  | 47 |

| Modes of Operation                        | 48 |

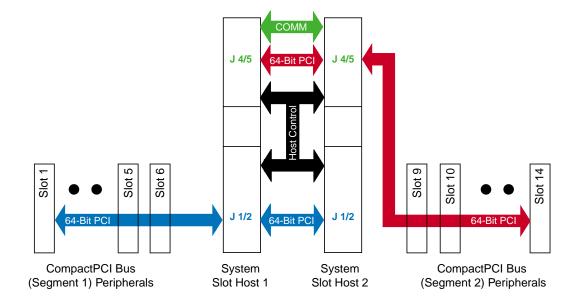

| System Backplane                          | 48 |

| System CPUs                               | 49 |

| Software Considerations                   | 50 |

| Frequently Asked Questions                | 53 |

| 5. Hot Swap                               | 57 |

| What is Hot Swap?                         | 57 |

| Definition of Hot Swap Terminology        | 57 |

| 6. Reset                                  | 59 |

| Reset Types and Sources                   | 59 |

| Master Reset Sources                      | 59 |

| Backend Power Down Sources                | 60 |

| Hard Reset Sources                        | 60 |

| Soft Reset Sources                        | 61 |

| NMI Sources                               | 62 |

| 7. System Monitoring and Alarms           | 63 |

| SMBus Address Map                         | 63 |

| 8. Enhanced IDE Controller                | 64 |

| Features of the EIDE Controller           | 64 |

| Disk Drive Support                        | 64 |

| Internal Disks                            | 64 |

| External Disks                            | 65 |

| I/O Mapping                               | 65 |

| CompactFlash Option                       | 65 |

| CompactFlash Input Characteristics        | 65 |

| Device Drivers                            | 66 |

| 9. Watchdog Timer                         | 67 |

| Watchdog Timer Operation                  | 67 |

| Power Up Initialization                   | 67 |

| Time Out Values                           | 68 |

| Using the Watchdog in an Application      | 68 |

| Watchdog Reset                            | 68 |

| Watchdog NMI                              | 69 |

| Watchdog INIT                             | 71 |

| 10. Timers                                  | 72  |

|---------------------------------------------|-----|

| Timer Operation                             | 72  |

| Loading the Counter                         | 72  |

| 11. Flash Memory and SRAM                   | 74  |

| Flash                                       | 74  |

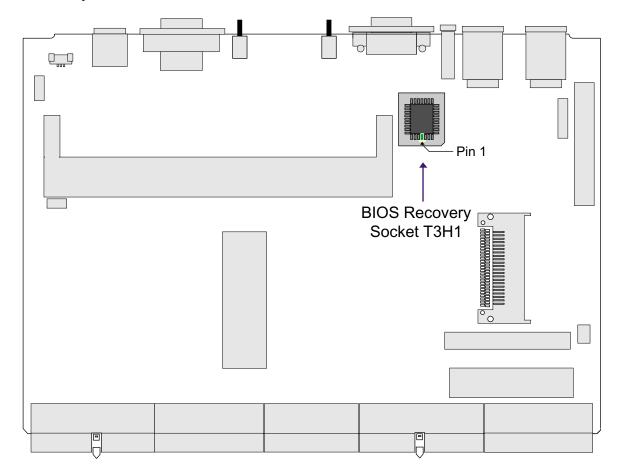

| BIOS Recovery Module                        | 75  |

| Flash Utility Program                       | 75  |

| SRAM                                        | 76  |

| A. Specifications                           | 77  |

| Electrical and Environmental Specifications | 77  |

| Absolute Maximum Ratings                    | 77  |

| DC Operating Characteristics                | 78  |

| Battery Backup Characteristics              | 78  |

| Reliability                                 | 78  |

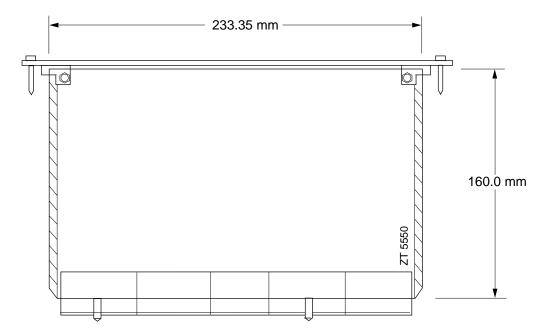

| Mechanical Specifications                   | 78  |

| Board Dimensions and Weight                 | 79  |

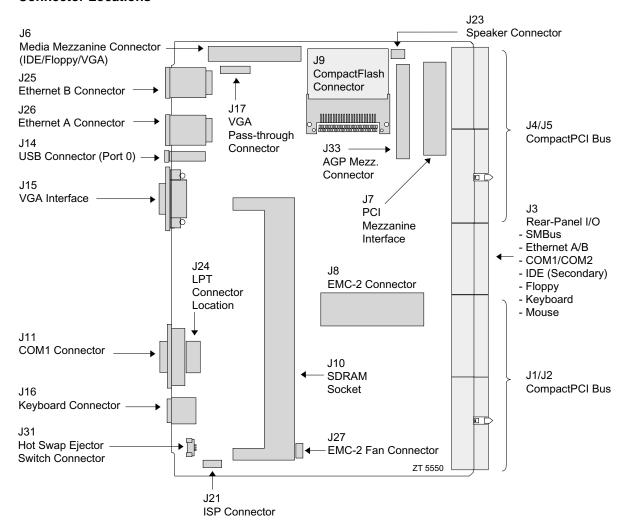

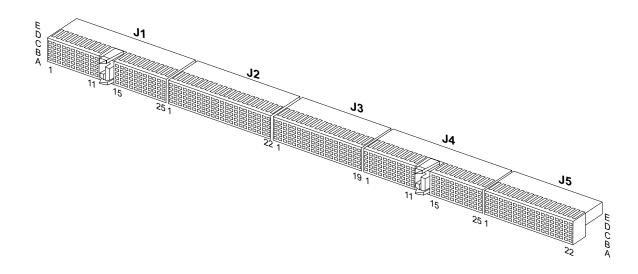

| Connectors                                  | 80  |

| B. Thermal Considerations                   | 95  |

| Thermal Requirements                        | 95  |

| Heat Pipe Temperature Range                 | 95  |

| Thermal Verification                        | 96  |

| Temperature Monitoring                      | 96  |

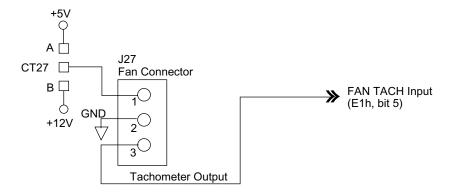

| Tachometer Monitoring                       | 97  |

| C. System Registers                         | 98  |

| System Register Definitions                 | 98  |

| System Register 1 (78h)                     | 99  |

| System Register 2 (79h)                     | 100 |

| System Register 3 (E1h)                     | 102 |

| System Register 4 (E2h)                     | 102 |

| System Register 5 (E3h)                     | 103 |

| System Register 6 (E4h)                     | 104 |

| System Register 7 (E5h)                     | 104 |

| ZT 4804 RPIO SMBus Registers                | 105 |

| ZT 4804 SMBus Output Register               | 105 |

| ZT 4804 SMBus Input Register                | 105 |

| D. Agency Approvals                         | 106 |

| UL 1950 Certification                       | 106 |

|      | CE Certification                                    | 106 |

|------|-----------------------------------------------------|-----|

|      | FCC Regulatory Information                          | 107 |

| E. [ | Data Sheet Reference                                | 108 |

|      | AGP Video                                           | 108 |

|      | Board Serial # ID                                   | 108 |

|      | CompactFlash                                        | 108 |

|      | CompactPCI                                          | 108 |

|      | Ethernet                                            | 108 |

|      | Hot Swap                                            | 109 |

|      | PCI-to-PCI Bridge                                   | 109 |

|      | Pentium III Processor                               | 109 |

|      | PIIX4                                               | 109 |

|      | SDRAM                                               | 110 |

|      | SuperI/O                                            | 110 |

|      | Thermal                                             | 110 |

|      | User Documentation                                  | 111 |

| F. ( | Customer Support                                    | 112 |

|      | Technical Support and Return for Service Assistance | 112 |

|      | Sales Assistance                                    | 112 |

|      | Warranty Information                                | 112 |

## **Tables**

| Revision History                                  | 2  |

|---------------------------------------------------|----|

| SMBus Isolation Control                           | 19 |

| COM1 Isolation Control                            | 21 |

| Media Options                                     | 35 |

| Switch Cross-Reference Table                      | 36 |

| Cuttable Trace Definitions                        | 43 |

| CompactFlash Input Characteristics Table          | 66 |

| Flash                                             | 74 |

| SRAM:                                             | 74 |

| BIOS Recovery Module:                             | 74 |

| Connector Assignments                             | 80 |

| J1 CompactPCI Bus Connector Pinout                | 82 |

| J2 CompactPCI Bus Connector Pinout                | 83 |

| J3 Rear-Panel User I/O Connector Pinout           | 84 |

| J4 CompactPCI Bus Connector Pinout                | 85 |

| J5 CompactPCI Bus Connector Pinout                | 86 |

| J6 I/O Expansion Connector Pinout                 | 87 |

| J7 PCI Mezzanine Interface Connector Pinout       | 88 |

| J11 COM1 Serial Port Pinout                       | 89 |

| J14 Universal Serial Bus Connector Pinout         | 89 |

| J15 VGA Interface Pinout                          | 90 |

| J16 Keyboard Connector Pinout                     | 90 |

| J17 Video Mezzanine Pass-Through Connector Pinout | 91 |

| J23 Speaker Connector Pinout                      | 91 |

| J25/J26 Ethernet Connectors Pinout                | 92 |

| J27 Fan Sink Power Connector Pinout               | 92 |

| J31 Hot Swap Ejector Switch Connector Pinout      | 92 |

| J33 AGP Video Mezzanine Interface Pinout          | 93 |

## **Figures**

| ZT 5550 Revision C and Earlier Faceplate          | 13 |

|---------------------------------------------------|----|

| ZT 5550 Revision D and Later Faceplate            | 14 |

| Functional Block Diagram                          | 17 |

| Memory Address Map Example                        | 30 |

| I/O Address Map                                   | 31 |

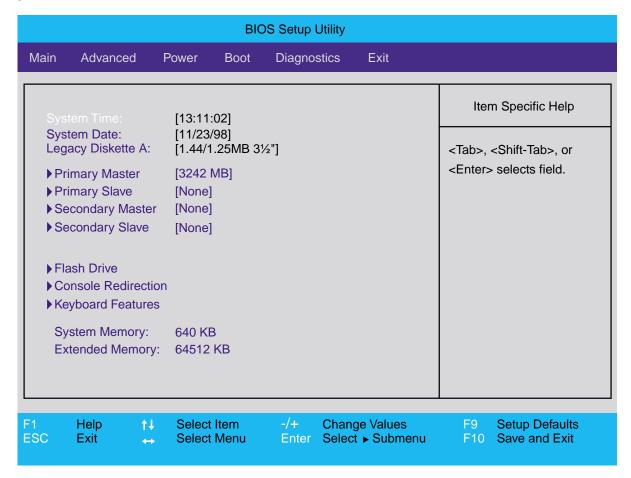

| Setup Screen                                      | 34 |

| Factory Default and Customer Switch Configuration | 37 |

| Cuttable Trace Locations                          | 44 |

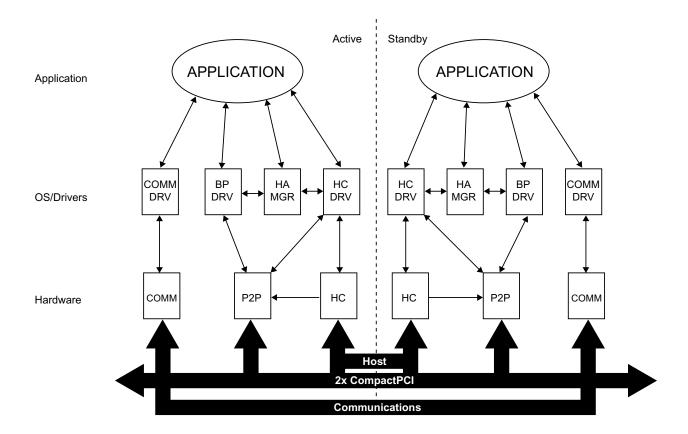

| HA System Backplane Architecture                  | 48 |

| HA CPU Architecture                               | 49 |

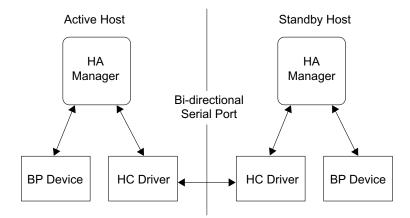

| Inter-Host Communication Architecture             | 50 |

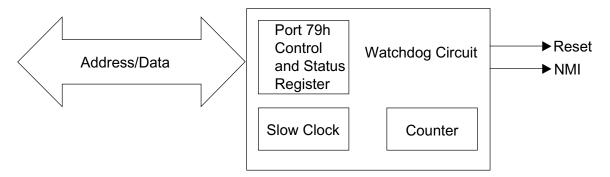

| Watchdog Timer Architecture                       | 67 |

| BIOS Recovery Socket Location                     | 76 |

| Board Dimensions                                  | 79 |

| Connector Locations                               | 81 |

| Backplane Connectors Pin Locations                | 81 |

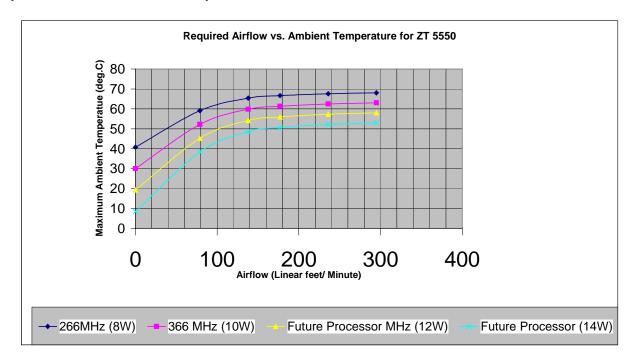

| Required Airflow vs. Ambient Temperature          | 96 |

| Tachometer Monitoring Input Circuitry             | 97 |

### **Manual Organization**

This manual describes the operation and use of the ZT 5550 High Availability Processor Board. Pre-configured systems such as the ZT 5083 High Availability System are available from Intel for applications requiring 99.999% availability. Refer to the *Intel® NetStructure™ ZT 5083 15U High Availability Platform* data sheet available on Intel's website for additional information.

**Chapter 1, "Introduction,"** introduces the key features of the ZT 5550 CPU. It includes a product definition, a list of product features, a functional block diagram, and a brief description of each block. This chapter is most useful to those who wish to compare the features of the ZT 5550 against the needs of a specific application.

**Chapter 2, "Getting Started,"** provides setup information for the ZT 5550 and its optional boards. It summarizes what you need to know in order to install and configure the boards in your system and should be read before attempting to use the boards.

**Chapter 3, "Configuration,"** describes the switches and cuttable traces on the ZT 5550 CPU. This chapter details factory default settings and provides information allowing you to tailor your board to the needs of specific applications.

**Chapter 4, "High Availability,"** briefly describes the main hardware and software components of Intel's Redundant CPU Architecture for High Availability systems. A section on frequently asked questions (FAQ) is also provided.

**Chapter 5, "Hot Swap,"** defines many hot swap related terms, with emphasis on the Pin Staging and Power Ramping aspects of hot swappable applications.

Chapter 6, "Reset," explains how reset works on the ZT 5550.

**Chapter 7, "System Monitoring and Alarms,"** explains how to access various system monitoring devices and alarming functions on the ZT 5550 CPU and ZT 4804 RPIO Transition Board.

**Chapter 8, "Enhanced IDE Controller,"** provides an introduction to the ZT 5550's Enhanced IDE Interface Controller. It covers drive configuration, software device drivers, and the ZT 5550's support for CompactFlash IDE disk drives and optional remote drive(s).

**Chapter 9, "Watchdog Timer,"** explains the operation of the ZT 5550's watchdog timer used to monitor user applications. Sample code is provided to illustrate how the watchdog's functions are used in an application.

**Chapter 10, "Timers,"** explains the operation of the ZT 5550's two custom timers. These timers provide a unique 32-time stamp for use by telecommunications applications. These custom timers are distinct from the standard counter timers residing in the PIIX4 device.

**Chapter 11, "Flash Memory and SRAM,"** discusses on-board flash memory, battery-backed SRAM, and the BIOS Recovery Module. The FLASH.EXE utility program for reprogramming the BIOS is also discussed.

**Appendix A, "Specifications,"** contains the electrical, environmental, and mechanical specifications for the ZT 5550. It provides illustrations showing the connector locations and board dimensions, as well as connector pinouts.

**Appendix B, "Thermal Considerations,"** describes the thermal requirements for reliable operation of the ZT 5550. It covers basic thermal requirements, specifics about maintaining and verifying the heat pipe temperature, and details about monitoring the output of an optional fan-sink tachometer.

**Appendix C, "System Registers,"** provides detailed descriptions of the system and SMBus registers used to configure and monitor operation of the ZT 5550.

**Appendix D, "Agency Approvals,"** presents UL, CE, and FCC agency approval and certification information for the board.

**Appendix E, "Data Sheet Reference,"** provides links to data sheets for many of the devices located on the board.

**Appendix F, "Customer Support,"** offers technical assistance and warranty information, and the necessary information should you need to return your ZT 5550 for repair.

### 1. Introduction

This chapter provides a brief introduction to the ZT 5550. It includes a product definition, a list of product features, a "ZT 5550 Connector Plate" figure, a functional block diagram, and a description of each block. Unpacking information and initial board configuration instructions are provided in Chapter 2, "Getting Started."

See Chapter 3, "Configuration," for configuration details and Appendix A, "Specifications," for complete power and temperature requirements, as well as connector locations, descriptions, and pinout tables.

#### **Product Definition**

The ZT 5550 is an Intel Pentium III processor-based single board CompactPCI computer. Two ZT 5550 CPUs can be used on the same backplane, as an Active/Standby System Master pair, or as a Split Mode (Revision D and later boards) Standby System Master pair, to provide redundancy for the ZT 5083 and ZT 5084 High Availability (HA) Systems designed for mission-critical telecommunication and industrial control applications requiring 99.999% availability. The ZT 5083 and ZT 5084 systems incorporate redundant ZT 5550s, power supplies, and cooling fans in a single enclosure. Each ZT 5550 can be an Active, Standby, or Split Mode (Revision D and later boards) Host CPU. Resource management and database information is synchronized between the Active, Standby, and Split Mode (Revision D and later boards) Hosts via a bi-directional serial channel and an Ethernet\* channel.

The ZT 5550 utilizes the Intel Pentium III Processor Mobile Module: Embedded Module Connector 2 (EMC-2) to provide extremely high PCI performance and the latest in memory and I/O technology. An active ZT 5550 is designed to function in the System Slot controlling the CompactPCI backplane.

Each ZT 5550 supports attachment of an optional 6U I/O Expansion Board (such as the ZT 96072 or ZT 96073). I/O Expansion boards (IOX) are designed to greatly expand the I/O capability of the ZT 5550. Rear-panel access to the CPU/IOX combination can be provided by rear-panel I/O (RPIO) transition boards (such as the ZT 4804 and ZT 4802).

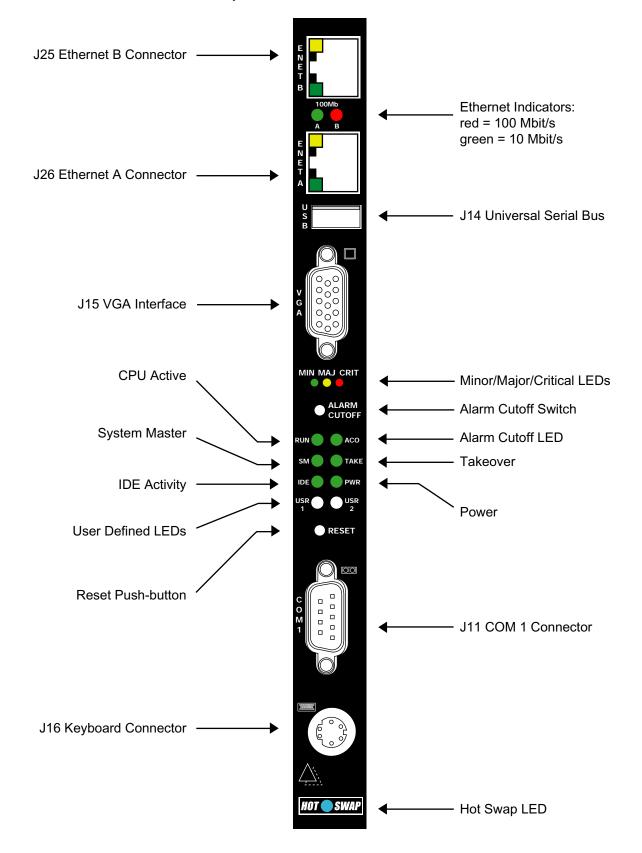

#### **ZT 5550 Revision C and Earlier Faceplate**

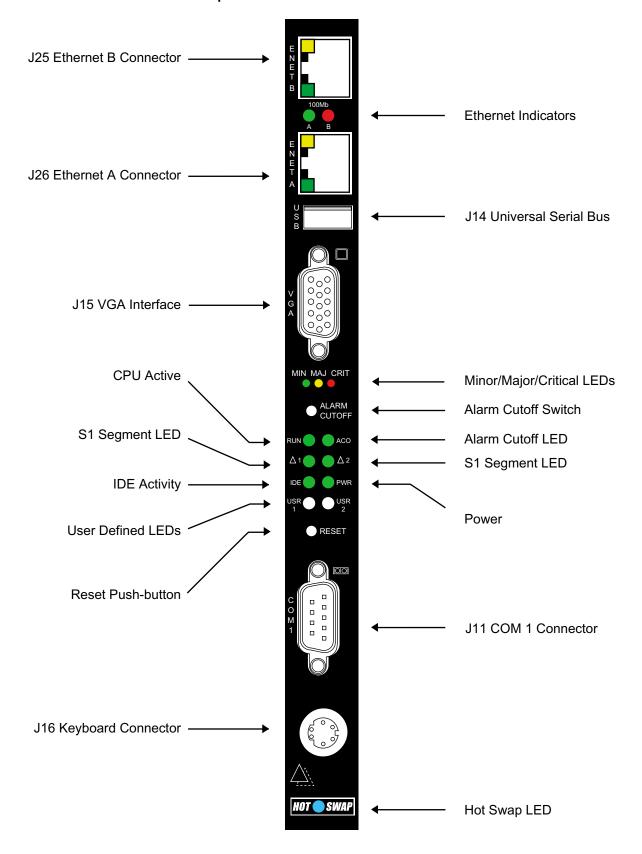

#### ZT 5550 Revision D and Later Faceplate

#### **Features**

- Acts as a CompactPCI System Slot device in either HA or non-HA systems. Up to 14 peripheral devices (assumes non-HA system) can reside on dual CompactPCI bus segments

- CompactPCI Specification, PICMG \* 2.0, Version 3.0 compliant

- CompactPCI Hot Swap Specification, PICMG 2.1, Version 2.0 compliant as a 5V platform component

- Intel Pentium III Processor Mobile Module (EMC-2)

- Single 6U CompactPCI slot form factor (two slots with ZT 96072 or ZT 96073 IOX board)

- Built-in numeric coprocessor support (Intel Pentium III)

- 16 KB of CPU instruction cache

- 16 KB of CPU data cache

- 512 KB pipelined burst L2 cache

- PCI mezzanine interface (Primary PCI bus)

- Dual 10/100 Mbit/s Ethernet interfaces

- Supports 64-bit PCI segment-to- segment transfers between the dual backplane bus segments.

- Supports 64, 128, or 256 MB of ECC SDRAM in a 168-pin DIMM socket in a single CompactPCI slot

- 4 MB of flash memory

- 128 KB of battery-backable SRAM

- CompactFlash memory socket

- Standard AT<sup>\*</sup> peripherals include:

- Two enhanced interrupt controllers (8259)

- Three counter/timers (one 8254)

- Real-time clock/CMOS RAM (146818)

- Two enhanced DMA controllers (8237)

- 8042 compatible keyboard controller

- Two 16C550 RS-232 serial ports (COM1 at front panel, COM1 and COM2 at rear panel)

- Universal Serial Bus (USB)

- System Management Bus (SMBus)

- Two Stage Programmable Watchdog Timer

- Additional 32-bit and 16-bit programmable Timers

- Push-button reset

- Software programmable LEDs

- DC power monitors (3.3V and 5V)

- I/O expansion options

- Five-year warranty

#### **Functional Blocks**

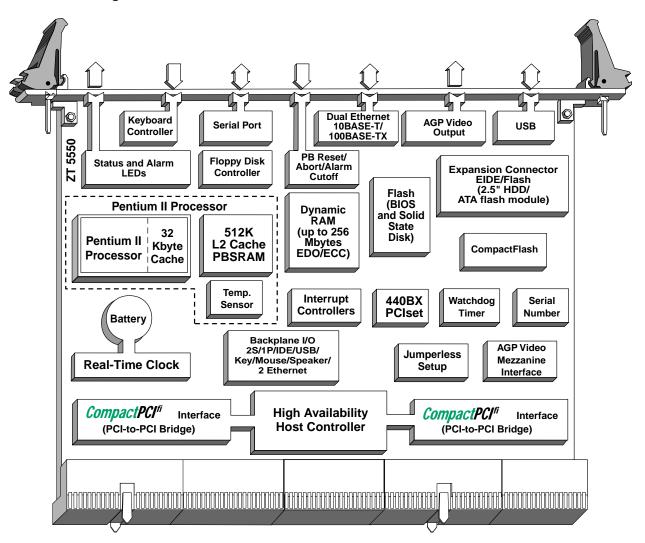

Below is a functional block diagram of the ZT 5550. The following topics provide overviews of the ZT 5550's functional blocks.

### **High Availability**

Intel's High Availability architecture incorporates redundant ZT 5550 CPUs, power supplies, and cooling fans in a single enclosure. The redundant CPU is in "hot standby" mode backing up the Active CPU. Resource management and data base information is synchronized between the Active and the Standby Hosts via a bi-directional serial channel and an ENET channel. The system minimizes duplication of expensive peripherals through an N+1 hot swappable peripheral board architecture. The additional (+1) 'standby' peripheral is online and ready for use should another peripheral fail.

Each redundant ZT 5550 provides a communications channel (COMM) for inter-CPU messaging, fault detection, and data base synchronization. It is based on 100Mbps Ethernet hardware and utilizes a standard communications driver (COMM DRV).

Interface to the dual CompactPCI buses is provided by PCI-to-PCI (P2P) bridges. The Host Controller (HC) controls these bridges such that the P2P on the Standby CPU is isolated from the backplane. Arbitration of the CompactPCI buses is provided by additional logic within the HC.

See Chapter 4, "High Availability," for more details.

#### **Functional Block Diagram**

### **CompactPCI Bus Interface**

The ZT 5550 operates in a 6U CompactPCI system. The CompactPCI standard is electrically identical to the PCI local bus standard but has been enhanced to support rugged industrial environments and more slots. Additionally, when used in a Hot Swap compliant backplane and in accordance with the *CompactPCI Hot Swap Specification*, *PICMG 2.1*, *Version 2.0*, the ZT 5550 supports hosting hot swappable peripherals in a powered system. The ZT 5550 can also function in a standard (non-Hot Swap) CompactPCI system.

### **Rear-Panel I/O**

The following I/O signals are routed out the J3 Rear-Panel User I/O Connector.

- COM1

- COM2

- Floppy

- Ethernet A

- Ethernet B

- Front Panel Eject LED

- SMBus

- Speaker

- Keyboard

- USB (Port 1)

- PS/2 Mouse

- IDE secondary channel

### **Dual CompactPCI System Slot Interfaces**

The ZT 5550 features two Intel 21154 PCI-to-PCI bridges to support both the J1/J2 and J4/J5 CompactPCI Bus Segments. The 21154 is compliant with the *PCI Local Bus Specification, Revision 2.1.* Each System Slot Interface provides the isolation, arbitration, and clocks for seven PCI peripheral cards, meaning support for up to 14 CompactPCI peripherals (all bus masters) without the need for an external bridge board.

Special features of the 21154 include:

- 33 MHz PCI bus operation

- 64-bit PCI transparent operation with 32-bit or 64-bit devices between backplane bus segments

#### Intel Pentium III Processor

The ZT 5550 uses the Intel Pentium III Processor Mobile Module (EMC-2), a small, highly integrated assembly containing an Intel Pentium III mobile processor and its immediate system-level support. The processor module contains a power supply for the processor's unique voltage requirements, system memory (L2 cache), and the core logic required to bridge the processor to the standard system buses. The module interfaces electrically to its host system via a 3.3V PCI bus, a 3.3V memory bus, and some Intel 443BX Host Bridge control signals.

The Intel Pentium III Processor Mobile Module includes 32 KB of code and data cache (L1 cache). Additionally, the Pentium III Processor Mobile Module contains a secondary 512 KB cache (L2 cache) to further enhance memory performance.

### I/O Expansion Connector

The ZT 5550's 100-pin, 2 mm, stacking I/O Expansion Connector (J6) routes VGA, IDE (secondary), and floppy signals between the CPU and an Intel I/O Expansion board (such as the ZT 96072 and the ZT 96073).

### **SMBus (Alarming Functions)**

The ZT 5550 incorporates the System Management Bus (SMBus) for access to several system monitoring and alarming functions. The SMBus allows the ZT 5550 to monitor onboard operating voltages and temperatures.

Since the HC comes out of PCI reset with the SMBus isolated from the backplane, the system BIOS (or user software) is required to enable SMBus access to the backplane. The system BIOS provides a user setup option to determine how the SMBus should be enabled. The SMBus Isolation Control functions are implemented in the HC with the register mapped at BAR Offset 7Ah as shown in the "SMBus Isolation Control" table.

Board and processor temperatures are monitored and can be set to interrupt at programmable thresholds. The SMBus is supported with an Intel software driver that can be used to read and program the various devices.

Additionally, the SMBus is accessible to certain optional rear-panel transition boards (such as the ZT 4804) via rear-panel user I/O connector J3.

Intel's optional alarm software may be purchased for telecommunication alarm applications, where data logging, programmable alarms, and system management is desired. This software utility provides program notification and visual indication of events and event statuses. See Chapter 7, "System Monitoring And Alarms," for more information.

#### **SMBus Isolation Control**

| BAR<br>Offset | 110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110 |                         | Default Value | Access | Size    | Reset  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------|--------|---------|--------|

| 7Ah           | SMB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SMBus Isolation Control | 00h           | R/W    | 8 bits  | PCIRST |

| Bit           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                         |               |        | Default |        |

| 7:1           | Reserved – Reserved for future use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |               |        |         | XX     |

| 0             | <b>SMBus Enable</b> – When this bit is 0, the SMBus is disconnected from the backplane. When this bit is set to 1, the SMBus is connected to the backplane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                         |               | R/W    |         | 0      |

#### **AGP Mezzanine**

The ZT 5550 provides a 114-pin AGP mezzanine connector for interfacing to an Intel AGP Video Mezzanine Adapter (such as the ZT 96079). The CPU - AGP adapter combination

occupies only a single CompactPCI slot. The AGP bus supports 32 bits of data and runs at a speed of 66 MHz, giving it a theoretical bandwidth of 266 MB/s in 1x AGP mode, or 533 MB/s in 2x AGP mode (two transfers per clock cycle).

The topic "AGP Video" in Appendix E, "Data Sheet Reference," contains a link to an Intel website detailing its "Accelerated Graphics Port Technology". The site also provides a link to the AGP Specification.

#### **PCI Mezzanine**

The PCI bus (Primary, Bus 0) mezzanine interface (J7) provides 3.3V PCI signaling to Intel I/O expansion boards and optional mezzanine adapter boards that may be attached to the ZT 5550.

#### **Dual Ethernet Interfaces**

The ZT 5550 provides two Ethernet interfaces (ENET A / ENET B) through the industry standard Intel 21143 PCI-Ethernet Bridge. The Physical Interface (PHY) is provided by the Level One LXT970 Dual-Speed Fast Ethernet Transceiver.

Both 10 Mbit/s and 100 Mbit/s Ethernet protocols are automatically detected through each of two RJ-45 connectors on the faceplate. Status LEDs on the faceplate indicate transmit and receive activity and 100 Mbit operation for each channel.

In a non-HA system, both ENET channels are available through rear-panel user I/O connector J3. In an HA system, ENET B is directed out J5 to serve as a communications channel (COMM) for inter-CPU messaging, fault detection, and data base synchronization.

The topic "Ethernet" in Appendix E, "Data Sheet Reference," contains links to the data sheets for the Ethernet devices used on the ZT 5550.

### **Memory and I/O Addressing**

A single, 168-pin, SDRAM DIMM is used on the ZT 5550 for local memory. The ZT 5550 supports modules of 32, 64, 128 and 256 MB. The SDRAM is implemented as Error Correcting Coded (ECC), which will correct single bit errors (97% of all DRAM errors are single bit errors) and report multiple bit errors to the operating system.

The ZT 5550 also provides 4 MB of on-board flash memory. The flash memory contains the system BIOS. The remainder may be allocated as solid-state drive. A 128 KB battery-backable SRAM device is also provided for application use, or for video emulation in cases where the CPU has no local video.

See the "Memory Configuration" and "I/O Configuration" topics in Chapter 2 for more information.

#### Serial I/O

The ZT 5550 provides two 16C550 PC-compatible serial ports:

Front Panel: COM1 directed out J11

Rear Panel: COM1 and COM2 directed out J3

The serial ports are implemented with a 5V charge pump technology to eliminate the need for a ±12V supply. Both serial ports include a complete set of handshaking and modem control signals, maskable interrupt generation, and data transfer rates up to 115.2 KB. The serial ports are configured as DTE. The COM1 RS-232 transceiver enable can be software controlled.

Since the HC comes out of PCI reset with the COM1 transceiver disabled, the system BIOS (or user software) is required to enable COM1. The system BIOS provides a user setup option to determine how COM1 should be enabled. The COM1 Isolation Control functions are implemented in the HC with the register mapped at BAR Offset 0Bh as shown in the "COM1 Isolation Control" table.

The ZT 5550's serial controller resides in the National Semiconductor\* PC87309 SuperI/O\* device. The topic "SuperI/O" in Appendix E, "Data Sheet Reference," provides a link to the data sheet for this device.

#### **COM1** Isolation Control

| BAR<br>Offset | Register Symbol                                                                                                                                                                                                                                                                | Register Name              | Default Value | Access | Size  | Reset  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------|--------|-------|--------|

| 0Bh           | COM1                                                                                                                                                                                                                                                                           | COM1 Isolation Control 00h |               |        |       | PCIRST |

| Bit           | Description                                                                                                                                                                                                                                                                    |                            |               |        | Defau | ılt    |

| 7:2           | Reserved                                                                                                                                                                                                                                                                       | Reserved                   |               |        |       |        |

| 1             | <b>COM1 Active Host Enable</b> – This bit has meaning only when bit 0 of this register is cleared to 0. When COM1[0] = 0, and this bit is set to 1, the COM1_ENA output is put in high impedance only when this host is in Active mode. This function is disabled when HA = 0. |                            |               |        | 0     |        |

| 0             | COM1 Unconditional Enable – When this bit is set to 1, the COM1_ENA output is put in high impedance regardless of the HC operating mode. In practice, COM1_ENA is routed to the active-high COM1 transceiver ENABLE input, which has a passive pull-up.                        |                            |               |        | 0     |        |

### **Interrupts**

Two enhanced, 8259-style interrupt controllers provide the ZT 5550 with a total of 15 interrupt inputs. Interrupt controller features include support for:

Level-triggered and edge-triggered inputs

- Individual input masking

- Fixed and rotating priorities

Interrupt sources include:

- Serial I/O

- Keyboard

- Floppy disk

- IDE interface

- On-board PCI devices

- Digital I/O

- Printer Port

- Counter/Timers

- Real-Time Clock

- CompactPCI backplane (21154)

Enhanced capabilities include the ability to configure each interrupt level for active highgoing edge or active low-level inputs.

The ZT 5550's interrupt controllers reside in the Intel 82371EB (PIIX4E) device. The topic "PIIX4" in Appendix E, "Data Sheet Reference," provides a link to this data sheet.

#### Counter/Timers

Three 8254-style counter/timers are included on the ZT 5550 as defined for the PC/AT. Operating modes supported by the counter/timers include interrupt on count, frequency divider, square wave generator, software triggered, hardware triggered, and one shot.

The ZT 5550's Counter/Timers reside in the Intel 82371EB (PIIX4E) device. The topic "PIIX4" in Appendix E, "Data Sheet Reference," provides a link to this data sheet.

In addition to the 8254-style counter/timers provided in the 82371EB (PIIX4E) device, the ZT 5550 also provides two custom timers offering unique functions to telecommunications applications. These timers reside in the custom Host Controller device and are described in Chapter 10, "Timers."

#### **DMA**

Two enhanced, 8237-style DMA controllers are provided on the ZT 5550 for use by the onboard peripherals. DMA channel 2 is reserved for a future peripheral such as an optional floppy drive. DMA channels 1 or 3 are assigned to the parallel printer port for ECP mode support

The ZT 5550's DMA controllers reside in the Intel 82371EB (PIIX4E) device. The topic "PIIX4" in Appendix E, "Data Sheet Reference," provides a link to this data sheet.

#### **Real-Time Clock**

The real-time clock performs timekeeping functions and includes 256 bytes of general-purpose, battery-backed, CMOS RAM. Timekeeping features include an alarm function, a maskable periodic interrupt, and a 100-year calendar. The system BIOS uses a portion of this RAM for BIOS setup information. The system BIOS is also Year 2000 (Y2K) Compliant.

The ZT 5550's Real-Time Clock resides in the Intel 82371EB (PIIX4E) device. The topic "PIIX4" in Appendix E, "Data Sheet Reference," provides a link to this data sheet.

### **Power Ramp Circuitry**

The ZT 5550's power ramp circuitry prevents glitches to the power supply and disruption to CompactPCI peripherals caused by insertion or removal of the CPU. Power ramp circuitry allows the board's voltages to be ramped in a controlled fashion, thereby eliminating any large voltage or current spikes caused by removing or inserting the board while the system is still under power. This controlled ramping is a requirement of the *CompactPCI Hot Swap Specification*, *PICMG 2.1*, *Version 2.0*.

The ZT 5550's hot swap controller unconditionally resets the board when it detects that the 3.3V, 5V, and 12V supplies are below an acceptable operating limit. These limits are defined as 4.75V (5V supply), 3.0V (3.3V supply), and 10.0V (+12V supply).

Fault current sensing is also provided. If a board fault (short circuit) or over-current condition is detected, the hot swap controller automatically removes power from the ZT 5550 components and the "Fault/Power" indicator LED turns red.

See Chapter 5 "Hot Swap" for more information. You may also wish to obtain the complete CompactPCI Hot Swap Specification, PICMG 2.1, Version 2.0. A link to PICMG's website is provided in the topic "Hot Swap" in Appendix E, "Data Sheet Reference."

#### Reset

The ZT 5550's various reset types can be tailored to the needs of specific applications.

- Backend Power Down

- Hard Reset

- Soft Reset

- NMI

See Chapter 6, "Reset," for more information. See the PIIX4E data sheet to learn more about the Reset and Control Register within the Intel 82371EB (PIIX4E) device. A link to the data sheet is provided in the topic "PIIX4" in Appendix E, "Data Sheet Reference."

### **Two-Stage Watchdog Timer**

The ZT 5550's custom two-stage watchdog timer circuit is contained in the High Availability Host Controller. The watchdog timer monitors system operation and is programmable for one of eight different timeout periods (from 0.25 s to 256 s). When the watchdog times out, the first-stage timeout (T1) is driven first, followed by the second-stage (T2) 250ms later. T1 results in an NMI or a CPUINIT, depending on DIP switch configuration. When the switch is closed, CPUINIT is asserted; when open, NMI is asserted. T2 results in a hard reset. Watchdog T1 and T2 can be independently disabled.

See Chapter 9, "Watchdog Timer," for more information about the ZT 5550's Watchdog Timer implementation. Chapter 9 also includes sample code showing how to use the watchdog in an application.

### **Universal Serial Bus (USB)**

The emerging Universal Serial Bus (USB) provides a common interface to slower-speed peripherals. In the future, functions such as keyboard, serial ports, printer port, and mouse ports will be consolidated into USB, greatly simplifying the cabling requirements of future computers. The ZT 5550 provides a front panel USB port (J14, Port 0). A second USB port (Port 1) is directed through the ZT 5550's rear-panel I/O connector J3.

The ZT 5550's USB Host Controller resides in the Intel 82371EB (PIIX4E) device. The topic "PIIX4" in Appendix E, "Data Sheet Reference," provides a link to the data sheet for this device.

#### **Enhanced IDE Controller**

The ZT 5550 includes an Enhanced IDE controller for optional internal (CompactFlash socket) or external (IOX, RPIO) EIDE drives. The EIDE controller is covered in more detail in Chapter 8, "Enhanced IDE Controller."

The EIDE controller resides in the Intel 82371EB (PIIX4E) device. The topic "PIIX4" in Appendix E, "Data Sheet Reference," provides a link to the data sheet for this device.

### **Floppy Controller**

The ZT 5550 includes a Floppy Disk Controller for optional external (IOX, RPIO) floppy drives. The floppy controller resides in the National Semiconductor PC87309 SuperI/O device. The topic "SuperI/O" in Appendix E, "Data Sheet Reference," provides a link to the data sheet for this device.

### **Keyboard Controller**

The ZT 5550 includes an on-board PC/AT keyboard controller, available through front-panel connector J16. Keyboard signals are also available through rear-panel I/O connector J3.

The ZT 5550's keyboard controller resides in the National Semiconductor PC87309 SuperI/O device. The topic "SuperI/O" in Appendix E, "Data Sheet Reference," provides a link to the data sheet for this device.

#### Mouse

The ZT 5550 includes signals for a PS/2 style mouse, available through rear-panel I/O connector J3. The mouse is also available through front panel connector J16 when an IBM\* ThinkPad\* style "Y" cable is used. The system BIOS supports standard PS/2 bus mouse devices. Use of the PS/2 mouse leaves both serial ports available for other communication.

The ZT 5550's mouse controller resides in the National Semiconductor PC87309 SuperI/O device. The topic "SuperI/O" in Appendix E, "Data Sheet Reference," provides a link to the data sheet for this device.

### **Speaker Interface**

For external speaker interfacing, the ZT 5550 supports an external AT-compatible speaker through connector J23. The speaker outputs are also available through rear-panel I/O connector J3.

#### **LED Indicators**

The LEDs located on the connector plate are defined below. See the "Programming the LEDs" topic in Chapter 2 for software code used to program the User LEDs.

- Ethernet Channels A and B:

- Status LEDs, one per channel: green = 100Base-T; off = 10Base-T

- RJ-45 LEDs, two per connector: green = data receive; yellow = data transmit

- MIN MAJ CRIT (Minor = green; Major = yellow; Critical = red)

- RUN (CPU Activity): green = run; red = halt

- ACO (Alarm Cutoff): red = cutoff

- **SM** (System Master) (Revision C and earlier boards): green = this CPU Active; no light = this CPU Standby; red = configuration mode; orange = Active Host in reset

- TAKE (Takeover) (Revision C and earlier boards): green = friendly; red = hostile

- S1 and S2 Segment LEDS (Revision D and later boards):

| S1 LED | S2 LED | Meaning                                   |  |  |

|--------|--------|-------------------------------------------|--|--|

| Green  | Green  | Active both Segments                      |  |  |

| Green  | Black  | Active S1 - Armed for takeover            |  |  |

| Green  | Red    | Active S1 - Not Armed for takeover        |  |  |

| Green  | Orange | Active in System Slot in non-HA backplane |  |  |

| Black  | Green  | Active S2 - Armed for takeover            |  |  |

| Black  | Black  | Standby both Segments                     |  |  |

| Black  | Red    | Not Defined                               |  |  |

| Black  | Orange | Not Defined                               |  |  |

| Red    | Green  | Active S2 - Not Armed for takeover        |  |  |

| Red    | Black  | Non-Active in Config Mode                 |  |  |

| Red    | Red    | Non-Active in Local Reset                 |  |  |

| Red    | Orange | Active S2 - in Reset                      |  |  |

| Orange | Green  | Installed in Peripheral slot              |  |  |

| Orange | Black  | Not Defined                               |  |  |

| Orange | Red    | Active S1 - in Reset                      |  |  |

| Orange | Orange | Active both - in Reset                    |  |  |

- IDE (Local EIDE disk activity) green = active; off = inactive

- **PWR** (Power): green = power on; red = fault

- USR1 USR2: (Bi-color user LEDs)

- HOT SWAP: blue = board removal is allowed

#### **Software**

The Intel Netstructure Embedded BIOS is loaded in flash on board the ZT 5550. The BIOS is user-configurable to boot an operating system from local flash memory, a fixed or floppy drive, a CD-ROM drive, or over a network. The BIOS also supports the BIOS Boot Specification (BBS) to allow devices with BBS Option ROMs to be selectable in the boot order menu.

The ZT 5550 is compatible with all major PC operating systems. Intel provides additional operating system support when the ZT 5550 is purchased in conjunction with an Intel NetStructure development system (for example, the Intel NetStructure ZT 5083 15U High Availability Platform). This support may include additional drivers for NetStructure products such as peripherals and flash drives. Software device drivers for the ZT 5550 can be found at:

http://www.ziatech.com/software/matrix.htm.

The following operating systems are supported:

- Windows\* 2000 Professional OS or Windows 2000 Server OS

- Industry standard version of Linux\*

- Comprehensive board support package (BSP) for VxWorks\*. The CompactPCI VxWorks-Tornado II BSP streamlines the implementation of VxWorks on the ZT 5550. The VxWorks Tornado development system must be purchased directly from WindRiver.

### 2. Getting Started

This chapter summarizes the information you need to make the ZT 5550 CPU operational and should be read before attempting to use the board.

### **Unpacking**

Check the shipping carton for damage. If the shipping carton and contents are damaged, notify the carrier and Intel for an insurance settlement. Retain the shipping carton and packing material for inspection by the carrier. Obtain authorization before returning any product to Intel. Refer to the "Customer Support" section for assistance information.

**Caution:** Like all equipment utilizing MOS devices, the ZT 5550 must be protected from static discharge. Never remove any of the socketed parts except at a static-free workstation. Use the anti-static bag shipped with the ZT 5550 to handle the board.

### **System Requirements**

The following topics briefly describe the basic system requirements and configurable features of the ZT 5550 CPU board. Links are also provided to other chapters and appendices containing more detailed information.

### **Connectivity**

The ZT 5550 is designed to operate in a backplane providing CompactPCI buses on connectors J1/J2 and J4/J5. When used with the ZT 4804 RPIO Transition board, the backplane's rear panel connector on J3 must be available and have through-pins to the ZT 5550's J3 connector. See the "Connectors" topic in Appendix A for complete descriptions and pinout tables for all the board's connectors.

For specific backplane requirements in a High Availability system, see the "System Backplane" topic in Chapter 4.

### **LPT1 Signaling**

The ZT 5550 CPU does not direct LPT1 signals out the J3 Rear-Panel I/O connector. Therefore, if your system includes a ZT 5980 System Utility Board and/or a ZT 4800 Rear-panel I/O board, be aware that the LPT1 interfaces on these boards will not work with the ZT 5550 CPU, and hardware that may be connected to these interfaces can be damaged in a ZT 5550 implementation.

Warning: ZT 5550 users should not connect hardware to the ZT 5980 or the ZT 4800 LPT1 interfaces!

### **Electrical and Environmental Requirements**

The parameters given below should be maintained to avoid improper operation and possible damage to the board.

The ZT 5550 requires +5VDC  $\pm$  5% @ 2.2A typical, 3.8A maximum; +3.3VDC  $\pm$  5% @ 2.7A typical, 4.4A maximum; +12VDC  $\pm$  5% @ 250mA typical, 350mA maximum.

Intel recommends vertical mounting. Depending on your configuration, the ZT 5550 is supplied with a heatpipe to allow operation between 0° and approximately 50° C ambient. Heatpipe configurations require 250 LFM (linear feet per minute) of airflow across the board.

The maximum power dissipation of the EMC-2 module is 14 W. External airflow must be provided if operating above 25° C ambient. Because the ambient temperature (around the heatsink) can easily exceed 25° C in an enclosed card rack, it is strongly recommended that a "fan tray" below the card rack be used to supply external airflow. The relative humidity should be less than 95%, non-condensing.

Maintain these parameters to avoid improper operation and possible damage to the board. See Appendix A, "Specifications," and Appendix B, "Thermal Considerations," for more details.

#### Switches and Cuttable Traces

The ZT 5550 CPU Board provides several switch and cuttable trace configuration options for features that cannot be provided through the BIOS Setup Utility. Refer to Chapter 3, "Configuration," for location figures and descriptions.

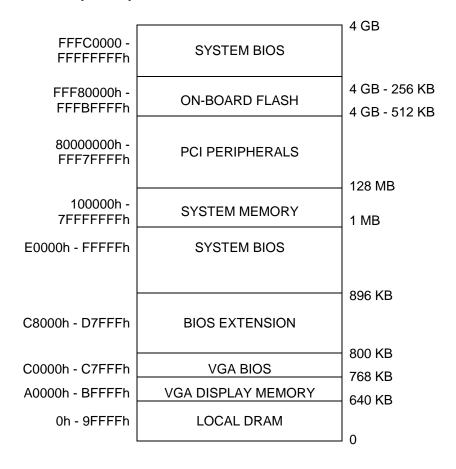

### **Memory Configuration**

The ZT 5550 addresses up to 4 GB of memory. The address space is divided between memory local to the board and memory located on the CompactPCI bus (or buses). Any memory not reserved or occupied by a local memory device (SDRAM/flash) is available to the CompactPCI bus.

The ZT 5550 is populated with several memory devices:

SDRAM Industry-standard, 168-pin, DIMM socket (J10) supports SDRAM

modules up to 256 MB.

Flash 4 MB flash device soldered directly to the board contains the BIOS,

and optionally space for use as solid state drive.

SRAM 128 KB battery-backed static RAM device.

The "Memory Address Map Example" illustration shows example memory addressing for the ZT 5550.

### I/O Configuration

The ZT 5550 addresses up to 64 KB of I/O using a 16-bit I/O address. The address space is divided between I/O local to the board and I/O on the CompactPCI bus. Any I/O space not occupied by a local I/O device is available for the CompactPCI bus. The ZT 5550 is populated with several I/O peripheral devices for industrial control and computing applications. The I/O address location for each of the peripherals is shown in the "I/O Address Map" illustration.

#### **Memory Address Map Example**

#### I/O Address Map

|                                  |      |         |                                      | 1 64 K |

|----------------------------------|------|---------|--------------------------------------|--------|

|                                  | D00h | — FFFFh | PCI*                                 |        |

| *Onboard ISA peripherals         | CF8h | — CFFh  | PCI Config/RST Control               |        |

| addressed between                | 780h | — CF7h  | PCI Reserved                         |        |

| 100h - 7FFh decode 11            | 780h | — 77Fh  | LPT ECP Registers                    |        |

| bits of address (A0 - A10).      | 400h | — 777h  | RESERVED                             | 4.12   |

| Therefore, these peripherals     | 3F8h | — 3FFh  | COM1                                 | 1 K    |

| will alias throughout the 16-bit | 3F0h | — 3F7h  | Floppy / IDE Registers               |        |

| I/O space at the following       | 3E0h | — 3EFh  | Reserved                             |        |

| ranges:                          | 3B0h | — 3DFh  | VGA Registers                        |        |

| x100-x3FFh                       | 380h | — 3AFh  | Reserved                             |        |

| x500-x7FFh                       | 378h | — 37Fh  | LPT                                  |        |

| x900-xBFFh                       | 300h | — 377h  | Reserved                             | 700    |

| xD00-xFFFh                       | 2F8h | — 2FFh  | COM2                                 | 768    |

| PCI devices can fully utilize    | 200h | — 2F7h  | Reserved                             | - 40   |

| the address space from           | 1F8h | — 1FFh  | Reserved                             | 512    |

| D00 - FFFFh, since subtractive   | 1F0h | — 1F7h  | Primary IDE Registers                |        |

| decoding is used for the         | 178h | — 1DFh  | Reserved                             |        |

| onboard ISA devices.             | 170h | — 177h  | Secondary IDE Registers              |        |

|                                  | 100h | — 16Fh  | Reserved                             | 050    |

|                                  | F0h  | — FFh   | Coprocessor                          | 256    |

|                                  | E0h  | — EFh   | Digital I/O                          |        |

|                                  | C0h  | — DFh   | On-board Slave DMA Controller        |        |

|                                  | B4h  | — BFh   | Reserved                             |        |

|                                  | B2h  | — B3h   | APM Registers                        |        |

|                                  | B0h  | — B1h   | Reserved                             |        |

|                                  | A0h  | — AFh   | On-board Slave Interrupt Controller  |        |

|                                  | 93h  | — 9Fh   | Reserved                             |        |

|                                  |      | 92h     | Fast RESET and Gate A20              |        |

|                                  | 90h  | — 91h   | Reserved                             |        |

|                                  | 81h  | — 8Fh   | On-board DMA Page Registers          |        |

|                                  |      | 80h     | Diagnostic Port                      |        |

|                                  |      | 79h     | ZT 5550 Watchdog Timer Register      |        |

|                                  |      | 78h     | ZT 5550 System Register 0            |        |

|                                  | 70h  | — 77h   | On-board Real-Time Clock             |        |

|                                  | 60h  | — 6Fh   | Keyboard and System Ports            |        |

|                                  | 50h  | — 5Fh   | Reserved                             |        |

|                                  | 40h  | — 4Fh   | On-board Timer/Counters              |        |

|                                  | 30h  | — 3Fh   | Reserved                             |        |

|                                  | 2Eh  | — 2Fh   | 87309 SuperI/O Configuration         | ]      |

|                                  | 22h  | — 2Dh   | Reserved                             |        |

|                                  | 20h  | — 21h   | On-board master Interrupt Controller |        |

|                                  | 0h   | — 1Fh   | On-board Master DMA Controller       | 0      |

|                                  |      |         |                                      |        |

### **Programming the LEDs**

The ZT 5550 includes two user-controlled bi-color (red/green) Light-Emitting Diodes (LEDs) located on the connector plate. The LEDs are software programmable through System Register 7 (Port E5h). The LEDs are turned off after a power cycle or a reset.

As shown below, two bits are used to control the state of each LED. Bits 0 and 2 change the LED from red to green; Bits 1 and 3 turn the LED on or off. Since a bi-color LED is used, there are three states for the LED: green, red, and off.

| User LED1                  |             | User LED2           |             |

|----------------------------|-------------|---------------------|-------------|

| E5h Bit 1 = 1              | LED1 is ON  | E5h Bit 3 = 1       | LED2 is ON  |

| E5h Bit 0 = 1              | Green       | E5h Bit 2 = 1       | Green       |

| E5h Bit 0 = 0              | Red         | E5h Bit 2 = 0       | Red         |

| E5h Bit 1 = 0 <sup>1</sup> | LED1 is OFF | E5h Bit $3 = 0^{1}$ | LED2 is OFF |

**Note:** <sup>1</sup> Indicates 'off' condition after power-on or hard reset.

The LED bits are in the same register as other functions. It is important **not** to change the state of other bits in this register when modifying the User LED status. The following code demonstrates the mechanism for modifying the bits for LED1:

```

; set USR1 LED ON (GREEN)

cli

; clear interrupts

al, E5h

in

; read current state

al, FCh

; preserve other register bits

and

al, 03h

; set USR1 LED (GREEN and enabled)

or

E5h, al

; output new value for register

out

sti

; re-enable interrupts

; set USR1 LED ON (RED)

; clear interrupts

cli

al, E5h

in

; read current state

and

al, FCh

; preserve other register bits

; set USR1 LED (RED and enabled)

or

al, 02h

E5h, al

out

; output new value for register

; re-enable interrupts

sti

; set USR1 LED OFF

cli

; clear interrupts

al, E5h

; read current state

in

and al, FDh

; set bit 3 to turn off LED

out E5h, al

; output new value for register

sti

; re-enable interrupts

```

#### **Video Interface Selection**

When used without IOX or RPIO boards, the ZT 5550 provides front-panel video only (J15—an AGP video board is also required for front panel video). A ZT 5550 used in combination with certain IOX and RPIO boards supports both front- and rear-panel video. Interfaces are enabled through software on the CPU and switch settings on the IOX board. Details on rear-panel video configuration in multi-board systems are presented in the "Configuration" chapter of IOX board manuals.

### **Removing Mezzanine Boards**

Your system may implement an I/O Expansion board (such as the ZT 96072 or ZT 96073) or a Intel mezzanine adapter (such as the ZT 97074 AGP Video Adapter). Mechanical connection of IOX boards and mezzanine adapters is reinforced by metal or nylon stand-offs screwed through mounting holes in each board.

**Caution:** To avoid damage to the CPU, IOX boards, and mezzanine adapters install or remove boards at a static-free workstation. When disconnecting boards, Intel recommends removing only the screw attaching the board to the stand-off. If it is necessary to remove the stand-off from the CPU, be aware that on some CPUs washers may be located between the PCB and the stand-off. Be sure to retain and re-install these washers to their original position if they are removed for any reason.

Care should also be taken when installing and removing boards to prevent premature wear or accidental bending of pins and receptacles. When removing a board, try to disengage the pins evenly across the length of the connector instead of prying only from one side. It may be helpful to gently wiggle the board from side-to-side when removing it.

### **BIOS Configuration Overview**

This topic presents a brief introduction to the Intel NetStructure Embedded BIOS. For more detailed information about the BIOS and other utilities, see the *Intel NetStructure Embedded BIOS* software manual. The Intel NetStructure Embedded BIOS has many separately configurable features. These features are selected by running the built-in Setup utility.

Setup is a utility you use to configure your system. The system configuration settings are saved in a portion of the battery-backed RAM in the real-time clock device and are used by the BIOS to initialize the system at boot up or reset. The configuration is protected by a checksum word for system integrity. To access the Setup utility, press the "F2" key during the system RAM check at boot time.

When Setup runs, an interactive configuration screen displays. See the "Setup Screen" illustration below for an example. Setup parameters are divided into different categories. The available categories are listed in a menu across the top of the Setup screen. The parameters within the highlighted (current) category are listed in the main (left) portion of the Setup screen. Context sensitive help is displayed in the right portion of the screen for each parameter. A legend of keys is listed at the bottom of the Setup screen.

Use the left and right arrow keys to select a category from the menu. Use the up and down arrow keys to select a parameter in the main portion of the screen. Use the + or – keys to change the value of a parameter.

Items in the main portion of the screen that have a triangular mark to their left are submenus. To display a submenu, use the up and down arrow keys to highlight the submenu and then press the "Enter" key.

#### Setup Screen

### **Console Redirection**

Console Redirection allows users to monitor the ZT 5550's boot process and to run the ZT 5550's SETUP utility from a remote serial terminal. Connection is made either directly through a serial port or through a modem.

The Console Redirection feature is most useful in cases where it is necessary to communicate with an Intel single board computer, such as the ZT 5550, in an embedded application without video support.

See the *Intel NetStructure Embedded BIOS Software Manual* for more information about Console Redirection.

### **Identifying Media Options**

It may be helpful to review the *ZT 5550 High Availability Software Manual for Windows NT\** for an overview of ZT 5550 software considerations prior to installing software on the board. For detailed information about your operating system, refer to the documentation provided by the operating system vendor.

The "Media Options" table below identifies the media options that may be available to you depending on the boards in your system. Use it to determine the target and distribution media you will use to install software on the ZT 5550 CPU.

#### **Media Options**

| Media                                  | Possible Device Locations                                                                                                                                                                                                            | Cable Interfaces                                                                                                                                                                                                              |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| On-board flash device                  | ZT 5550 CPU — a portion of this 4 MB device may be available as solid state drive, used to contain user programs and data. This feature requires a driver. Intel provides drivers (on the BSP CD-ROM) for several operating systems. | N/A                                                                                                                                                                                                                           |  |

| IDE devices                            |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                               |  |